JP2010032834A - マトリクス型表示装置 - Google Patents

マトリクス型表示装置 Download PDFInfo

- Publication number

- JP2010032834A JP2010032834A JP2008195727A JP2008195727A JP2010032834A JP 2010032834 A JP2010032834 A JP 2010032834A JP 2008195727 A JP2008195727 A JP 2008195727A JP 2008195727 A JP2008195727 A JP 2008195727A JP 2010032834 A JP2010032834 A JP 2010032834A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- pixel

- area

- substrate

- pixel electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Abstract

【解決手段】画素電極1が形成されている第1基板10Aと、対向電極21が形成されている第2基板20と、前記画素電極1と対向電極21の間に設けられた光制御層30とを有するマトリクス型表示装置60Aであって、前記画素電極1の上層に、絶縁膜2を介して前記画素電極1の一部を覆うように参照電極3を配設する構成とすることにより、前記画素電極1と参照電極3との間で保持容量を形成するとともに、前記画素電極1と対向電極21との間に形成される液晶容量を前記参照電極3の領域相当分だけ減少させる。

【選択図】図1

Description

責任編集:堀 浩雄、鈴木幸治、「カラー液晶ディスプレイ」、共立出版、2001年発行、第116〜120頁。

ベース基板と、該ベース基板上に設けられた画素形成部及びスイッチング素子部とを有する第1基板であって、該画素形成部には、前記ベース基板上に形成された画素電極と、該画素電極の一部を覆うように形成された絶縁膜と、該絶縁膜上に形成され、前記画素電極との平面視における重複部分の面積がBとなるように形成された参照電極とを少なくとも有する第1基板と、

透明基板と、該透明基板上の全面又は一部に前記画素電極に対向するように形成された対向電極とを有する第2基板と、

前記第1基板と前記第2基板との間に設けられて前記画素電極と前記対向電極との間に電圧を印加することで光学特性が変化する光制御層と、を備えるマトリクス型表示装置であって、

各画素単位において、前記画素電極と前記面積Bからなる参照電極との平面視での重複部分が保持容量を構成し、前記画素電極の面積から前記面積Bを差し引いた面積をAとしたとき、該面積Aからなる画素電極と前記対向電極との平面視での重複部分が画素容量を構成することを特徴とする。

透明基板と、該透明基板上の全面又は一部に前記画素電極に対向するように形成された対向電極とを有する第2基板と、

前記第1基板と前記第2基板との間に設けられて前記画素電極と前記対向電極との間に電圧を印加することで光学特性が変化する光制御層と、を備えるマトリクス型表示装置であって、

各画素単位において、前記画素電極と前記面積Bからなる第1参照電極との平面視での重複部分が第1保持容量を構成し、前記画素電極と前記第2参照電極との平面視での重複部分が第2保持容量を構成し、前記画素電極の面積から前記面積Bを差し引いた面積をAとしたとき、該面積Aからなる画素電極と前記対向電極との平面視での重複部分が画素容量を構成することを特徴とする。

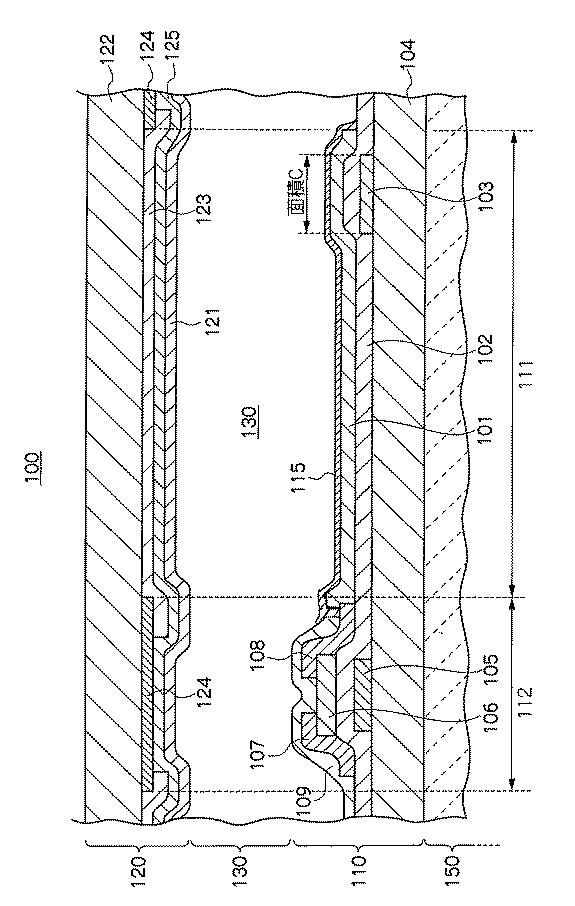

図1、図2及び図5(以下、これらを示すときは「図1等」という。)は、本発明のマトリクス型表示装置の単画素領域の例を示す模式的な断面図であり、図3は、本発明のマトリクス型表示装置の単画素領域の一例を示す模式的な平面図であり、図4は、本発明のマトリクス型表示装置の単画素の等価回路図の模式図である。ここで、図1及び図2に示すマトリクス型表示装置60A,60Bは、光制御層30として液晶層が採用されてなる液晶表示装置を示す実施形態であり、図5に示すマトリクス型表示装置60Cは、光制御層30’としてマイクロカプセル方式の電気泳動層が採用されてなる電気泳動表示装置を示す実施形態である。なお、以下において、各マトリクス型表示装置60A,60B,60Cを総称するときは、符号60で表す。

第1形態に係る第1基板10Aは、図1に示すように、ベース基板4上の面内方向に規則的に設けられた単画素を多数有している。図1では、スイッチング素子部12と画素形成部11とを備えた単画素を表している。

第2形態に係る第1基板10Bは、図2に示すように、画素電極1の下(ベース基板4の側)に第2絶縁膜14を介して対向電極21と同電位の第2参照電極13が形成されている点で上記の第1形態に係る第1基板10Aと相違するが、それ以外は第1形態に係る第1基板10Aと同様である。以下において、第1形態に係る第1基板10Aと同じ符号で表した構成要素は、第1形態のものと同じであるのでその説明は最小限にする。

第2基板20は、第1基板10が有する画素電極1と参照電極3(第2形態では第1参照電極3)に対向するように対向電極21が設けられている。より詳しくは、この第2基板20は、図1等に示すように、透明基板22と、その透明基板22の一方の面(光制御層30側の面)上に所定のパターンで形成された着色層23及びブラックマトリクス層24と、その着色層23及びブラックマトリクス層24上に形成された透明保護膜25と、その透明保護膜25上の全面又は一部に形成された対向電極21とを有するカラーフィルター基板である。なお、モノクロディスプレイやカラーフィルターを使用しないフィールドシーケンシャル方式ディスプレイなどの場合にはカラーフィルターを構成する必要はなく、対向電極21があればよい。なお、図示しないが、第2基板20の他方の面(光制御層30側の面の反対面)上には、通常、偏光板が設けられている。この偏光板と第1基板10に設けられている偏光板の光吸収軸は、それぞれ直交して配置されているものがある。

光制御層30として、液晶層又は電気泳動層を挙げることができる。これらの層は、第1基板10に設けられた画素電極1と第2基板20に設けられた対向電極21との間に設けられ、両電極間に電圧が印加されることによって光学特性が変化する。

本発明の第1形態に係るマトリクス型表示装置60A,60Cは、図1及び図5に示すように、各単位画素において、面積B[画素電極1の面積と参照電極3の面積との平面視における重複部分の面積]と、面積A[画素電極1の面積から前記した重複部分の面積Bを差し引いた面積]との比(B/A)が0.1/0.9以上0.7/0.3未満の範囲内であることが好ましい。

Ps=100×10−6×300×10−6×0.8×60×10−9×10000 =14.4pC

CST=46.5pF

εr/d=2.2×108

V’=(CLC+CST)/(C’LC+CST)×V、

ここで、液晶分子の誘電率異方性をΔεとすると、

C’LC=CLC+ε×Δε×S/d、

となることから、

V’=V−(ε×Δε×S/d)/(C’LC+CST)×V

となる。

図1に示す態様の第1形態に係るマトリクス型表示装置を作製した。最初に、第1基板10Aを作製した。先ず、ベース基板4として、アルミノシリケート系無アルカリガラスからなる厚さ600μmのガラス基板を用いた。そのベース基板4上に、クロム膜を厚さ100nmとなるようにDCマグネトロンスパッタ法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンのゲート電極5をスイッチング素子部12に形成すると共に走査線41を形成した。次に、同じくベース基板4上に、ITO膜を厚さ100nmとなるようにDCマグネトロンスパッタ法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンの画素電極1を画素形成部11に形成した。次に、図1に示すように、ゲート電極5を覆うと共に、画素電極1の一部(画素電極1の面積の30%)を覆うように、窒化シリコン膜を厚さd:36nmとなるようにPECVD法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンの絶縁膜2(ゲート絶縁膜を含む)をスイッチング素子部12及び画素形成部11に形成した。次に、ゲート電極5の上の絶縁膜2上に、厚さ200nmのノンドープのアモルファスシリコン(a−Si)膜と、リンをドープした厚さ50nmのn+a−Si膜とを連続してスパッタ成膜し、マスク露光、現像及びエッチング等を行って所定パターンの半導体膜6をスイッチング素子部12に形成した。次に、クロム膜を厚さ200nmとなるようにDCマグネトロンスパッタ法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンのソース電極7及びドレイン電極8をスイッチング素子部12に形成すると共に信号線42と参照電極3を形成した。次に、窒化シリコン膜を厚さ50nmとなるようにPECVD法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンの保護膜25を、スイッチング素子部12を覆うように形成した。最後に、ポリイミド膜を厚さ10nmとなるようにスピンコート法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンの液晶配向膜15を、画素電極1及び参照電極3を覆うように画素形成部11に形成した。こうして図1に示す形態の第1基板10Aを作製した。

実施例1において、画素電極1と参照電極3の形成パターンを変化させて面積Aと面積Bを表1に示すように変化させ、また絶縁膜2の膜厚dを変化させた他は、実施例1のマトリクス型表示装置と同様にして、実施例2,3及び比較例1のマトリクス型表示装置を作製した。また、比較例2に関しては、実施例1において、図6の構成となるように、参照電極103をゲート電極105と同時に形成し、画素電極101と参照電極103の面積A、Bが表1となるようにした他は、実施例1と同様にして、比較例1のマトリクス型表示装置を作製した。ただし、ここでの面積Aは、CLCを構成する面積として画素電極全面の面積を用いている。得られたマトリクス型表示装置について、B/A、画素容量CLC、保持容量CST、CST/CLCを計算して表1に示した。

実施例1において、液晶として、大きな誘電率異方性を持つナフタレン系液晶(Δε=7.2)を用いた他は、実施例1のマトリクス型表示装置と同様にして、実施例4,5のマトリクス型表示装置を作製した。なお、面積A、面積B及び絶縁膜2の膜厚dについては表1に示すように変化させた。また、比較例3,4に関しては、上記同様、液晶として大きな誘電率異方性を持つナフタレン系液晶(Δε=7.2)を用いた他は、比較例2と同様にしてした。計算したB/A、画素容量CLC、保持容量CST、CST/CLCを表1に示した。なお、表1中、Δεは液晶の誘電率異方性を表す。

実施例1において、液晶として、大きな誘電率異方性を持つフルオロナフタレン系液晶(Δε=23.69)を用いた他は、実施例1のマトリクス型表示装置と同様にして、実施例6のマトリクス型表示装置を作製した。なお、面積A、面積B及び絶縁膜2の膜厚dについては表1に示すように変化させた。計算したB/A、画素容量CLC、保持容量CST、CST/CLCを表1に示した。なお、表1中、Δεは液晶の誘電率異方性を表す。

図2に示す態様の第2形態に係るマトリクス型表示装置を作製した。最初に、第1基板10Bを作製した。先ず、ベース基板4として、アルミノシリケート系無アルカリガラスからなる厚さ600μmのガラス基板を用いた。そのベース基板4上に、クロム膜を厚さ100nmとなるようにDCマグネトロンスパッタ法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンのゲート電極5をスイッチング素子部12に形成すると共に走査線41と第2参照電極13を形成した。次に、ゲート電極5と第2参照電極13とを覆うように、窒化シリコン膜を厚さd:36nmとなるようにPECVD法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンの第2絶縁膜14(ゲート絶縁膜を含む)をスイッチング素子部12及び画素電極形成部11に形成した。次に、第2絶縁膜14上に、厚さ200nmのノンドープのアモルファスシリコン(a−Si)膜と、リンをドープした厚さ50nmのn+a−Si膜とを連続してPECVD成膜し、マスク露光、現像及びエッチング等を行って所定パターンの半導体膜6をスイッチング素子部12に形成した。次に、クロム膜を厚さ200nmとなるようにDCマグネトロン法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンのソース電極7及びドレイン電極8をスイッチング素子部12に形成すると共に信号線42を形成した。次に、ITO膜を厚さ150nmとなるようにDCマグネトロンスパッタ法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンの画素電極1を画素電極形成部11に形成した。次に、図1に示すように、画素電極1の一部(画素電極1の面積の30%)を覆うように、窒化シリコン膜を厚さ300nmとなるようにPECVD法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンの第1絶縁膜2と保護膜25を形成した。次に、クロム膜を厚さ200nmとなるようにDCマグネトロンスパッタ法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンの第1参照電極3を画素形成部11の第1絶縁膜2上に形成した。最後に、ポリイミドを厚さ10nmとなるようにスピンコート法で成膜し、マスク露光、現像及びエッチング等を行って所定パターンの液晶配向膜15を、画素電極1及び第1参照電極3を覆うように画素形成部11に形成した。こうして図2に示す形態の第1基板10Bを作製した。

2 絶縁膜(第1絶縁膜)

3 参照電極(第1参照電極)

4 ベース基板

5 ゲート電極

6 半導体膜

7 ソース電極

8 ドレイン電極

9 保護膜

10,10A,10B 第1基板

11 画素形成部

12 スイッチング素子部

13 第2参照電極

14 第2絶縁膜

15 液晶配向膜

20 第2基板

21 対向電極

22 透明基板

23 着色層

24 ブラックマトリックス層

25 透明保護膜

30 光制御層(液晶層)

30’ 光制御層(電気泳動層)

31 マイクロカプセル

41 走査線

42 信号線

50 バックライト等

60,60A,60B,60C マトリクス型表示装置

CLC 画素容量

CST 保持容量

CST1 第1保持容量

CST2 第2保持容量

CGS 寄生容量

A 画素電極の面積から面積Bを差し引いた面積

B 画素電極と第1参照電極との平面視での重複面積

C 画素電極と第2参照電極との平面視での重複面積

Claims (6)

- ベース基板と、該ベース基板上に設けられた画素形成部及びスイッチング素子部とを有する第1基板であって、該画素形成部には、前記ベース基板上に形成された画素電極と、該画素電極の一部を覆うように形成された絶縁膜と、該絶縁膜上に形成され、前記画素電極との平面視における重複部分の面積がBとなるように形成された参照電極とを少なくとも有する第1基板と、

透明基板と、該透明基板上の全面又は一部に前記画素電極に対向するように形成された対向電極とを有する第2基板と、

前記第1基板と前記第2基板との間に設けられて前記画素電極と前記対向電極との間に電圧を印加することで光学特性が変化する光制御層と、を備えるマトリクス型表示装置であって、

各画素単位において、前記画素電極と前記面積Bからなる参照電極との平面視での重複部分が保持容量を構成し、前記画素電極の面積から前記面積Bを差し引いた面積をAとしたとき、該面積Aからなる画素電極と前記対向電極との平面視での重複部分が画素容量を構成することを特徴とするマトリクス型表示装置。 - 各画素単位において、前記面積Bと前記面積Aとの比(B/A)が0.1/0.9以上0.7/0.3未満の範囲内である、請求項1に記載のマトリクス型表示装置。

- ベース基板と、該ベース基板上に設けられた画素形成部及びスイッチング素子部を有する第1基板であって、該画素形成部には、後に形成される画素電極との平面視における重複部分の面積がCとなるように前記ベース基板上に形成された第2参照電極と、該第2参照電極を覆うように形成された第2絶縁膜と、該第2絶縁膜上に形成された画素電極と、該画素電極の一部を覆うように形成された第1絶縁膜と、該第1絶縁膜上に形成され、前記画素電極との平面視における重複部分の面積がBとなるように形成された第1参照電極とを少なくとも有する第1基板と、

透明基板と、該透明基板上の全面又は一部に前記画素電極に対向するように形成された対向電極とを有する第2基板と、

前記第1基板と前記第2基板との間に設けられて前記画素電極と前記対向電極との間に電圧を印加することで光学特性が変化する光制御層と、を備えるマトリクス型表示装置であって、

各画素単位において、前記画素電極と前記面積Bからなる第1参照電極との平面視での重複部分が第1保持容量を構成し、前記画素電極と前記第2参照電極との平面視での重複部分が第2保持容量を構成し、前記画素電極の面積から前記面積Bを差し引いた面積をAとしたとき、該面積Aからなる画素電極と前記対向電極との平面視での重複部分が画素容量を構成することを特徴とするマトリクス型表示装置。 - 前記スイッチング素子部が薄膜トランジスタ部である、請求項1〜3のいずれか1項に記載のマトリクス型表示装置。

- 前記光制御層が液晶層である、請求項1〜4のいずれか1項に記載のマトリクス型表示装置。

- 前記光制御層が電気泳動材料層である、請求項1〜4のいずれか1項に記載のマトリクス型表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008195727A JP5608963B2 (ja) | 2008-07-30 | 2008-07-30 | マトリクス型表示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008195727A JP5608963B2 (ja) | 2008-07-30 | 2008-07-30 | マトリクス型表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010032834A true JP2010032834A (ja) | 2010-02-12 |

| JP5608963B2 JP5608963B2 (ja) | 2014-10-22 |

Family

ID=41737371

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008195727A Expired - Fee Related JP5608963B2 (ja) | 2008-07-30 | 2008-07-30 | マトリクス型表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5608963B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011242583A (ja) * | 2010-05-18 | 2011-12-01 | Seiko Epson Corp | 電気泳動表示装置及び電子機器 |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0455824A (ja) * | 1990-06-25 | 1992-02-24 | Matsushita Electric Ind Co Ltd | 液晶素子及びその製造法 |

| JPH05289082A (ja) * | 1992-04-07 | 1993-11-05 | Fujitsu Ltd | 液晶表示装置 |

| JPH0772506A (ja) * | 1993-06-14 | 1995-03-17 | Casio Comput Co Ltd | 薄膜トランジスタパネル |

| JPH09101543A (ja) * | 1995-10-05 | 1997-04-15 | Toshiba Corp | アクティブマトリクス型液晶表示装置 |

| JP2000019562A (ja) * | 1997-09-01 | 2000-01-21 | Canon Inc | 光学的変調素子 |

| JP2000310793A (ja) * | 1999-04-28 | 2000-11-07 | Canon Inc | 液晶素子 |

| JP2002311445A (ja) * | 2001-04-16 | 2002-10-23 | Hitachi Ltd | 液晶表示装置 |

| JP2003091019A (ja) * | 2001-09-19 | 2003-03-28 | Fujitsu Ltd | 液晶表示装置 |

| JP2007140526A (ja) * | 2005-11-18 | 2007-06-07 | Lg Philips Lcd Co Ltd | 電気泳動表示装置 |

-

2008

- 2008-07-30 JP JP2008195727A patent/JP5608963B2/ja not_active Expired - Fee Related

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0455824A (ja) * | 1990-06-25 | 1992-02-24 | Matsushita Electric Ind Co Ltd | 液晶素子及びその製造法 |

| JPH05289082A (ja) * | 1992-04-07 | 1993-11-05 | Fujitsu Ltd | 液晶表示装置 |

| JPH0772506A (ja) * | 1993-06-14 | 1995-03-17 | Casio Comput Co Ltd | 薄膜トランジスタパネル |

| JPH09101543A (ja) * | 1995-10-05 | 1997-04-15 | Toshiba Corp | アクティブマトリクス型液晶表示装置 |

| JP2000019562A (ja) * | 1997-09-01 | 2000-01-21 | Canon Inc | 光学的変調素子 |

| JP2000310793A (ja) * | 1999-04-28 | 2000-11-07 | Canon Inc | 液晶素子 |

| JP2002311445A (ja) * | 2001-04-16 | 2002-10-23 | Hitachi Ltd | 液晶表示装置 |

| JP2003091019A (ja) * | 2001-09-19 | 2003-03-28 | Fujitsu Ltd | 液晶表示装置 |

| JP2007140526A (ja) * | 2005-11-18 | 2007-06-07 | Lg Philips Lcd Co Ltd | 電気泳動表示装置 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011242583A (ja) * | 2010-05-18 | 2011-12-01 | Seiko Epson Corp | 電気泳動表示装置及び電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5608963B2 (ja) | 2014-10-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8502793B2 (en) | Touch screen display device and method of manufacturing the same | |

| JP5654677B2 (ja) | 液晶表示パネル及び液晶表示装置 | |

| TWI383204B (zh) | 多顯示域垂直配向型之液晶顯示面板及其製造方法 | |

| JP5764665B2 (ja) | 薄膜トランジスタアレイ基板及び液晶表示装置 | |

| US20080231779A1 (en) | Display substrate and display apparatus having the same | |

| US20070236623A1 (en) | Array substrate for liquid crystal display device and method of fabricating the same | |

| US7649578B2 (en) | Array substrate and display panel having the same with particular sensor electrodes | |

| US20110285610A1 (en) | Pixel structure and pixel circuit having multi-display mediums | |

| US9285647B2 (en) | TFT array substrate, E-paper display panel and method for manufacturing the same | |

| CN101266374A (zh) | 液晶显示器及其操作方法和制造方法 | |

| JP5728587B2 (ja) | 液晶駆動方法及び液晶表示装置 | |

| US20070146563A1 (en) | Liquid crystal display and method of manufacturing thereof | |

| WO2013001984A1 (ja) | 液晶表示パネル及び液晶表示装置 | |

| US20170235200A1 (en) | Display device and manufacturing method thereof | |

| US8339533B2 (en) | Vertical alignment mode liquid crystal display and method of manufacturing the same | |

| US7961265B2 (en) | Array substrate, display panel having the same and method of driving the same | |

| US20080278435A1 (en) | Display device and method of manufacturing the same | |

| JP4614726B2 (ja) | 液晶表示装置 | |

| US10281786B2 (en) | Display device using low capacitance bus lines having gate lines and data lines on different substrates | |

| JP2007058045A (ja) | 液晶表示装置 | |

| JP5608963B2 (ja) | マトリクス型表示装置 | |

| US20030202130A1 (en) | Floating electrode switching liquid crystal display | |

| CN101067704A (zh) | 像素结构、显示装置以及光电装置 | |

| JP2010032835A (ja) | マトリクス型表示装置 | |

| US20190072814A1 (en) | Display device and method of manufacturing the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110520 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121002 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121003 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121129 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130625 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130823 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140325 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140516 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140805 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140818 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5608963 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |