JP2010027984A - 不揮発性記憶装置およびその製造方法 - Google Patents

不揮発性記憶装置およびその製造方法 Download PDFInfo

- Publication number

- JP2010027984A JP2010027984A JP2008190174A JP2008190174A JP2010027984A JP 2010027984 A JP2010027984 A JP 2010027984A JP 2008190174 A JP2008190174 A JP 2008190174A JP 2008190174 A JP2008190174 A JP 2008190174A JP 2010027984 A JP2010027984 A JP 2010027984A

- Authority

- JP

- Japan

- Prior art keywords

- memory device

- electrode

- nonvolatile memory

- memory cell

- access transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 36

- 239000010410 layer Substances 0.000 claims description 143

- 239000004065 semiconductor Substances 0.000 claims description 85

- 239000000758 substrate Substances 0.000 claims description 66

- 230000004888 barrier function Effects 0.000 claims description 42

- 238000003860 storage Methods 0.000 claims description 40

- 238000000034 method Methods 0.000 claims description 36

- 239000011229 interlayer Substances 0.000 claims description 25

- 239000004020 conductor Substances 0.000 claims description 23

- 239000000463 material Substances 0.000 claims description 16

- 229910000618 GeSbTe Inorganic materials 0.000 claims description 13

- 229910018072 Al 2 O 3 Inorganic materials 0.000 claims description 8

- 229910052802 copper Inorganic materials 0.000 claims description 8

- -1 SbSe Inorganic materials 0.000 claims description 7

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 claims description 5

- 229910052718 tin Inorganic materials 0.000 claims description 5

- 229910052721 tungsten Inorganic materials 0.000 claims description 5

- 229910002546 FeCo Inorganic materials 0.000 claims description 4

- 229910005900 GeTe Inorganic materials 0.000 claims description 4

- 229910002367 SrTiO Inorganic materials 0.000 claims description 4

- 229910010413 TiO 2 Inorganic materials 0.000 claims description 4

- 229910052759 nickel Inorganic materials 0.000 claims description 4

- 230000001590 oxidative effect Effects 0.000 claims description 3

- 238000000151 deposition Methods 0.000 claims 3

- 229910052710 silicon Inorganic materials 0.000 abstract description 5

- 239000010703 silicon Substances 0.000 abstract description 5

- LPQOADBMXVRBNX-UHFFFAOYSA-N ac1ldcw0 Chemical compound Cl.C1CN(C)CCN1C1=C(F)C=C2C(=O)C(C(O)=O)=CN3CCSC1=C32 LPQOADBMXVRBNX-UHFFFAOYSA-N 0.000 abstract 1

- 238000010586 diagram Methods 0.000 description 33

- 239000010949 copper Substances 0.000 description 17

- 229910021332 silicide Inorganic materials 0.000 description 16

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 16

- 229910052751 metal Inorganic materials 0.000 description 15

- 239000002184 metal Substances 0.000 description 15

- 230000008859 change Effects 0.000 description 13

- 229910044991 metal oxide Inorganic materials 0.000 description 11

- 150000004706 metal oxides Chemical class 0.000 description 10

- 230000008569 process Effects 0.000 description 10

- 238000002955 isolation Methods 0.000 description 9

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 7

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 239000012535 impurity Substances 0.000 description 7

- 238000007747 plating Methods 0.000 description 7

- 229910052814 silicon oxide Inorganic materials 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 6

- 238000001459 lithography Methods 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- 230000005669 field effect Effects 0.000 description 4

- 239000012212 insulator Substances 0.000 description 4

- 230000010354 integration Effects 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 3

- 239000000470 constituent Substances 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 3

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 238000009825 accumulation Methods 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229910019001 CoSi Inorganic materials 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 230000002159 abnormal effect Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 230000012447 hatching Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 230000001568 sexual effect Effects 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Landscapes

- Semiconductor Memories (AREA)

Abstract

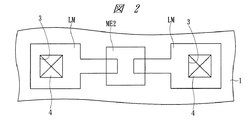

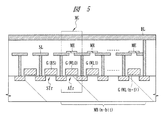

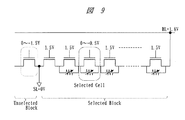

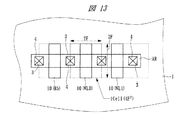

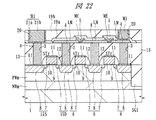

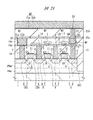

【解決手段】アクセストランジスタATrと、アクセストランジスタATrの一対のソース・ドレイン領域間に電気的に接続された記憶素子MEとからなるメモリセルMCが、隣接するメモリセルMC間でソース・ドレイン領域を共有して複数個直列に接続されて構成されるメモリセルブロックMBを備えている。メモリセルブロックMBの一方の端部とソース線SLとの間に選択トランジスタSTrが接続され、メモリセルブロックMBの他方の端部にビット線BLが接続されている。また、記憶素子MEは、その一部に100nm以下の幅のスリットを有して形成されたローカル配線上に、スリットを跨いで配置されている。

【選択図】図4

Description

本実施の形態1による不揮発性メモリセルの互いに異なる構造を有する3つの記憶素子を図1〜図3を用いて説明する。

Id=β(Vgs−Vth)2 式(1)

VthのVbb依存は、式(2)で表される。

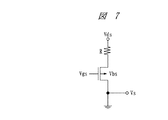

従って、図7に示すnMISのドレイン側に記憶素子を接続した回路では、ドレイン電流は式(3)で表されるので、

Id=β(Vgs−Vth)2 式(3)

nMISのドレイン側に記憶素子を接続した場合のドレイン電流Idの理論式が変わるわけではない。

本実施の形態2によるメモリセルのアクセストランジスタの構造は、前述した実施の形態1と同様であるが、記憶素子の構造が前述した実施の形態1と相違する。すなわち、前述した実施の形態1では、記憶素子MEの両端に接続される電極にローカル配線LMを用いたのに対して、本実施の形態2では、第1層目の配線M1を用いる。

本実施の形態3による不揮発性メモリセルを構成するNAND型セルアレイの構造を図28に示すメモリセルアレイの一部の基本回路図を用いて説明する。

本実施の形態4による不揮発性メモリセルを構成するNAND型セルアレイの構造を図29に示すメモリセルアレイの一部の要部平面図(基板からプラグ電極までの各層を重ねた要部平面図)を用いて説明する。

本実施の形態5による不揮発性メモリセルを構成するNAND型セルアレイの構造を図30に示すメモリセルの要部断面図を用いて説明する。

本実施の形態6による不揮発性メモリセルを構成するNOR型セルアレイの等価回路図を図31(a)および(b)に示す。図31(a)はメモリセルアレイの全体の等価回路図、図31(b)はメモリセルアレイの部分的な等価回路図である。ここでは、ソースを共有する2つのメモリセルM00,M10を例に挙げてメモリアレイ構成の詳細を説明するが、これら以外のソースを共有する2つのメモリセルについても同様である。

3 接続孔

4 プラグ電極

5 バリア層

6 ソース・ドレイン領域

7,8 半導体領域

9 ゲート絶縁膜

10 ゲート電極

11 シリサイド層

12 サイドウォール

13 層間絶縁膜

14 スリット

15D ドレイン領域

15S ソース領域

16 プラグ電極

19a ストッパ絶縁膜

19b 配線形成用絶縁膜

20 配線溝

21a バリアメタル膜

21b Cuめっき膜

22a ストッパ絶縁膜

22b ビア形成用絶縁膜

23 ビア

24 プラグ電極

25a バリアメタル膜

25b Cuめっき膜

27 絶縁膜

28 バリア層

29 半導体領域

30D ドレイン領域

30S ソース領域

31 絶縁膜

32 接続孔

ATr アクセストランジスタ

AR 活性領域

BL,BL0,BL1,BL(j−1) ビット線

BS ブロック選択線

D ドレイン

G ゲート

ISO 絶縁膜

LM ローカル配線

M1,M2 配線

M00,M10 メモリセル

MB メモリセルブロック

MC メモリセル

ME,ME1,ME2,ME3 記憶素子

NTr アクセストランジスタ

NWm nウェル

PWm pウェル

RP1,RP2,RP3 レジストパターン

S ソース

SGI 素子分離部

SL,SL0,SL(k−1) ソース線

STr,STr0,STr1 選択トランジスタ

WL0,WL1,WL2,WL3,WL4,WL5,WL6,WL7 ワード線

WL(i−1),WL(n−1) ワード線

Claims (34)

- 半導体基板上に、ゲート電極が第1方向に沿って形成されたワード線の一部からなるアクセストランジスタと、前記アクセストランジスタの一対のソース・ドレイン領域間に電気的に接続され、抵抗値の差によって記憶情報を判断する記憶素子とからなるメモリセルが、隣接する前記メモリセル間で前記ソース・ドレイン領域を共有して複数個直列に接続されて構成されるメモリセルブロックを備える不揮発性記憶装置であって、

前記メモリセルブロックの一方の端部に位置する前記アクセストランジスタとソース線との間に選択トランジスタが接続され、前記選択トランジスタのソース領域は前記ソース線と電気的に接続され、前記選択トランジスタのドレイン領域は前記メモリセルブロックの一方の端部に位置する前記アクセストランジスタの一方のソース・ドレイン領域と共有し、

前記メモリセルブロックの他方の端部に位置する前記アクセストランジスタの一方のソース・ドレイン領域が、前記第1方向と直交する第2方向に沿って形成されたビット線と電気的に接続されていることを特徴とする不揮発性記憶装置。 - 請求項1記載の不揮発性記憶装置において、前記アクセストランジスタを覆う層間絶縁膜と、前記アクセストランジスタの一対のソース・ドレイン領域にそれぞれ達して前記層間絶縁膜に形成された2つの接続孔と、2つの前記接続孔の内部にそれぞれ埋め込まれた2つのプラグ電極と、2つの前記プラグ電極間に電気的に接続され、前記第2方向に沿って形成された電極とをさらに含み、

前記電極に前記第1方向に沿ってスリットが形成され、前記スリットを跨いで前記記憶素子が配置されていることを特徴とする不揮発性記憶装置。 - 請求項2記載の不揮発性記憶装置において、前記スリットの幅は100nm以下であることを特徴とする不揮発性記憶装置。

- 請求項2記載の不揮発性記憶装置において、前記記憶素子と前記電極との間にバリア層が形成されていることを特徴とする不揮発性記憶装置。

- 請求項2記載の不揮発性記憶装置において、前記記憶素子は、NiO、CuO、TiO2、HfO2、ZrO2、Al2O3、GeSbTe、SbSe、GeTe、Nが添加されたGeSbTe、InがドープされたGeSbTe、SrZrO3、SrTiO3またはMgOにより構成されることを特徴とする不揮発性記憶装置。

- 請求項2記載の不揮発性記憶装置において、前記電極は、Ni、W、Cu、TiN、NiPt、Co、PyまたはFeCoにより構成されることを特徴とする不揮発性記憶装置。

- 請求項4記載の不揮発性記憶装置において、前記バリア層は、Cu、CuO、TaO、CrO、MgOまたはAl2O3により構成されることを特徴とする不揮発性記憶装置。

- 請求項2記載の不揮発性記憶装置において、前記電極はローカル配線であることを特徴とする不揮発性記憶装置。

- 請求項8記載の不揮発性記憶装置において、前記ローカル配線に第1層目の配線が電気的に接続され、前記第1層目の配線にプラグ電極を介して第2層目の配線が接続され、前記ソース線は前記第1層目の配線により構成され、前記ビット線は前記第2層目の配線により構成されることを特徴とする不揮発性記憶装置。

- 請求項8記載の不揮発性記憶装置において、前記ローカル配線に第1層目の配線が電気的に接続され、前記第1層目の配線にプラグ電極を介して第2層目の配線が接続され、前記ソース線は前記半導体基板に形成された半導体領域により構成され、前記ビット線は前記第2層目の配線により構成されることを特徴とする不揮発性記憶装置。

- 請求項2記載の不揮発性記憶装置において、前記電極は第1層目の配線により構成されることを特徴とする不揮発性記憶装置。

- 請求項11記載の不揮発性記憶装置において、前記第1層目の配線にプラグ電極を介して第2層目の配線が接続され、前記ソース線は前記第1層目の配線により構成され、前記ビット線は前記第2層目の配線により構成されることを特徴とする不揮発性記憶装置。

- 請求項11記載の不揮発性記憶装置において、前記第1層目の配線にプラグ電極を介して第2層目の配線が接続され、前記ソース線は前記半導体基板に形成された半導体領域により構成され、前記ビット線は前記第2層目の配線により構成されることを特徴とする不揮発性記憶装置。

- 請求項1記載の不揮発性記憶装置において、さらに、前記メモリセルブロックの他方の端部に位置する前記アクセストランジスタと前記ビット線との間に第2の選択トランジスタが接続され、

前記第2の選択トランジスタのドレイン領域は前記ビット線と電気的に接続され、前記第2の選択トランジスタのソース領域は前記メモリセルブロックの他方の端部に位置する前記アクセストランジスタの一方のソース・ドレイン領域と共有することを特徴とする不揮発性記憶装置。 - 請求項1記載の不揮発性記憶装置において、前記アクセストランジスタを覆う絶縁膜と、前記アクセストランジスタの一対のソース・ドレイン領域にそれぞれ達して前記絶縁膜に形成された2つの接続孔と、2つの前記接続孔を通じて前記一対のソース・ドレイン領域間に電気的に接続され、前記第2方向に沿って形成された電極とをさらに含み、

前記電極に前記第1方向に沿ってスリットが形成され、前記スリットを跨いで前記記憶素子が配置されていることを特徴とする不揮発性記憶装置。 - 請求項15記載の不揮発性記憶装置において、前記スリットの幅は100nm以下であることを特徴とする不揮発性記憶装置。

- 請求項15記載の不揮発性記憶装置において、前記記憶素子と前記電極との間にバリア層が形成されていることを特徴とする不揮発性記憶装置。

- 半導体基板上に、第1方向に沿って延在する第1ワード線および第2ワード線と、前記第1方向に沿って延在するソース線と、前記第1方向と直交する第2方向に沿って延在するビット線と、第1アクセストランジスタおよび抵抗値の差によって記憶情報を判断する第1記憶素子から構成される第1メモリセルと、第2アクセストランジスタおよび抵抗値の差によって記憶情報を判断する第2記憶素子とから構成される第2メモリセルとを含み、

前記第1アクセストランジスタのソース領域と前記第2アクセストランジスタのソース領域とは共有され、

前記第1アクセストランジスタのゲート電極は前記第1ワード線の一部により構成され、前記第2アクセストランジスタのゲート電極は前記第2ワード線の一部により構成され、前記第1アクセストランジスタと前記第2アクセストランジスタとが共有するソース領域は前記ソース線の一部によって構成され、前記第1メモリセルのドレイン領域と前記ビット線との間に前記第1記憶素子が接続され、前記第2メモリセルのドレイン領域と前記ビット線との間に前記第2記憶素子が接続されていることを特徴とする不揮発性記憶装置。 - 請求項18記載の不揮発性記憶装置において、前記第1および第2アクセストランジスタを覆う層間絶縁膜と、前記第1アクセストランジスタのドレイン領域に達して前記層間絶縁膜に形成された第1接続孔と、前記第1接続孔の内部に埋め込まれた第1プラグ電極と、前記第2アクセストランジスタのドレイン領域に達して前記層間絶縁膜に形成された第2接続孔と、前記第2接続孔の内部に埋め込まれた第2プラグ電極と、前記第1プラグ電極と前記第2プラグ電極とに電気的に接続し、前記第2方向に沿って形成された第1電極と、前記第1電極に電気的に接続する第2電極と、前記第1プラグ電極と前記第2電極との間に位置する前記第1電極に前記第1方向に沿って形成された第1スリットと、前記第2プラグ電極と前記第2電極との間に位置する前記第1電極に前記第1方向に沿って形成された第2スリットと、前記第1スリットを跨いで形成された前記第1記憶素子と、前記第2スリットを跨いで形成された前記第2記憶素子とを有することを特徴とする不揮発性記憶装置。

- 請求項19記載の不揮発性記憶装置において、前記第1および第2スリットの幅は100nm以下であることを特徴とする不揮発性記憶装置。

- 請求項19記載の不揮発性記憶装置において、前記第1記憶素子と前記第1電極との間および前記第2記憶素子と前記第1電極との間にバリア層が形成されていることを特徴とする不揮発性記憶装置。

- 請求項19記載の不揮発性記憶装置において、前記第1および第2記憶素子は、NiO、CuO2、TiO2、HfO2、ZrO2、Al2O3、GeSbTe、SbSe、GeTe、Nが添加されたGeSbTe、InがドープされたGeSbTe、SrZrO3、SrTiO3またはMgOにより構成されることを特徴とする不揮発性記憶装置。

- 請求項19記載の不揮発性記憶装置において、前記第1電極は、Ni、W、Cu、TiN、NiPt、Co、PyまたはFeCoにより構成されることを特徴とする不揮発性記憶装置。

- 請求項21記載の不揮発性記憶装置において、前記バリア層は、Cu、CuO、TaO、CrO、MgOまたはAl2O3により構成されることを特徴とする不揮発性記憶装置。

- 請求項19記載の不揮発性記憶装置において、前記第1電極はローカル配線により構成され、前記第2電極は第1層目の配線により構成され、前記第1層目の配線にプラグ電極を介して第2層目の配線が接続され、前記第2層目の配線により前記ビット線は構成されることを特徴とする不揮発性記憶装置。

- 請求項19記載の不揮発性記憶装置において、前記第1電極は第1層目の配線により構成され、前記第1層目の配線にプラグ電極を介して第2層目の配線が接続され、前記第2層目の配線により前記ビット線は構成されることを特徴とする不揮発性記憶装置。

- 以下の製造工程を含むことを特徴とする不揮発性記憶装置の製造方法:

(a)半導体基板の主面上にゲート絶縁膜、ゲート電極および一対のソース・ドレイン領域からなるアクセストランジスタを形成する工程、

(b)前記アクセストランジスタを覆う層間絶縁膜を形成し、前記一対のソース・ドレイン領域にそれぞれ達する2つの接続孔を前記層間絶縁膜に形成する工程、

(c)2つの前記接続孔の内部にそれぞれ導体膜を埋め込み、2つのプラグ電極を形成する工程、

(d)前記半導体基板の主面上に導体膜を堆積し、前記導体膜を加工して、2つの前記プラグ電極に接続し、第1方向に沿ってスリットが形成された電極を形成する工程、

(e)前記半導体基板の主面上にバリア層および記憶素子用材料を順次堆積し、前記記憶素子用材料および前記バリア層を順次加工して、前記スリットを跨ぐ記憶素子を形成する工程。 - 以下の製造工程を含むことを特徴とする不揮発性記憶装置の製造方法:

(a)半導体基板の主面上にゲート絶縁膜、ゲート電極および一対のソース・ドレイン領域からなるアクセストランジスタを形成する工程、

(b)前記アクセストランジスタを覆う層間絶縁膜を形成し、前記一対のソース・ドレイン領域にそれぞれ達する2つの接続孔を前記層間絶縁膜に形成する工程、

(c)2つの前記接続孔の内部にそれぞれ導体膜を埋め込み、2つのプラグ電極を形成する工程、

(d)前記半導体基板の主面上に導体膜を堆積し、前記導体膜を加工して、2つの前記プラグ電極に接続し、第1方向に沿ってスリットが形成された第1層目の配線を形成する工程、

(e)前記第1層目の配線の表面を酸化処理した後、前記半導体基板の主面上に記憶素子用材料を順次堆積し、前記記憶素子用材料を加工して、前記スリットを跨ぐ記憶素子を形成する工程。 - 請求項27または28記載の不揮発性記憶装置の製造方法において、前記スリットの幅は100nm以下であることを特徴とする不揮発性記憶装置の製造方法。

- 請求項27または28記載の不揮発性記憶装置の製造方法において、前記記憶素子は、NiO、CuO2、TiO2、HfO2、ZrO2、Al2O3、GeSbTe、SbSe、GeTe、Nが添加されたGeSbTe、InがドープされたGeSbTe、SrZrO3、SrTiO3またはMgOにより構成されることを特徴とする不揮発性記憶装置の製造方法。

- 請求項27記載の不揮発性記憶装置の製造方法において、前記バリア層は、Cu、CuO、TaO、CrO、MgOまたはAl2O3により構成されることを特徴とする不揮発性記憶装置の製造方法。

- 請求項27記載の不揮発性記憶装置の製造方法において、前記電極はローカル配線または第1層目の配線により構成されることを特徴とする不揮発性記憶装置の製造方法。

- 請求項32記載の不揮発性記憶装置の製造方法において、前記ローカル配線は、Ni、W、Cu、TiN、NiPt、Co、PyまたはFeCoにより構成されることを特徴とする不揮発性記憶装置の製造方法。

- 請求項28または32記載の不揮発性記憶装置の製造方法において、前記第1層目の配線は、Cuにより構成されることを特徴とする不揮発性記憶装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008190174A JP5378722B2 (ja) | 2008-07-23 | 2008-07-23 | 不揮発性記憶装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008190174A JP5378722B2 (ja) | 2008-07-23 | 2008-07-23 | 不揮発性記憶装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010027984A true JP2010027984A (ja) | 2010-02-04 |

| JP5378722B2 JP5378722B2 (ja) | 2013-12-25 |

Family

ID=41733498

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008190174A Expired - Fee Related JP5378722B2 (ja) | 2008-07-23 | 2008-07-23 | 不揮発性記憶装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5378722B2 (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2010090128A1 (ja) * | 2009-02-09 | 2010-08-12 | 独立行政法人産業技術総合研究所 | 固体メモリ |

| JP2011204296A (ja) * | 2010-03-24 | 2011-10-13 | Toshiba Corp | 半導体記憶装置 |

| JP2012204404A (ja) * | 2011-03-23 | 2012-10-22 | Toshiba Corp | 抵抗変化型不揮発性半導体記憶装置 |

| JP2013161978A (ja) * | 2012-02-06 | 2013-08-19 | National Institute Of Advanced Industrial & Technology | 半導体記憶装置およびその製造方法 |

| US9947685B2 (en) | 2016-03-16 | 2018-04-17 | Toshiba Memory Corporation | 3D non-volatile memory array utilizing metal ion source |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004213744A (ja) * | 2002-12-27 | 2004-07-29 | Tdk Corp | メモリ装置 |

| JP2004272975A (ja) * | 2003-03-06 | 2004-09-30 | Sharp Corp | 不揮発性半導体記憶装置 |

| JP2006019687A (ja) * | 2004-06-30 | 2006-01-19 | Hynix Semiconductor Inc | 相変化記憶素子及びその製造方法 |

| WO2006079952A1 (en) * | 2005-01-25 | 2006-08-03 | Nxp B.V. | Fabrication of phase-change resistor using a backend process |

| WO2007046144A1 (ja) * | 2005-10-19 | 2007-04-26 | Fujitsu Limited | 抵抗記憶素子及びその製造方法、並びに不揮発性半導体記憶装置 |

| JP2008021750A (ja) * | 2006-07-11 | 2008-01-31 | Matsushita Electric Ind Co Ltd | 抵抗変化素子およびその製造方法、ならびにそれを用いた抵抗変化型メモリ |

| JP2008060569A (ja) * | 2006-08-29 | 2008-03-13 | Internatl Business Mach Corp <Ibm> | シリコン・オン・インシュレータ基板上に形成された薄膜相変化メモリ・セル、その形成方法、および1つ以上のメモリ・セルを含む集積回路 |

| JP2008091682A (ja) * | 2006-10-03 | 2008-04-17 | Gunma Univ | 多値記録相変化メモリ素子、多値記録相変化チャンネルトランジスタおよびメモリセルアレイ |

| WO2008068867A1 (ja) * | 2006-12-07 | 2008-06-12 | Renesas Technology Corp. | 半導体記憶装置 |

| JP2008251059A (ja) * | 2007-03-29 | 2008-10-16 | Toshiba Corp | 不揮発性半導体記憶装置およびそのデータ消去方法 |

-

2008

- 2008-07-23 JP JP2008190174A patent/JP5378722B2/ja not_active Expired - Fee Related

Patent Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004213744A (ja) * | 2002-12-27 | 2004-07-29 | Tdk Corp | メモリ装置 |

| JP2004272975A (ja) * | 2003-03-06 | 2004-09-30 | Sharp Corp | 不揮発性半導体記憶装置 |

| JP2006019687A (ja) * | 2004-06-30 | 2006-01-19 | Hynix Semiconductor Inc | 相変化記憶素子及びその製造方法 |

| WO2006079952A1 (en) * | 2005-01-25 | 2006-08-03 | Nxp B.V. | Fabrication of phase-change resistor using a backend process |

| JP2008529269A (ja) * | 2005-01-25 | 2008-07-31 | エヌエックスピー ビー ヴィ | バックエンドプロセスを使用する相変化抵抗体の製造 |

| WO2007046144A1 (ja) * | 2005-10-19 | 2007-04-26 | Fujitsu Limited | 抵抗記憶素子及びその製造方法、並びに不揮発性半導体記憶装置 |

| JP2008021750A (ja) * | 2006-07-11 | 2008-01-31 | Matsushita Electric Ind Co Ltd | 抵抗変化素子およびその製造方法、ならびにそれを用いた抵抗変化型メモリ |

| JP2008060569A (ja) * | 2006-08-29 | 2008-03-13 | Internatl Business Mach Corp <Ibm> | シリコン・オン・インシュレータ基板上に形成された薄膜相変化メモリ・セル、その形成方法、および1つ以上のメモリ・セルを含む集積回路 |

| JP2008091682A (ja) * | 2006-10-03 | 2008-04-17 | Gunma Univ | 多値記録相変化メモリ素子、多値記録相変化チャンネルトランジスタおよびメモリセルアレイ |

| WO2008068867A1 (ja) * | 2006-12-07 | 2008-06-12 | Renesas Technology Corp. | 半導体記憶装置 |

| JP2008251059A (ja) * | 2007-03-29 | 2008-10-16 | Toshiba Corp | 不揮発性半導体記憶装置およびそのデータ消去方法 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2010090128A1 (ja) * | 2009-02-09 | 2010-08-12 | 独立行政法人産業技術総合研究所 | 固体メモリ |

| JP2010183017A (ja) * | 2009-02-09 | 2010-08-19 | National Institute Of Advanced Industrial Science & Technology | 固体メモリ |

| JP2011204296A (ja) * | 2010-03-24 | 2011-10-13 | Toshiba Corp | 半導体記憶装置 |

| JP2012204404A (ja) * | 2011-03-23 | 2012-10-22 | Toshiba Corp | 抵抗変化型不揮発性半導体記憶装置 |

| US9025369B2 (en) | 2011-03-23 | 2015-05-05 | Kabushiki Kaisha Toshiba | Resistance change nonvolatile semiconductor memory device |

| JP2013161978A (ja) * | 2012-02-06 | 2013-08-19 | National Institute Of Advanced Industrial & Technology | 半導体記憶装置およびその製造方法 |

| US9947685B2 (en) | 2016-03-16 | 2018-04-17 | Toshiba Memory Corporation | 3D non-volatile memory array utilizing metal ion source |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5378722B2 (ja) | 2013-12-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11825653B2 (en) | Semiconductor device and array layout thereof and package structure comprising the same | |

| TWI639162B (zh) | 包括多個選擇閘及不同偏壓條件的記憶體裝置 | |

| KR102551350B1 (ko) | 수직형 메모리 소자를 구비한 집적회로 소자 및 그 제조 방법 | |

| JP5661992B2 (ja) | 積層されたnand型抵抗性メモリセルストリングを含む不揮発性メモリ素子及びその製造方法 | |

| JP6645940B2 (ja) | 不揮発性半導体記憶装置 | |

| JP2010027835A (ja) | 不揮発性記憶装置およびその製造方法 | |

| JP4345676B2 (ja) | 半導体記憶装置 | |

| US20080149913A1 (en) | Semiconductor memory device and method of manufacturing the same | |

| JP5284044B2 (ja) | 不揮発性半導体記憶装置 | |

| KR102902380B1 (ko) | 반도체 메모리 장치 | |

| US9087715B2 (en) | Nonvolatile semiconductor memory device and method of manufacturing the same | |

| US10141321B2 (en) | Method of forming flash memory with separate wordline and erase gates | |

| WO2000070683A1 (en) | Semiconductor memory | |

| KR20090120414A (ko) | 불휘발성 기억 장치 및 그 제조 방법 | |

| JP2002124585A (ja) | 不揮発性半導体記憶装置およびその製造方法 | |

| JP2010067645A (ja) | 半導体装置およびその製造方法 | |

| JP2006216957A (ja) | 垂直なゲート電極のトランジスタを備える半導体装置及びその製造方法 | |

| US20230187548A1 (en) | Semiconductor memory device | |

| JP5378722B2 (ja) | 不揮発性記憶装置およびその製造方法 | |

| JP3941517B2 (ja) | 半導体装置およびその製造方法 | |

| US9741768B1 (en) | Controlling memory cell size in three dimensional nonvolatile memory | |

| JP2007305710A (ja) | 半導体記憶装置およびその製造方法 | |

| JP5801341B2 (ja) | 半導体メモリ | |

| US20230115434A1 (en) | Semiconductor memory device | |

| JP2008294111A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110622 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130426 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130521 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130710 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130903 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130926 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |