JP2010025688A - マイクロチップの製造方法 - Google Patents

マイクロチップの製造方法 Download PDFInfo

- Publication number

- JP2010025688A JP2010025688A JP2008185972A JP2008185972A JP2010025688A JP 2010025688 A JP2010025688 A JP 2010025688A JP 2008185972 A JP2008185972 A JP 2008185972A JP 2008185972 A JP2008185972 A JP 2008185972A JP 2010025688 A JP2010025688 A JP 2010025688A

- Authority

- JP

- Japan

- Prior art keywords

- silicon

- glass substrate

- substrate

- base material

- flow path

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Automatic Analysis And Handling Materials Therefor (AREA)

- Micromachines (AREA)

- Apparatus Associated With Microorganisms And Enzymes (AREA)

- Joining Of Glass To Other Materials (AREA)

- Physical Or Chemical Processes And Apparatus (AREA)

Abstract

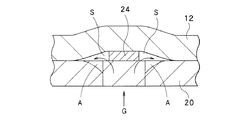

【解決手段】貫通孔用ガラス基材11と、主ガラス基材12と、流路21を含むマイクロチップ10を製造する方法において、まず主ガラス基材12およびシリコン含有基材20を準備し、このうちシリコン含有基材20に電極24を設けるとともに、主ガラス基材12に凹部25を形成する。次に主ガラス基材12にシリコン含有基材20を接合し、シリコン含有基材20に設けられた電極24を主ガラス基材12の凹部25内に収容する。次に主ガラス基材12上のシリコン含有基材20に対して研磨を行って、シリコン含有基材20を所定厚に形成し、シリコン含有基材20にエッチングにより流路21を形成する。その後、シリコン含有基材20に貫通孔用ガラス基材11を接合する。

【選択図】図3

Description

以下、図面を参照して本発明の第1の実施の形態について説明する。

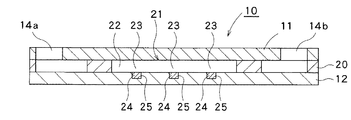

図1は、本実施の形態によるマイクロチップの製造方法により製造されたマイクロチップを示す平面図であり、図2は、本実施の形態によるマイクロチップの製造方法により製造されたマイクロチップを示す断面図(図1のII−II線断面図)である。図3(a)〜(g)は、本実施の形態によるマイクロチップの製造方法を示す概略図であり、図10は、ドライエッチング方法を用いてシリコン含有基材に流路を形成する工程の比較例を示す図である。

まず、図1および図2により本実施の形態によるマイクロチップの概要について説明する。

次に、図3(a)〜(g)により本実施の形態によるマイクロチップの製造方法について説明する。

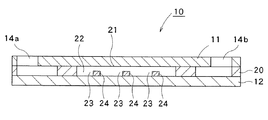

次に、本発明によるマイクロチップの製造方法の第2の実施の形態について図1、図4、および図5(a)〜(g)を参照して説明する。このうち図4は、本実施の形態によるマイクロチップの製造方法により製造されたマイクロチップを示す断面図であり、図5(a)〜(g)は、本実施の形態によるマイクロチップの製造方法を示す概略図である。図1、図4、および図5(a)〜(g)に示す第2の実施の形態は、シリコン含有基材20に凹部26を設けるとともに、シリコン含有基材20の凹部26内に電極24を収容した点が異なるものであり、他の構成は上述した第1の実施の形態と略同一である。図1、図4、および図5(a)〜(g)において、上述した第1の実施の形態と同一部分には同一の符号を付して詳細な説明は省略する。

図1および図4に示すように、本実施の形態によるマイクロチップ(流路デバイス)10は、貫通孔用ガラス基材11と、主ガラス基材12と、貫通孔用ガラス基材11および主ガラス基材12の間に介在され、流路21を含むシリコン含有基材20とを含んでいる。

次に、図5(a)〜(g)により本実施の形態によるマイクロチップの製造方法の概略について説明する。

次に、本発明によるマイクロチップの製造方法の第3の実施の形態について図1、図2、図6(a)〜(g)、および図7を参照して説明する。このうち図6(a)〜(g)は、本実施の形態によるマイクロチップの製造方法を示す概略図であり、図7は、ドライエッチング方法を用いてシリコン含有基材に流路を形成する工程を説明する図である。図1、図2、図6(a)〜(g)、および図7に示す第3の実施の形態は、貫通孔用ガラス基材11および主ガラス基材12をシリコン含有基材20に接合する順番などが異なるものであり、他の構成は上述した第1の実施の形態と略同一である。図1、図2、図6(a)〜(g)、および図7において、上述した第1の実施の形態および第2の実施の形態と同一部分には同一の符号を付して詳細な説明は省略する。

図1および図2に示すように、本実施の形態によるマイクロチップ(流路デバイス)10は、貫通孔用ガラス基材11と、主ガラス基材12と、貫通孔用ガラス基材11および主ガラス基材12の間に介在され、流路21を含むシリコン含有基材20とを含んでいる。このマイクロチップ10の構成は、上述した第1の実施の形態によるマイクロチップ10の構成と同一であるので、詳細な説明は省略する。

次に、図6(a)〜(g)および図7により本実施の形態によるマイクロチップの製造方法の概略について説明する。

次に、本発明によるマイクロチップの製造方法の第4の実施の形態について図1、図4、および図8(a)〜(g)を参照して説明する。このうち図8(a)〜(g)は、本実施の形態によるマイクロチップの製造方法を示す概略図である。図1、図4、および図8(a)〜(g)に示す第4の実施の形態は、シリコン含有基材20に凹部26を設けるとともに、シリコン含有基材20の凹部26内に電極24を収容した点が異なるものであり、他の構成は上述した第3の実施の形態と略同一である。図1、図4、および図8(a)〜(g)において、上述した第1の実施の形態乃至第3の実施の形態と同一部分には同一の符号を付して詳細な説明は省略する。

図1および図4に示すように、本実施の形態によるマイクロチップ(流路デバイス)10は、貫通孔用ガラス基材11と、主ガラス基材12と、貫通孔用ガラス基材11および主ガラス基材12の間に介在され、流路21を含むシリコン含有基材20とを含んでいる。このマイクロチップ10の構成は、上述した第2の実施の形態によるマイクロチップ10の構成と同一であるので、詳細な説明は省略する。

次に、図8(a)〜(g)により本実施の形態によるマイクロチップの製造方法の概略について説明する。

次に、本発明によるマイクロチップの製造方法の第5の実施の形態について図9(a)〜(c)を参照して説明する。図9(a)〜(c)は、本実施の形態によるマイクロチップの製造方法を示す概略図である。図9(a)〜(c)に示す第5の実施の形態は、シリコン含有基材20の構成、およびシリコン含有基材20を所定厚に形成する工程が異なるものであり、他の構成は上述した第1の実施の形態乃至第4の実施の形態と同一である。図9(a)〜(c)において、上述した第1の実施の形態乃至第4の実施の形態と同一部分には同一の符号を付して詳細な説明は省略する。

なお、上述した第1の実施の形態乃至第5の実施の形態の各々において、シリコン含有基材20に電極24を設ける例を示してきた。しかしながら、これに限らず、電極24は、第1ガラス基材となる貫通孔用ガラス基材11または主ガラス基材12に設けられてもよい。例えば貫通孔用ガラス基材11(または主ガラス基材12)に電極24を設けるとともに、シリコン含有基材20に前記電極24に対応する凹部25を形成し、電極24が設けられた貫通孔用ガラス基材11(主ガラス基材12)とシリコン含有基材20とを接合して、電極24を凹部25内に収容しても良い。あるいは、貫通孔用ガラス基材11(または主ガラス基材12)に凹部26を設けるとともに、この凹部26に電極24を収容し、電極24が設けられた貫通孔用ガラス基材11(主ガラス基材12)とシリコン含有基材20とを接合しても良い。

11 貫通孔用ガラス基材

12 主ガラス基材

14a 流入孔

14b 流出孔

15 保護層

20 シリコン含有基材

20A 第1のシリコン層

20B 酸化シリコン層

20C 第2のシリコン層

21 流路

22 主流路

23 トラップ

24 電極

25 凹部

26 凹部

Claims (6)

- 第1ガラス基材と、第2ガラス基材と、第1ガラス基材および第2ガラス基材の間に介在され、流路を含むシリコン含有基材とを含むマイクロチップの製造方法において、

第1ガラス基材およびシリコン含有基材を準備する工程と、

シリコン含有基材および第1ガラス基材の一方に電極を設けるとともに、他方に前記電極に対応する凹部を形成する工程と、

第1ガラス基材にシリコン含有基材を接合して、電極をこの電極に対応する凹部内に収容する工程と、

第1ガラス基材上のシリコン含有基材に対して研磨を行って、シリコン含有基材を所定厚に形成する工程と、

所定厚のシリコン含有基材に対してエッチングにより流路を形成する工程と、

流路が形成されたシリコン含有基材に第2ガラス基材を接合する工程とを備えたことを特徴とするマイクロチップの製造方法。 - 第1ガラス基材と、第2ガラス基材と、第1ガラス基材および第2ガラス基材の間に介在され、流路を含むシリコン含有基材とを含むマイクロチップの製造方法において、

第1ガラス基材およびシリコン含有基材を準備する工程と、

シリコン含有基材および第1ガラス基材の一方に凹部を設けるとともに、当該凹部内に電極を収容する工程と、

第1ガラス基材にシリコン含有基材を接合する工程と、

第1ガラス基材上のシリコン含有基材に対して研磨を行って、シリコン含有基材を所定厚に形成する工程と、

所定厚のシリコン含有基材に対してエッチングにより流路を形成する工程と、

流路が形成されたシリコン含有基材に第2ガラス基材を接合する工程とを備えたことを特徴とするマイクロチップの製造方法。 - 第2ガラス基材は貫通孔用ガラス基材となっており、流路が形成されたシリコン含有基材に第2ガラス基材を接合する工程の前に、第2ガラス基材に予めシリコン含有基材の流路に連通する流入孔および流出孔となる貫通孔を設けておくことを特徴とする請求項1または2記載のマイクロチップの製造方法。

- 第1ガラス基材は貫通孔用ガラス基材となっており、第1ガラス基材にシリコン含有基材を接合する工程の前に、第1ガラス基材に予めシリコン含有基材の流路に連通する流入孔および流出孔となる貫通孔を設けておくことを特徴とする請求項1または2記載のマイクロチップの製造方法。

- エッチングにより流路を形成する工程の前に、第1ガラス基材のうちシリコン含有基材が設けられた面と反対側の面に、少なくとも第1ガラス基材に設けられた貫通孔を覆う保護層を形成する工程が設けられ、

エッチングにより流路を形成する工程の後に、第1ガラス基材を覆う保護層を剥離する工程が設けられていることを特徴とする請求項4記載のマイクロチップの製造方法。 - シリコン含有基材は、第1のシリコン層と、前記所定厚を有する第2のシリコン層と、第1のシリコン層および第2のシリコン層の間に介在された酸化シリコン層とからなり、

第1ガラス基材にシリコン含有基材を接合する工程において、シリコン含有基材のうち第2のシリコン層が第1ガラス基材に接合され、

シリコン含有基材を所定厚に形成する工程は、

シリコン含有基材のうち、第1のシリコン層を除去する工程と、

シリコン含有基材のうち、酸化シリコン層を除去するとともに、前記所定厚を有する第2のシリコン層を残す工程とを有することを特徴とする請求項1乃至5のいずれか一項記載のマイクロチップの製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008185972A JP5354324B2 (ja) | 2008-07-17 | 2008-07-17 | マイクロチップの製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008185972A JP5354324B2 (ja) | 2008-07-17 | 2008-07-17 | マイクロチップの製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010025688A true JP2010025688A (ja) | 2010-02-04 |

| JP5354324B2 JP5354324B2 (ja) | 2013-11-27 |

Family

ID=41731672

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008185972A Expired - Fee Related JP5354324B2 (ja) | 2008-07-17 | 2008-07-17 | マイクロチップの製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5354324B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011242240A (ja) * | 2010-05-18 | 2011-12-01 | Dainippon Printing Co Ltd | マイクロチップ及びその製造方法 |

| KR20200043846A (ko) * | 2018-10-18 | 2020-04-28 | 연세대학교 산학협력단 | Mems 기반의 응축 입자 계수기 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0369228U (ja) * | 1989-11-09 | 1991-07-09 | ||

| JPH10318982A (ja) * | 1997-05-22 | 1998-12-04 | Olympus Optical Co Ltd | 電気泳動装置 |

| JP2001208672A (ja) * | 1999-11-16 | 2001-08-03 | Kanagawa Acad Of Sci & Technol | プローブ及びプローブの製造方法、プローブアレイ及びプローブアレイの製造方法 |

| JP2004003950A (ja) * | 2002-03-25 | 2004-01-08 | Seiko Epson Corp | インクジェットヘッド及びプローブアレイの製造方法 |

| JP2007238379A (ja) * | 2006-03-09 | 2007-09-20 | Casio Comput Co Ltd | 接合基板及び接合方法 |

| WO2007107901A2 (en) * | 2006-03-20 | 2007-09-27 | Koninklijke Philips Electronics N.V. | A system-in-package platform for electronic-microfluidic devices |

-

2008

- 2008-07-17 JP JP2008185972A patent/JP5354324B2/ja not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0369228U (ja) * | 1989-11-09 | 1991-07-09 | ||

| JPH10318982A (ja) * | 1997-05-22 | 1998-12-04 | Olympus Optical Co Ltd | 電気泳動装置 |

| JP2001208672A (ja) * | 1999-11-16 | 2001-08-03 | Kanagawa Acad Of Sci & Technol | プローブ及びプローブの製造方法、プローブアレイ及びプローブアレイの製造方法 |

| JP2004003950A (ja) * | 2002-03-25 | 2004-01-08 | Seiko Epson Corp | インクジェットヘッド及びプローブアレイの製造方法 |

| JP2007238379A (ja) * | 2006-03-09 | 2007-09-20 | Casio Comput Co Ltd | 接合基板及び接合方法 |

| WO2007107901A2 (en) * | 2006-03-20 | 2007-09-27 | Koninklijke Philips Electronics N.V. | A system-in-package platform for electronic-microfluidic devices |

Non-Patent Citations (1)

| Title |

|---|

| JPN6012060599; Wei-Heong Tan,Shoji Takeuchi: 'A Trap-and-release integrated microfluidic system for dynamic microarray applications' Proceedings of the National Academy of Sciences of the United States of America vol.104,no.4, 20070123, pp.1146-1151 * |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011242240A (ja) * | 2010-05-18 | 2011-12-01 | Dainippon Printing Co Ltd | マイクロチップ及びその製造方法 |

| KR20200043846A (ko) * | 2018-10-18 | 2020-04-28 | 연세대학교 산학협력단 | Mems 기반의 응축 입자 계수기 |

| KR102111715B1 (ko) | 2018-10-18 | 2020-05-15 | 연세대학교 산학협력단 | Mems 기반의 응축 입자 계수기 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5354324B2 (ja) | 2013-11-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20230375501A1 (en) | Method of making biochip having a channel | |

| US10145847B2 (en) | Method for forming biochips and biochips with non-organic landings for improved thermal budget | |

| US9616617B2 (en) | Scalable biochip and method for making | |

| Schlautmann et al. | Fabrication of a microfluidic chip by UV bonding at room temperature for integration of temperature-sensitive layers | |

| JP4480939B2 (ja) | ガラス系材料からなるフラット基板を構造化する方法 | |

| CN107118938B (zh) | 流体增强介电泳单细胞排列与控制芯片及其制作方法 | |

| Vulto et al. | A full-wafer fabrication process for glass microfluidic chips with integrated electroplated electrodes by direct bonding of dry film resist | |

| US10538731B2 (en) | Device for manipulating biological cells using a vibrating support | |

| JP4383446B2 (ja) | 微細構造化基板を接着する方法 | |

| Thompson et al. | Polymeric microbead arrays for microfluidic applications | |

| JP4432778B2 (ja) | マイクロチップおよび質量分析システム | |

| JP2004180594A (ja) | 細胞培養装置 | |

| KR100763907B1 (ko) | 미세유동 장치의 제조방법 및 그에 의하여 제조되는미세유동 장치 | |

| JP5354324B2 (ja) | マイクロチップの製造方法 | |

| CN108080043B (zh) | 真空负压进样的多通道微流控芯片装置及制备方法与应用 | |

| JP5272552B2 (ja) | マイクロチップの製造方法 | |

| CN101516513A (zh) | 双面流体构件 | |

| US8696881B2 (en) | Patch-clamp providing on-chip thermal gradient | |

| US11607683B2 (en) | Microfluidic device and method for manufacturing a microfluidic device | |

| CN101855018A (zh) | 用于热隔离检定卡的腔室的设备及方法 | |

| WO2006085604A1 (ja) | 分析用の蓋付きマイクロチップ、該蓋付きマイクロチップのサンプル処理方法、該蓋付きマイクロチップの自動サンプル処理方法、該処理方法に基づく、自動サンプル処理装置、ならびに、該自動サンプル処理方法を応用する物質の分析装置 | |

| CN102600917B (zh) | 具有散热能力的集成磁泳分离芯片及其制备方法 | |

| US20180236444A1 (en) | Process for producing a buried microfluidic channel with integrated heater | |

| KR20070067442A (ko) | 기판으로부터 포토레지스트 막을 분리하는 방법 및 상기포토레지스트 막을 이차 기판과 접합하는 방법 | |

| US20090107844A1 (en) | Glass electrophoresis microchip and method of manufacturing the same by mems fabrication |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110517 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120823 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120828 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121025 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130412 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130703 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130710 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130802 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130815 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5354324 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D02 |

|

| LAPS | Cancellation because of no payment of annual fees |