JP2010010478A - 光電変換装置、光電変換装置の製造方法及び撮像装置 - Google Patents

光電変換装置、光電変換装置の製造方法及び撮像装置 Download PDFInfo

- Publication number

- JP2010010478A JP2010010478A JP2008169181A JP2008169181A JP2010010478A JP 2010010478 A JP2010010478 A JP 2010010478A JP 2008169181 A JP2008169181 A JP 2008169181A JP 2008169181 A JP2008169181 A JP 2008169181A JP 2010010478 A JP2010010478 A JP 2010010478A

- Authority

- JP

- Japan

- Prior art keywords

- photoelectric conversion

- forming

- conversion device

- layer

- upper electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K39/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic radiation-sensitive element covered by group H10K30/00

- H10K39/30—Devices controlled by radiation

- H10K39/32—Organic image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/18—Complementary metal-oxide-semiconductor [CMOS] image sensors; Photodiode array image sensors

- H10F39/182—Colour image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/806—Optical elements or arrangements associated with the image sensors

- H10F39/8063—Microlenses

Landscapes

- Solid State Image Pick-Up Elements (AREA)

- Light Receiving Elements (AREA)

Abstract

【課題】有機材料を含む光電変換層が劣化することを防止して、素子性能が低下することを防止することができる光電変換装置、光電変換装置の製造方法及び撮像装置を提供する。

【解決手段】基板の上方に形成された下部電極12と、下部電極12の上方に形成された光電変換層13と、光電変換層13の上方に形成された上部電極14とを含む光電変換素子1を少なくとも1つ有する画素が複数配列された光電変換装置であって、隣り合う画素同士の間に形成され、上部電極14と電気的に接続された導電性の隔壁15と、上部電極14上に設けられた透明絶縁膜16とを備え、画素が隔壁15と透明絶縁膜16とによって封止されている。

【選択図】図1

【解決手段】基板の上方に形成された下部電極12と、下部電極12の上方に形成された光電変換層13と、光電変換層13の上方に形成された上部電極14とを含む光電変換素子1を少なくとも1つ有する画素が複数配列された光電変換装置であって、隣り合う画素同士の間に形成され、上部電極14と電気的に接続された導電性の隔壁15と、上部電極14上に設けられた透明絶縁膜16とを備え、画素が隔壁15と透明絶縁膜16とによって封止されている。

【選択図】図1

Description

本発明は、光電変換装置、光電変換装置の製造方法及び撮像装置に関する。

デジタルスチルカメラやデジタルビデオカメラ等に利用されているイメージセンサとしては、Si半導体基板などにホトダイオードを含む画素を配列し、各画素のホトダイオードで生じた光電子に対応した信号電荷をCCD型やCMOS型駆動回路で読出す固体撮像装置(いわゆるCCDセンサやCMOSセンサ)が広く知られている。

これら固体撮像装置は、半導体基板上にホトダイオードだけでなく、信号電荷蓄積部位・電荷転送部位・信号読出部位やそれらを接続する配線などが形成されている。そのために画素微細化が進展するにつれ一画素に占める回路領域が相対的に大きくなりホトダイオードの受光面積が小さくなるという「開口率の低下」が問題となっている。開口率の低下はそのまま感度の低下につながる。

開口率の低下を抑制するため各画素上にマイクロレンズなどを形成して集光することで実質的な開口率を増加させることが必須となる。しかし、製造工程の増加や光学設計の複雑化などコストの上昇が避けられない上に感度向上の改善は限定的である。

そこで、各回路と配線を形成した半導体基板上方に光電変換層を積層し開口率を向上させるという「積層型固体撮像装置」が提案されている。例えば、半導体基板上に積層された下部電極と、下部電極上に積層された光電変換層と、光電変換層上に積層された上部電極とを含む光電変換素子を半導体基板に対して平行な面に多数配列した構成になる。光電変換素子の、下部電極と上部電極との間にバイアス電圧を印加することで、光電変換層内で発生した電荷が下部電極と上部電極とに移動し、いずれかの電極に移動した電荷に応じた信号が、半導体基板内に設けられたCCD型やCMOS型回路で読出される。ここで、光電変換層とは、入射した特定の波長の光を吸収し、吸収した光量に応じた電荷(電子および正孔)を発生する層である。

これら固体撮像装置は、半導体基板上にホトダイオードだけでなく、信号電荷蓄積部位・電荷転送部位・信号読出部位やそれらを接続する配線などが形成されている。そのために画素微細化が進展するにつれ一画素に占める回路領域が相対的に大きくなりホトダイオードの受光面積が小さくなるという「開口率の低下」が問題となっている。開口率の低下はそのまま感度の低下につながる。

開口率の低下を抑制するため各画素上にマイクロレンズなどを形成して集光することで実質的な開口率を増加させることが必須となる。しかし、製造工程の増加や光学設計の複雑化などコストの上昇が避けられない上に感度向上の改善は限定的である。

そこで、各回路と配線を形成した半導体基板上方に光電変換層を積層し開口率を向上させるという「積層型固体撮像装置」が提案されている。例えば、半導体基板上に積層された下部電極と、下部電極上に積層された光電変換層と、光電変換層上に積層された上部電極とを含む光電変換素子を半導体基板に対して平行な面に多数配列した構成になる。光電変換素子の、下部電極と上部電極との間にバイアス電圧を印加することで、光電変換層内で発生した電荷が下部電極と上部電極とに移動し、いずれかの電極に移動した電荷に応じた信号が、半導体基板内に設けられたCCD型やCMOS型回路で読出される。ここで、光電変換層とは、入射した特定の波長の光を吸収し、吸収した光量に応じた電荷(電子および正孔)を発生する層である。

また、光電変換層に色再現性に優れる有機材料を用いた構成の光電変換装置の実用化が進められている。従来、有機材料を含む層を備えたセンサとしては、例えば下記特許文献に示すものがある。

特許文献1には、導電性電極間に有機半導体の薄層が挟持された構成のフルカラーの画像センサが記載されている。

特許文献2には、電極間に、有機材料を含む受光部が設けられたセンサが記載されている。

ところで、カラーイメージセンサとして用いる光電変換装置は、少なくとも1つの光電変換素子を含む画素が半導体基板上に2次元配列で複数形成され、各画素がR(赤),G(緑),B(青)の波長の光のいずれかを検出する光電変換層を含み、かつ、RGBの各画素が2次元上に所定のカラーパターンで配列される構成である。

このような構成の光電変換装置は、半導体基板上に光電変換層を形成する際に半導体微細加工技術(例えば、光リソグラフィ、ナノインプリント、レーザ描画や電子線描画による熱リソグラフィ等)を利用するが、製造時及び製造後に光電変換層に含まれる有機材料が大気中で顕著に劣化してしまうことに起因して、素子性能が低下することが懸念されている。

特許文献1には、RGBの各画素のパターニングをレーザアブレーションやプラズマエッチングによって行うことが記載されているが、有機材料を含む薄膜をパターニングする際に、該薄膜が雰囲気中の大気に曝されることを防ぐことについては何ら対策がとられていないため、製造時に有機材料が大気中で劣化することによって素子性能が低下することが懸念される。

特許文献2には、複数の受光部が非透光性絶縁体によって隔離された構成であるが、受光部に含まれる有機材料が劣化しないように保護することについては記載されていない。

本発明は、上記事情に鑑みてなされたもので、その目的は、有機材料を含む光電変換層が劣化することを防止して、素子性能の低下を防止することができる光電変換装置、光電変換装置の製造方法及び撮像装置を提供することにある。

本発明は、下記に示すものである。

(1)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置であって、

隣り合う前記画素同士の間に形成され、前記上部電極と電気的に接続された導電性の隔壁と、

前記上部電極上に設けられた透明絶縁膜とを備え、

前記画素が前記隔壁と前記透明絶縁膜とによって封止されている光電変換装置。

(2)上記(1)に記載の光電変換装置であって、

前記上部電極の上面が前記隔壁の上部よりも低く形成されている光電変換装置。

(3)上記(1)又は(2)に記載の光電変換装置であって、

前記上部電極が透明である光電変換装置。

(4)上記(1)から(3)のいずれかに記載の光電変換装置であって、

前記隔壁が光の入射側から視て井桁状に形成され、前記画素が前記隔壁によってそれぞれ隔離されて配列されている光電変換装置。

(5)上記(1)から(4)のいずれかに記載の光電変換装置であって、

前記隔壁が導電性で、下層壁部と、前記下層壁部の上に連接され、該下層壁部よりも画素側から退避するように寸法が変化した上層壁部とを有し、前記下層壁部及び前記上層壁部が前記上部電極と接触する光電変換装置。

(6)上記(1)から(4)のいずれかに記載の光電変換装置であって、

前記隔壁が導電性で、下層壁部と、前記下層壁部の上に連接され、該下層壁部よりも画素側に突出するように寸法が変化した上層壁部とを有し、前記下層壁部及び前記上層壁部が前記上部電極と接触する光電変換装置。

(7)上記(1)から(6)のいずれかに記載の光電変換装置であって、

隣り合う前記画素の前記下部電極同士を離間する絶縁膜が形成され、前記絶縁膜上に前記隔壁が形成される光電変換装置。

(8)上記(1)から(4),(6),及び(7)のいずれかに記載の光電変換装置であって、

前記画素それぞれの前記上部電極と前記光電変換層と前記下部電極とが、光の入射側から視て、等しい面積で、かつ、重なるように配置される光電変換装置。

(9)上記(1)から(8)に記載の光電変換装置であって、

前記光電変換素子が前記光電変換層で生成された電子を前記下部電極に捕集する構成であって、前記光電変換層が前記隔壁と接触し、前記隔壁の仕事関数の値が前記上部電極の仕事関数の値より大きい光電変換装置。

(10)上記(1)から(8)に記載の光電変換装置であって、

前記光電変換素子が前記光電変換層で生成された正孔を前記下部電極に捕集する構成であって、前記光電変換層が前記隔壁と接触し、前記隔壁の仕事関数の値が前記上部電極の仕事関数の値より小さい光電変換装置。

(11)上記(1)から(10)のいずれかに記載の光電変換装置であって、

前記複数の画素が、第1の波長の電磁波を光電変換する光電変換素子を含む第1の画素と、第2の波長の電磁波を光電変換する光電変換素子を含む第2の画素と、を含む光電変換装置。

(12)上記(1)から(10)のいずれかに記載の光電変換装置であって、

前記複数の画素が、赤色光を光電変換する光電変換素子を含む赤色画素と、緑色光を光電変換する光電変換素子を含む緑色画素と、青色光を光電変換する光電変換素子を含む青色画素と、を含む光電変換装置。

(13)上記(1)から(10)のいずれかに記載の光電変換装置であって、

各画素が、第1の波長の電磁波を光電変換する光電変換素子と第2の波長の電磁波を光電変換する光電変換素子とを有する光電変換装置。

(14)上記(1)から(10)のいずれかに記載の光電変換装置であって、

各画素が、赤色光を光電変換する光電変換素子と緑色光を光電変換する光電変換素子と青色光を光電変換する光電変換素子とを有する光電変換装置。

(15)上記(1)から(14)のいずれかに記載の光電変換装置を備えた撮像装置であって、

前記基板内に、前記下部電極に接続され、電荷に応じた信号を出力する駆動回路が設けられている撮像装置。

(16)上記(15)に記載の撮像装置であって、

前記駆動回路がCCD型又はCMOS型である撮像装置。

(17)(実施形態1)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)前記下部電極上に導電性材料を成膜する工程と、

(b)前記導電性材料の膜に、各画素を形成する領域に応じて開口を設けることで前記画素間に隔壁を形成する工程と、

(c)上記(b)の工程の後、前記光電変換層を成膜する工程と、

(d)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(e)前記上部電極を成膜した後、透明絶縁膜を成膜する工程と、

(f)前記開口を設けた部分以外に成膜された、前記光電変換層、前記上部電極、前記透明絶縁膜を除去する工程と、を含む光電変換装置の製造方法。

(18)(実施形態3)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)前記下部電極上に導電性材料を成膜する工程と、

(b)前記導電性材料の膜に、各画素を形成する領域に応じて第1の開口を設けることで前記画素間に隔壁を形成する工程と、

(c)上記(b)の工程の後、前記光電変換層を成膜する工程と、

(d)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(e)前記上部電極を成膜した後、前記導電性材料を成膜する工程と、

(f)前記導電性材料の上に形成された、前記光電変換層、前記上部電極、該上部電極に積層する前記導電性材料を除去する工程と、

(g)前記導電性材料の膜に、前記第1の開口よりも開口面積の小さい第2の開口を設ける工程と、

(h)透明絶縁膜を成膜する工程と、を含む光電変換装置の製造方法。

(19)(実施形態4)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)絶縁性材料を成膜する工程と、

(b)成膜された前記絶縁性材料のうえに導電性材料を成膜する工程と、

(c)前記絶縁性材料及び前記導電性材料の膜に、各画素を形成する領域に応じて開口を設ける工程と、

(d)前記下部電極を成膜する工程と、

(e)前記光電変換層を成膜する工程と、

(f)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(g)前記上部電極を成膜した後、前記透明絶縁膜を成膜する工程と、

(h)前記開口を設けた領域以外の、前記下部電極、前記光電変換層、前記上部電極、前記透明絶縁膜を除去する工程と、を含む光電変換装置の製造方法。

(20)(実施形態4変形)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)前記基板に絶縁性材料を成膜する工程と、

(b)成膜された前記絶縁性材料に、前記下部電極と接続される接続部を形成するための第1の孔と、前記第1の孔と連通し、かつ、該第1の孔より開口面積の大きい第2の孔を形成する工程と、

(c)導電性材料を成膜する工程と、

(d)前記導電性材料の膜に、各画素を形成する領域に応じて開口を設ける工程と、

(e)前記下部電極を成膜する工程と、

(f)前記光電変換層を成膜する工程と、

(g)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(h)前記上部電極を成膜した後、前記透明絶縁膜を成膜する工程と、

(i)前記開口を設けた領域以外の、前記下部電極、前記光電変換層、前記上部電極、前記透明絶縁膜を除去する工程と、を含む光電変換装置の製造方法。

(21)(実施形態5)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)絶縁性材料を成膜する工程と、

(b)前記絶縁性材料の膜に、各画素を形成する領域に応じて第1の開口を設けることで前記画素間に隔壁を形成する工程と、

(c)前記下部電極を成膜する工程と、

(d)前記光電変換層を成膜する工程と、

(e)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(f)前記上部電極を成膜した後、導電性材料を成膜する工程と、

(g)前記開口を設けた部分以外に成膜された、前記下部電極、前記光電変換層、前記上部電極、該上部電極に積層する前記導電性材料を除去する工程と、

(h)各画素の導電性材料の膜の上面、及び、前記絶縁性材料の膜の上面に前記導電性材料を成膜する工程と、

(i)上記(g)の工程で成膜した導電性材料に、前記第1の開口よりも開口面積が小さい第2の開口を設ける工程と、

(j)透明絶縁膜を成膜する工程と、を含む光電変換材料の製造方法。

(1)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置であって、

隣り合う前記画素同士の間に形成され、前記上部電極と電気的に接続された導電性の隔壁と、

前記上部電極上に設けられた透明絶縁膜とを備え、

前記画素が前記隔壁と前記透明絶縁膜とによって封止されている光電変換装置。

(2)上記(1)に記載の光電変換装置であって、

前記上部電極の上面が前記隔壁の上部よりも低く形成されている光電変換装置。

(3)上記(1)又は(2)に記載の光電変換装置であって、

前記上部電極が透明である光電変換装置。

(4)上記(1)から(3)のいずれかに記載の光電変換装置であって、

前記隔壁が光の入射側から視て井桁状に形成され、前記画素が前記隔壁によってそれぞれ隔離されて配列されている光電変換装置。

(5)上記(1)から(4)のいずれかに記載の光電変換装置であって、

前記隔壁が導電性で、下層壁部と、前記下層壁部の上に連接され、該下層壁部よりも画素側から退避するように寸法が変化した上層壁部とを有し、前記下層壁部及び前記上層壁部が前記上部電極と接触する光電変換装置。

(6)上記(1)から(4)のいずれかに記載の光電変換装置であって、

前記隔壁が導電性で、下層壁部と、前記下層壁部の上に連接され、該下層壁部よりも画素側に突出するように寸法が変化した上層壁部とを有し、前記下層壁部及び前記上層壁部が前記上部電極と接触する光電変換装置。

(7)上記(1)から(6)のいずれかに記載の光電変換装置であって、

隣り合う前記画素の前記下部電極同士を離間する絶縁膜が形成され、前記絶縁膜上に前記隔壁が形成される光電変換装置。

(8)上記(1)から(4),(6),及び(7)のいずれかに記載の光電変換装置であって、

前記画素それぞれの前記上部電極と前記光電変換層と前記下部電極とが、光の入射側から視て、等しい面積で、かつ、重なるように配置される光電変換装置。

(9)上記(1)から(8)に記載の光電変換装置であって、

前記光電変換素子が前記光電変換層で生成された電子を前記下部電極に捕集する構成であって、前記光電変換層が前記隔壁と接触し、前記隔壁の仕事関数の値が前記上部電極の仕事関数の値より大きい光電変換装置。

(10)上記(1)から(8)に記載の光電変換装置であって、

前記光電変換素子が前記光電変換層で生成された正孔を前記下部電極に捕集する構成であって、前記光電変換層が前記隔壁と接触し、前記隔壁の仕事関数の値が前記上部電極の仕事関数の値より小さい光電変換装置。

(11)上記(1)から(10)のいずれかに記載の光電変換装置であって、

前記複数の画素が、第1の波長の電磁波を光電変換する光電変換素子を含む第1の画素と、第2の波長の電磁波を光電変換する光電変換素子を含む第2の画素と、を含む光電変換装置。

(12)上記(1)から(10)のいずれかに記載の光電変換装置であって、

前記複数の画素が、赤色光を光電変換する光電変換素子を含む赤色画素と、緑色光を光電変換する光電変換素子を含む緑色画素と、青色光を光電変換する光電変換素子を含む青色画素と、を含む光電変換装置。

(13)上記(1)から(10)のいずれかに記載の光電変換装置であって、

各画素が、第1の波長の電磁波を光電変換する光電変換素子と第2の波長の電磁波を光電変換する光電変換素子とを有する光電変換装置。

(14)上記(1)から(10)のいずれかに記載の光電変換装置であって、

各画素が、赤色光を光電変換する光電変換素子と緑色光を光電変換する光電変換素子と青色光を光電変換する光電変換素子とを有する光電変換装置。

(15)上記(1)から(14)のいずれかに記載の光電変換装置を備えた撮像装置であって、

前記基板内に、前記下部電極に接続され、電荷に応じた信号を出力する駆動回路が設けられている撮像装置。

(16)上記(15)に記載の撮像装置であって、

前記駆動回路がCCD型又はCMOS型である撮像装置。

(17)(実施形態1)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)前記下部電極上に導電性材料を成膜する工程と、

(b)前記導電性材料の膜に、各画素を形成する領域に応じて開口を設けることで前記画素間に隔壁を形成する工程と、

(c)上記(b)の工程の後、前記光電変換層を成膜する工程と、

(d)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(e)前記上部電極を成膜した後、透明絶縁膜を成膜する工程と、

(f)前記開口を設けた部分以外に成膜された、前記光電変換層、前記上部電極、前記透明絶縁膜を除去する工程と、を含む光電変換装置の製造方法。

(18)(実施形態3)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)前記下部電極上に導電性材料を成膜する工程と、

(b)前記導電性材料の膜に、各画素を形成する領域に応じて第1の開口を設けることで前記画素間に隔壁を形成する工程と、

(c)上記(b)の工程の後、前記光電変換層を成膜する工程と、

(d)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(e)前記上部電極を成膜した後、前記導電性材料を成膜する工程と、

(f)前記導電性材料の上に形成された、前記光電変換層、前記上部電極、該上部電極に積層する前記導電性材料を除去する工程と、

(g)前記導電性材料の膜に、前記第1の開口よりも開口面積の小さい第2の開口を設ける工程と、

(h)透明絶縁膜を成膜する工程と、を含む光電変換装置の製造方法。

(19)(実施形態4)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)絶縁性材料を成膜する工程と、

(b)成膜された前記絶縁性材料のうえに導電性材料を成膜する工程と、

(c)前記絶縁性材料及び前記導電性材料の膜に、各画素を形成する領域に応じて開口を設ける工程と、

(d)前記下部電極を成膜する工程と、

(e)前記光電変換層を成膜する工程と、

(f)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(g)前記上部電極を成膜した後、前記透明絶縁膜を成膜する工程と、

(h)前記開口を設けた領域以外の、前記下部電極、前記光電変換層、前記上部電極、前記透明絶縁膜を除去する工程と、を含む光電変換装置の製造方法。

(20)(実施形態4変形)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)前記基板に絶縁性材料を成膜する工程と、

(b)成膜された前記絶縁性材料に、前記下部電極と接続される接続部を形成するための第1の孔と、前記第1の孔と連通し、かつ、該第1の孔より開口面積の大きい第2の孔を形成する工程と、

(c)導電性材料を成膜する工程と、

(d)前記導電性材料の膜に、各画素を形成する領域に応じて開口を設ける工程と、

(e)前記下部電極を成膜する工程と、

(f)前記光電変換層を成膜する工程と、

(g)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(h)前記上部電極を成膜した後、前記透明絶縁膜を成膜する工程と、

(i)前記開口を設けた領域以外の、前記下部電極、前記光電変換層、前記上部電極、前記透明絶縁膜を除去する工程と、を含む光電変換装置の製造方法。

(21)(実施形態5)基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)絶縁性材料を成膜する工程と、

(b)前記絶縁性材料の膜に、各画素を形成する領域に応じて第1の開口を設けることで前記画素間に隔壁を形成する工程と、

(c)前記下部電極を成膜する工程と、

(d)前記光電変換層を成膜する工程と、

(e)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(f)前記上部電極を成膜した後、導電性材料を成膜する工程と、

(g)前記開口を設けた部分以外に成膜された、前記下部電極、前記光電変換層、前記上部電極、該上部電極に積層する前記導電性材料を除去する工程と、

(h)各画素の導電性材料の膜の上面、及び、前記絶縁性材料の膜の上面に前記導電性材料を成膜する工程と、

(i)上記(g)の工程で成膜した導電性材料に、前記第1の開口よりも開口面積が小さい第2の開口を設ける工程と、

(j)透明絶縁膜を成膜する工程と、を含む光電変換材料の製造方法。

本発明によれば、有機材料を含む光電変換層が劣化することを防止して、素子性能が低下することを防止することができる光電変換素子、光電変換素子の製造方法及び撮像装置を提供できる。

本発明の光電変換装置は、基板と、該基板の上方に形成された下部電極と、下部電極の上方に形成された光電変換層を含む中間層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された構成である。光電変換装置は、複数の画素を2次元状に配置したイメージセンサとして用いることができ、または、複数の画素を1次元状に配列したラインセンサとして用いることができる。なお、以下の実施形態では、複数の画素を2次元状に配置したイメージセンサを例に説明する。

中間層は電磁波を吸収する部位、光電変換層、電子輸送部位、正孔輸送部位、電子阻止部位、正孔阻止部位、結晶化防止部位、電極ならびに層間接触改良部位等の積み重ねもしくは混合から形成される。光電変換層は有機層を含み、該有機層は有機p形化合物または有機n形化合物を含有することが好ましい。

有機p形半導体(化合物)は、ドナ性有機半導体(化合物)であり、主に正孔輸送性有機化合物に代表され、電子を供与しやすい性質がある有機化合物をいう。さらに詳しくは2つの有機材料を接触させて用いたときにイオン化ポテンシャルの小さい方の有機化合物をいう。したがって、ドナ性有機化合物は、電子供与性のある有機化合物であればいずれの有機化合物も使用可能である。例えば、トリアリールアミン化合物、ベンジジン化合物、ピラゾリン化合物、スチリルアミン化合物、ヒドラゾン化合物、トリフェニルメタン化合物、カルバゾール化合物、ポリシラン化合物、チオフェン化合物、フタロシアニン化合物、シアニン化合物、メロシアニン化合物、オキソノール化合物、ポリアミン化合物、インドール化合物、ピロール化合物、ピラゾール化合物、ポリアリーレン化合物、縮合芳香族炭素環化合物(ナフタレン誘導体、アントラセン誘導体、フェナントレン誘導体、テトラセン誘導体、ピレン誘導体、ペリレン誘導体、フルオランテン誘導体)、含窒素ヘテロ環化合物を配位子として有する金属錯体等を用いることができる。なお、これに限らず、上記したように、n形(アクセプタ性)化合物として用いた有機化合物よりもイオン化ポテンシャルの小さい有機化合物であればドナ性有機半導体として用いてよい。

有機n形半導体(化合物)は、アクセプタ性有機半導体(化合物)であり、主に電子輸送性有機化合物に代表され、電子を受容しやすい性質がある有機化合物をいう。さらに詳しくは2つの有機化合物を接触させて用いたときに電子親和力の大きい方の有機化合物をいう。したがって、アクセプタ性有機化合物は、電子受容性のある有機化合物であればいずれの有機化合物も使用可能である。例えば、縮合芳香族炭素環化合物(ナフタレン誘導体、アントラセン誘導体、フェナントレン誘導体、テトラセン誘導体、ピレン誘導体、ペリレン誘導体、フルオランテン誘導体)、窒素原子、酸素原子、硫黄原子を含有する5ないし7員のヘテロ環化合物(例えばピリジン、ピラジン、ピリミジン、ピリダジン、トリアジン、キノリン、キノキサリン、キナゾリン、フタラジン、シンノリン、イソキノリン、プテリジン、アクリジン、フェナジン、フェナントロリン、テトラゾール、ピラゾール、イミダゾール、チアゾール、オキサゾール、インダゾール、ベンズイミダゾール、ベンゾトリアゾール、ベンゾオキサゾール、ベンゾチアゾール、カルバゾール、プリン、トリアゾロピリダジン、トリアゾロピリミジン、テトラザインデン、オキサジアゾール、イミダゾピリジン、ピラリジン、ピロロピリジン、チアジアゾロピリジン、ジベンズアゼピン、トリベンズアゼピン等)、ポリアリーレン化合物、フルオレン化合物、シクロペンタジエン化合物、シリル化合物、含窒素ヘテロ環化合物を配位子として有する金属錯体などが挙げられる。なお、これに限らず、上記したように、ドナ性有機化合物として用いた有機化合物よりも電子親和力の大きな有機化合物であればアクセプタ性有機半導体として用いてよい。

p形有機色素、またはn形有機色素としては、いかなるものを用いても良いが、好ましくは、シアニン色素、スチリル色素、ヘミシアニン色素、メロシアニン色素(ゼロメチンメロシアニン(シンプルメロシアニン)を含む)、3核メロシアニン色素、4核メロシアニン色素、ロダシアニン色素、コンプレックスシアニン色素、コンプレックスメロシアニン色素、アロポーラ色素、オキソノール色素、ヘミオキソノール色素、スクアリウム色素、クロコニウム色素、アザメチン色素、クマリン色素、アリーリデン色素、アントラキノン色素、トリフェニルメタン色素、アゾ色素、アゾメチン色素、スピロ化合物、メタロセン色素、フルオレノン色素、フルギド色素、ペリレン色素、フェナジン色素、フェノチアジン色素、キノン色素、インジゴ色素、ジフェニルメタン色素、ポリエン色素、アクリジン色素、アクリジノン色素、ジフェニルアミン色素、キナクリドン色素、キノフタロン色素、フェノキサジン色素、フタロペリレン色素、ポルフィリン色素、クロロフィル色素、フタロシアニン色素、金属錯体色素、縮合芳香族炭素環系色素(ナフタレン誘導体、アントラセン誘導体、フェナントレン誘導体、テトラセン誘導体、ピレン誘導体、ペリレン誘導体、フルオランテン誘導体)が挙げられる。

次に金属錯体化合物について説明する。金属錯体化合物は金属に配位する少なくとも1つの窒素原子または酸素原子または硫黄原子を有する配位子をもつ金属錯体であり、金属錯体中の金属イオンは特に限定されないが、好ましくはベリリウムイオン、マグネシウムイオン、アルミニウムイオン、ガリウムイオン、亜鉛イオン、インジウムイオン、または錫イオンであり、より好ましくはベリリウムイオン、アルミニウムイオン、ガリウムイオン、または亜鉛イオンであり、更に好ましくはアルミニウムイオン、または亜鉛イオンである。前記金属錯体中に含まれる配位子としては種々の公知の配位子が有るが、例えば、H.Yersin著「Photochemistry and Photophysics of Coordination Compounds」(Springer−Verlag、1987年)、山本明夫著「有機金属化学−基礎と応用−」(裳華房、1982年)等に記載の配位子が挙げられる。

配位子として、好ましくは含窒素ヘテロ環配位子(好ましくは炭素数1〜30、より好ましくは炭素数2〜20、特に好ましくは炭素数3〜15であり、単座配位子であっても2座以上の配位子であっても良い。好ましくは2座配位子である。例えばピリジン配位子、ビピリジル配位子、キノリノール配位子、ヒドロキシフェニルアゾール配位子(ヒドロキシフェニルベンズイミダゾール、ヒドロキシフェニルベンズオキサゾール配位子、ヒドロキシフェニルイミダゾール配位子)などが挙げられる)、アルコキシ配位子(好ましくは炭素数1〜30、より好ましくは炭素数1〜20、特に好ましくは炭素数1〜10であり、例えばメトキシ、エトキシ、ブトキシ、2−エチルヘキシロキシなどが挙げられる。)、アリールオキシ配位子(好ましくは炭素数6〜30、より好ましくは炭素数6〜20、特に好ましくは炭素数6〜12であり、例えばフェニルオキシ、1−ナフチルオキシ、2−ナフチルオキシ、2,4,6−トリメチルフェニルオキシ、4−ビフェニルオキシなどが挙げられる。)、ヘテロアリールオキシ配位子(好ましくは炭素数1〜30、より好ましくは炭素数1〜20、特に好ましくは炭素数1〜12であり、例えばピリジルオキシ、ピラジルオキシ、ピリミジルオキシ、キノリルオキシなどが挙げられる。)、アルキルチオ配位子(好ましくは炭素数1〜30、より好ましくは炭素数1〜20、特に好ましくは炭素数1〜12であり、例えばメチルチオ、エチルチオなどが挙げられる。)、アリールチオ配位子(好ましくは炭素数6〜30、より好ましくは炭素数6〜20、特に好ましくは炭素数6〜12であり、例えばフェニルチオなどが挙げられる。)、ヘテロ環置換チオ配位子(好ましくは炭素数1〜30、より好ましくは炭素数1〜20、特に好ましくは炭素数1〜12であり、例えばピリジルチオ、2−ベンズイミゾリルチオ、2−ベンズオキサゾリルチオ、2−ベンズチアゾリルチオなどが挙げられる。)、またはシロキシ配位子(好ましくは炭素数1〜30、より好ましくは炭素数3〜25、特に好ましくは炭素数6〜20であり、例えば、トリフェニルシロキシ基、トリエトキシシロキシ基、トリイソプロピルシロキシ基などが挙げられる)であり、より好ましくは含窒素ヘテロ環配位子、アリールオキシ配位子、ヘテロアリールオキシ基、またはシロキシ配位子であり、更に好ましくは含窒素ヘテロ環配位子、アリールオキシ配位子、またはシロキシ配位子が挙げられる。

下部電極と上部電極の間にp形半導体層とn形半導体層とを有し、該p形半導体とn形半導体の少なくともいずれかが有機半導体であり、かつ、それらの半導体層の間に、該p形半導体およびn形半導体を含むバルクヘテロ接合構造層を中間層として有する光電変換膜(感光層)を含有する場合が好ましい。このような場合、光電変換膜において、有機層にバルクへテロ接合構造を含有させることにより有機層のキャリア拡散長が短いという欠点を補い、光電変換効率を向上させることができる。なお、バルクへテロ接合構造については、特開2005−303266号において詳細に説明されている。

下部電極と上部電極の間にp形半導体の層とn形半導体の層で形成されるpn接合層の繰り返し構造(タンデム構造)の数を2以上有する構造を持つ光電変換膜(感光層)を含有する場合も好ましく、さらに好ましくは、前記繰り返し構造の間に、導電材料の薄層を挿入する場合である。pn接合層の繰り返し構造(タンデム構造)の数はいかなる数でもよいが、光電変換効率を高くするために好ましくは2〜50であり、さらに好ましくは2〜30であり、特に好ましくは2または10である。導電材料としては銀または金が好ましく、銀が最も好ましい。なお、タンデム構造については、特開2006−086493号において詳細に説明されている。

下部電極と上部電極の間にp形半導体の層、n形半導体の層、(好ましくは混合・分散(バルクヘテロ接合構造)層)を持つ光電変換膜において、p形半導体およびn形半導体のうちの少なくとも1方に配向制御された有機化合物を含むことを特徴とする光電変換膜の場合も好ましく、さらに好ましくは、p形半導体およびn形半導体の両方に配向制御された(可能な)有機化合物を含む場合である。光電変換膜の有機層に用いられる有機化合物としては、π共役電子を持つものが好ましく用いられるが、このπ電子平面が、基板(電極基板)に対して垂直ではなく、平行に近い角度で配向しているほど好ましい。基板に対する角度として好ましくは0°以上80°以下であり、さらに好ましくは0°以上60°以下であり、さらに好ましくは0°以上40°以下であり、さらに好ましくは0°以上20°以下であり、特に好ましくは0°以上10°以下であり、最も好ましくは0°(すなわち基板に対して平行)である。上記のように、配向の制御された有機化合物の層は、有機層全体に対して一部でも含めば良いが、好ましくは、有機層全体に対する配向の制御された部分の割合が10%以上の場合であり、さらに好ましくは30%以上、さらに好ましくは50%以上、さらに好ましくは70%以上、特に好ましくは90%以上、最も好ましくは100%である。このような状態は、光電変換膜において、有機層の有機化合物の配向を制御することにより有機層のキャリア拡散長が短いという欠点を補い、光電変換効率を向上させるものである。

有機化合物の配向が制御されている場合において、さらに好ましくはヘテロ接合面(例えばpn接合面)が基板に対して平行ではない場合である。ヘテロ接合面が、基板(電極基板)に対して平行ではなく、垂直に近い角度で配向しているほど好ましい。基板に対する角度として好ましくは10°以上90°以下であり、さらに好ましくは30°以上90°以下であり、さらに好ましくは50°以上90°以下であり、さらに好ましくは70°以上90°以下であり、特に好ましくは80°以上90°以下であり、最も好ましくは90°(すなわち基板に対して垂直)である。上記のような、ヘテロ接合面の制御された有機化合物の層は、有機層全体に対して一部でも含めば良い。好ましくは、有機層全体に対する配向の制御された部分の割合が10%以上の場合であり、さらに好ましくは30%以上、さらに好ましくは50%以上、さらに好ましくは70%以上、特に好ましくは90%以上、最も好ましくは100%である。このような場合、有機層におけるヘテロ接合面の面積が増大し、界面で生成する電子、正孔、電子正孔対等のキャリア量が増大し、光電変換効率の向上が可能となる。以上の、有機化合物のヘテロ接合面とπ電子平面の両方の配向が制御された光電変換膜において、特に光電変換効率の向上が可能である。これらの状態については、特開2006−086493号において詳細に説明されている。

光吸収の点では有機色素層の膜厚は大きいほど好ましいが、電荷分離に寄与しない割合を考慮すると、有機色素層の膜厚として好ましくは、30nm以上300nm以下、さらに好ましくは50nm以上250nm以下、特に好ましくは80nm以上200nm以下である。

光吸収の点では有機色素層の膜厚は大きいほど好ましいが、電荷分離に寄与しない割合を考慮すると、有機色素層の膜厚として好ましくは、30nm以上300nm以下、さらに好ましくは50nm以上250nm以下、特に好ましくは80nm以上200nm以下である。

(有機層の形成法)

これらの有機化合物を含む層は、乾式成膜法あるいは湿式成膜法により成膜される。乾式成膜法の具体的な例としては、真空蒸着法、スパッタ法、イオンプレーティング法,分子線エピタキシ法等の物理気相堆積(PVD)法あるいはプラズマ重合等の化学気相堆積(CVD)法が挙げられる。湿式成膜法としては、塗布法、回転塗布法、浸漬法、LB法等が用いられる。

p形半導体(化合物)、または、n形半導体(化合物)のうちの少なくとも一つとして高分子化合物を用いる場合は、作成の容易な湿式成膜法により成膜することが好ましい。蒸着等の乾式成膜法を用いた場合、高分子を用いることは分解のおそれがあるため難しく、代わりとしてそのオリゴマを好ましく用いることができる。一方、低分子を用いる場合は、乾式成膜法が好ましく用いられ、特に真空蒸着法が好ましく用いられる。真空蒸着法は抵抗加熱蒸着法、電子線加熱蒸着法等の化合物の加熱の方法、るつぼ、ボ−ト等の蒸着源の形状、真空度、蒸着温度、基板温度、蒸着速度等が基本的なパラメータである。均一な蒸着を可能とするために基板を回転させて蒸着することは好ましい。真空度は高い方が好ましく10-2Pa以下、好ましくは10-4Pa以下、特に好ましくは10-6Pa以下で真空蒸着が行われる。蒸着時のすべての工程は上記の真空中で行われることが好ましく、基本的には化合物が直接、外気の酸素、水分と接触しないようにする。真空蒸着の上述した条件は有機膜の結晶性、非晶質性、密度、緻密度等に影響するので厳密に制御する必要がある。水晶振動子、干渉計等の膜厚モニタを用いて蒸着速度をPIもしくはPID制御することは好ましく用いられる。2種以上の化合物を同時に蒸着する場合には共蒸着法、フラッシュ蒸着法等を好ましく用いることができる。

これらの有機化合物を含む層は、乾式成膜法あるいは湿式成膜法により成膜される。乾式成膜法の具体的な例としては、真空蒸着法、スパッタ法、イオンプレーティング法,分子線エピタキシ法等の物理気相堆積(PVD)法あるいはプラズマ重合等の化学気相堆積(CVD)法が挙げられる。湿式成膜法としては、塗布法、回転塗布法、浸漬法、LB法等が用いられる。

p形半導体(化合物)、または、n形半導体(化合物)のうちの少なくとも一つとして高分子化合物を用いる場合は、作成の容易な湿式成膜法により成膜することが好ましい。蒸着等の乾式成膜法を用いた場合、高分子を用いることは分解のおそれがあるため難しく、代わりとしてそのオリゴマを好ましく用いることができる。一方、低分子を用いる場合は、乾式成膜法が好ましく用いられ、特に真空蒸着法が好ましく用いられる。真空蒸着法は抵抗加熱蒸着法、電子線加熱蒸着法等の化合物の加熱の方法、るつぼ、ボ−ト等の蒸着源の形状、真空度、蒸着温度、基板温度、蒸着速度等が基本的なパラメータである。均一な蒸着を可能とするために基板を回転させて蒸着することは好ましい。真空度は高い方が好ましく10-2Pa以下、好ましくは10-4Pa以下、特に好ましくは10-6Pa以下で真空蒸着が行われる。蒸着時のすべての工程は上記の真空中で行われることが好ましく、基本的には化合物が直接、外気の酸素、水分と接触しないようにする。真空蒸着の上述した条件は有機膜の結晶性、非晶質性、密度、緻密度等に影響するので厳密に制御する必要がある。水晶振動子、干渉計等の膜厚モニタを用いて蒸着速度をPIもしくはPID制御することは好ましく用いられる。2種以上の化合物を同時に蒸着する場合には共蒸着法、フラッシュ蒸着法等を好ましく用いることができる。

(電極)

光電変換素子の電極について詳細に説明する。光電変換層を含む中間層は、下部電極(画素電極膜)、上部電極(対向電極膜)により挟まれ、電極間材料等を含むことができる。画素電極膜とは、電荷蓄積/転送/読出部位が形成された基板上方に作成された電極膜のことで、通常1画素ごとに分割される。これは、光電変換層により変換された信号電荷を電荷蓄積/転送/信号読出回路基板上に1画素ごとに読出すことで、画像を得るためである。対向電極膜とは、光電変換層を画素電極膜と共にはさみこむことで信号電荷と逆の極性を持つ信号電荷を吐出す機能をもっている。この信号電荷の吐出しは各画素間で分割する必要がないため、通常、対向電極膜は各画素間で共通にすることができる。そのため、共通電極膜(コモン電極膜)と呼ばれることもある。

光電変換素子の電極について詳細に説明する。光電変換層を含む中間層は、下部電極(画素電極膜)、上部電極(対向電極膜)により挟まれ、電極間材料等を含むことができる。画素電極膜とは、電荷蓄積/転送/読出部位が形成された基板上方に作成された電極膜のことで、通常1画素ごとに分割される。これは、光電変換層により変換された信号電荷を電荷蓄積/転送/信号読出回路基板上に1画素ごとに読出すことで、画像を得るためである。対向電極膜とは、光電変換層を画素電極膜と共にはさみこむことで信号電荷と逆の極性を持つ信号電荷を吐出す機能をもっている。この信号電荷の吐出しは各画素間で分割する必要がないため、通常、対向電極膜は各画素間で共通にすることができる。そのため、共通電極膜(コモン電極膜)と呼ばれることもある。

光電変換素子を構成する透明導電膜の材料は、プラズマフリーである成膜装置、電子線蒸着装置、およびパルスレーザ蒸着装置により成膜できるものが好ましい。例えば、金属、合金、金属酸化物、金属窒化物、金属硼化物、有機導電性化合物、これらの混合物等が好適に挙げられ、具体例としては、酸化錫、酸化亜鉛、酸化インジウム、酸化インジウム錫(ITO)、酸化インジウム亜鉛(IZO)、酸化インジウムタングステン(IWO)、酸化チタン等の導電性金属酸化物、窒化チタン(TiN)等の金属窒化物、Au、Pt、Ag、Cr、Ni、Al等の金属、更にこれらの金属と導電性金属酸化物との混合物または積層物、ヨウ化銅、硫化銅などの無機導電性物質、ポリアニリン、ポリチオフェン、ポリピロール等の有機導電性材料、これらとITOとの積層物、などが挙げられる。また、日本学術振興会透明酸化物光・電子材料第166委員会編「透明導電膜の技術 改訂2版」(オーム社、2006年)や、南内嗣監修「透明導電膜の新展開III―ITOとその代替材料開発の現状−」(シーエムシー出版、2008年)等に詳細に記載されているものを用いても良い。

透明導電膜の材料として特に好ましいのは、ITO、IZO、酸化錫、アンチモンドープ酸化錫(ATO)、弗素ドープ酸化錫(FTO)、酸化亜鉛、アンチモンドープ酸化亜鉛(AZO)、ガリウムドープ酸化亜鉛(GZO)のいずれかの材料である。透明導電膜の光透過率は、その透明導電膜を含む光電変換素子に含まれる光電変換層の光電変換光吸収極大波長において、60%以上が好ましく、より好ましくは80%以上で、より好ましくは90%以上、より好ましくは95%以上である。また、透明導電膜の表面抵抗は、下部電極であるか上部電極であるか、さらには電荷蓄積/転送・読出部位がCCD型であるかCMOS型であるか等により好ましい範囲は異なる。上部電極に使用し電荷蓄積/転送/読出部位がCMOS型の場合には10kΩ/□以下が好ましく、より好ましくは、1kΩ/□以下である。上部電極に使用し電荷蓄積/転送/読出部位がCCD型の場合には1kΩ/□以下が好ましく、より好ましくは、0.1kΩ/□以下である。下部電極に使用する場合には1MΩ/□以下が好ましく、より好ましくは、0.1MΩ/□以下である。

透明導電膜成膜時の条件について触れる。透明導電膜成膜時の基板温度は500℃以下が好ましく、より好ましくは、300℃以下で、さらに好ましくは200℃以下、さらに好ましくは150℃以下である。また、透明導電膜成膜中にガスを導入しても良く、基本的にそのガス種は制限されないが、Ar、He、O2、N2などを用いることができる。また、これらのガスの混合ガスを用いても良い。特に酸化物の材料の場合は、酸素欠陥が生じることが多いので、O2を用いることが好ましい。

光電変換層に電圧を印加した場合、光電変換効率が向上する点で好ましい。印加電圧としては、いかなる電圧でも良いが、光電変換層を含む中間層の膜厚により必要な電圧は変わってくる。すなわち、光電変換効率は、光電変換層に加わる電界が大きいほど向上するが、同じ印加電圧でも中間層の膜厚が薄いほど加わる電界は大きくなる。従って、中間層の膜厚が薄い場合は、印加電圧は相対的に小さくても良い。中間層に加える電界として好ましくは、10V・m−1以上であり、さらに好ましくは1×103V・m−1以上、さらに好ましくは1×105V・m−1以上、特に好ましくは1×106V・m−1以上、最も好ましくは1×107V・m−1以上である。上限は特にないが、高電界になるほど暗電流が増大するので、1×1012V・m−1以下が好ましく、さらに1×109V・m−1以下が好ましい。

(補助層)

好ましくは各画素の上方に紫外線吸収層および/または赤外線吸収層を有する。紫外線吸収層は少なくとも400nm以下の光を吸収または反射することができ、好ましくは400nm以下の波長域での吸収率は50%以上である。赤外線吸収層は少なくとも700nm以上の光を吸収または反射することができ、好ましくは700nm以上の波長域での吸収率は50%以上である。これらの紫外線吸収層、赤外線吸収層は従来公知の方法によって形成できる。例えば基板上にゼラチン、カゼイン、グリュあるいはポリビニルアルコールなどの親水性高分子物質からなる媒染層を設け、その媒染層に所望の吸収波長を有する色素を添加もしくは染色して着色層を形成する方法が知られている。さらには、ある種の着色材が透明樹脂中に分散されてなる着色樹脂を用いた方法が知られている。例えば、特開昭58−46325号公報・特開昭60−78401号公報・特開昭60−184202号公報・特開昭60−184203号公報・特開昭60−184204号公報・特開昭60−184205号公報等に示されている様に、ポリアミノ系樹脂に着色材を混合した着色樹脂膜を用いることができる。感光性を有するポリイミド樹脂を用いた着色剤も可能である。特公平7−113685号公報記載の感光性を有する基を分子内に持つ、200℃以下にて硬化膜を得ることのできる芳香族系のポリアミド樹脂中に着色材料を分散すること、特公平7−69486号公報記載の含量を分散着色樹脂を用いることも可能である。好ましくは誘電体多層膜が用いられる。誘電体多層膜は光の透過の波長依存性が鮮鋭であり、好ましく用いられる。更に、マイクロレンズアレイを光電変換装置の上部に形成することにより、集光効率を向上させることができるため、このような態様も好ましい。

好ましくは各画素の上方に紫外線吸収層および/または赤外線吸収層を有する。紫外線吸収層は少なくとも400nm以下の光を吸収または反射することができ、好ましくは400nm以下の波長域での吸収率は50%以上である。赤外線吸収層は少なくとも700nm以上の光を吸収または反射することができ、好ましくは700nm以上の波長域での吸収率は50%以上である。これらの紫外線吸収層、赤外線吸収層は従来公知の方法によって形成できる。例えば基板上にゼラチン、カゼイン、グリュあるいはポリビニルアルコールなどの親水性高分子物質からなる媒染層を設け、その媒染層に所望の吸収波長を有する色素を添加もしくは染色して着色層を形成する方法が知られている。さらには、ある種の着色材が透明樹脂中に分散されてなる着色樹脂を用いた方法が知られている。例えば、特開昭58−46325号公報・特開昭60−78401号公報・特開昭60−184202号公報・特開昭60−184203号公報・特開昭60−184204号公報・特開昭60−184205号公報等に示されている様に、ポリアミノ系樹脂に着色材を混合した着色樹脂膜を用いることができる。感光性を有するポリイミド樹脂を用いた着色剤も可能である。特公平7−113685号公報記載の感光性を有する基を分子内に持つ、200℃以下にて硬化膜を得ることのできる芳香族系のポリアミド樹脂中に着色材料を分散すること、特公平7−69486号公報記載の含量を分散着色樹脂を用いることも可能である。好ましくは誘電体多層膜が用いられる。誘電体多層膜は光の透過の波長依存性が鮮鋭であり、好ましく用いられる。更に、マイクロレンズアレイを光電変換装置の上部に形成することにより、集光効率を向上させることができるため、このような態様も好ましい。

(駆動回路)

駆動回路を構成する電荷転送/読出部位については特開昭58−103166号公報、特開昭58−103165号公報、特開2003−332551号公報等を参考にすることができる。半導体基板上にMOSトランジスタが各画素単位に形成された構成や、あるいは、素子としてCCDを有する構成を適宜採用することができる。例えばMOSトランジスタを用いた撮像装置の場合、補助層、透明絶縁膜、上部電極を透過した入射光によって光電変換層の中に電荷が発生し、下部電極と上部電極との間に電圧を印加することで生じる電界によって電荷が中間層内を下部電極まで走行し、さらにMOSトランジスタの電荷蓄積部まで移動し、電荷蓄積部に電荷が蓄積される。電荷蓄積部に蓄積された電荷は、MOSトランジスタのスイッチングにより電荷読出部に移動し、さらに電気信号として出力される。これにより、フルカラーの画像信号が、信号処理部を含む撮像装置に入力される。一定量のバイアス電荷を蓄積ダイオードに注入しておき(リフレッシュモード)、一定の電荷を蓄積(光電変換モード)後、信号電荷を読出すことが可能である。光電変換素子そのものを蓄積ダイオードとして用いることもできるし、別途、蓄積ダイオードを付設することもできる。

駆動回路を構成する電荷転送/読出部位については特開昭58−103166号公報、特開昭58−103165号公報、特開2003−332551号公報等を参考にすることができる。半導体基板上にMOSトランジスタが各画素単位に形成された構成や、あるいは、素子としてCCDを有する構成を適宜採用することができる。例えばMOSトランジスタを用いた撮像装置の場合、補助層、透明絶縁膜、上部電極を透過した入射光によって光電変換層の中に電荷が発生し、下部電極と上部電極との間に電圧を印加することで生じる電界によって電荷が中間層内を下部電極まで走行し、さらにMOSトランジスタの電荷蓄積部まで移動し、電荷蓄積部に電荷が蓄積される。電荷蓄積部に蓄積された電荷は、MOSトランジスタのスイッチングにより電荷読出部に移動し、さらに電気信号として出力される。これにより、フルカラーの画像信号が、信号処理部を含む撮像装置に入力される。一定量のバイアス電荷を蓄積ダイオードに注入しておき(リフレッシュモード)、一定の電荷を蓄積(光電変換モード)後、信号電荷を読出すことが可能である。光電変換素子そのものを蓄積ダイオードとして用いることもできるし、別途、蓄積ダイオードを付設することもできる。

信号の読出しについてさらに詳細に説明する。信号の読出しは、通常のカラー読出回路を用いることができる。光電変換素子で光電変換された信号電荷は、光電変換素子そのものもしくは付設されたキャパシタで蓄えられる。蓄えられた電荷は、X−Yアドレス方式を用いたMOS型撮像装置(いわゆるCMOSセンサ)の手法により、画素位置の選択とともに読出される。他には、アドレス選択方式として、1画素づつ順次マルチプレクサスイッチとデジタルシフトレジスタで選択し、共通の出力線に信号電圧(または電荷)として読出す方式が挙げられる。2次元にアレイ化されたX−Yアドレス操作の撮像素子がCMOSセンサとして知られる。これは、X−Yの交点に接続された画素に設けられたスイッチは垂直シフトレジスタに接続され、垂直走査シフトレジスタからの電圧でスイッチがオンすると同じ行に設けられた画素から読出された信号は、列方向の出力線に読出される。この信号は水平走査シフトレジスタにより駆動されるスイッチを通して順番に出力端から読出される。

出力信号の読出しには、フローティングディフュージョン検出器や、フローティングゲート検出器を用いることができる。また画素部分に信号増幅回路を設けることや、相関二重サンプリング(Correlated Double Sampling)の手法などにより、SN比の向上をはかることができる。

信号処理には、ADC回路によるガンマ補正、AD変換機によるデジタル化、輝度信号処理や、色信号処理を施すことができる。色信号処理としては、ホワイトバランス処理や、色分離処理、カラーマトリクス処理などが挙げられる。NTSC信号に用いる際は、RGB信号をYIQ信号の変換処理を施すことができる。

電荷転送・読出部位は電荷の移動度が100cm2・V−1・s−1以上であることが必要であり、この移動度は、材料をIV族、III−V族、II−VI族の半導体から選択することによって得ることができる。その中でも微細化技術が進んでいることと、低コストであることからSi半導体が好ましい。電荷転送・電荷読出の方式は数多く提案されているが、何れの方式でも良い。特に好ましい方式はCMOS型あるいはCCD型である。更に、CMOS型の方が高速読出し、画素加算、部分読出し、消費電力などの点で好ましいことが多い。

出力信号の読出しには、フローティングディフュージョン検出器や、フローティングゲート検出器を用いることができる。また画素部分に信号増幅回路を設けることや、相関二重サンプリング(Correlated Double Sampling)の手法などにより、SN比の向上をはかることができる。

信号処理には、ADC回路によるガンマ補正、AD変換機によるデジタル化、輝度信号処理や、色信号処理を施すことができる。色信号処理としては、ホワイトバランス処理や、色分離処理、カラーマトリクス処理などが挙げられる。NTSC信号に用いる際は、RGB信号をYIQ信号の変換処理を施すことができる。

電荷転送・読出部位は電荷の移動度が100cm2・V−1・s−1以上であることが必要であり、この移動度は、材料をIV族、III−V族、II−VI族の半導体から選択することによって得ることができる。その中でも微細化技術が進んでいることと、低コストであることからSi半導体が好ましい。電荷転送・電荷読出の方式は数多く提案されているが、何れの方式でも良い。特に好ましい方式はCMOS型あるいはCCD型である。更に、CMOS型の方が高速読出し、画素加算、部分読出し、消費電力などの点で好ましいことが多い。

(接続)

光電変換素子の下部電極や上部電極と駆動回路を連結する複数の接続部はいずれの金属で連結してもよいが、Cu、Al、Ag、Au、Cr、Wの中から選択するのが好ましい。複数の画素に応じて、それぞれの接続部を駆動回路との間に設置する必要がある。

光電変換素子の下部電極や上部電極と駆動回路を連結する複数の接続部はいずれの金属で連結してもよいが、Cu、Al、Ag、Au、Cr、Wの中から選択するのが好ましい。複数の画素に応じて、それぞれの接続部を駆動回路との間に設置する必要がある。

(プロセス)

光電変換装置は、公知の半導体製造に用いるいわゆるミクロファブリケーションプロセスにしたがって製造することができる。基本的には、この方法は電磁波や電子線などによるパターン露光(水銀のi,g輝線、エキシマレーザ、さらにはX線、電子線)、現像および/またはバーニングによるパターン形成、素子形成材料の配置(塗布、蒸着、スパッタ、CVDなど)、非パターン部の材料の除去(熱処理、溶解処理など)の反復操作による。

光電変換装置は、公知の半導体製造に用いるいわゆるミクロファブリケーションプロセスにしたがって製造することができる。基本的には、この方法は電磁波や電子線などによるパターン露光(水銀のi,g輝線、エキシマレーザ、さらにはX線、電子線)、現像および/またはバーニングによるパターン形成、素子形成材料の配置(塗布、蒸着、スパッタ、CVDなど)、非パターン部の材料の除去(熱処理、溶解処理など)の反復操作による。

以下、本発明の実施形態を図面に基づいて詳しく説明する。

(第1実施形態)

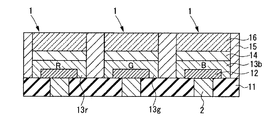

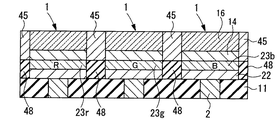

図1は、本発明の光電変換装置の第1実施形態の構成の一部を示す断面模式図である。光電変換装置は、光電変換素子1を2次元方向に多数配列された構成である。本実施形態の光電変換装置は、光電変換素子1を1つずつ有する画素を、半導体基板の表面に形成された撮像領域において2次元状に複数配列させた構成である。各画素の光電変換素子1は、入射する光のうち所定の波長の光のみを吸収して光電変換によって電荷を生成する光電変換層を備えている。光電変換層は、光電変換作用を行う有機材料を含む。本実施形態では、R(赤色),G(緑色),B(青色)の光を吸収して電荷を生成する画素をそれぞれ備えた構成を例に説明している。図1では、Rの画素、Gの画素、Bの画素を並べた3画素分のみを示している。

図1は、本発明の光電変換装置の第1実施形態の構成の一部を示す断面模式図である。光電変換装置は、光電変換素子1を2次元方向に多数配列された構成である。本実施形態の光電変換装置は、光電変換素子1を1つずつ有する画素を、半導体基板の表面に形成された撮像領域において2次元状に複数配列させた構成である。各画素の光電変換素子1は、入射する光のうち所定の波長の光のみを吸収して光電変換によって電荷を生成する光電変換層を備えている。光電変換層は、光電変換作用を行う有機材料を含む。本実施形態では、R(赤色),G(緑色),B(青色)の光を吸収して電荷を生成する画素をそれぞれ備えた構成を例に説明している。図1では、Rの画素、Gの画素、Bの画素を並べた3画素分のみを示している。

赤色の光を検出する光電変換素子1は、Si等の半導体基板(基板)上に形成された層間絶縁膜11と、該層間絶縁膜11上に形成された下部電極12と、下部電極12の上方に形成された光電変換層13rと、光電変換層13rの上方に形成された上部電極14とを含んで構成されている。緑色の光を検出する光電変換素子1は、Si等の層間絶縁膜11と、該層間絶縁膜11上に形成された下部電極12と、下部電極12の上方に形成された光電変換層13gと、光電変換層13gの上方に形成された上部電極14とを含んで構成されている。青色の光を検出する光電変換素子1は、Si等の層間絶縁膜11と、該層間絶縁膜11上に形成された下部電極12と、下部電極12の上方に形成された光電変換層13bと、光電変換層13bの上方に形成された上部電極14とを含んで構成されている。なお、以下の実施形態で説明する光電変換装置は、光電変換素子1が中間層を光電変換層のみからなる層で構成されている場合を例に説明している。

層間絶縁膜11には、下部電極12の下面に接触するビアプラグ2が設けられている。ビアプラグ2は、下部電極12を半導体基板内に形成された図示しない基板内配線(駆動回路)に電気的に接続する接続部として機能する。駆動回路は電極から読出した電荷に応じた信号を出力する機能を有する、例えばCCD型又はCMOS型の読出回路を含む。

本実施形態の光電変換装置は、隣り合う画素同士の間に、導電性の隔壁15を備えている。隔壁15は、各画素の上部電極14の水平方向端部に接触している。隔壁15の上部(光入射側の端部)が上部電極14よりも層間絶縁膜11に対して高く設けられている。言い換えると、上部電極14の上面が隔壁15の上部よりも半導体基板側に近い位置となるように形成されている。

各画素の上部電極14には、入射する光に対して透光性を有する透明絶縁膜16が積層され、該透明絶縁膜16が該画素ごとに隔壁15によって区画された状態で設けられている。本実施形態の光電変換装置では、画素ごとに光電変換素子の光電変換層13r,13g,13bが、画素間の隔壁15と上部電極14上の透明絶縁膜16とによって封止されている。

光電変換装置の基本動作としては、上部電極14と下部電極12との間にバイアス電圧を印加した状態で、上部電極14側から光が入射すると、各画素の光電変換層13r,13g,13bで光電変換によって電荷(正孔及び電子)が生成される。そして、生成された電荷のうち、上部電極14及び下部電極12のうち一方に正孔が捕集され、他方に電子が捕集される。各画素の下部電極12に捕集された電荷は、ビアプラグ2を介して半導体基板内の読み出し回路によって読出される。光電変換装置をイメージセンサとして用いる場合には、各画素から読出した電荷に応じて画像信号を生成する。

図2は、第1実施形態の光電変換装置の変形例を示す図である。図2に示す光電変換装置では、各光電変換素子1の光電変換層13が隔壁と接触せずに、下部電極12を覆うように形成されている。また、光電変換層13の上面及び側面が、上部電極14に覆われ、該上部電極が隔壁15に接触している。こうすれば、上部電極14と下部電極12との間に電界をかけた場合に、光電変換層13の端部と中央部とにかけられる電界をより均一にすることができる。このため、光電変換装置をデジタルスチルカメラ等のイメージセンサとして用いた場合に、残像を低減することができる。

次に、第1実施形態の光電変換装置の製造方法を説明する。図3は、第1実施形態の光電変換装置の製造方法の手順を説明する断面模式図である。なお、下記光電変換装置の製造方法の手順の説明において、図1に示す光電変換装置の構成を適宜参照するものとする。

図3(a)に示すように、層間絶縁膜11上に、画素ごとに下部電極12を形成する。下部電極12は、層間絶縁膜11に形成されたビアプラグ2と接触する。ビアプラグ2は、半導体基板内に設けられた基板内配線に電気的に導通している。基板内配線としては、例えば、Si基板内に形成されたCMOS型の読出回路を形成することができる。下部電極12は、既存の半導体微細加工技術(光リソグラフィ・ナノインプリント・レーザ描画や電子線描画による熱リソグラフィ等)を用いて形成することができる。下部電極12を構成する材料は、光電変換素子1の構成に対応して導電膜を適宜利用することができる。例えば、画素ピッチを2.0μmとし、各画素の下部電極12を1.6μm角にパターニングする。本実施形態の光電変換素子は、受光して励起子を生成した光電変換層から下部電極12に正孔を捕集する、いわゆる、正孔読出素子とすることができ、この場合には、下部電極12の材料にITOを利用する。ITOの下部電極12は、例えば膜厚50nmとし、HIを使用した乾式エッチングでパターニングして形成することができる。

図3(b)に示すように、下部電極12を形成した後、隔壁15となる導電性材料を成膜する。このとき、導電性材料を、図1に示す光電変換装置における、光電変換素子1の厚さと透明絶縁膜16の厚さとの総膜厚と略同等となるような膜厚で成膜する。導電性材料は、光電変換素子1の構成に対応したものを適宜利用できる。ここで、光電変換素子1が光電変換層13r,13g,13bで生成した正孔を下部電極12に捕集する構成の場合には、隔壁15を構成する導電性材料の仕事関数の値が上部電極(例えば、仕事関数4.5eVのITOとする。)14の仕事関数の値より小さくすることが好ましく、反応性イオンエッチングなど異方性エッチングが容易で仕事関数が略同等のMoや仕事関数がより小さいAlがより好ましく、不純物ドーピングで仕事関数(フェルミ準位)の調整が容易で異方性エッチングにも適するn+形多結晶Si(n+形poly‐Si)が特に好ましい。

隔壁15を構成する導電性材料としてAlを用いる場合には、TiN上にAlを成膜し更にその上にTiNを再び成膜する事がAl膜の耐久性が向上するので好ましい。成膜は、各材料に対応した成膜技術を適宜利用する。例えば、n+形poly‐Siを隔壁材料として使用した場合、非晶質SiをプラズマCVDで1μm成膜した後にエキシマレーザを照射して多結晶Siに変化させ更に燐ドーピングでn+形poly‐Siにすることができる。

光電変換素子が光電変換層13r,13g,13bで生成した電子を下部電極12に捕集する構成の場合には、上記の光電変換素子構成とは逆に、隔壁15の仕事関数の値が上部電極14の仕事関数の値より大きいことが好ましい。具体的には、ITOの上部電極14の仕事関数以上である導電膜を隔壁に使用する事が好ましく、反応性イオンエッチングなど異方性エッチングが容易で、仕事関数が略同等のMoが好ましく、不純物ドーピングで仕事関数(フェルミ準位)の調整が容易で異方性エッチングにも適するp+形多結晶Si(p+形poly‐Si)が特に好ましい。

図3(c)に示すように、隔壁15を構成する導電性材料を成膜した後、G画素を形成する領域以外をレジスト膜Rで覆い、G画素を形成する領域の、隔壁15を構成する導電性材料の膜をエッチングにより除去し、開口を設ける。この開口の形成には、公知の半導体微細加工技術を利用できる。レジスト材料は、各微細加工技術に対応した材料を適宜利用する。導電性材料のエッチングは、高精細な異方性エッチング条件が可能な反応性イオンエッチングなどの乾式エッチングが好ましい。先に作製した下部電極12の表面が完全に露出するまでエッチングを行なう。レジスト膜Rは、後の工程でリフトオフする際の剥離層として利用するためエッチング直後に除去せずに次工程の有機光電変換材料を含む光電変換層の作製に進む。例えば、隔壁15の導電性材料がn+形poly‐Siである場合には、Cl2を使用した反応性イオンエッチングによって、G用画素を形成する部分に1.8μm角で開口を設ける。

図3(d)に示すように、開口を設けた領域に光電変換層13g、上部電極14、透明絶縁膜16をこの順に成膜する。光電変換層13gは、有機光電変換材料に対応した成膜方法を適宜利用できるが、この後に成膜する上部電極14と隔壁15の導電膜が確実に電気的接続が出来るように、又、透明絶縁膜16と隔壁15も封止を確実にするため隙間なく接触するように隔壁15の側面に光電変換層13gを構成する材料が付着しない異方性成膜が可能な蒸着などのPVD法が好ましい。例えば、G用有機光電変換素子の光電変換層13gとして、例えば、下から順に、化合物1:(膜厚)150nm/キナクリドン:(膜厚)100nm/酸化珪素:(膜厚)30nmを真空度1×10−4Pa未満で真空蒸着することができる。

上部電極14は、特に駆動回路を基板内に作込んだ能動素子基板(アクティブマトリクス)を使用した光電変換装置では、上部電極14側から受光および/または発光するので透明導電膜を選択する。また、上部電極14としては、有機光電変換素子に対応する透明導電材料を適宜利用する。上部電極14の成膜方法は、各透明導電膜に対応した成膜技術を利用するが、隔壁15の導電膜と電気的に確実に接続されるためにスパッタなどのPVD法や各CVD法等の等方性成膜が可能な成膜方法が好ましい。例えば、上部透明電極としてITO:(膜厚)10nmを、Arガスを導入した真空度1Paの、ITO対向ターゲットを使用したスパッタで成膜する。

透明絶縁膜16は、外気に曝露すると顕著に劣化する真空蒸着法等で作製した有機発光ダイオード(有機LED)や有機光電変換素子を封止可能な酸化アルミニウム・酸化珪素・窒化珪素・窒化酸化珪素等の透明絶縁膜をスパッタなどのPVD法やプラズマCVD法・触媒CVD法・原子層堆積(ALD)法等で成膜する事が好ましい。例えば、プラズマCVD法によりSiH4とN2を導入した真空度10Paで窒化珪素0.6μmを成膜する。

本実施形態の光電変換層13r,13g,13b、上部電極14、透明絶縁膜16を成膜する工程は、真空中および/またはAr・N2等の不活性気体中で、基板を一切外気に曝露せず、連続して実施する事が、有機LEDや有機光電変換素子の劣化因子が混入せずに好ましい。例えば、光電変換層13r,13g,13bを成膜する真空蒸着装置と、ITOの上部電極14を成膜するスパッタ装置と、窒化珪素からなる透明絶縁膜16を成膜するプラズマCVD装置が真空度1×10−4Pa以下のクラスタ型真空搬送系にそれぞれ直結されている有機LED作製装置を使用することができる。

図3(e)に示すように、G画素以外の領域に積層された光電変換層13g、上部電極14、透明絶縁膜16を剥離するリフトオフ工程を行う。このリフトオフ工程では、隔壁15となる導電膜を開口する際に使用したレジスト膜Rを剥離することで、レジスト膜R上に積層された光電変換層13g、上部電極14・透明絶縁膜16を一括して除去する。レジスト膜Rの剥離は、使用したレジスト膜Rに対応した剥離液や、レジスト膜Rを分解するプラズマエッチングを適宜利用する。

図3(c)から図3(e)に示す工程を同様に行うことで、R画素及びB画素に対応する光電変換素子1を作製することができる。例えば、図中、破線及び矢印で示す領域に相等するR用画素の部分を開口してから、順に、化合物1:(膜厚)150nm/スクアリリウム:(膜厚)100nm/酸化珪素:(膜厚)30nm/ITO:(膜厚)10nm/窒化珪素:(膜厚)0.6μmを積層してリフトオフする。次に、破線及び矢印で示す領域に相等するB用画素の部分を開口してから順に化合物1:(膜厚)150nm/メロシアニン:(膜厚)100nm/酸化珪素:(膜厚)30nm/ITO:(膜厚)10nm/窒化珪素:(膜厚)0.6μmを積層してリフトオフする。隔壁15を構成する導電性材料の開口やリフトオフのような光リソグラフィ工程において、その工程以前に作製した画素の有機光電変換材料を含む光電変換素子は、画素ごとに層間絶縁膜11と隔壁15と透明絶縁膜16とで封止されているので外気や溶媒に素子が曝露されて劣化することがなく、このため、素子性能が低下することを防止することができる。

上記の本実施形態の光電変換装置の製造方法によれば、光リソグラフィなどの半導体微細加工技術を利用した製造工程において、各画素の有機光電変換素子を劣化させずにR用・G用・B用3種類の画素を平面上に配列したカラーイメージセンサに対応した光電変換装置を作製できる。従来のマスク蒸着やインクジェット印刷による基板上へのRGB画素のパターニングでは画素ピッチが10μm未満であると作製が極めて困難だったが、本発明では既存の半導体製造工程に利用される光リソグラフィをそのまま使用できるため、開口率60%以上を保持しつつも画素ピッチ2μm以下の高解像度な光電変換装置の作製が可能である。また、半導体製造技術の進歩による更なる画素の微細化をそのまま享受でき、より一層の画素微細化・解像度向上が将来においても可能である。

また、本実施形態の光電変換装置は、隔壁15を設けることで、画素間の電気的クロストークを解消でき、画素微細化に制限されず解像度の向上が可能である。

さらに、光電変換装置は、特に、隔壁15の導電膜に金属を使用することで隔壁15へ入射する光を反射でき、または、多結晶Siを使用することで隔壁15へ入射する光を反射および吸収できるため、画素間の光学的クロストーク(混色)を解消でき、画素微細化に制限されず解像度の向上が可能である。

また、本実施形態の光電変換装置は、隔壁15を設けることで、画素間の電気的クロストークを解消でき、画素微細化に制限されず解像度の向上が可能である。

さらに、光電変換装置は、特に、隔壁15の導電膜に金属を使用することで隔壁15へ入射する光を反射でき、または、多結晶Siを使用することで隔壁15へ入射する光を反射および吸収できるため、画素間の光学的クロストーク(混色)を解消でき、画素微細化に制限されず解像度の向上が可能である。

本発明の光電変換装置では、複数の画素が、R光を光電変換する光電変換素子を含む赤色画素と、G光を光電変換する光電変換素子を含む緑色画素と、B光を光電変換する光電変換素子を含む青色画素と、を含む構成とした。しかし、複数の画素の構成としてはこれに限定されず、例えば、複数の画素が、第1の波長の電磁波を光電変換する光電変換素子を含む第1の画素と、第2の波長の電磁波を光電変換する光電変換素子を含む第2の画素と、を含んで構成されていてもよい。こうすれば、それぞれ波長の異なる複数の赤外線を各画素で電荷検出することができる。

また、本発明の光電変換装置は、各画素が、1つの光電変換層のみを有する構成としたがこれに限定されない。例えば、第1の波長の電磁波を光電変換する光電変換素子と第2の波長の電磁波を光電変換する光電変換素子とを有する構成とすることができる。例えば、画素が、赤色光を光電変換する光電変換素子と緑色光を光電変換する光電変換素子と青色光を光電変換する光電変換素子とを有することができる。こうすれば、一つの画素で、異なる波長域の光を検出することができる。

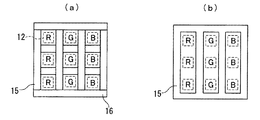

図4は、光電変換装置の隔壁の構成例を示す模式的な平面図である。図4(a)及び図4(b)はそれぞれ、半導体基板を光の入射側から視た状態の一部を示している。

図4(a)は、1列に並べられた複数の画素からなる画素列を隔壁で区画した例を示している。図4(a)では、同色の画素を3個づつ画素列とし、各画素列同士の間に隔壁15を介してストライプ状に並べた状態である。各画素列の列方向の端部(図4(a)において上下方向の端部)は、隔壁15が設けられず、透明絶縁膜16が、各画素列の上面と隔壁15が設けられていない端部とに形成されている。画素列を構成する画素の数は、3個に限定されず、任意の数の画素で画素列を構成してもよい。

図4(a)は、1列に並べられた複数の画素からなる画素列を隔壁で区画した例を示している。図4(a)では、同色の画素を3個づつ画素列とし、各画素列同士の間に隔壁15を介してストライプ状に並べた状態である。各画素列の列方向の端部(図4(a)において上下方向の端部)は、隔壁15が設けられず、透明絶縁膜16が、各画素列の上面と隔壁15が設けられていない端部とに形成されている。画素列を構成する画素の数は、3個に限定されず、任意の数の画素で画素列を構成してもよい。

図4(b)は、1列に並べられた複数の画素からなる画素列を隔壁で区画した別の例を示している。図4(b)では、同色の画素を3個づつ画素列とし、各画素列同士の間に隔壁15を介してストライプ状に並べた状態とし、各画素列の列方向の端部にも隔壁15を設けている。透明絶縁膜16が、隔壁15が設けられていない領域、つまり、各画素列の上面全体に形成されている。画素列を構成する画素の数は、3個に限定されず、任意の数の画素で画素列を構成してもよい。

図5は、光電変換装置の隔壁の構成例と各画素の配置例を示す模式的な平面図である。図5(a)及び図5(b)はそれぞれ、半導体基板を光の入射側から視た状態の一部を示している。

図5(a)及び図5(b)に示すように隔壁15は、光の入射側から視て井桁状に形成することができ、このとき、各画素が隔壁15によってそれぞれ隔離されて配列される。図5(a)は、RGB画素がいわゆるベイヤー配列を有し、G画素2つとB画素及びR画素1つづつからなる2×2画素の配置が、2次元平面に繰り返される配列である。図5(b)は、同色の画素のみを一列に配置し、Rの画素の列、Gの画素の列、Bの画素の列、Rの画素の列、、、と行方向に繰り返される配列である。このように、隔壁15を井桁状に形成することで、ベイヤー配列などの任意の画素配列が可能である。

図5(a)及び図5(b)に示すように隔壁15は、光の入射側から視て井桁状に形成することができ、このとき、各画素が隔壁15によってそれぞれ隔離されて配列される。図5(a)は、RGB画素がいわゆるベイヤー配列を有し、G画素2つとB画素及びR画素1つづつからなる2×2画素の配置が、2次元平面に繰り返される配列である。図5(b)は、同色の画素のみを一列に配置し、Rの画素の列、Gの画素の列、Bの画素の列、Rの画素の列、、、と行方向に繰り返される配列である。このように、隔壁15を井桁状に形成することで、ベイヤー配列などの任意の画素配列が可能である。

(第2実施形態)

図6は、本発明の光電変換装置の第2実施形態の構成の一部を示す断面模式図である。なお、以下に説明する各実施形態において、すでに説明した部材などと同等な構成・作用を有する部材等については、図中に同一符号又は相当符号を付すことにより、説明を簡略化あるいは省略する。

図6は、本発明の光電変換装置の第2実施形態の構成の一部を示す断面模式図である。なお、以下に説明する各実施形態において、すでに説明した部材などと同等な構成・作用を有する部材等については、図中に同一符号又は相当符号を付すことにより、説明を簡略化あるいは省略する。

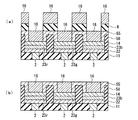

本実施形態の光電変換装置は、導電性材料で構成された隔壁25が、層間絶縁膜11側に設けられた下層壁部25aと、下層壁部25aの上に連設され、該下層壁部25aよりも画素側から退避するように寸法が変化した上層壁部25bとを有する。具体的には、上層壁部25bは、図6に示すように隣り合う画素同士の断面を視た状態で、上層壁部25bの水平方向の幅寸法が、下層壁部25aの水平方向の幅寸法よりも小さくなるように形成されている。また、下層壁部25aの側面には光電変換層13r,13g,13bのみが接触し、下層壁部25aと上層壁部25bと連接する部位に形成された段に上部電極14の端部の下面が接触し、該上部電極14の端部側面が上層壁部25bに接触している。こうすれば、隔壁25と上部電極14との接触面積を増大することができ、電気的接続が確実になる。

本実施形態の光電変換装置は、隔壁25と上部電極14との接触面積が、上記第1実施形態の光電変換装置の構成に比べて大きくなるため、電気的接続をより一層確実に行うことができる。

次に、本実施形態の光電変換装置の製造方法を説明する。なお、下記光電変換装置の製造方法の手順の説明において、図6に示す光電変換装置の構成を適宜参照するものとする。

最初に、層間絶縁膜11上に下部電極12を形成する。下部電極12の構成及び該下部電極12を形成する手順は、上記第1実施形態の光電変換装置の製造方法で説明したものと同じである。

次に、隔壁25となる導電性材料を成膜する。このとき、隔壁25を導電性材料からなる膜を2層構造(下層壁部25a/上層壁部25b)にして、特に、下層壁部25aの幅寸法を上層壁部25bの幅寸法より大きくすることで、隔壁25と上部電極14との接触面積を大きくなるように形成し、より確実な電気的接続を可能にする。下層壁部25aの層間絶縁膜11からの高さは、光電変換層13r,13g,13bの上面の高さと略同等になるように成膜する。上層壁部25bの上面は各光電変換素子1の透明絶縁膜16の上面の高さと略同等の厚さまで成膜する。下層壁部25aの材料は、光電変換素子に対応して各導電膜を適宜利用できる。例えば、光電変換層で生成した正孔を前記下部電極に捕集する構成とし、上部電極14にITO(仕事関数4.5eV)を使用する。下層壁部25aの導電性材料はこの仕事関数以下の各導電材料が好ましい。上層壁部25bがエッチング用マスクの役割を果たすので、隔壁25が同一の導電性材料を用いて1層で形成する場合に比べて材料の制限が少ない。上層壁部25bの材料は、下層壁部25aの材料と同一でもかまわないが、下層壁部25aの幅寸法より小さくする為にはエッチングしやすいように異なる材料を利用する方が好ましい。例えば、下層壁部25aとしてTi(仕事関数4.3eV)を成膜し、上層壁部25bとしてAlを積層することができる。

次に、画素を形成する領域に成膜された導電性材料にエッチングして開口を設ける。このとき、公知の半導体微細加工技術を利用できる。エッチングの際に、開口を設ける領域以外の領域にレジスト膜を形成する。レジスト材料は、各微細加工技術に対応した材料を適宜利用する。隔壁25を構成する材料は、高精細な異方性エッチング条件が可能な反応性イオンエッチングなどの乾式エッチングが好ましい。上層壁部25bのエッチングは、上層壁部25bの幅寸法を小さくするため、レジスト膜下方の上層壁部25bもエッチングされるよう、異方性エッチング条件だけではなく、等方性エッチングも行なえるようなガス種を選択する事が好ましい。または、上層壁部25bと下層壁部25aを同じガス種で異方性エッチングを行なうが、上層壁部25bのエッチング速度がより大きい条件で行なう事も好ましい。上層壁部25bと下層壁部25aを順に異方性エッチングし(ガス種・条件は同じでも異なっていてもかまわない。)、その後に上層壁部25bだけ等方性エッチングし幅を細くする事も可能である。先に作製した下部電極12の表面が完全に露出するまでエッチングを最終的に行なう。レジスト膜は、後の工程でリフトオフする際の剥離層として利用するためエッチング直後に除去せずに次工程の有機光電変換材料を含む光電変換層13r,13g,13bの作製に進む。例えば、隔壁25を構成する材料をTi/Alの2層構造とし、AlのエッチングではBCl3・Cl2・N2を使用し、その後にTiのエッチングでCl2・N2を使用して反応性イオンエッチングを行なう。Tiのエッチングの際もAlはエッチングされるので開口終了時にはAlの上層壁部25bがTiの下層壁部25aよりも幅が細くできる。画素を形成する部分に、Tiの下層壁部25aが1.8μm角の開口になるようにエッチングする。

開口を形成した後、上述した第1実施形態の光電変換装置の製造方法と同様の手順によって、各画素ごとに、光電変換層13r,13g,13b、上部電極14、透明絶縁膜16を形成する。こうすることで、本実施形態の光電変換装置を得ることができる。

上記の本実施形態の光電変換装置の製造方法によれば、半導体微細加工技術を利用した製造工程において、各画素の有機材料を含む光電変換素子を劣化させずに光電変換装置を作製でき、高解像度な光電変換装置の作製が可能である。また、半導体製造技術の進歩による更なる画素の微細化をそのまま享受でき、より一層の画素微細化・解像度向上が将来においても可能である。

(第3実施形態)

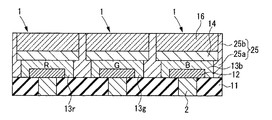

図7は、本発明の光電変換装置の第3実施形態の構成の一部を示す断面模式図である。

図7は、本発明の光電変換装置の第3実施形態の構成の一部を示す断面模式図である。

本実施形態の光電変換装置は、隔壁35が導電性材料で構成され、下層壁部35aと、該下層壁部35aの上に連接され、該下層壁部35aよりも画素側に突出するように幅寸法が変化した上層壁部35bとを有し、下層壁部35a及び上層壁部35bが上部電極14と接触する。具体的には、上層壁部35bは、図7に示すように隣り合う画素同士の断面を視た状態で、上層壁部35bの水平方向の幅寸法が、下層壁部35aの水平方向の幅寸法よりも大きくなるように形成されている。また、下層壁部35aの側面には上部電極14の端部側面と光電変換層13r,13g,13bが接触し、下層壁部35aと上層壁部35bと連接する部位に形成された段に上部電極14の端部の上面が接触し、該上部電極14の端部側面が下層壁部35aに接触している。

本実施形態の光電変換装置は、隔壁35と上部電極14との接触面積が、上記第1実施形態の光電変換装置の構成に比べて大きくなるため、電気的接続をより一層確実に行うことができる。

次に、本実施形態の光電変換装置の製造方法を説明する。図8及び図9は、第3実施形態の光電変換装置の製造方法の手順を説明する断面模式図である。なお、下記光電変換装置の製造方法の手順の説明において、図7に示す光電変換装置の構成を適宜参照するものとする。

図8(a)に示すように、最初に、ビアプラグ2を形成した層間絶縁膜11に、下部電極12を形成する。下部電極12の構成及び該下部電極12を形成する手順は、上記第1実施形態の光電変換装置の製造方法で説明したものと同じである。

図8(b)に示すように、層間絶縁膜11及び下部電極12の上に、隔壁35を構成する導電性材料(第1の導電性材料)を成膜する。その後、図8(c)に示すように、G画素を形成する領域に応じて第1の開口を設ける。導電性材料の構成及び該導電性材料を成膜する手順は、上記第1実施形態と同様の手順を用いることができる。第1の開口を設ける手順は、上記第1実施形態の開口を設ける手順と同じ手順を用いることができる。

第1の開口を設けた後、図8(d)に示すように、G画素に対応する第1の開口に、光電変換層13g、上部電極14を順に成膜する。光電変換層13g及び上部電極14を成膜する手順は、上記第1実施形態の手順を同じである。

上部電極を成膜した後に、G画素に対応する第1の開口に、導電性材料(第2の導電性材料)を成膜する。このとき、導電性材料は、外気に曝露すると顕著に劣化する真空蒸着法等で作製した有機LEDや有機光電変換素子を封止可能な緻密な金属膜で、かつ、エッチングストッパの役割を担う上部電極14がエッチングされない条件でエッチングされる金属膜でなくてはならない。反応性イオンエッチングなど異方性エッチングが容易な金属膜でもあるAlやMo等の金属をスパッタなどのPVD法や各種CVD法で成膜する事が好ましい。例えば、CVD法によりMoを0.6μm成膜する。

本実施形態の光電変換層13r,13g,13b、上部電極14、第2の導電性材料の成膜工程は、真空中および/またはAr・N2等の不活性気体中で、基板を一切外気に曝露せず、連続して実施する事が、有機LEDや有機光電変換素子の劣化因子が混入せずに好ましい。本実施形態では、例えば、光電変換層13r,13g,13bを成膜する真空蒸着装置と、ITOの上部電極14を成膜するスパッタ装置と、Mo導電膜を成膜するCVD装置が真空度1×10−4Pa以下のクラスタ型真空搬送系にそれぞれ直結されている有機LED作製装置を使用する。

次に、G画素以外の領域に積層された、つまり、第1の導電性材料の上に積層された光電変換層13g、上部電極14、第2の導電性材料を剥離するリフトオフ工程を行う。このリフトオフ工程では、隔壁35となる第1の導電性材料の膜に開口を設ける際に使用したレジスト膜Rを剥離する事で、レジスト膜R上に積層された光電変換層13g,上部電極14,第2の導電性材料を該レジスト膜Rとともに一括して除去する。レジスト膜Rの剥離は、使用したレジスト膜Rに対応した剥離液や、レジスト膜Rを分解するプラズマエッチングを適宜利用する。

図8(b)から(d)及び図9(a)に示す工程を同様に行なうことで、図9(b)のようにR画素及びB画素に対応する光電変換素子1を作製することができる。隔壁35を構成する導電性材料の第1の開口の形成やリフトオフのような光リソグラフィ工程において、その工程以前に作製した画素の光電変換素子は層間絶縁膜11と隔壁35と導電性材料35で封止されているので外気や溶媒に素子が曝露されず素子性能が劣化しない。

隔壁35の導電性材料の膜と上部電極14の接触面積を大きくするため、上部電極14より上に位置する隔壁35の導電性材料の幅寸法が下方より大きくなるように、第1の開口より小さい第2の開口を形成する。具体的には、図8(c)で示す工程の各画素に対応する第1の開口より開口面積が小さく、かつ、各画素の第1の開口に成膜された上部電極14上に導電性材料を一部残すように第2の開口を形成し、隔壁35の上層壁部35bが上部電極14の上に突出して該上層壁部35bの幅寸法が大きくなる。工程としては、RGB全画素作製後に、封止膜として利用した上部電極14上の導電性材料の膜に第2の開口を各画素ごとに設ける。このとき、公知の半導体微細加工技術を利用できる。レジスト材料は、各微細加工技術に対応した材料を適宜利用する。エッチングは、高精細な異方性エッチング条件が可能な反応性イオンエッチングなどの乾式エッチングが好ましい。レジスト膜Rは、後の工程でリフトオフする際の剥離層として利用するためエッチング直後に除去せずに次工程の透明絶縁膜16の成膜に進む。例えば、上部電極14上の導電性材料の膜にMoを成膜した場合はMoのエッチングではCF4・O2を使用し反応性イオンエッチングを行なうことができる。ITOの上部電極14が露出するとエッチングが終了する。第2の開口が、その中心を第1の開口の中心と同じになるように、1.6μm角でエッチングする。こうすると、上部電極14上の隔壁35の上層壁部35bの幅寸法が下層壁部35aの幅寸法より0.2μm大きくなり、ITOの上部電極14と隔壁35との接触面積が大きくなり、より確実に電気的接続が可能になる。

第2の開口を形成した後、図9(d)に示すように、各画素の光電変換素子を封止するため、透明絶縁膜16をそれぞれの第2の開口に成膜する。透明絶縁膜16は、有機LEDや有機光電変換素子を封止可能な酸化アルミニウム・酸化珪素・窒化珪素・窒化酸化珪素等の透明絶縁膜をスパッタなどのPVD法やプラズマCVD法・触媒CVD法・ALD法等で成膜する事が好ましい。最後に、隔壁35上のレジスト膜Rを剥離する事で、レジスト膜Rと該レジスト膜R上に成膜された透明絶縁膜16をリフトオフする。例えば、プラズマCVD法により窒化珪素0.6μmを成膜することができる。こうすることで、図9(e)に示すように、本実施形態の光電変換装置を得ることができる。

上記の本実施形態の光電変換装置の製造方法によれば、半導体微細加工技術を利用した製造工程において、各画素の有機材料を含む光電変換素子を劣化させずに光電変換装置を作製でき、高解像度な光電変換装置の作製が可能である。また、半導体製造技術の進歩による更なる画素の微細化をそのまま享受でき、より一層の画素微細化・解像度向上が将来においても可能である。

(第4実施形態)

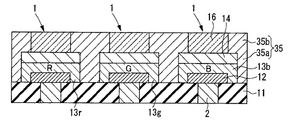

図10は、本発明の光電変換装置の第4実施形態の構成の一部を示す断面模式図である。

図10は、本発明の光電変換装置の第4実施形態の構成の一部を示す断面模式図である。

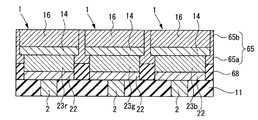

本実施形態の光電変換装置は、層間絶縁膜11と隔壁45との間に絶縁性材料から構成された絶縁膜48が形成されている。絶縁膜48によって隣り合う画素の下部電極22同士を離間する。具体的には、各画素の上部電極14の端部側面が導電性材料で構成された隔壁45に接触し、光電変換層23r,23g,23b及び下部電極22の端部側面が絶縁膜48に接触する。上部電極14上には、透明絶縁膜16が形成され、また、隔壁45が、その上端が該透明絶縁膜16の上面と略等しい位置になるように形成されている。また、画素それぞれの上部電極14と光電変換層23r,23g,23bと下部電極22とが、光の入射側から視て(図10の上方から視て)、等しい面積で、かつ、重なるように配置されている。

本実施形態の光電変換装置の構成によれば、下部電極22と光電変換層23r,23g,23bと上部電極14の面積が略同等に出来るので、光電変換層23r,23g,23bに掛かる電界を均一にでき、デジタルスチルカメラなどの撮像装置に適用した場合に残像が解消される効果がある。また、光電変換層23r,23g,23bに掛かる電界を均一にすることで、素子の短絡不良が解消される。さらに、下部電極22と光電変換層23r,23g,23bと上部電極14の面積が略同等に出来るので、各画素が形成された開口部分すべてが光電変換素子の有効面積となり、開口率が最大となる。ここで、絶縁膜48は隔壁45と光電変換素子の下部電極22を絶縁する役割を担う。一方で隔壁45と光電変換素子の上部電極14との電気的接続を妨げないために、絶縁膜48の膜厚は、下部電極22の膜厚より厚く、光電変換素子の総膜厚(下部電極22と光電変換層23r,23g,23bと上部電極14の合計膜厚)よりは薄くなくてはならない。絶縁膜48の膜厚は、下部電極22と光電変換層23r,23g,23bとの合計膜厚より薄い方が好ましい。

次に、本実施形態の光電変換装置の製造方法を説明する。図11は、第4実施形態の光電変換装置の製造方法の手順を説明する断面模式図である。なお、下記光電変換装置の製造方法の手順の説明において、図10に示す光電変換装置の構成を適宜参照するものとする。

図11(a)に示すように、ビアプラグ2を各画素ごとに設けた層間絶縁膜11に、絶縁膜48を構成するための絶縁性材料と、隔壁45を構成するための導電性材料とを順に重ねて成膜する。

絶縁膜48は、下部電極22と導電性材料45の膜の電気的絶縁だけでなく、各画素を構成する光電変換素子を封止する保護膜としての機能も要求される。絶縁膜48は、透明絶縁膜16と同様に、有機LEDや有機光電変換素子の保護膜として利用されている酸化アルミニウム・酸化珪素・窒化珪素・窒化酸化珪素等の透明絶縁膜をスパッタなどのPVD法やプラズマCVD法・触媒CVD法・ALD法等で成膜する事が好ましい。例えば、基板の層間絶縁膜が窒化珪素の場合、開口の際に窒化珪素がエッチングされない条件でエッチング可能な酸化珪素0.2μmをCVD法で成膜することができる。

絶縁膜48は、下部電極22と導電性材料45の膜の電気的絶縁だけでなく、各画素を構成する光電変換素子を封止する保護膜としての機能も要求される。絶縁膜48は、透明絶縁膜16と同様に、有機LEDや有機光電変換素子の保護膜として利用されている酸化アルミニウム・酸化珪素・窒化珪素・窒化酸化珪素等の透明絶縁膜をスパッタなどのPVD法やプラズマCVD法・触媒CVD法・ALD法等で成膜する事が好ましい。例えば、基板の層間絶縁膜が窒化珪素の場合、開口の際に窒化珪素がエッチングされない条件でエッチング可能な酸化珪素0.2μmをCVD法で成膜することができる。

隔壁45を構成する導電性材料に関しては、第1実施形態と同様のものを用いることができ、例えば、n+形poly‐Siを膜厚0.8μmで成膜することができる。

図11(b)に示すように、G画素を形成する領域の隔壁45を構成する導電性材料の膜と絶縁膜48をエッチングして開口を設ける。開口を設ける際には、上述と同じ半導体微細加工技術を利用できる。レジスト材料は、各微細加工技術に対応した材料を適宜利用する。隔壁45を構成する導電性材料の膜と絶縁膜48のエッチングとしては、高精細な異方性エッチング条件が可能な反応性イオンエッチングなどの乾式エッチングが好ましい。レジスト膜Rは、後の工程でリフトオフする際の剥離層として利用するためエッチング直後に除去せずに次工程の有機光電変換材料を含む光電変換層の作製に進む。ここでは、開口を設けた領域以外を酸化珪素/n+形poly‐Siの2層構造にするので、n+形poly‐SiのエッチングではCl2を使用し、その後に酸化珪素のエッチングでCF4・H2を使用して反応性イオンエッチングを行なうことができる。画素を形成する部分に、隔壁45を構成する導電性材料の膜と絶縁膜48を例えば1.8μm角で開口するようにエッチングする。

G画素の開口を形成した後、図11(c)に示すように、下部電極22、光電変換層23g、上部電極14、透明絶縁膜16を順に、成膜する。下部電極22を成膜する際には、隔壁45の側面と接触することで下部電極22と上部電極14とが短絡しないよう、下部電極22を成膜する材料が隔壁45の側面に付着しない蒸着やスパッタなどPVD法による異方性成膜によって下部電極22を作製する事が好ましい。例えば、スパッタによりITOを膜厚50nmで成膜することができる。

G画素以外の領域に積層された下部電極22、光電変換層23g、上部電極14、透明絶縁膜16を剥離するリフトオフ工程を行う。このリフトオフ工程では、図11(c)に示すレジスト膜Rを剥離することで、レジスト膜R上に積層された下部電極22、光電変換層23g、上部電極14、透明絶縁膜16を一括して除去する。レジスト膜Rの剥離は、使用したレジスト膜Rに対応した剥離液や、レジスト膜Rを分解するプラズマエッチングを適宜利用する。図11(b)から(c)に示す工程を、図11(d)中の矢印で示す各画素を形成する領域において同様に行うことで、R画素及びB画素に対応する光電変換素子1を作製することができる。

上記の本実施形態の光電変換装置の製造方法によれば、半導体微細加工技術を利用した製造工程において、各画素の有機材料を含む光電変換素子を劣化させずに光電変換装置を作製でき、高解像度な光電変換装置の作製が可能である。また、半導体製造技術の進歩による更なる画素の微細化をそのまま享受でき、より一層の画素微細化・解像度向上が将来においても可能である。

また、上記手順によれば、絶縁膜48に区画された開口に下部電極22を成膜するため、上記実施形態のように先に層間絶縁膜11上に下部電極22のパターニング工程を行なう必要がなく、工程数を削減することができる。

次に、本実施形態の光電変換装置の製造方法の他の例を説明する。図12は、第4実施形態の光電変換装置の製造方法の他の例の手順を説明する断面模式図である。なお、下記光電変換装置の製造方法の手順の説明において、図10に示す光電変換装置の構成を適宜参照するものとする。

図12(a)に示すように、半導体基板上に所定の厚さの層間絶縁膜11を形成する。

層間絶縁膜11における、基板内回路と接続するビアプラグ2を作製する位置に第1の孔11aを開口するため、層間絶縁膜11をパターニングする。層間絶縁膜11をエッチングした後にレジストを剥離する。第1の孔11aを開口する際には、汎用的な半導体製造工程を適宜利用する。

次に、層間絶縁膜11のRGB各画素を形成する領域に対応する第2の孔11bを開口するため、レジストパターンを作製する。第2の孔11bを開口する際には、汎用的な半導体製造工程を適宜利用することができ、例えば、各画素の位置に1.8μm角の第2の孔11bが出来るようレジストパターンを形成する。

層間絶縁膜11における、基板内回路と接続するビアプラグ2を作製する位置に第1の孔11aを開口するため、層間絶縁膜11をパターニングする。層間絶縁膜11をエッチングした後にレジストを剥離する。第1の孔11aを開口する際には、汎用的な半導体製造工程を適宜利用する。

次に、層間絶縁膜11のRGB各画素を形成する領域に対応する第2の孔11bを開口するため、レジストパターンを作製する。第2の孔11bを開口する際には、汎用的な半導体製造工程を適宜利用することができ、例えば、各画素の位置に1.8μm角の第2の孔11bが出来るようレジストパターンを形成する。

次に、層間絶縁膜11を再度エッチングする。その後、第2の孔11bに作製する画素に対応した、光電変換素子の下部電極22と上部電極14とをそれぞれ電気的に絶縁できるように、かつ、この後に作製する隔壁45と上部電極14の電気的接続を妨げないように、層間絶縁膜11をエッチングする。このとき、層間絶縁膜11をエッチングする深さは、下部電極22の膜厚より厚く、光電変換素子の総膜厚(下部電極22と光電変換層23gと上部電極14の合計膜厚)よりは浅くなくてはならない。下部電極22と光電変換層23gの合計膜厚より浅い方が好ましい。層間絶縁膜11をエッチングした後にレジスト膜Rを剥離する。ここでは、汎用的な半導体製造工程を適宜利用できる。

図12(b)に示すように、層間絶縁膜11上に、ビアプラグ2を形成するために配線金属などの導電性材料を成膜する。第1の孔11aに欠陥なく導電性材料を埋込むことと、隔壁45の導電性材料の膜として利用することを両立させる為に、ITOと仕事関数が略同等でもあるMoやWのCVD法による成膜が好ましい。層間絶縁膜11との反応を防止する為に、MoやWの成膜前にTiNをCVD法で成膜する事が半導体製造工程では一般的に行なわれている。例えば、第1の孔11a及び第2の孔11bを完全に埋込んだ状態でかつ層間絶縁膜11上に厚さ0.6μmになるまでMoを成膜することができる。

図12(c)に示すように、G画素を形成する領域の導電膜材料をエッチングし、第1の孔11bに相等する開口を設ける。このとき、上述した半導体微細加工技術を利用できる。レジスト材料は、各微細加工技術に対応した材料を適宜利用する。隔壁45を構成する材料は、高精細な異方性エッチング条件が可能な反応性イオンエッチングなどの乾式エッチングが好ましい。先に作製した層間絶縁膜11の第2の孔11b内の底面が露出するまでエッチングを行なうが、ビアプラグ2と下部電極12の接触面積を大きくするために、第2の孔11b内の導電膜材料を例えば0.1μm以下の厚さで残してエッチングを終了してもかまわない。レジスト膜Rは、後の工程でリフトオフする際の剥離層として利用するためエッチング直後に除去せずに次工程の有機光電変換材料を含む光電変換層23gの作製に進む。ここでは、隔壁45の導電膜材料がMoなので、CF4・O2を使用し、各画素を形成する部分に、隔壁45が1.8μm角で開口するようにエッチングすることができる。

G画素の開口を形成した後、図12(c)に示すように、下部電極22、光電変換層23g、上部電極14、透明絶縁膜16を順に、成膜する。下部電極22を成膜する際には、隔壁45の側面と接触することで下部電極22と上部電極14とが短絡しないよう、下部電極22を成膜する材料が隔壁45の側面に付着しない蒸着やスパッタなどPVD法による異方性成膜によって下部電極22を作製する事が好ましい。例えば、スパッタによりITOを膜厚50nmで成膜することができる。

G画素以外の領域に積層された下部電極22、光電変換層23g、上部電極14、透明絶縁膜16を剥離するリフトオフ工程を行う。このリフトオフ工程では、図12(d)に示すレジスト膜Rを剥離することで、レジスト膜R上に積層された下部電極22、光電変換層23g、上部電極14・透明絶縁膜16を一括して除去する。レジスト膜Rの剥離は、使用したレジスト膜Rに対応した剥離液や、レジスト膜Rを分解するプラズマエッチングを適宜利用する。図12(c)から(e)に示す工程を、図12(e)中の矢印で示す各画素を形成する領域において同様に行うことで、R画素及びB画素に対応する光電変換素子1を作製することができる。

上記の本実施形態の光電変換装置の製造方法によれば、半導体微細加工技術を利用した製造工程において、各画素の有機材料を含む光電変換素子を劣化させずに光電変換装置を作製でき、高解像度な光電変換装置の作製が可能である。また、半導体製造技術の進歩による更なる画素の微細化をそのまま享受でき、より一層の画素微細化・解像度向上が将来においても可能である。また、半導体基板内の駆動回路と画素の下部電極を接続するビアプラグ2と隔壁45を構成する導電性材料の膜を同時に成膜することができるため、更に工程数を削減することができる。

(第5実施形態)

図13は、本発明の光電変換装置の第5実施形態の構成の一部を示す断面模式図である。

本実施形態では、隣り合う画素間に絶縁膜58が設けられ、該絶縁膜58の上端が上部基板14の上面よりも高く(つまり、層間絶縁膜11より上方に離れるように)形成されている。各画素において、上部電極14の絶縁膜58側端部には、導電性材料で構成された隔壁55が形成され、該隔壁55は、隣り合う画素の両方の上部電極14と接触するように、そのうち一方の画素から隔壁55の上面にも連なって形成され、他方の画素の上部電極14の端部まで延設されている。

図13は、本発明の光電変換装置の第5実施形態の構成の一部を示す断面模式図である。

本実施形態では、隣り合う画素間に絶縁膜58が設けられ、該絶縁膜58の上端が上部基板14の上面よりも高く(つまり、層間絶縁膜11より上方に離れるように)形成されている。各画素において、上部電極14の絶縁膜58側端部には、導電性材料で構成された隔壁55が形成され、該隔壁55は、隣り合う画素の両方の上部電極14と接触するように、そのうち一方の画素から隔壁55の上面にも連なって形成され、他方の画素の上部電極14の端部まで延設されている。

本実施形態の光電変換装置は、画素それぞれの上部電極14と光電変換層23r,23g,23bと下部電極22とが、光の入射側から視て、等しい面積で、かつ、重なるように配置されている。このため、光電変換層23r,23g,23bに掛かる電界を均一にでき、光電変換装置をデジタルスチルカメラなどの撮像装置に適用した場合に残像の発生を防止でき、また、短絡不良を解消することができる。

次に、本実施形態の光電変換装置の製造方法の他の例を説明する。図14から図16は、第5実施形態の光電変換装置の製造方法の他の例の手順を説明する断面模式図である。なお、下記光電変換装置の製造方法の手順の説明において、図13に示す光電変換装置の構成を適宜参照するものとする。

図14(a)に示すように、各画素に対応してビアプラグ2が形成された層間絶縁膜11上に絶縁性材料を成膜する。該絶縁性材料の膜は、各画素の光電変換素子1を区画する絶縁膜58を構成するものである。

図14(b)に示すように、成膜した絶縁性材料上にレジスト膜Rをパターニングし、エッチングを行いG画素を形成する領域に応じて、絶縁性材料の膜に第1の開口を設ける。この第1の開口は、各画素を構成する光電変換素子を形成するための部位に相当する。

図14(c)に示すように、第1の開口及びレジスト膜R上に、下部電極22、光電変換層23g、上部電極14を順に成膜する。また、上部電極14上に導電性材料を成膜する。この導電性材料は、他の画素の光電変換素子1を形成する際の保護層として機能し、また、後の工程後に隔壁55を構成する。

図14(d)に示すように、G画素以外の領域に積層された下部電極22、光電変換層23g、上部電極14、導電性材料の膜55を剥離するリフトオフ工程を行う。このリフトオフ工程では、図14(c)に示すレジスト膜Rを剥離することで、レジスト膜R上に積層された下部電極22、光電変換層23g、上部電極14、導電性材料の膜55を一括して除去する。レジスト膜Rの剥離は、使用したレジスト膜Rに対応した剥離液や、レジスト膜Rを分解するプラズマエッチングを適宜利用する。

R画素及びB画素についても図14(b)から(d)に示す工程を同様に行うことで、図15(a)に示すように、上部電極14上が導電性材料の膜55で覆われた光電変換素子をそれぞれ作製することができる。

次に、図15(b)に示すように、各画素の上部電極14上に設けられた導電性材料の膜55及び絶縁膜58の上に、再び導電性材料の膜55を形成する。

図15(c)に示すように、導電性材料の膜55において、各画素の上方に、先の工程で設けた第1の開口より小さい開口面積の第2の開口を設ける。第2の開口は、レジスト膜Rを予めパターニングし、第2の開口を形成する領域の導電性材料をエッチングで除去することで設けることができる。第2の開口は、後の工程で、透明絶縁膜16を設ける領域である。第2の開口を形成した状態で、隔壁55の上面にレジスト膜Rが残る。

続いて、図16(a)に示すように、透明絶縁膜16を成膜する。このとき、各画素の上方の第2の開口に成膜された透明絶縁膜16の上面の位置が、画素間の隔壁55の上面の位置と略同じとする。

透明絶縁膜16を成膜した後、隔壁55上のレジスト膜Rと、該レジスト膜R上に形成された透明絶縁膜16をリフトオフ工程によって剥離する。こうして、図16(b)に示すように、各画素が隔壁55と透明絶縁膜16とによって封止された光電変換装置を構成することができる。

上記の本実施形態の光電変換装置の製造方法によれば、半導体微細加工技術を利用した製造工程において、各画素の有機材料を含む光電変換素子を劣化させずに光電変換装置を作製でき、高解像度な光電変換装置の作製が可能である。また、半導体製造技術の進歩による更なる画素の微細化をそのまま享受でき、より一層の画素微細化・解像度向上が将来においても可能である。また、下部電極22のパターニング工程を行う必要がなく、工程数を削減することができる。

(第6実施形態)

図17は、本発明の光電変換装置の第6実施形態の構成の一部を示す断面模式図である。

本実施形態の光電変換装置は、図6に示す光電変換装置又は図10に示す光電変換装置の変形例である。層間絶縁膜11と隔壁65との間に絶縁性材料から構成された絶縁膜68が形成されている。絶縁膜68によって隣り合う画素の下部電極22同士を離間する。具体的には、各画素の上部電極14の端部側面が導電性材料で構成された隔壁65に接触し、光電変換層23r,23g,23bの端部側面の一部及び下部電極22の端部側面が絶縁膜68に接触する。

図17は、本発明の光電変換装置の第6実施形態の構成の一部を示す断面模式図である。

本実施形態の光電変換装置は、図6に示す光電変換装置又は図10に示す光電変換装置の変形例である。層間絶縁膜11と隔壁65との間に絶縁性材料から構成された絶縁膜68が形成されている。絶縁膜68によって隣り合う画素の下部電極22同士を離間する。具体的には、各画素の上部電極14の端部側面が導電性材料で構成された隔壁65に接触し、光電変換層23r,23g,23bの端部側面の一部及び下部電極22の端部側面が絶縁膜68に接触する。

また、隔壁65は、下層隔壁65aと、該下層隔壁65aの上に連設され、該下層壁部65aよりも画素側から退避するように寸法が変化した上層壁部65bとから構成されている。具体的には、上層壁部65bは、図17に示すように隣り合う画素同士の断面を視た状態で、上層壁部65bの水平方向の幅寸法が、下層壁部65aの水平方向の幅寸法よりも小さくなるように形成されている。また、下層壁部65aの側面には光電変換層23r,23g,23bのみが接触し、下層壁部65aと上層壁部65bと連接する部位に形成された段に上部電極14の端部の下面が接触し、該上部電極14の端部側面が上層壁部65bに接触している。こうすることで、隔壁65と上部電極14との電気的接続を確実に行うことができる。

本実施形態では、上部電極14上には、透明絶縁膜16が形成されている。また、隔壁65は、その上端が該透明絶縁膜16の上面と略等しい位置になるように形成されている。また、上部電極14の大部分と光電変換層23r,23g,23bと下部電極22とが、光の入射側から視て(図17の上方から視て)、等しい面積で、かつ、重なるように配置されている。このため、光電変換層23r,23g,23bにかかる電界を均一にでき、光電変換装置をデジタルスチルカメラ等の撮像装置に適用した場合に、残像の発生を防止でき、素子の短絡不良を防止することができる。

絶縁膜68は、上記第4実施形態で説明した手順と同様の手順によって設けることができる。また、隔壁65は、上記第2実施形態で説明した手順と同様の手順によって設けることができる。

上記の本実施形態の光電変換装置によれば、各画素が隔壁65、絶縁膜68及び透明絶縁膜16とで封止されているため、半導体微細加工技術を利用した製造工程において、各画素の有機材料を含む光電変換素子を劣化させずに光電変換装置を作製でき、高解像度な光電変換装置の作製が可能である。また、半導体製造技術の進歩による更なる画素の微細化をそのまま享受でき、より一層の画素微細化・解像度向上が将来においても可能である。

(第7実施形態)

図18は、本発明の光電変換装置の第7実施形態の構成の一部を示す断面模式図である。

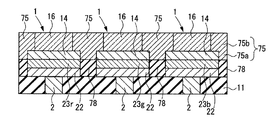

本実施形態の光電変換装置は、図7に示す光電変換装置又は図10に示す光電変換装置の変形例である。層間絶縁膜11と隔壁75との間に絶縁性材料から構成された絶縁膜78が形成されている。絶縁膜78によって隣り合う画素の下部電極22同士を離間する。具体的には、各画素の上部電極14の端部側面が導電性材料で構成された隔壁75に接触し、光電変換層23r,23g,23bの端部側面及び下部電極22の端部側面が絶縁膜78にのみ接触する。

図18は、本発明の光電変換装置の第7実施形態の構成の一部を示す断面模式図である。

本実施形態の光電変換装置は、図7に示す光電変換装置又は図10に示す光電変換装置の変形例である。層間絶縁膜11と隔壁75との間に絶縁性材料から構成された絶縁膜78が形成されている。絶縁膜78によって隣り合う画素の下部電極22同士を離間する。具体的には、各画素の上部電極14の端部側面が導電性材料で構成された隔壁75に接触し、光電変換層23r,23g,23bの端部側面及び下部電極22の端部側面が絶縁膜78にのみ接触する。

また、隔壁75は、下層隔壁75aと、該下層隔壁75aの上に連設され、該下層壁部75aよりも画素側へ突出するように寸法が変化した上層壁部75bとから構成されている。具体的には、上層壁部75bは、図18に示すように隣り合う画素同士の断面を視た状態で、上層壁部75bの水平方向の幅寸法が、下層壁部75aの水平方向の幅寸法よりも大きくなるように形成されている。また、下層壁部75aの側面には上部電極14の端部側面が接触し、下層壁部75aと上層壁部75bと連接する部位に形成された段において、上部電極14の端部の上面が上層壁部75aに接触し、上部電極14の端部側面が下層壁部75bに接触している。こうすることで、隔壁75と上部電極14との電気的接続を確実に行うことができる。

本実施形態では、上部電極14上には、透明絶縁膜16が形成されている。また、隔壁75は、その上端が該透明絶縁膜16の上面と略等しい位置になるように形成されている。また、画素それぞれの上部電極14と光電変換層23r,23g,23bと下部電極22とが、光の入射側から視て(図17の上方から視て)、等しい面積で、かつ、重なるように配置されている。このため、光電変換層23r,23g,23bにかかる電界を均一にでき、光電変換装置をデジタルスチルカメラ等の撮像装置に適用した場合に、残像の発生を防止でき、素子の短絡不良を防止することができる。

絶縁膜78は、上記第4実施形態で説明した手順と同様の手順によって設けることができる。また、隔壁75は、上記第3実施形態で説明した手順と同様の手順によって設けることができる。

上記の本実施形態の光電変換装置によれば、各画素が隔壁75、絶縁膜78及び透明絶縁膜16とで封止されているため、半導体微細加工技術を利用した製造工程において、各画素の有機材料を含む光電変換素子を劣化させずに光電変換装置を作製でき、高解像度な光電変換装置の作製が可能である。また、半導体製造技術の進歩による更なる画素の微細化をそのまま享受でき、より一層の画素微細化・解像度向上が将来においても可能である。

なお、本発明は、前述した実施形態に限定されるものではなく、適宜な変形、改良などが可能である。

例えば、本発明の光電変換装置は、デジタルスチルカメラ等の撮像装置に好適であるが、これに限定されず、有機LEDを用いた有機EL(エレクトロルミネセンス)ディスプレイなどの表示装置にも適用することができる。

例えば、本発明の光電変換装置は、デジタルスチルカメラ等の撮像装置に好適であるが、これに限定されず、有機LEDを用いた有機EL(エレクトロルミネセンス)ディスプレイなどの表示装置にも適用することができる。

1 光電変換素子

2 ビアプラグ(接続部)

11 層間絶縁膜

12,22 下部電極

13r,13g,13b 光電変換層

14 上部電極

15,25,35,45,55,65,75 隔壁

48,58,68,78 絶縁膜

23r,23g,23b 光電変換層

2 ビアプラグ(接続部)

11 層間絶縁膜

12,22 下部電極

13r,13g,13b 光電変換層

14 上部電極

15,25,35,45,55,65,75 隔壁

48,58,68,78 絶縁膜

23r,23g,23b 光電変換層

Claims (21)

- 基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置であって、

隣り合う前記画素同士の間に形成され、前記上部電極と電気的に接続された導電性の隔壁と、

前記上部電極上に設けられた透明絶縁膜とを備え、

前記画素が前記隔壁と前記透明絶縁膜とによって封止されている光電変換装置。 - 上記請求項1に記載の光電変換装置であって、

前記上部電極の上面が前記隔壁の上部よりも低く形成されている光電変換装置。 - 上記請求項1又は2に記載の光電変換装置であって、

前記上部電極が透明である光電変換装置。 - 上記請求項1から3のいずれかに記載の光電変換装置であって、

前記隔壁が光の入射側から視て井桁状に形成され、前記画素が前記隔壁によってそれぞれ隔離されて配列されている光電変換装置。 - 上記請求項1から4のいずれかに記載の光電変換装置であって、

前記隔壁が導電性で、下層壁部と、前記下層壁部の上に連接され、該下層壁部よりも画素側から退避するように寸法が変化した上層壁部とを有し、前記下層壁部及び前記上層壁部が前記上部電極と接触する光電変換装置。 - 上記請求項1から4のいずれかに記載の光電変換装置であって、

前記隔壁が導電性で、下層壁部と、前記下層壁部の上に連接され、該下層壁部よりも画素側に突出するように寸法が変化した上層壁部とを有し、前記下層壁部及び前記上層壁部が前記上部電極と接触する光電変換装置。 - 上記請求項1から6のいずれかに記載の光電変換装置であって、

隣り合う前記画素の前記下部電極同士を離間する絶縁膜が形成され、前記絶縁膜上に前記隔壁が形成される光電変換装置。 - 上記請求項1から4,6,及び7のいずれかに記載の光電変換装置であって、

前記画素それぞれの前記上部電極と前記光電変換層と前記下部電極とが、光の入射側から視て、等しい面積で、かつ、重なるように配置される光電変換装置。 - 上記請求項1から8に記載の光電変換装置であって、

前記光電変換素子が前記光電変換層で生成された電子を前記下部電極に捕集する構成であって、前記光電変換層が前記隔壁と接触し、前記隔壁の仕事関数の値が前記上部電極の仕事関数の値より大きい光電変換装置。 - 上記請求項1から8に記載の光電変換装置であって、

前記光電変換素子が前記光電変換層で生成された正孔を前記下部電極に捕集する構成であって、前記光電変換層が前記隔壁と接触し、前記隔壁の仕事関数の値が前記上部電極の仕事関数の値より小さい光電変換装置。 - 上記請求項1から10のいずれかに記載の光電変換装置であって、

前記複数の画素が、第1の波長の電磁波を光電変換する光電変換素子を含む第1の画素と、第2の波長の電磁波を光電変換する光電変換素子を含む第2の画素と、を含む光電変換装置。 - 上記請求項1から10のいずれかに記載の光電変換装置であって、

前記複数の画素が、赤色光を光電変換する光電変換素子を含む赤色画素と、緑色光を光電変換する光電変換素子を含む緑色画素と、青色光を光電変換する光電変換素子を含む青色画素と、を含む光電変換装置。 - 上記請求項1から10のいずれかに記載の光電変換装置であって、

各画素が、第1の波長の電磁波を光電変換する光電変換素子と第2の波長の電磁波を光電変換する光電変換素子とを有する光電変換装置。 - 上記請求項1から10のいずれかに記載の光電変換装置であって、

各画素が、赤色光を光電変換する光電変換素子と緑色光を光電変換する光電変換素子と青色光を光電変換する光電変換素子とを有する光電変換装置。 - 上記請求項1から14のいずれかに記載の光電変換装置を備えた撮像装置であって、

前記基板内に、前記下部電極に接続され、電荷に応じた信号を出力する駆動回路が設けられている撮像装置。 - 上記請求項15に記載の撮像装置であって、

前記駆動回路がCCD型又はCMOS型である撮像装置。 - (実施形態1)

基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)前記下部電極上に導電性材料を成膜する工程と、

(b)前記導電性材料の膜に、各画素を形成する領域に応じて開口を設けることで前記画素間に隔壁を形成する工程と、

(c)上記(b)の工程の後、前記光電変換層を成膜する工程と、

(d)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(e)前記上部電極を成膜した後、透明絶縁膜を成膜する工程と、

(f)前記開口を設けた部分以外に成膜された、前記光電変換層、前記上部電極、前記透明絶縁膜を除去する工程と、を含む光電変換装置の製造方法。 - (実施形態3)

基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)前記下部電極上に第1の導電性材料を成膜する工程と、

(b)前記第1の導電性材料の膜に、各画素を形成する領域に応じて第1の開口を設けることで前記画素間に隔壁を形成する工程と、

(c)上記(b)の工程の後、前記光電変換層を成膜する工程と、

(d)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(e)前記上部電極を成膜した後、該上部電極上に第2の導電性材料を成膜する工程と、

(f)前記第1の導電性材料の上に形成された、前記光電変換層、前記上部電極、該上部電極に積層する前記導電性材料を除去する工程と、

(g)前記導電性材料の膜に、前記第1の開口よりも開口面積の小さい第2の開口を設ける工程と、

(h)透明絶縁膜を成膜する工程と、を含む光電変換装置の製造方法。 - (実施形態4)

基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)絶縁性材料を成膜する工程と、

(b)成膜された前記絶縁性材料のうえに導電性材料を成膜する工程と、

(c)前記絶縁性材料及び前記導電性材料の膜に、各画素を形成する領域に応じて開口を設ける工程と、

(d)前記下部電極を成膜する工程と、

(e)前記光電変換層を成膜する工程と、

(f)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(g)前記上部電極を成膜した後、前記透明絶縁膜を成膜する工程と、

(h)前記開口を設けた領域以外の、前記下部電極、前記光電変換層、前記上部電極、前記透明絶縁膜を除去する工程と、を含む光電変換装置の製造方法。 - (実施形態4変形)

基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)前記基板に絶縁性材料を成膜する工程と、

(b)成膜された前記絶縁性材料に、前記下部電極と接続される接続部を形成するための第1の孔と、前記第1の孔と連通し、かつ、該第1の孔より開口面積の大きい第2の孔を形成する工程と、

(c)導電性材料を成膜する工程と、

(d)前記導電性材料の膜に、各画素を形成する領域に応じて開口を設ける工程と、

(e)前記下部電極を成膜する工程と、

(f)前記光電変換層を成膜する工程と、

(g)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(h)前記上部電極を成膜した後、前記透明絶縁膜を成膜する工程と、

(i)前記開口を設けた領域以外の、前記下部電極、前記光電変換層、前記上部電極、前記透明絶縁膜を除去する工程と、を含む光電変換装置の製造方法。 - (実施形態5)

基板と、該基板の上方に形成された下部電極と、前記下部電極の上方に形成された光電変換層と、前記光電変換層の上方に形成された上部電極とを含む光電変換素子を少なくとも1つ有する画素が複数配列された光電変換装置の製造方法であって、

(a)絶縁性材料を成膜する工程と、

(b)前記絶縁性材料の膜に、各画素を形成する領域に応じて第1の開口を設けることで前記画素間に隔壁を形成する工程と、

(c)前記下部電極を成膜する工程と、

(d)前記光電変換層を成膜する工程と、

(e)前記光電変換層を成膜した後、上部電極を成膜する工程と、

(f)前記上部電極を成膜した後、導電性材料を成膜する工程と、

(g)前記開口を設けた部分以外に成膜された、前記下部電極、前記光電変換層、前記上部電極、該上部電極に積層する前記導電性材料を除去する工程と、

(h)各画素の導電性材料の膜の上面、及び、前記絶縁性材料の膜の上面に前記導電性材料を成膜する工程と、

(i)上記(g)の工程で成膜した導電性材料に、前記第1の開口よりも開口面積が小さい第2の開口を設ける工程と、

(j)透明絶縁膜を成膜する工程と、を含む光電変換材料の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008169181A JP2010010478A (ja) | 2008-06-27 | 2008-06-27 | 光電変換装置、光電変換装置の製造方法及び撮像装置 |

| US12/490,920 US8193542B2 (en) | 2008-06-27 | 2009-06-24 | Photoelectric apparatus and imaging apparatus including the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008169181A JP2010010478A (ja) | 2008-06-27 | 2008-06-27 | 光電変換装置、光電変換装置の製造方法及び撮像装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010010478A true JP2010010478A (ja) | 2010-01-14 |

| JP2010010478A5 JP2010010478A5 (ja) | 2011-03-17 |

Family

ID=41446921

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008169181A Withdrawn JP2010010478A (ja) | 2008-06-27 | 2008-06-27 | 光電変換装置、光電変換装置の製造方法及び撮像装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8193542B2 (ja) |

| JP (1) | JP2010010478A (ja) |

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2011155121A1 (ja) * | 2010-06-08 | 2011-12-15 | パナソニック株式会社 | 固体撮像装置及びその製造方法 |

| KR101108517B1 (ko) * | 2010-02-01 | 2012-01-30 | 한국과학기술원 | 열구동 전자종이화면 장치 및 그 제조방법 |

| JP2012038784A (ja) * | 2010-08-03 | 2012-02-23 | Brother Ind Ltd | フォトダイオードアレイ、およびフォトダイオードアレイの製造方法 |

| KR20140020674A (ko) * | 2012-08-10 | 2014-02-19 | 엘지디스플레이 주식회사 | 유기발광소자 및 그 제조방법 |

| JP2015056554A (ja) * | 2013-09-12 | 2015-03-23 | ソニー株式会社 | 固体撮像素子および製造方法、並びに電子機器 |

| KR20150099730A (ko) * | 2012-12-26 | 2015-09-01 | 소니 주식회사 | 고체 촬상 소자 및 이것을 구비한 고체 촬상 장치 |

| WO2016185914A1 (ja) * | 2015-05-19 | 2016-11-24 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置、固体撮像装置、電子機器、および半導体装置の製造方法 |

| KR20170104086A (ko) * | 2016-03-04 | 2017-09-14 | 삼성디스플레이 주식회사 | 표시 장치 |

| JP2017174903A (ja) * | 2016-03-22 | 2017-09-28 | キヤノン株式会社 | 光電変換装置、及び撮像システム |

| JP2021527235A (ja) * | 2018-06-04 | 2021-10-11 | イソルグ | 画像センサ及びディスプレイスクリーンを備えたデバイス |

| JPWO2020188959A1 (ja) * | 2019-03-20 | 2021-10-14 | 株式会社ジャパンディスプレイ | 検出装置 |

Families Citing this family (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9123653B2 (en) * | 2009-07-23 | 2015-09-01 | Sony Corporation | Solid-state imaging device, method of manufacturing the same, and electronic apparatus |

| US9985237B2 (en) * | 2009-08-12 | 2018-05-29 | X-Fab Semiconductor Foundries Ag | Method of manufacturing an organic light emitting diode by lift-off |

| TWI557875B (zh) * | 2010-07-19 | 2016-11-11 | 晶元光電股份有限公司 | 多維度發光裝置 |

| KR20120081505A (ko) * | 2011-01-11 | 2012-07-19 | 삼성전자주식회사 | 이미지 센서 및 그 제조 방법 |

| CA2835870A1 (en) | 2011-05-12 | 2012-11-15 | Olive Medical Corporation | Pixel array area optimization using stacking scheme for hybrid image sensor with minimal vertical interconnects |

| US9224770B2 (en) | 2012-04-26 | 2015-12-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Image sensor device and method |

| US9455288B2 (en) | 2012-05-21 | 2016-09-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | Image sensor structure to reduce cross-talk and improve quantum efficiency |

| MX344146B (es) | 2012-07-26 | 2016-12-07 | Depuy Synthes Products Inc | Sistema de cámara con sensor de imagen cmos monolítico de area mínima. |

| US9516239B2 (en) | 2012-07-26 | 2016-12-06 | DePuy Synthes Products, Inc. | YCBCR pulsed illumination scheme in a light deficient environment |

| AU2013295553B2 (en) | 2012-07-26 | 2017-10-19 | DePuy Synthes Products, Inc. | Continuous video in a light deficient environment |

| EP2967309B1 (en) | 2013-03-15 | 2022-05-04 | DePuy Synthes Products, Inc. | Viewing trocar for use with angled endoscope |

| CN105246394B (zh) | 2013-03-15 | 2018-01-12 | 德普伊新特斯产品公司 | 无输入时钟和数据传输时钟的图像传感器同步 |

| EP2967294B1 (en) | 2013-03-15 | 2020-07-29 | DePuy Synthes Products, Inc. | Super resolution and color motion artifact correction in a pulsed color imaging system |

| JP6404318B2 (ja) | 2013-03-15 | 2018-10-10 | デピュイ・シンセス・プロダクツ・インコーポレイテッド | レーザーパルスの積算光エネルギー制御 |

| US10750933B2 (en) | 2013-03-15 | 2020-08-25 | DePuy Synthes Products, Inc. | Minimize image sensor I/O and conductor counts in endoscope applications |

| AU2014233464B2 (en) | 2013-03-15 | 2018-11-01 | DePuy Synthes Products, Inc. | Scope sensing in a light controlled environment |

| DE102013205714A1 (de) | 2013-03-28 | 2014-10-02 | Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. | Organisches bauelement und herstellungsverfahren |

| CN104937386B (zh) * | 2013-03-29 | 2017-07-04 | 松下电器(美国)知识产权公司 | 推断装置、推断方法、集成电路以及程序 |

| KR102197069B1 (ko) | 2014-02-04 | 2020-12-30 | 삼성전자 주식회사 | 이미지 센서 및 이미지 처리 장치 |

| US10084944B2 (en) | 2014-03-21 | 2018-09-25 | DePuy Synthes Products, Inc. | Card edge connector for an imaging sensor |

| CN104795433B (zh) * | 2015-05-08 | 2016-07-13 | 京东方科技集团股份有限公司 | 显示面板及其制作方法、显示装置 |

| JP6903584B2 (ja) * | 2015-10-26 | 2021-07-14 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像装置およびその製造方法、並びに電子機器 |

| DE102015225797B3 (de) * | 2015-12-17 | 2017-05-04 | Robert Bosch Gmbh | Optischer Detektor |

| US10038019B2 (en) | 2015-12-29 | 2018-07-31 | Industrial Technology Research Institute | Image sensor and manufacturing method thereof |

| US10038033B2 (en) * | 2015-12-29 | 2018-07-31 | Industrial Technology Research Institute | Image sensor |

| JP6979974B2 (ja) * | 2017-01-24 | 2021-12-15 | ソニーセミコンダクタソリューションズ株式会社 | 受光素子の製造方法 |

| CN106784389A (zh) * | 2017-02-17 | 2017-05-31 | 京东方科技集团股份有限公司 | 一种复合透明电极、有机发光二极管及其制备方法 |

| US12185018B2 (en) | 2019-06-28 | 2024-12-31 | Apple Inc. | Stacked electromagnetic radiation sensors for visible image sensing and infrared depth sensing, or for visible image sensing and infrared image sensing |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4868664A (en) * | 1984-05-04 | 1989-09-19 | Energy Conversion Devices, Inc. | Contact type image replication employing a light piping faceplate |

| JPH02275670A (ja) * | 1989-01-18 | 1990-11-09 | Canon Inc | 光電変換装置および画像読取装置 |

| GB2228367B (en) * | 1989-02-21 | 1993-04-07 | Canon Kk | Semiconductor device having matrix wiring section,and semiconductor device using the same and having photoelectric conversion function |

| CN1181569C (zh) | 1998-02-02 | 2004-12-22 | 杜邦显示器股份有限公司 | 有机半导体图像传感器 |

| JP4868694B2 (ja) * | 2000-09-18 | 2012-02-01 | 新日鉄マテリアルズ株式会社 | 半導体用ボンディングワイヤ |

| US6765187B2 (en) * | 2001-06-27 | 2004-07-20 | Canon Kabushiki Kaisha | Imaging apparatus |

| JP2005311315A (ja) | 2004-03-23 | 2005-11-04 | Matsushita Electric Ind Co Ltd | 有機情報読み取りセンサとその製造方法、及びそれを用いた情報読み取り装置 |

| JP2006049834A (ja) * | 2004-06-30 | 2006-02-16 | Fuji Film Microdevices Co Ltd | 固体撮像素子およびその製造方法 |

| US7410906B2 (en) * | 2004-07-16 | 2008-08-12 | Fujifilm Corporation | Functional device and method for producing the same, and image pickup device and method for producing the same |

| JP2008277511A (ja) * | 2007-04-27 | 2008-11-13 | Fujifilm Corp | 撮像素子及び撮像装置 |

| JP2009088292A (ja) * | 2007-09-28 | 2009-04-23 | Fujifilm Corp | 光電変換素子、撮像素子及び光センサー |

-

2008

- 2008-06-27 JP JP2008169181A patent/JP2010010478A/ja not_active Withdrawn

-

2009

- 2009-06-24 US US12/490,920 patent/US8193542B2/en not_active Expired - Fee Related

Cited By (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101108517B1 (ko) * | 2010-02-01 | 2012-01-30 | 한국과학기술원 | 열구동 전자종이화면 장치 및 그 제조방법 |

| WO2011155121A1 (ja) * | 2010-06-08 | 2011-12-15 | パナソニック株式会社 | 固体撮像装置及びその製造方法 |

| JP2012038784A (ja) * | 2010-08-03 | 2012-02-23 | Brother Ind Ltd | フォトダイオードアレイ、およびフォトダイオードアレイの製造方法 |

| KR101936774B1 (ko) * | 2012-08-10 | 2019-01-09 | 엘지디스플레이 주식회사 | 유기발광소자 및 그 제조방법 |

| KR20140020674A (ko) * | 2012-08-10 | 2014-02-19 | 엘지디스플레이 주식회사 | 유기발광소자 및 그 제조방법 |

| KR20150099730A (ko) * | 2012-12-26 | 2015-09-01 | 소니 주식회사 | 고체 촬상 소자 및 이것을 구비한 고체 촬상 장치 |

| KR102163307B1 (ko) * | 2012-12-26 | 2020-10-08 | 소니 주식회사 | 고체 촬상 소자 및 이것을 구비한 고체 촬상 장치 |

| JP2015056554A (ja) * | 2013-09-12 | 2015-03-23 | ソニー株式会社 | 固体撮像素子および製造方法、並びに電子機器 |

| US9666643B2 (en) | 2013-09-12 | 2017-05-30 | Sony Semiconductor Solutions Corporation | Solid state image sensor, production method thereof and electronic device |

| US12035549B2 (en) | 2013-09-12 | 2024-07-09 | Sony Semiconductor Solutions Corporation | Solid state image sensor, production method thereof and electronic device |

| US10622563B2 (en) | 2015-05-19 | 2020-04-14 | Sony Semiconductor Solutions Corporation | Semiconductor device, solid-state imaging device, electronic apparatus, and manufacturing method of semiconductor device |

| WO2016185914A1 (ja) * | 2015-05-19 | 2016-11-24 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置、固体撮像装置、電子機器、および半導体装置の製造方法 |

| KR20170104086A (ko) * | 2016-03-04 | 2017-09-14 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR102610027B1 (ko) * | 2016-03-04 | 2023-12-11 | 삼성디스플레이 주식회사 | 표시 장치 |

| JP2017174903A (ja) * | 2016-03-22 | 2017-09-28 | キヤノン株式会社 | 光電変換装置、及び撮像システム |

| JP2021527235A (ja) * | 2018-06-04 | 2021-10-11 | イソルグ | 画像センサ及びディスプレイスクリーンを備えたデバイス |

| JP7320006B2 (ja) | 2018-06-04 | 2023-08-02 | イソルグ | 画像センサ及びディスプレイスクリーンを備えたデバイス |

| JPWO2020188959A1 (ja) * | 2019-03-20 | 2021-10-14 | 株式会社ジャパンディスプレイ | 検出装置 |

| JP7220775B2 (ja) | 2019-03-20 | 2023-02-10 | 株式会社ジャパンディスプレイ | 検出装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8193542B2 (en) | 2012-06-05 |

| US20090322923A1 (en) | 2009-12-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2010010478A (ja) | 光電変換装置、光電変換装置の製造方法及び撮像装置 | |

| JP5087304B2 (ja) | 固体撮像素子の製造方法 | |

| US8298855B2 (en) | Photoelectric conversion device, imaging device, and process for producing the photoelectric conversion device | |

| JP4911445B2 (ja) | 有機と無機のハイブリッド光電変換素子 | |

| JP4802286B2 (ja) | 光電変換素子及び撮像素子 | |

| US7659499B2 (en) | Photoelectric conversion device and solid-state imaging device | |

| JP4961111B2 (ja) | 光電変換膜積層型固体撮像素子とその製造方法 | |

| JP2005303266A (ja) | 撮像素子、その電場印加方法および印加した素子 | |

| JP2007067194A (ja) | 有機光電変換素子、および積層型光電変換素子 | |

| US9040973B2 (en) | Organic image sensor and method of producing the same | |

| JP2010062380A (ja) | 光電変換装置,光電変換装置の製造方法及び撮像装置 | |

| JP2008258421A (ja) | 有機光電変換素子及びその製造方法 | |

| JP2011233908A (ja) | 光電変換素子及び撮像素子 | |

| JP5492939B2 (ja) | 固体撮像素子の製造方法 | |

| JP2007324405A (ja) | 固体撮像素子 | |

| JP4719531B2 (ja) | 光電変換素子及び撮像素子 | |

| JP2006237351A (ja) | 光電変換膜、光電変換素子及び光電変換膜の製造方法 | |

| JP2007059483A (ja) | 光電変換素子、撮像素子、並びに、光電変換素子および撮像素子に電場を印加する方法 | |

| JP2008004899A (ja) | 固体撮像装置 | |

| JP2012009910A (ja) | 固体撮像素子 | |

| JP2007073742A (ja) | 光電変換素子及び固体撮像素子 | |

| JP4815233B2 (ja) | 固体撮像素子、その駆動方法、及び固体撮像素子の製造方法 | |

| JP2007088440A (ja) | 光電変換素子及び撮像素子 | |

| JP2007208840A (ja) | 固体撮像素子 | |

| JP2007080936A (ja) | 光電変換素子及び固体撮像素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110202 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110202 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20111216 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20120522 |