本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の記載内容に限定して解釈されるものではない。以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いることとする。

本発明に係る半導体基板を図1(A)(B)に示す。図1(A)においてベース基板100は、絶縁表面を有する基板若しくは絶縁基板であり、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板を適用される。その他に石英ガラス、シリコンウエハのような半導体基板も適用可能である。LTSS(Low Temperature Single crystal Semiconductor)層102は単結晶半導体材料を適用することができ、例えば単結晶シリコンなどが挙げられる。複数の元素からなるソースガスをプラズマ励起して生成されたイオンを用い、分離層を形成して、単結晶半導体基板若しくは多結晶半導体基板から剥離可能であるシリコン、ゲルマニウム、その他、ガリウムヒ素、インジウムリンなどの化合物半導体による結晶性半導体材料を適用することもできる。

このようなベース基板とLTSS層102の間に、平滑面を有し親水性表面を形成する接合層104を設ける。この接合層104として酸化シリコン膜が適している。特に有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。有機シランガスとしては、珪酸エチル(TEOS:化学式Si(OC2H5)4)、トリメチルシラン(TMS:(CH3)3SiH)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OC2H5)3)、トリスジメチルアミノシラン(SiH(N(CH3)2)3)等のシリコン含有化合物を用いることができる。

接合層104は5nm乃至500nmの厚さで設けられる。この厚さであれば、被成膜表面の表面荒れを平滑化すると共に、当該膜の成長表面の平滑性を確保することが可能である。また、接合する基板との歪みを緩和することができる。ベース基板にも同様の酸化シリコン膜を設けておいてもよい。すなわち、絶縁表面を有する基板若しくは絶縁性のベース基板100にLTSS層102を接合するに際し、接合を形成する面の一方若しくは双方に、好ましくは有機シランを原材料として成膜した酸化シリコン膜でなる接合層104を設けることで強固な接合を形成することができる。

接合層104はLTSS層102側に設けられ、ベース基板100の表面と密接することで、室温であっても接合をすることが可能である。より強固に接合を形成するには、ベース基板100とLTSS層102を押圧すれば良い。室温で形成された接合強度を高めるためには更に熱処理をすることが好ましい。

異種材料であるベース基板100と接合層104を室温などの低温で接合するには表面を清浄化する。このような状態でベース基板100と接合層104を密着させると、表面間引力により接合が形成される。さらに表面に複数の水酸基を付着させる処理を加えると好ましい。例えば、ベース基板100の表面を酸素プラズマ処理若しくはオゾン処理して親水性にすることが好ましい。このように表面を親水性にする処理を加えた場合には、表面の水酸基が作用して水素結合により接合が形成される。

異種材料であるベース基板100と接合層104を低温で接合するための処理として、接合を形成する表面にアルゴンなどの不活性ガスによるイオンビームを照射して清浄化しても良い。イオンビームの照射により、ベース基板100若しくは接合層104の未結合手が露呈して非常に活性な表面が形成される。このように活性化された表面同士を密着させると低温でも接合を形成することが可能である。表面を活性化して接合を形成する方法は、当該表面を高度に清浄化しておくことが要求されるので、真空中で行うことが好ましい。

LTSS層102は単結晶半導体基板を薄片化して形成されるものである。例えば、単結晶半導体基板の所定の深さに、シラン又はハロゲン化ケイ素をプラズマ励起して生成されたイオンを照射し、その後熱処理を行って表層の単結晶シリコン層を剥離してLTSS層102を形成することができる。LTSS層102の厚さは5nm乃至500nm、好ましくは10nm乃至200nmの厚さである。

以上、接合層104を有する例を示したが、ベース基板100とLTSS層102との接合強度に問題がなければ、接合層104は形成せず、ベース基板100とLTSS層102を直接接合してもよい。

図1(B)は、ベース基板100にバリア層105と接合層104を設けた構成を示す。バリア層105と接合層104をベース基板に設けることにより、LTSS層102をベース基板100に接合した場合に、ベース基板100としてガラス基板を用いた場合に、アルカリ金属若しくはアルカリ土類金属のような可動イオン不純物が拡散してLTSS層102が汚染されることを防ぐことができる。また、ベース基板100側の接合層104は適宜設ければ良い。

図2(A)はLTSS層102と接合層104の間に窒素含有絶縁層120を設けた構成を示す。窒素含有絶縁層120は窒化シリコン膜、窒化酸化シリコン膜若しくは酸化窒化シリコン膜から選ばれた一又は複数の膜を積層して形成する。例えば、LTSS層102側から酸化窒化シリコン膜、窒化酸化シリコン膜を積層して窒素含有絶縁層120とすることができる。接合層104がベース基板100と接合を形成するために設けるのに対し、窒素含有絶縁層120は、可動イオンや水分等の不純物がLTSS層102に拡散して汚染されることを防ぐために設けることが好ましい。

なお、ここで窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、濃度範囲として酸素が15〜30原子%、窒素が20〜35原子%、ケイ素が25〜35原子%、水素が15〜25原子%の範囲で含まれるものをいう。また、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、濃度範囲として酸素が55〜65原子%、窒素が1〜20原子%、ケイ素が25〜35原子%、水素が0.1〜10原子%の範囲で含まれるものをいう。

図2(B)は、ベース基板100に接合層104を設けた構成である。ベース基板100と接合層104との間にはバリア層105が設けられていることが好ましい。バリア層105を設けるのは、ベース基板100として用いられるガラス基板からアルカリ金属若しくはアルカリ土類金属のような可動イオン不純物が拡散してLTSS層102が汚染されることを防ぐためである。また、LTSS層102には酸化シリコン膜121が形成されている。この酸化シリコン膜121が接合層104と接合を形成し、ベース基板100上にLTSS層102を固定する。酸化シリコン膜121は熱酸化により形成されたものが好ましい。

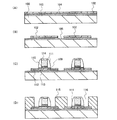

このような半導体基板の作製方法について図3乃至図5を参照して説明する。

図3に、半導体基板101の表面に対して複数の元素からなるソースガスをプラズマ励起して生成されたイオンを照射することにより、分離層103を形成する態様を示す。

半導体基板101としては、シリコンやゲルマニウムなどからなる半導体基板、又はガリウムヒ素やインジウムリンなどからなる化合物半導体基板を適用することができる。単結晶半導体基板を適用することが好ましいが、多結晶半導体基板を適用することも可能である。また、適用する半導体基板は矩形状でもよいし、円形状でもよい。

ここで用いるソースガスとして、シラン(SiH4)、ジシラン(Si2H6)、重水素シラン(SiD4)、フッ化ケイ素(SiF4)、塩化ケイ素(SiCl4)、臭化ケイ素(SiBr4)、ヨウ化ケイ素(SiI4)等のハロゲン化ケイ素、ゲルマン(GeH4)等の複数の元素からなるガスを用いることができる。

半導体基板101に照射するイオンとして、シランをプラズマ励起することにより生成されたSiH+イオン、SiH2 +イオン、SiH3 +イオン、及びSiH4 +イオンを用いることができる。フッ化ケイ素をプラズマ励起することにより生成されたSiF+イオン、SiF2 +イオン、SiF3 +イオン、及びSiF4 +イオン、塩化ケイ素をプラズマ励起することにより生成されたSiCl+イオン、SiCl2 +イオン、SiCl3 +イオン、及びSiCl4 +イオン、臭化ケイ素をプラズマ励起することにより生成されたSiBr+イオン、SiBr2 +イオン、SiBr3 +イオン、及びSiBr4 +イオン、ヨウ化ケイ素をプラズマ励起することにより生成されたSiI+イオン、SiI2 +イオン、SiI3 +イオン、及びSiI4 +イオン等を用いることができる。なお、シランをプラズマ励起することによりされたSiH+イオン、SiH2 +イオン、SiH3 +イオン、及びSiH4 +イオンのうち、少なくとも一のイオンが基板に照射されればよい。その他のソースガスをプラズマ励起して生成されるイオンについても同様である。

このように、イオン照射工程で使用するイオンは、水素イオンに対して質量が比較的大きく且つ熱処理に応じて半導体基板から脱離可能なイオン種であれば、上記のイオンに限らないものであり、半導体基板101に悪影響を及ぼさないものであれば良い。したがって、ジシラン、重水素シラン、ゲルマン等の複数の元素からなるソースガスをプラズマ励起して生成されたイオンを用いることができる。

イオン照射による分離層103の形成はベース基板100に転置するLTSS層の厚さを考慮して行われる。当該LTSS層の厚さは5nm乃至500nm、好ましくは10nm乃至200nmの厚さとする。イオンを照射するための加速電圧はこのような厚さを考慮して、半導体基板101に添加されるようにする。

イオン照射はイオンドーピング装置を用いて行うことが好ましい。すなわち、ソースガスをプラズマ化して生成された複数のイオン種を質量分離しないで照射するドーピング方式を用いる。本実施の形態では、ドーピング法により、モノシラン(SiH4)をプラズマ励起して生成されたイオンを40keVの加速電圧にて、5×1015atoms/cm2のドーズ量で照射する。

イオンドーピング装置では、イオンの生成に係るプラズマ空間が大きく、大量のイオンを生成し、打ち込むことができるというメリットを有している。よって、イオンドーピング装置を用いることによって、生産性が向上する。イオン注入装置は、生成したイオンを質量分離して特定のイオン種だけを基板に打ち込めるという特徴がある一方、基本的に点ビームを走査することによりイオンを打ち込むため、生産性に問題が生じる。プラズマの発生方法としては、例えば、フィラメントを加熱して出てくる熱電子によるものが挙げられるが、プラズマの発生方法はいずれの装置においても大差はない。

ここで、図4に、半導体基板にシランをプラズマ励起して生成されたイオンをドーピング法により照射し分離層を形成した場合のシリコン、水素、及び結晶欠陥の深さ方向プロファイルを示す。横軸は半導体基板の表面からの深さを示し、縦軸は濃度分布を示している。

シランのイオン(SiH+イオン、SiH2 +イオン、SiH3 +イオン、及びSiH4 +イオン)をドーピング法により半導体基板に照射すると、照射されたシランのイオンの衝撃により結晶構造が乱されて結晶欠陥を形成する。シランのイオンは、水素イオンよりも質量が大きいため、水素イオン単独で照射する場合よりも一定の深さに集中させるための制御がしやすく、効率良く結晶欠陥を形成することができる。また、シランのイオンに含まれる水素イオンは結晶欠陥に捕獲されやすいため、結晶欠陥の極近傍に水素イオンを集中して照射することができる。さらに、質量数の大きいイオン、例えば、SiH3 +イオンとSiH4 +イオンの割合を高めておくことにより照射効率を高めることができ、イオンの照射時間を短縮することができる。SiH3 +イオンとSiH4 +イオンは合計で6割以上含ませておくことが好ましい。また、ハロゲン化ケイ素等のイオンを用いる場合にも、質量数の大きいイオン、例えば、SiF3 +、SiF4 +の割合を高めておくことにより照射効率を高めることができ、イオンの照射時間を短縮することができる。質量数の大きいイオンの割合を高めてイオンを照射することによって、水素イオンを単独で照射する場合に比べて、低ドーズ量のイオンで分離層を形成することができる。

また、シラン、ハロゲン化ケイ素等のイオンを質量分離して半導体基板101に照射しても、分離層103を形成することができる。この場合には、質量数の大きいイオン(例えば、SiH3 +、SiH4 +イオン)を選択的に照射することが好ましい。

なお、半導体基板に照射されたシリコン原子、ゲルマニウム原子はドーパント不純物とはならないため、最終的にデバイス領域に残存しても、その特性に大きな影響は与えないという利点もある。

分離層103の形成に当たってはイオンを照射する際に、イオン照射によって半導体基板101の表面がダメージを受けるため、半導体基板101の表面が粗くなってしまう場合がある。そのためイオンが照射される表面に窒化シリコン膜若しくは窒化酸化シリコン膜などによりイオン照射に対する保護膜(図示せず)を50nm乃至200nmの厚さで設けておいても良い。

次に、図5(A)で示すようにベース基板と接合を形成する面に接合層104として酸化シリコン膜を形成する。酸化シリコン膜としては上述のように有機シランガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。そのほかに、シランガスを用いて化学気相成長法により作製される酸化シリコン膜を適用することもできる。化学気相成長法による成膜では、単結晶半導体基板に形成した分離層103から脱ガスが起こらない温度として、例えば350℃以下の成膜温度が適用される。なお、単結晶若しくは多結晶半導体基板からLTSS層を剥離する第2の熱処理は、成膜温度よりも高い熱処理温度が適用される。

図5(B)はベース基板100と、半導体基板101の接合層104が形成された面とを密接させ、この両者を接合させる態様を示す。接合を形成する面は、十分に清浄化しておく。そして、ベース基板100と接合層104とを密着させることにより接合が形成される。この接合はファン・デル・ワールス力が作用しており、ベース基板100と半導体基板101とを圧接することで水素結合により強固な接合を形成することが可能である。

良好な接合を形成するために、表面を活性化しておいても良い。例えば、接合を形成する面に原子ビーム若しくはイオンビームを照射する。原子ビーム若しくはイオンビームを利用する場合には、アルゴン等の不活性ガスに中性原子ビーム若しくは不活性ガスイオンビームを用いることができる。その他に、プラズマ照射若しくはラジカル処理を行う。このような表面処理により200℃乃至400℃の温度であっても異種材料間の接合を形成することが容易となる。

ベース基板100と半導体基板101とを接合層104を介して貼り合わせた後に、第1の熱処理又は加圧処理を行うことが好ましい。第1の熱処理又は加圧処理を行うことで接合強度を向上させることが可能となる。第1の熱処理の温度は、ベース基板100の耐熱温度以下であることが好ましい。加圧処理においては、接合面に垂直な方向に圧力が加わるように行い、ベース基板100及び半導体基板101の耐圧性を考慮して行う。

図5(C)に、第2の熱処理を行い分離層103に亀裂を生じさせ、分離層103を劈開面として半導体基板101をベース基板100から剥離する態様を示す。接合層104はベース基板100と接合しているので、ベース基板100上には、半導体基板101と同じ結晶性のLTSS層102が残存することとなる。

第2の熱処理の温度は接合層104の成膜温度以上、ベース基板100の耐熱温度以下で行うことが好ましい。例えば、第2の熱処理を400℃乃至600℃で行うことが好ましい。第2の熱処理を行うことにより、水素イオンが集中して添加された領域で、シリコンと水素との結合が切れて、水素原子がシリコン原子の結晶面に析出し、シリコン−水素結合による積層欠陥を形成する。熱処理温度を上記温度とし、熱処理時間を増すと水素の析出量が増加し、その析出された水素同士が結合して水素ガスとして脱離する。これにより、シリコン結晶面が劈開し、LTSS層102を剥離することができる。

分離層103にはイオンが一定の深さの領域に集中して添加されているため、容易に剥離を行うことができ、分離層103の剥離界面(LTSS層の表面)において平坦性を向上させることができる。

また、半導体基板101に分離層103を形成するために照射するイオンとして、ハロゲン化ケイ素のイオンを用いた場合も、ハロゲンのイオンが集中して添加された領域で、ハロゲンのガスが脱離するため、シリコン結晶面が劈開し、LTSS層102を剥離することができる。

次いで、ベース基板100にLTSS層102が接合された状態で第3の熱処理を行ってもよい。第3の熱処理は、第2の熱処理温度よりも高い温度であってベース基板の歪み点を超えない温度で行うことが好ましい。或いは、第2の熱処理と第3の熱処理が同じ温度であっても、第3の熱処理時間を長くすることが好ましい。第3の熱処理は、熱伝導加熱、対流加熱、又は輻射加熱などにより、ベース基板及び/又はLTSS層102が加熱されるようにすれば良い。熱処理装置として電熱炉、ランプアニール炉、レーザ照射装置等を適用することができる。第3の熱処理は多段階に温度を変化させて行っても良い。また瞬間熱アニール(RTA)装置を用いても良い。RTA装置によって第3の熱処理を行う場合は、基板の歪み点近傍またはそれよりも若干高い温度に加熱することもできる。

第3の熱処理を行うことでLTSS層102に残留する応力を緩和することができる。すなわち、第3の熱処理によって、ベース基板100とLTSS層102の膨張係数の違いにより生じる熱歪みを緩和する。また、第3の熱処理はイオンを照射することによって結晶性が損なわれたLTSS層102の結晶性を回復させることができる。さらに、第3の熱処理は半導体基板101をベース基板と接合させた後、分割する際に生じるLTSS層102のダメージを回復させることにも有効である。よって、平坦性を向上させることができる。

以上、接合層104を有する例を示したが、ベース基板100とLTSS層102との接合強度に問題が無ければ、接合層104は形成せず、ベース基板100とLTSS層102とを直接接合してもよい。

また、分離層103を形成するためにイオンを照射した後の半導体基板101の表面(ベース基板100と接合される部分)に窒素含有絶縁層を形成しても良い。窒素含有絶縁層は、窒化シリコン、窒化酸化シリコン、酸化窒化シリコンから選ばれた一又は複数の膜を積層して形成する。窒素含有絶縁層を設けることにより、ベース基板100を接合した後、ベース基板から可動イオンや水分等の不純物がLTSS層102に拡散して汚染されることを防ぐことができる。

図6(A)〜図6(C)はベース基板側に接合層を設けてLTSS層102を形成する工程を示す。

図6(A)は保護膜として酸化シリコン膜121が形成された半導体基板101に電界で加速されたイオンを照射することにより、分離層103を形成する工程を示している。酸化シリコン膜121は、半導体基板101上に酸化シリコン層をスパッタ法やCVD法で成膜してもよいし、半導体基板101が単結晶シリコンの場合、半導体基板101を熱酸化して形成してもよい。本実施の形態では、半導体基板101が単結晶シリコン基板として、酸化シリコン膜121は単結晶シリコン基板を熱酸化して形成する。半導体基板101の表面に酸化シリコン膜121を形成しておくことで、イオンの照射によって表面がダメージを受け、平坦性が損なわれるのを防ぐことができる。

次に、図3と同様にして、半導体基板101の表面から電界で加速されたイオンを照射することにより分離層103を形成する。イオンの照射は、ベース基板に転置するLTSS層の厚さを考慮して行われる。イオンの照射は、ドーピング法により行われることが好ましい。ソースガスとしてシラン、ハロゲン化ケイ素等を用いることができる。シラン、ハロゲン化ケイ素等は水素と比べて質量が大きいため、一定の深さに集中させるための制御がしやすく、照射の深さのばらつきが少なくなるため、低ドーズ量で分離層を形成することができる。さらに、シリコン系基板を用いた場合は、添加されたシリコン原子はドーパント不純物とはならないため、最終的にデバイス領域に残存しても、その特性に大きな影響は与えないという利点もある。

図6(B)は、バリア層105及び接合層104が形成されたベース基板100と半導体基板101の酸化シリコン膜121が形成された面を密着させて接合を形成する工程を示している。ベース基板100上の接合層104と半導体基板101の酸化シリコン膜121を密着させることにより接合が形成される。

ベース基板100と半導体基板101とを接合層104を介して貼り合わせた後は、第1の熱処理又は加圧処理を行うことが好ましい。第1の熱処理又は加圧処理を行うことで接合強度を向上させることが可能となる。第1の熱処理の温度は、ベース基板100の耐熱温度以下であることが好ましい。加圧処理においては、接合面に垂直な方向に圧力が加わるように行い、ベース基板100及び半導体基板101の耐圧性を考慮して行う。

この状態で第2の熱処理を行う。第2の熱処理は接合層104の成膜温度以上で行うことが好ましく、400℃以上600℃未満の温度で行うことが好ましい。分離層103において水素イオンが集中して添加された領域で、シリコンと水素との結合が切れて、水素原子がシリコン原子の結晶面に析出し、シリコン−水素結合による積層欠陥を形成する。熱処理温度を上記温度とし、熱処理時間を増すと水素の析出量が増加し、その析出された水素同士が結合して水素ガスとして脱離する。これにより、図6(C)で示すようにシリコン結晶面が劈開し、LTSS層102を剥離することができる。ベース基板100には半導体基板101と同じ結晶性を有するLTSS層102が形成される。

分離層103にはイオンが一定の深さの領域に集中して注入されているため、容易に剥離を行うことができ、分離層103の剥離界面(LTSS層の表面)において平坦性を向上させることができる。

このようにして図2(B)で示す半導体基板を得ることができる。

なお、必要に応じて第3の熱処理を行うことが好ましい。第3の熱処理は、第2の熱処理温度よりも高い温度であってベース基板100の歪み点を超えない温度で行うことが好ましい。或いは、第2の熱処理と第3の熱処理は同じ温度であっても、第2の熱処時間を長くすることが好ましい。熱処理は、熱伝導加熱、対流加熱または輻射加熱などによりベース基板100及びまたはLTSS層102が加熱されるようにすれば良い。

第3の熱処理を行うことでLTSS層102に残留する応力を緩和することができる。すなわち、熱処理によって、ベース基板100とLTSS層102の膨張係数の違いにより生じる熱歪みを緩和する。また、第3の熱処理はイオンを照射することによって結晶性が損なわれたLTSS層102の結晶性を回復させるためにも有効である。さらに、熱処理は半導体基板101をベース基板と接合させた後、分割する際に生じるLTSS層102のダメージを回復させることにも有効である。

なお、図6(A)〜図6(C)において、ベース基板側に接合層を設けてLTSS層を形成する工程を示したが、接合を形成する面の双方に接合層を設けても良い。接合を形成する面の双方に接合層を設けることにより、強固な接合を形成することができる。

このように本形態によれば、シラン、ハロゲン化ケイ素等の複数の元素からなるイオンをドーピング法により照射して分離層を形成するので、水素イオンを照射する場合に比べて、イオンが照射される深さのばらつきを少なくすることができる。水素イオンよりも質量の大きいイオンの照射により結晶欠陥を効率良く形成しつつ、半導体基板を劈開するためのイオンを集中して照射することができるため、低ドーズ量で分離層を形成することができる。また、一定の領域にイオンが集中して照射されるため、容易に剥離を行うことができ、単結晶半導体層の剥離界面での平坦性が向上する。

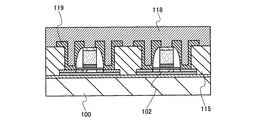

次いで、本発明に係る半導体基板を用いた半導体装置について図7と図8を参照して説明する。図7(A)において、ベース基板100に接合層104を介してLTSS層102が設けられている。LTSS層102の膜厚は5nm乃至500nm、好ましくは10nm乃至200nmの厚さとする。LTSS層102の厚さは、図3で説明した分離層103の深さを制御することにより適宜設定できる。LTSS層102にはしきい値電圧を制御するために、硼素、アルミニウム、ガリウムなどのp型不純物を添加する。例えば、p型不純物として硼素を5×1016cm−3以上1×1017cm−3以下の濃度で添加されていてもよい。ベース基板100にはバリア層105として窒化シリコン層と酸化シリコン層が積層形成されている。ベース基板100にバリア層を設けることで、LTSS層102の汚染を防ぐことができる。なお、窒化シリコン層に代えて、窒化酸化シリコン層、窒化アルミニウム層、窒化酸化アルミニウム層を適用してもよい。

図7(B)に、LTSS層102をエッチングして、半導体素子の配置に合わせて島状に分離したLTSS層102を形成する図を示す。

図7(C)に、LTSS層102が露出した後ゲート絶縁層109、ゲート電極110、サイドウォール絶縁層111を形成し、第1不純物領域112、第2不純物領域113を形成する図を示す。絶縁層114は、窒化シリコンで形成し、ゲート電極をエッチングするときのハードマスクとして用いる。

図7(D)に、層間絶縁層115を形成する図を示す。層間絶縁層115は、BPSG(Bron Phosphorus Silicon Glass)膜を成膜するか、ポリイミドに代表される有機樹脂を塗布して形成する。層間絶縁層115にはコンタクトホール116を形成する。コンタクトホール116は、サイドウォール絶縁層111を利用してセルフアラインコンタクトの構成となっている。

その後、図8で示すように、コンタクトホール116に合わせて配線119を形成する。配線119は、アルミニウム若しくはアルミニウム合金で形成し、上層と下層にはバリアメタルとしてモリブデン、クロム、チタンなどの金属膜で形成する。

このように、ベース基板100に接合されたLTSS層102を用いて電界効果トランジスタを作製することができる。本形態に係るLTSS層102は、結晶方位が一定の単結晶半導体であるため、均一で高性能な電界効果トランジスタを得ることができる。すなわち、しきい値電圧や移動度などトランジスタ特性として重要な特性値の不均一性を抑制し、高移動度化などの高性能化を達成することができる。

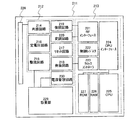

図9は、半導体装置の一例として、マイクロプロセッサ200の一例を示す。このマイクロプロセッサ200は、上記したように本形態に係る半導体基板により製造されるものである。このマイクロプロセッサ200は、演算回路201(Arithmetic logic unit。ALUともいう。)、演算回路制御部202(ALU Controller)、命令解析部203(Instruction Decoder)、割り込み制御部204(Interrupt Controller)、タイミング制御部205(Timing Controller)、レジスタ206(Register)、レジスタ制御部207(Register Controller)、バスインターフェース208(Bus I/F)、読み出し専用メモリ209、及びメモリインターフェース210(ROM I/F)を有している。

バスインターフェース208を介してマイクロプロセッサ200に入力された命令は、命令解析部203に入力され、デコードされた後、演算回路制御部202、割り込み制御部204、レジスタ制御部207、タイミング制御部205に入力される。演算回路制御部202、割り込み制御部204、レジスタ制御部207、タイミング制御部205は、デコードされた命令に基づき各種制御を行う。具体的に演算回路制御部202は、演算回路201の動作を制御するための信号を生成する。また、割り込み制御部204は、マイクロプロセッサ200のプログラム実行中に、外部の入出力装置や周辺回路からの割り込み要求を、その優先度やマスク状態から判断して処理する。レジスタ制御部207は、レジスタ206のアドレスを生成し、マイクロプロセッサ200の状態に応じてレジスタ206の読み出しや書き込みを行う。タイミング制御部205は、演算回路201、演算回路制御部202、命令解析部203、割り込み制御部204、レジスタ制御部207の動作のタイミングを制御する信号を生成する。例えばタイミング制御部205は、規準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、クロック信号CLK2を上記各種回路に供給する。なお、図9に示すマイクロプロセッサ200は、その構成を簡略化して示した一例にすぎず、実際にはその用途によって多種多様な構成を備えることができる。

このようなマイクロプロセッサ200は、絶縁の表面を有する基板若しくは絶縁基板上に接合された結晶方位が一定の単結晶半導体層(LTSS層)によって集積回路が形成されているので、処理速度の高速化のみならず、低消費電力化を図ることができる。

次に、非接触でデータの送受信を行うことのできる演算機能を備えた半導体装置の一例について図10を参照して説明する。図10は、無線通信により外部装置と信号の送受信を行って動作するコンピュータ(以下、「RFCPU」という)の一例を示す。RFCPU211は、アナログ回路部212とデジタル回路部213を有している。アナログ回路部212として、共振容量を有する共振回路214、整流回路215、定電圧回路216、リセット回路217、発信回路218、復調回路219と、変調回路220を有している。デジタル回路部213は、RFインターフェース221、制御レジスタ222、クロックコントローラ223、インターフェース224、中央処理ユニット225、ランダムアクセスメモリ226、読み出し専用メモリ227を有している。

リセット回路217は、デジタル回路部213をリセットし、初期化する信号を生成する。例えば、電源電圧の上昇に遅延して立ち上がる信号をリセット信号として生成する。発信回路218は、定電圧回路216により生成される制御信号に応じて、クロック信号の周波数とデューティー比を変更する。ローパスフィルタで形成される復調回路219は、例えば振幅変調(ASK)方式の送信信号の振幅を変動させて送信する。変調回路220は、共振回路214の共振点を変化させることで通信信号の振幅を変化させている。クロックコントローラ223は、電源電圧又は中央処理ユニット225における消費電流に応じてクロック信号の周波数とデューティー比を変更するための制御信号を生成している。電源電圧の監視は電源管理回路230が行っている。

アンテナ228からRFCPU211に入力された信号は復調回路219で復調された後、RFインターフェース221で制御コマンドには、読み出し専用メモリ227に記憶されているデータの読み出し、ランダムアクセスメモリ226へのデータの書き込み、中央処理ユニット225への演算命令などが含まれている。中央処理ユニット225は、インターフェース224を介して読み出し専用メモリ227、ランダムアクセスメモリ226、制御レジスタ222にアクセスする。インターフェース224は、中央処理ユニット225が要求するアドレスより、読み出し専用メモリ227、ランダムアクセスメモリ226、制御レジスタ222のいずれかに対するアクセス信号を生成する機能を有している。

中央処理ユニット225の演算方式は、読み出し専用メモリ227にOS(オペレーティングシステム)を記憶させておき、起動とともにプログラムを読み出し実行する方式を採用することができる。また、専用回路で演算回路を構成して、演算処理をハードウェア的に処理する方式を採用することもできる。ハードウェアとソフトウェアを併用する方式では、専用の演算回路で一部の処理を行い、残りの演算はプログラムを使って、中央処理ユニット225が実行する方式を適用することができる。

このようなRFCPU211は、絶縁表面を有する基板若しくは絶縁基板上に接合された結晶方位が一定の単結晶半導体層(LTSS層)によって集積回路が形成されているので、処理速度の高速化のみならず低消費電力化を図ることができる。それにより、電力を供給する容量部229を小型化しても長時間の動作を保証することができる。

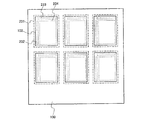

図1及び図2で例示するLTSS層102は、表示パネルを製造するマザーガラスと呼ばれる大型のガラス基板に接合することもできる。図11は、ベース基板100としてマザーガラスにLTSS層102を形成する場合を示す。まず、図5(A)を用いて説明した工程を経て、分離層103が形成された半導体基板101を複数用意する。次に、分離層103が形成された複数の半導体基板をマザーガラスに貼り合わせ、仮接合を行う。次に、図5(C)を用いて説明した加熱工程を行い、半導体基板101を分離層103において分離することで、マザーガラス上に、複数のLTSS層が接合される。

マザーガラスに接合されたLTSS層102からは複数の表示パネルを切り出すことができるが、LTSS層102は、表示パネル231の形成領域に合わせて接合することが好ましい。半導体基板に比べて、マザーガラス基板は面積が大きいので、LTSS層102は図11のように分割して配置することが好ましい。表示パネル231には、走査線駆動回路領域232、信号線駆動回路領域233、画素形成領域234があり、これらの領域が含まれるようにLTSS層102をベース基板100(マザーガラス)に形成する。

図12は、LTSS層102により画素トランジスタが形成される液晶表示装置の画素の一例を示す。図12(A)は画素の平面図を示し、LTSS層102に走査線126が交差し、信号線127、画素電極128が接続する画素を示す。図12(A)に示すJ−K切断面に対応する断面図が図12(B)に示されている。

図12(B)において、ベース基板100にはバリア層105として窒化シリコン層と酸化シリコン層が積層されている。LTSS層102は接合層104によってバリア層105と接合している。絶縁層118上に画素電極128が設けられている。LTSS層102と信号線127を接続するコンタクトホールには絶縁層118をエッチングして凹段差が生じるのでそこを埋めるように柱状スペーサ131が設けられている。対向基板129には対向電極130が形成され、柱状スペーサ131によって形成される空隙に液晶層132が形成されている。

図13(A)は、LTSS層102により画素部のトランジスタが形成されるエレクトロルミネッセンス表示装置の一例を示す。図13(A)は画素の平面図を示し、信号線127に接続する選択トランジスタ133と、電流供給線135に接続する表示制御トランジスタ134を有している。この表示パネルはエレクトロルミネッセンス材料を含んで形成される層(EL層)を電極間に挟んだ発光素子が各画素に設けられる構成となっている。画素電極128は表示制御トランジスタ134に接続されている。図13(B)はこのような画素の要部を示す断面図である。

図13(B)において、ベース基板100、バリア層105、接合層104、LTSS層102、絶縁層118などの構成は図12(B)と同様である。画素電極128は周辺部が絶縁性の隔壁層136で囲まれている。画素電極128上にはEL層137が形成されている。EL層137上には対向電極130が形成されている。画素部は封止樹脂138が充填され、補強板として対向基板129が設けられている。

本形態のエレクトロルミネッセンス表示装置はこのような画素をマトリクス状に配列させて表示画面を構成する。この場合、画素のトランジスタのチャネル部が本発明に係るLTSS層で形成されるので、各トランジスタ間で特性バラツキが無く、画素毎の発光輝度に斑がでないという利点がある。従って、発光素子の明るさを電流で制御して駆動することが容易となり、トランジスタ特性のバラツキを補正する補正回路も不要となるので、駆動回路の負担を低減することができる。

このように、表示装置を製造するマザーガラスにも本発明に係るLTSS層を形成しトランジスタを形成することが可能である。LTSS層で形成されるトランジスタは、アモルファスシリコントランジスタよりも電流駆動能力など全ての動作特性が優れているので、トランジスタのサイズを小型化することができる。それにより、表示装置における画素部の開口率を向上させることができる。また、図9及び図10で説明したようなマイクロプロセッサも形成することができるので、表示装置内にコンピュータの機能を搭載することもできる。また、非接触でデータの入出力を可能としたディスプレイを作製することもできる。

以上のように、本発明の適用範囲はきわめて広く、あらゆる分野の電子機器に用いることが可能である。