以下、図面を参照して本発明の実施形態について詳細に説明する。

<表示装置の全体概要>

図1は、本発明に係る表示装置の一実施形態であるアクティブマトリクス型表示装置の構成の概略を示すブロック図である。ここで示す構成例では、たとえば画素の表示素子(電気光学素子、発光素子)として有機EL素子を、能動素子としてポリシリコン薄膜トランジスタ(TFT;Thin Film Transistor)をそれぞれ用い、薄膜トランジスタを形成した半導体基板上に有機EL素子を形成してなるアクティブマトリクス型有機ELディスプレイ(以下「有機EL表示装置」と称する)に適用した場合を例に採って説明する。

なお、以下の全体構成の説明においては、画素の表示素子として有機EL素子を例に具体的に説明するが、これは一例であって、対象となる表示素子は有機EL素子に限らない。一般的に電流駆動で発光する表示素子の全てに、後述する全ての実施形態が同様に適用できる。

図1に示すように、表示装置1は、複数の表示素子としての有機EL素子(図示せず)を持った画素回路(画素とも称される)Pが表示アスペクト比である縦横比がX:Y(たとえば9:16)の有効映像領域を構成するように配置された表示パネル部100と、この表示パネル部100を駆動制御する種々のパルス信号を発するパネル制御部の一例である駆動信号生成部(いわゆるタイミングジェネレータ)200と、映像信号処理部220を備えている。駆動信号生成部200と映像信号処理部220とは、1チップのIC(Integrated Circuit;半導体集積回路)に内蔵され、本例では、表示パネル部100の外部に配置されている。

なお、製品形態としては、図示のように、表示パネル部100、駆動信号生成部200、および映像信号処理部220の全てを備えたモジュール(複合部品)形態の表示装置1として提供されることに限らず、たとえば、表示パネル部100のみで表示装置1として提供することも可能である。また、このような表示装置1は、半導体メモリやミニディスク(MD)やカセットテープなどの記録媒体を利用した携帯型の音楽プレイヤーやその他の電子機器の表示部に利用される。

表示パネル部100は、基板101の上に、画素回路Pがn行×m列のマトリクス状に配列された画素アレイ部102と、画素回路Pを垂直方向に走査する垂直駆動部103と、画素回路Pを水平方向に走査する水平駆動部(水平セレクタあるいはデータ線駆動部とも称される)106と、各駆動部103,106と外部回路とのインタフェースをとるインタフェース(IF)部130と、外部接続用の端子部(パッド部)108などが集積形成されている。すなわち、垂直駆動部103や水平駆動部106やインタフェース部130などの周辺駆動回路が、画素アレイ部102と同一の基板101上に形成された構成となっている。

インタフェース部130は、垂直駆動部103と外部回路とのインタフェースをとる垂直IF部133と、水平駆動部106と外部回路とのインタフェースをとる水平IF部136を有する。

垂直駆動部103(書込走査部104および駆動走査部105)と水平駆動部106とで、信号電位の保持容量への書込みや、閾値補正動作や、移動度補正動作や、ブートストラップ動作を制御する制御部109が構成される。この制御部109とインタフェース部130(垂直IF部133や水平IF部136)を含めて、画素アレイ部102の画素回路Pを駆動する駆動回路を構成している。

垂直駆動部103としては、たとえば、書込走査部(ライトスキャナWS;Write Scan)104や電源供給能力を有する電源スキャナとして機能する駆動走査部(ドライブスキャナDS;Drive Scan)105を有する。 画素アレイ部102は、一例として、図示する左右方向の一方側もしくは両側から書込走査部104および駆動走査部105で駆動され、かつ図示する上下方向の一方側もしくは両側から水平駆動部106で駆動されるようになっている。

端子部108には、表示装置1の外部に配された駆動信号生成部200から、種々のパルス信号が供給されるようになっている。また同様に、映像信号処理部220から映像信号Vsig (カラー表示の場合には色別の映像信号Vsig_R,G,B)が供給されるようになっている。

一例としては、垂直駆動用のパルス信号として、垂直方向の書込み開始パルスの一例であるシフトスタートパルスSPDS,SPWSや垂直走査クロックCKDS,CKWS(必要に応じて位相反転した垂直走査クロックxCKDS ,xCKWS も)など必要なパルス信号が供給される。また、水平駆動用のパルス信号として、水平方向の書込み開始パルスの一例である水平スタートパルスSPH や水平走査クロックCKH (必要に応じて位相反転した水平走査クロックxCKHも)など必要なパルス信号が供給される。

端子部108の各端子は、配線109を介して、垂直駆動部103や水平駆動部106に接続されるようになっている。たとえば、端子部108に供給された各パルスは、必要に応じて図示を割愛したレベルシフタ部で電圧レベルを内部的に調整した後、バッファを介して垂直駆動部103の各部や水平駆動部106に供給される。

画素アレイ部102は、図示を割愛するが(詳細は後述する)、表示素子としての有機EL素子に対して画素トランジスタが設けられた画素回路Pが行列状に2次元配置され、この画素配列に対して行ごとに走査線が配線されるとともに、列ごとに信号線が配線された構成となっている。

たとえば、画素アレイ部102には、走査線(ゲート線)104WSと映像信号線(データ線)106HSが形成されている。両者の交差部分には図示を割愛した有機EL素子とこれを駆動する薄膜トランジスタが形成される。有機EL素子と薄膜トランジスタの組み合わせで画素回路Pを構成する。

具体的には、マトリクス状に配列された各画素回路Pに対しては、書込走査部104によって書込駆動パルスWSで駆動されるn行分の書込走査線104WS_1〜104WS_nおよび駆動走査部105によって電源駆動パルスDSL で駆動されるn行分の電源供給線105DSL_1 〜105DSL_n が画素行ごとに配線される。

書込走査部104および駆動走査部105は、論理ゲートの組合せ(ラッチやシフトレジスタなども含む)によって構成され、画素アレイ部102の各画素回路Pを行単位で選択する、すなわち、駆動信号生成部200から供給される垂直駆動系のパルス信号に基づき、書込走査線104WSおよび電源供給線105DSL を介して各画素回路Pを順次選択する。

水平駆動部106は、論理ゲートの組合せ(ラッチやシフトレジスタなども含む)によって構成され、画素アレイ部102の各画素回路Pを列単位で選択する、すなわち、駆動信号生成部200から供給される水平駆動系のパルス信号に基づき、選択された画素回路Pに対し映像信号線106HSを介して映像信号Vsig の内の所定電位をサンプリングして保持容量に書き込ませる。

本実施形態の表示装置1は、線順次駆動や点順次駆動が可能になっており、垂直駆動部103の書込走査部104および駆動走査部105は線順次で(つまり行単位で)で画素アレイ部102を走査するとともに、これに同期して水平駆動部106が、画像信号を、1水平ライン分を同時に(線順次の場合)、あるいは画素単位で(点順次の場合)、画素アレイ部102に書き込む。

なお、図1では、画素アレイ部102の一方側にのみ垂直駆動部103を配置する構成を示しているが、画素アレイ部102を挟んで左右両側に垂直駆動部103を配置する構成を採ることも可能である。同様に、図1では、画素アレイ部102の一方側にのみ水平駆動部106を配置する構成を示しているが、画素アレイ部102を挟んで上下両側に水平駆動部106を配置する構成を採ることも可能である。

なお、本例では、シフトスタートパルスSPDS,SPWS、垂直走査クロックCKDS,CKWSや水平スタートパルスSPH 、水平走査クロックCKH などのパルス信号を表示パネル部100の外部から入力する構成としているが、これらの各種のタイミングパルスを生成する駆動信号生成部200を表示パネル部100上に搭載することも可能である。

<画素回路>

図2および図2Aは、本実施形態の基本構成の画素回路Pと、当該画素回路Pを備えた有機EL表示装置の一実施形態を示す図である。本実施形態の基本構成の画素回路Pを画素アレイ部102に備える表示装置1を本実施形態の基本構成の表示装置1と称する。図2は基本構成を示し、図2Aは具体的な構成を示す。なお、表示パネル部100の基板101上において画素回路Pの周辺部に設けられた垂直駆動部103と水平駆動部106も合わせて示している。図3は、有機EL素子127や駆動トランジスタ121の特性ばらつきが駆動電流Idsに与える影響を説明する図であり、図3Aは、その改善手法の概念を説明する図である。

pチャネル型のトランジスタではなく、nチャネル型のトランジスタで駆動トランジスタを構成することができれば、トランジスタ作成において従来のアモルファスシリコン(a−Si)プロセスを用いることが可能になる。これにより、トランジスタ基板の低コスト化が可能となり、このような構成の画素回路Pの開発が期待される。

駆動トランジスタを始めとする各トランジスタとしてはMOSトランジスタを使用する。この場合、駆動トランジスタについては、ゲート端を制御入力端として取り扱い、ソース端およびドレイン端の何れか一方(ここではソース端とする)を出力端として取り扱い、他方を電源供給端(ここではドレイン端とする)として取り扱う。

図2および図2Aに示す本実施形態の画素回路Pは、基本的にnチャネル型の薄膜電界効果トランジスタでドライブトランジスタが構成されている点に特徴を有する。また、有機EL素子の経時劣化による当該有機EL素子への駆動電流Idsの変動を抑制するための回路、すなわち電気光学素子の一例である有機EL素子の電流−電圧特性の変化を補正して駆動電流Idsを一定に維持する駆動信号一定化回路(その1)を備え、また駆動トランジスタの特性変動(閾値電圧ばらつきや移動度ばらつき)による駆動電流変動を防ぐ閾値補正機能や移動度補正機能を実現して駆動電流Idsを一定に維持する駆動方式を採用した点に特徴を有する。

駆動トランジスタ121の特性変動(たとえば閾値電圧や移動度などのばらつきや変動)による駆動電流Idsに与える影響を抑制する方法としては、2TR構成の駆動回路をそのまま駆動信号一定化回路(その1)として採用しつつ、各トランジスタ121,125の駆動タイミングを工夫することで対処する。

また、本実施形態の画素回路Pは、2TR駆動の構成であり、素子数や配線数が少ないため、高精細化が可能であることに加えて、映像信号Vsig の劣化なくサンプリングできるため、良好な画質を得ることができる。

また本実施形態の画素回路Pは、保持容量120の接続態様に特徴を有し、有機EL素子127の経時劣化による駆動電流変動を防ぐ回路として、駆動信号一定化回路(その2)の一例であるブートストラップ回路を構成している。有機EL素子の電流−電圧特性に経時変化があった場合でも駆動電流を一定にする(駆動電流変動を防ぐ)ブートストラップ機能を実現する駆動信号一定化回路(その2)を備えた点に特徴を有するのである。

詳細は後述するが、本実施形態の画素回路Pは、書込みゲインやブートストラップゲインや移動度補正期間に関係する補助容量を備える。ただし、この補助容量を備えることは必須ではない。本実施形態の画素回路Pを駆動するに当たっての基本的な制御動作は、補助容量を備えていない画素回路Pに対するものと同様である。

具体的には図2および図2Aに示すように、本実施形態の画素回路Pは、それぞれnチャネル型の駆動トランジスタ121およびサンプリングトランジスタ125と、電流が流れることで発光する電気光学素子の一例である有機EL素子127とを有する。一般に、有機EL素子127は整流性があるためダイオードの記号で表している。なお、有機EL素子127には、寄生容量Celが存在する。図では、この寄生容量Celを有機EL素子127(ダイオード状のもの)と並列に示す。

駆動トランジスタ121は、ドレイン端Dが第1電源電位を供給する電源供給線DSL に接続され、ソース端(出力端)Sが、有機EL素子127のアノード端Aに接続され(その接続点をノードND121とする)、有機EL素子127のカソード端Kが基準電位を供給する全画素共通の接地配線Vcath(GND )に接続されている。

なお、接地配線Vcathは、それ用の単一層の配線(上層配線)のみとしてもよいし、たとえばアノード用の配線が形成されるアノード層に、カソード配線用の補助配線を設けてカソード配線の抵抗値を低減するようにしてもよい。この補助配線は、表示エリア内に格子状または列または行状に配線され、上層配線と同電位で固定電位である。

サンプリングトランジスタ125は、ゲート端Gが書込走査部104からの書込走査線104WSに接続され、ドレイン端Dが映像信号線106HSに接続され、ソース端Sが駆動トランジスタ121のゲート端Gに接続されている(その接続点をノードND122とする)。サンプリングトランジスタ125のゲート端Gには、書込走査部104からアクティブHの書込駆動パルスWSが供給される。サンプリングトランジスタ125は、ソース端Sとドレイン端Dとを逆転させた接続態様とすることもできる。

駆動トランジスタ121のドレイン端Dは、電源スキャナとして機能する駆動走査部105からの電源供給線105DSL に接続されている。電源供給線105DSL は、この電源供給線105DSL そのものが、駆動トランジスタ121に対しての電源供給能力を備える点に特徴を有する。

駆動走査部105は、駆動トランジスタ121のドレイン端Dに対して、それぞれ電源電圧に相当する高電圧側の第1電位Vcc_Hと閾値補正に先立つ準備動作に利用される低電圧側の第2電位Vcc_L(初期化電圧もしくはイニシャル電圧Vini とも称される)とを切り替えて供給する。

駆動トランジスタ121のドレイン端D側を第1電位Vcc_Hと第2電位Vcc_Lの2値をとる電源駆動パルスDSL で駆動することで、閾値補正に先立つ準備動作を行なうことを可能にしている。

第2電位Vcc_Lとしては、映像信号線106HSにおける映像信号Vsig の基準電位Vo(オフセット電圧Vofs とも称する)より十分低い電位とする。具体的には、駆動トランジスタ121のゲート・ソース間電圧Vgs(ゲート電位Vgとソース電位Vsの差)が駆動トランジスタ121の閾値電圧Vthより大きくなるように、電源供給線105DSL の低電位側の第2電位Vcc_Lを設定する。なお、基準電位Vo(Vofs )は、閾値補正動作に先立つ初期化動作に利用するとともに映像信号線106HSを予めプリチャージにしておくためにも利用する。

このような画素回路Pでは、有機EL素子127を駆動するときには、駆動トランジスタ121のドレイン端Dに第1電位Vcc_Hが供給され、ソース端Sが有機EL素子127のアノード端A側に接続されることで、全体としてソースフォロワ回路を形成するようになっている。

このような画素回路Pを採用する場合、駆動トランジスタ121の他に走査用に1つのスイッチングトランジスタ(サンプリングトランジスタ125)を使用する2TR駆動の構成を採るとともに、各スイッチングトランジスタを制御する電源駆動パルスDSL および書込駆動パルスWSのオン/オフタイミングの設定により、有機EL素子127の経時劣化や駆動トランジスタ121の特性変動(たとえば閾値電圧や移動度などのばらつきや変動)による駆動電流Idsに与える影響を防ぐ点に特徴を有する。

加えて、本実施形態の表示装置1においては、画素回路Pごとに、ノードND121(駆動トランジスタ121のソース端Sおよび保持容量120の一方の端子と有機EL素子127のアノード端Aの接続点)に容量値Csub の容量素子である補助容量310を追加し、補助容量310の他方の端子(ノードND310と称する)の接続箇所を自行(自段)の電源供給線105DSL とする点に特徴を有する。補助容量310は、有機EL素子127(その寄生容量Cel)と電気回路的に並列接続されたものとなる。

本実施形態では、図2Aに具体例を示すように、ノードND310を有機EL素子127のカソード配線に接続することにする。ノードND310の接続点は、本実施形態では、有機EL素子127のカソード配線としているが、これ以外にも、たとえば自段(行)の電源供給線105DSL とすることや、自段(行)以外の電源供給線105DSL とすることや、任意の値(接地電位を含む)の固定電位とすることも考えられる。ノードND310の接続点が何れであるかによって、それぞれ長短(利点と欠点)があるが、ここではその説明を割愛する。

自行以外としては、当該行の電源供給線105DSL より前段側に属する別の電源供給線105DSL とすることや、当該行の電源供給線105DSL より後段側に属する別の電源供給線105DSL とすることが考えられる。たとえば、直前よりもさらにその前の電源供給線105DSL に接続してもよい。もちろん、ノードND310を直後の行(1水平期間後:後側の隣接行)の電源供給線105DSL に接続してもよい。ただしこれらは前段側や後段側の一例であって、これに限られるものではなく、たとえば、直前よりもさらにその前の電源供給線105DSL あるいは直後よりもさらにその後ろの電源供給線105DSL に接続してもよい。ただし、隣接行以外ではその分配線長が長くなり配線抵抗やクロストークノイズなどの難点が懸念される。この点においては自段以外に接続する際には、ノードND310を隣接行の電源供給線105DSL に接続するのがよい。

また、ノードND310を固定電位にする際には、たとえば、全ての有機EL素子127のカソード端Kが接続される全画素共通の接地配線Vcath(上層配線でもよいし補助配線でもよい)とすることも考えられる。あるいは、ノードND310用に専用の固定電位を与えるため、TFT層で配線を設けてもよい。なお、このTFT層の補助容量310用の配線をカソード配線と兼用してもよい。

<基本動作>

先ず、図2および図2Aに示す本実施形態の画素回路Pの特徴を説明する上での比較例として、図示を割愛するが、補助容量310を備えておらず、保持容量120は、一方の端子がノードND122に接続され、他方の端子が全画素共通の接地配線Vcath(GND )に接続されている場合での動作について説明する。以下、このような画素回路Pを第1比較例の画素回路Pと称する。またここでは図示を割愛するが(後述の図5を参照)、本実施形態の画素回路Pから補助容量310を外した構成を第2比較例の画素回路Pと称する。

第1比較例の画素回路Pに対する変形例として、発光期間を制御する発光制御トランジスタを追加した3TR型とする場合、たとえば、駆動トランジスタ121のソース端をnチャネル型の発光制御トランジスタのドレイン端Dに接続し、発光制御トランジスタのソース端Sを有機EL素子127のアノード端に接続する。

第1比較例(3TR型とした変形例も含む)の画素回路Pでは、発光制御トランジスタを設けるか否かに関わらず、有機EL素子127を駆動するときには、駆動トランジスタ121のドレイン端D側が第1電源電位に接続され、ソース端Sが有機EL素子127のアノード端A側に接続されることで、全体としてソースフォロワ回路を形成するようになっている。

第1比較例の画素回路Pを駆動する際のタイミングチャートの図示は割愛するが、映像信号線106HSが映像信号Vsig の有効期間である信号電位にある時間帯に、書込走査線WSの電位が高レベルに遷移することで、nチャネル型のサンプリングトランジスタ125はオン状態となり、信号線HSから供給される映像信号線電位を保持容量120に充電する。この期間が映像信号Vsig のサンプリング期間となり、それ以降が保持期間となる。これにより駆動トランジスタ121のゲート端Gの電位(ゲート電位Vg)は上昇を開始し、ドレイン電流を流し始める。そのため、有機EL素子127のアノード電位は上昇し発光を開始する。

この後、書込駆動パルスWSが低レベルに遷移すると、保持容量120にその時点の映像信号線電位、つまり、映像信号Vsig の電位の内の有効期間の電位(信号電位)が保持される。これによって、駆動トランジスタ121のゲート電位Vgが一定となり、発光輝度が次のフレーム(またはフィールド)まで一定に維持される。

ここで、第1比較例の画素回路Pでは、駆動トランジスタ121のソース端Sの電位(ソース電位Vs)は、駆動トランジスタ121と有機EL素子127との動作点で決まり、その電圧値は駆動トランジスタ121のゲート電位Vgによって異なる値を持ってしまう。

一般的に、MOS型の駆動トランジスタ121は飽和領域で駆動される。よって、飽和領域で動作するトランジスタのドレイン端−ソース間に流れる電流をIds、移動度をμ、チャネル幅(ゲート幅)をW、チャネル長(ゲート長)をL、ゲート容量(単位面積当たりのゲート酸化膜容量)をCoxは、トランジスタの閾値電圧をVthとすると、駆動トランジスタ121は下記の式(1)に示した値を持つ定電流源となっている。式(1)から明らかなように、飽和領域ではトランジスタのドレイン電流Idsはゲート・ソース間電圧Vgsによって制御される。

<有機EL素子のI−V特性>

図3(1)に示す有機EL素子の電流−電圧(I−V)特性において、実線で示す曲線が初期状態時の特性を示し、破線で示す曲線が経時変化後の特性を示している。一般的に有機EL素子のI−V特性は、グラフに示すように時間が経過すると劣化する。

第1比較例の画素回路Pでは、この経時劣化により動作点が変化してしまい、同じゲート電位Vgを印加しても駆動トランジスタ121のソース電位Vsは変化してしまう。これにより、駆動トランジスタ121のゲート・ソース間電圧Vgsは変化してしまう。特性式(1)から明らかなように、ゲート・ソース間電圧Vgsが変動すると、たとえゲート電位Vgが一定であっても駆動電流Idsが変動し、同時に有機EL素子127に流れる電流値も変化する。このように有機EL素子127のI−V特性が変化すると、図2に示したソースフォロワ構成を持つ第1比較例の画素回路Pでは、有機EL素子127の発光輝度が経時的に変化してしまう。

駆動トランジスタ121としてnチャネル型を使用した単純な回路では、ソース端Sが有機EL素子127側に接続されてしまうため、有機EL素子127の経時変化とともに、ゲート・ソース間電圧Vgsが変化してしまい、有機EL素子127に流れる電流量が変化し、その結果、発光輝度は変化してしまうのである。

発光素子の一例である有機EL素子127の特性の経時変動による有機EL素子127のアノード電位変動は、駆動トランジスタ121のゲート・ソース間電圧Vgsの変動となって現れ、ドレイン電流(駆動電流Ids)の変動を引き起こす。この原因による駆動電流の変動は画素回路Pごとの発光輝度のばらつきとなって現れ、画質の劣化が起きる。

これに対して、詳細は後述するが、駆動トランジスタ121のソース端Sの電位Vsの変動にゲート端Gの電位Vgが連動するようにするブートストラップ機能を実現する回路構成および駆動タイミングとすることで、有機EL素子127の特性の経時変動による有機EL素子127のアノード電位変動(つまりソース電位変動)があっても、その変動を相殺するようにゲート電位Vgを変動させることで、画面輝度の均一性(ユニフォーミティ)を確保できる。ブートストラップ機能が、有機EL素子を代表とする電流駆動型の発光素子の経時劣化補正能力を向上させることができる。

もちろん、このブートストラップ機能は、発光開始時点で、有機EL素子127に発光電流Ielが流れ始め、それによってアノード・カソード間電圧Velが安定となるまで上昇していく過程で、そのアノード・カソード間電圧Velの変動に伴って駆動トランジスタ121のソース電位Vsが変動する際にも機能する。

<駆動トランジスタのVgs−Ids特性>

また、駆動トランジスタ121の製造プロセスのばらつきにより、画素回路Pごとに閾値電圧や移動度などの特性変動がある。駆動トランジスタ121を飽和領域で駆動する場合においても、この特性変動により、駆動トランジスタ121に同一のゲート電位を与えても、画素回路Pごとにドレイン電流(駆動電流Ids)が変動し、発光輝度のばらつきになって現れる。

たとえば、図3(2)は、駆動トランジスタ121の閾値ばらつきに着目した電圧電流(Vgs−Ids)特性を示す図である。閾値電圧がVth1とVth2で異なる2個の駆動トランジスタ121について、それぞれ特性カーブを挙げてある。

前述のように、駆動トランジスタ121が飽和領域で動作しているときのドレイン電流Idsは、特性式(1)で表される。特性式(1)から明らかなように、閾値電圧Vthが変動すると、ゲート・ソース間電圧Vgsが一定であってもドレイン電流Idsが変動する。つまり、閾値電圧Vthのばらつきに対して何ら対策を施さないと、図3(2)に示すように、閾値電圧がVth1のときVgsに対応する駆動電流がIds1となるのに対して、閾値電圧がVth2のときの同じゲート電圧Vgsに対応する駆動電流Ids2はIds1と異なってしまう。

また、図3(3)は、駆動トランジスタ121の移動度ばらつきに着目した電圧電流(Vgs−Ids)特性を示す図である。移動度がμ1とμ2で異なる2個の駆動トランジスタ121について、それぞれ特性カーブを挙げてある。

特性式(1)から明らかなように、移動度μが変動すると、ゲート・ソース間電圧Vgsが一定であってもドレイン電流Idsが変動する。つまり、移動度μのばらつきに対して何ら対策を施さないと、図3(3)に示すように、移動度がμ1のときゲート・ソース間電圧Vgsに対応する駆動電流がIds1となるのに対して、移動度がμ2のときの同じゲート・ソース間電圧Vgsに対応する駆動電流Ids2はIds1と異なってしまう。

<閾値補正および移動度補正の概念>

これに対して、閾値補正機能および移動度補正機能を実現する駆動タイミング(詳細は後述する)とすることで、図3Aの各図から理解されるように、それらの変動の影響を抑制でき、画面輝度の均一性(ユニフォーミティ)を確保できる。

本実施形態の閾値補正動作および移動度補正動作では、詳細は後述するが、書込みゲインが1(理想値)であると仮定した場合、発光時のゲート・ソース間電圧Vgsが“Vin+Vth−ΔV”で表されるようにすることで、ドレイン・ソース間電流Idsが、閾値電圧Vthのばらつきや変動に依存しないようにするとともに、移動度μのばらつきや変動に依存しないようにする。結果として、閾値電圧Vthや移動度μが製造プロセスにより変動しても、駆動電流Idsは変動せず、有機EL素子127の発光輝度も変動しない。

たとえば、図3Aの各図においては、駆動トランジスタ121の電流電圧特性を、横軸に信号振幅Vinをとり、縦軸に駆動電流Idsをとって、閾値電圧Vthが比較的低く移動度μが比較的大きい駆動トランジスタ121で構成された画素回路Pa(実線のカーブ)と、逆に閾値電圧Vthが比較的高く移動度μが比較的小さい駆動トランジスタ121で構成された画素回路Pb(点線のカーブ)について、それぞれ特性カーブを挙げてある。

図3A(1)は、閾値補正および移動度補正ともに実行しない場合である。このときには画素回路Paおよび画素回路Pbで閾値電圧Vthおよび移動度μの補正が全く実行されないため、閾値電圧Vthや移動度μの違いでVin−Ids特性に大きな違いが出てしまう。したがって、同じ信号振幅Vinを与えても、駆動電流Idsすなわち発光輝度が異なってしまい、画面輝度の均一性(ユニフォーミティ)が得られない。

図3A(2)は、閾値補正を実行する一方、移動度補正を実行しない場合である。このとき画素回路Paと画素回路Pbで閾値電圧Vthの違いはキャンセルされる。しかしながら移動度μの相違はそのまま現れている。したがって信号振幅Vinが高い領域(すなわち輝度が高い領域)で、移動度μの違いが顕著に現れ、同じ階調でも輝度が違ってしまう。具体的には、同じ階調(同じ信号振幅Vin)で、移動度μの大きい画素回路Paの輝度(駆動電流Ids)は高く、移動度μの小さい画素回路Pbの輝度は低くなる。

図3A(3)は閾値補正および移動度補正ともに実行する場合である。閾値電圧Vthおよび移動度μの相違は完全に補正され、その結果、画素回路Paと画素回路PbのVin−Ids特性は一致する。したがって、全ての階調(信号振幅Vin)で輝度(Ids)が同一レベルとなり、画面輝度の均一性(ユニフォーミティ)が顕著に改善される。

図3A(4)は、閾値補正および移動度補正ともに実行するものの、閾値電圧Vthの補正が不十分な場合である。たとえば、1回の閾値補正動作では駆動トランジスタ121の閾値電圧Vthに相当する電圧を十分に保持容量120へ保持させることができない場合がその一例である。このときには、閾値電圧Vthの差が除去されないため、画素回路Paと画素回路Pbでは低階調の領域で輝度(駆動電流Ids)に差が出てしまう。よって、閾値電圧Vthの補正が不十分な場合は低階調で輝度のムラが現れ画質を損なうことになる。

<画素回路の動作>

第1比較例の画素回路Pにおける有機EL素子127の経時劣化による駆動電流変動を防ぐ回路(ブートストラップ回路)を搭載し、また駆動トランジスタ121の特性変動(閾値電圧ばらつきや移動度ばらつき)による駆動電流変動を防ぐ駆動方式を採用したのが図2および図2Aに示す本実施形態や図示しない第2比較例(補助容量310を備えていない構成)の画素回路Pである。

第2比較例(事実上、本実施形態の画素回路Pも同様;以下駆動タイミングに関して同様)の画素回路Pにおいて、駆動タイミングとしては、先ず、サンプリングトランジスタ125は、書込走査線104WSから供給された書込駆動パルスWSに応じて導通し、映像信号線106HSから供給された映像信号Vsig をサンプリングして保持容量120に保持する。この点は、基本的には、第1比較例の画素回路Pを駆動する場合と同じである。

以下では、説明や理解を容易にするため、特段の断りのない限り、書込みゲインが1(理想値)であると仮定して、保持容量120に信号振幅Vinの情報を、書き込む、保持する、あるいはサンプリングするなどと簡潔に記して説明する。書込みゲインが1未満の場合、保持容量120には信号振幅Vinの大きさそのものではなく、信号振幅Vinの大きさに対応するゲイン倍された情報が保持されることになる。

なお、第2比較例の画素回路Pにおける駆動タイミングは、映像信号Vsig の信号振幅Vinの情報を保持容量120に書き込む際に、順次走査の観点からは、1行分の映像信号を同時に各列の映像信号線106HSに伝達する線順次駆動を行なう。

駆動トランジスタ121は、第1電位(高電位側)にある電源供給線105DSL から電流の供給を受け保持容量120に保持された信号電位(映像信号Vsig の有効期間の電位に対応する電位)に応じて駆動電流Idsを有機EL素子127に流す。

垂直駆動部103は、電源供給線105DSL が第1電位にありかつ映像信号線106HSが映像信号Vsig の非有効期間である基準電位Vo(Vofs )にある時間帯でサンプリングトランジスタ125を導通させる制御信号として書込駆動パルスWSを出力して、駆動トランジスタ121の閾値電圧Vthに相当する電圧を保持容量120に保持しておく。この動作が閾値補正機能を実現する。この閾値補正機能により、画素回路Pごとにばらつく駆動トランジスタ121の閾値電圧Vthの影響をキャンセルすることができる。

第2比較例の画素回路Pにおける駆動タイミングとしては、垂直駆動部103は、映像信号Vsig の内の信号振幅Vinのサンプリングに先行する複数の水平期間で閾値補正動作を繰り返し実行して確実に駆動トランジスタ121の閾値電圧Vthに相当する電圧を保持容量120に保持するようにするのがよい。

このように、第2比較例の画素回路Pにおいて、閾値補正動作を複数回実行することで、十分に長い書込み時間を確保する。こうすることで、駆動トランジスタ121の閾値電圧Vthに相当する電圧を確実に保持容量120に予め保持することができる。

この保持された閾値電圧Vthに相当する電圧は駆動トランジスタ121の閾値電圧Vthのキャンセルに用いられる。したがって、画素回路Pごとに駆動トランジスタ121の閾値電圧Vthがばらついていても、画素回路Pごとに完全にキャンセルされるため、画像のユニフォーミティすなわち表示装置の画面全体に亘る発光輝度の均一性が高まる。特に信号電位が低階調のときに現れがちな輝度ムラを防ぐことができる。

好ましくは、垂直駆動部103は、閾値補正動作に先立って、電源供給線105DSL が第2電位にありかつ映像信号線106HSが映像信号Vsig の非有効期間である基準電位Vo(Vofs )にある時間帯で、書込駆動パルスWSをアクティブ(本例ではHレベル)にしてサンプリングトランジスタ125を導通させ、その後に書込駆動パルスWSをアクティブHにしたままで電源供給線105DSL を第1電位に設定する。

こうすることで、駆動トランジスタ121のゲート端Gを基準電位Vo(Vofs )にセットしかつソース端Sを第2電位にセットしてから閾値補正動作を開始する。このようなゲート電位およびソース電位のリセット動作(初期化動作)により、後続する閾値補正動作を確実に実行することが可能になる。

また、第2比較例の画素回路Pにおいては、閾値補正機能に加えて、移動度補正機能を備えている。すなわち、垂直駆動部103は、映像信号線106HSが映像信号Vsig の有効期間である信号電位(基準電位Vo+信号振幅Vin)にある時間帯にサンプリングトランジスタ125を導通状態にするため、書込走査線104WSに供給する書込駆動パルスWSを、上述の時間帯より短い期間だけアクティブ(本例ではHレベル)にする。この書込駆動パルスWSのアクティブ期間(サンプリング期間でもあり移動度補正期間でもある)を適切に設定することで、保持容量120に信号電位Vsig を保持する際、同時に駆動トランジスタ121の移動度μに対する補正を信号電位Vsig に加える。

特に、第2比較例の画素回路Pにおける駆動タイミングでは、電源供給線105DSL が高電位側である第1電位にあり、かつ、映像信号Vsig が有効期間にある時間帯内で書込駆動パルスWSをアクティブにしている。つまり、その結果、移動度補正時間(サンプリング期間も)は、映像信号線106HSの電位が、映像信号Vsig の有効期間の電位(信号線電位)にある時間幅と書込駆動パルスWSのアクティブ期間の両者が重なった範囲で決まる。特に、本実施形態では、映像信号線106HSが信号電位にある時間幅の中に入るように書込駆動パルスWSのアクティブ期間幅を細めに決めているため、結果的に移動度補正時間は書込駆動パルスWSで決まる。

正確には、移動度補正時間(サンプリング期間も)は、書込駆動パルスWS立ち上がってサンプリングトランジスタ125がオンしてから、同じく書込駆動パルスWSが立ち下がってサンプリングトランジスタ125がオフするまでの時間となる。

また、第2比較例の画素回路Pにおいては、ブートストラップ機能も備えている。すなわち、書込走査部104は、保持容量120に信号振幅Vinの情報が保持された段階で書込走査線104WSに対する書込駆動パルスWSの印加を解除し(すなわちインアクティブL(ロー)にして)、サンプリングトランジスタ125を非導通状態にして駆動トランジスタ121のゲート端Gを映像信号線106HSから電気的に切り離す。

駆動トランジスタ121のゲート端Gとソース端Sと間には保持容量120が接続されており、その保持容量120による効果によって、駆動トランジスタ121のソース電位Vsの変動にゲート電位Vgが連動するようになり、ゲート・ソース間電圧Vgsを一定に維持することができる。

<タイミングチャート:第2比較例>

図4は、第2比較例や図2および図2Aに示した本実施形態の画素回路Pに関する駆動タイミングの一例として、線順次方式で信号振幅Vinの情報を保持容量120に書き込む際の動作を説明するタイミングチャートである。

図4においては、時間軸を共通にして、書込走査線104WSの電位変化、電源供給線105DSL の電位変化、および映像信号線106HSの電位変化を表してある。また、これらの電位変化と並行に、1行分(図では1行目)について駆動トランジスタ121のゲート電位Vgおよびソース電位Vsの変化も表してある。

基本的には、書込走査線104WSや電源供給線105DSL の1行ごとに、1水平走査期間だけ遅れて同じような駆動を行なう。図4における各タイミングや信号は、処理対象行を問わず、第1行目のタイミングや信号と同じタイミングや信号で示す。そして、説明中において区別が必要とされるときには、そのタイミングや信号に、処理対象行を“_ ”付きの参照子で示すことで区別する。

また、第2比較例の画素回路Pにおける駆動タイミングでは、映像信号Vsig が非有効期間である基準電位Vo(Vofs )にある期間を1水平期間の前半部とし、有効期間である信号電位(Vofs +Vin)にある期間を1水平期間の後半部とする。

ここでは、閾値補正動作を1回のみ実行する事例で説明するが、このことは必須ではない。1水平期間を処理サイクルとして、閾値補正動作を複数回に亘って繰り返すようにしてもよい。

なお、閾値補正動作を複数回実行する場合に、1水平期間が閾値補正動作の処理サイクルとなるのは、行ごとに、サンプリングトランジスタ125が信号振幅Vinの情報を保持容量120にサンプリングする前に、閾値補正動作に先立って、電源供給線105DSL の電位を第2電位Vcc_Lにセットし、また駆動トランジスタ121のゲートを基準電位Vinにセットし、さらにソース電位を第2電位Vcc_Lにセットする初期化動作を経てから、電源供給線105DSL の電位が第1電位Vcc_Hにある状態でかつ映像信号線106HSが基準電位Vo(Vofs )にある時間帯でサンプリングトランジスタ125を導通させて駆動トランジスタ121の閾値電圧Vthに対応する電圧を保持容量120に保持させようとする閾値補正動作を行なうからである。

必然的に、閾値補正期間は、1水平期間よりも短くなってしまう。したがって、保持容量120の容量Csや第2電位Vcc_Lの大きさ関係やその他の要因で、この短い1回分の閾値補正動作期間では、閾値電圧Vthに対応する正確な電圧を保持容量120に保持仕切れないケースも起こり得る。閾値補正動作を複数回実行するのが好ましいのは、この対処のためである。すなわち、信号振幅Vinの保持容量120へのサンプリング(信号書込み)に先行する複数の水平周期で、閾値補正動作を繰り返し実行することで確実に駆動トランジスタ121の閾値電圧Vthに相当する電圧を保持容量120に保持させるのである。

ある行(ここでは第1行目とする)について、タイミングt11以前の前フィールドの発光期間Bでは、書込駆動パルスWSがインアクティブLでありサンプリングトランジスタ125が非導通状態である一方、電源駆動パルスDSL は高電位の電源電圧側である第1電位Vcc_Hにある。

したがって、映像信号線106HSの電位に関わらず、前フィールドの動作によって保持容量120に保持されている電圧状態(駆動トランジスタ121のゲート・ソース間電圧Vgs)に応じて有機EL素子127に駆動トランジスタ121から駆動電流Idsが供給され、全画素共通の接地配線Vcath(GND )に流れ込むことで、有機EL素子127が発光状態にある。

この後、線順次走査の新しいフィールドに入って、先ず、駆動走査部105は、書込駆動パルスWSがインアクティブLにある状態で、1行目の電源供給線105DSL_1 に与える電源駆動パルスDSL_1 を高低電位側の第1電位Vcc_Hから低電位側の第2電位Vcc_Lに切り替える(t11_1)。

このタイミング(t11_1)は、図4に示す態様では、映像信号Vsig が有効期間の信号電位(Vofs +Vin)にある期間内としている。たとえば、1行目については、タイミングt15V〜t13Vの範囲内である。ただし、このことは必須ではなく、映像信号Vsig が非効期間の基準電位Vo(Vofs )にあるときにしてもよい。1行目については、タイミングt13V〜t15Vの範囲内とすればよい。

次に、書込走査部104は、電源供給線105DSL_1 が第2電位Vcc_Lにある状態のままで、書込駆動パルスWSをアクティブHに切り替える(t13W)。このタイミング(t13W)は、直前の水平期間における映像信号Vsig が非有効期間である基準電位Vo(Vofs )から有効期間の信号電位(Vofs +Vin)に切り替わり(t15V)、その後に、当該水平期間における映像信号Vsig の有効期間の信号電位(Vofs +Vin)から非有効期間である基準電位Vo(Vofs )に切り替わるタイミング(t13V)と同じかそれよりも少し遅れたタイミングにする。この後に書込駆動パルスWSをインアクティブLに切り替えるタイミング(t15W)は、映像信号Vsig が非有効期間である基準電位Vo(Vofs )から有効期間の信号電位(Vofs +Vin)に切り替わるタイミング(t15V)と同じかそれよりも少し前のタイミングにする。

つまり、好ましくは、書込駆動パルスWSをアクティブHにする期間(t13W〜t15W)は、映像信号Vsig が非有効期間である基準電位Vo(Vofs )にある時間帯(t13V〜t15V)内とする。これは、電源供給線105DSL が第1電位Vcc_Hにある状態のときで映像信号Vsig が信号電位(Vofs +Vin)にあるときに書込駆動パルスWSをアクティブHにすると信号振幅Vinの保持容量120へのサンプリング動作(信号電位の書込み動作)がなされてしまい、閾値補正動作としては不都合が生じるからである。

タイミングt11_1〜t13W(放電期間Cと称する)では、電源供給線105DSL の電位は第2電位Vcc_Lまで放電され、さらに駆動トランジスタ121のソース電位Vsは第2電位Vcc_Lに近い電位まで遷移する。さらに、駆動トランジスタ121のゲート端Gとソース端Sと間には保持容量120が接続されており、その保持容量120による効果によって、駆動トランジスタ121のソース電位Vsの変動にゲート電位Vgが連動する。

電源供給線105DSL の配線容量が大きい場合は比較的早いタイミングで電源供給線105DSL を高電位Vcc_Hから低電位Vcc_Lに切り替えるとよい。この放電期間C(t11_1〜t13W)を十分に確保することで、配線容量やその他の画素寄生容量の影響を受けないようにしておく。

電源駆動パルスDSL を低電位側の第2電位Vcc_Lにしたままで、書込駆動パルスWSをアクティブHに切り替えると(t13W)、サンプリングトランジスタ125が導通状態になる。

このとき、映像信号線106HSは基準電位Vo(Vofs )にある。したがって、駆動トランジスタ121のゲート電位Vgは導通したサンプリングトランジスタ125を通じて映像信号線106HSの基準電位Vo(Vofs )となる。これと同時に、駆動トランジスタ121がオンすることで、駆動トランジスタ121のソース電位Vsは即座に低電位側の第2電位Vcc_Lに固定される。

つまり、電源供給線105DSL の電位が高電位側の第1電位Vcc_Hから映像信号線106HSの基準電位Vo(Vofs )より十分低い第2電位Vcc_Lにあることで、駆動トランジスタ121のソース電位Vsが映像信号線106HSの基準電位Vo(Vofs )より十分低い第2電位Vcc_Lに初期化(リセット)される。このようにして、駆動トランジスタ121のゲート電位Vgおよびソース電位Vsを初期化することで、閾値補正動作の準備が完了する。次に電源駆動パルスDSL を高電位側の第1電位Vcc_Hにするまでの期間(t13W〜t14_1)が、初期化期間Dとなる。なお、放電期間Cと初期化期間Dとを合わせて、駆動トランジスタ121のゲート電位Vgとソース電位Vsを初期化する閾値補正準備期間とも称する。

次に、書込駆動パルスWSをアクティブHにしたままで、電源供給線105DSL に与える電源駆動パルスDSL を第1電位Vcc_Hに切り替える(t14_1)。駆動走査部105は、それ以降は、次のフレーム(あるいはフィールド)の処理まで、電源供給線105DSL の電位を第1電位Vcc_Hに保持しておく。

これにより、ドレイン電流が保持容量120に流れ込み、駆動トランジスタ121の閾値電圧Vthを補正(キャンセル)する閾値補正期間Eに入る。この閾値補正期間Eは、書込駆動パルスWSがインアクティブLにされるタイミング(t15W)まで継続する。

タイミング(t14_1)以降の閾値補正期間Eでは、電源供給線105DSL の電位が低電位側の第2電位Vcc_Lから高電位側の第1電位Vcc_Hに遷移することで、駆動トランジスタ121のソース電位Vsが上昇を開始する。

すなわち、駆動トランジスタ121のゲート端Gは映像信号Vsig の基準電位Vo(Vofs )に保持されており、駆動トランジスタ121のソース端Sの電位Vsが上昇して駆動トランジスタ121がカットオフするまでドレイン電流が流れようとする。カットオフすると駆動トランジスタ121のソース電位Vsは“Vo−Vth”となる。

なお、閾値補正期間Eでは、ドレイン電流が専ら保持容量120側(Cs<<Cel時)に流れ、有機EL素子127側には流れないようにするため、有機EL素子127がカットオフとなるように共通接地配線cathの電位Vcathを設定しておく。

有機EL素子127の等価回路はダイオードと寄生容量Celの並列回路で表されるため、“Vel≦Vcath+VthEL”である限り、つまり、有機EL素子127のリーク電流が駆動トランジスタ121に流れる電流よりもかなり小さい限り、駆動トランジスタ121の電流は保持容量120と寄生容量Celを充電するために使われる。

この結果、駆動トランジスタ121を流れるドレイン電流の電流路が遮断されると、有機EL素子127のアノード端Aの電圧VelつまりノードND121の電位は、時間とともに上昇してゆく。そして、ノードND121の電位(ソース電位Vs)とノードND122の電圧(ゲート電位Vg)との電位差がちょうど閾値電圧Vthとなったところで駆動トランジスタ121はオン状態からオフ状態となり、ドレイン電流は流れなくなり、閾値補正期間が終了する。つまり、一定時間経過後、駆動トランジスタ121のゲート・ソース間電圧Vgsは閾値電圧Vthという値をとる。

ここで、実際には、閾値電圧Vthに相当する電圧が、駆動トランジスタ121のゲート端Gとソース端Sと間に接続された保持容量120に書き込まれることになる。しかしながら、閾値補正期間Eは、書込駆動パルスWSをアクティブHにしたタイミング(t13W)(詳しくはその後に電源駆動パルスDSL を第1電位Vcc_Hに戻した時点t14)からインアクティブLに戻すタイミング(t15W)までであり、この期間が十分に確保されていないときには、それ以前に終了してしまうこととなる。この問題を解消するには、閾値補正動作を複数回繰り返すのがよい。ここでは、そのタイミングについては図示を割愛する。

次に、駆動走査部105は、1水平期間の後半部で、書込駆動パルスWSをインアクティブLに切り替え(t15W)、さらに水平駆動部106は、映像信号線106HSの電位を基準電位Vo(Vofs )から信号振幅Vin分上昇させる(t15V)。これにより、タイミングt15W〜t15Vにおいては、映像信号線106HSが基準電位Vo(Vofs )にある状態で、書込走査線104WSの電位(書込駆動パルスWS)はローレベルになる。

この後、水平駆動部106により映像信号線106HSに信号電位(Vofs +Vin)を実際に供給して、書込駆動パルスWSをアクティブHにする期間を、保持容量120への信号振幅Vinの情報の書込み期間(サンプリング期間とも称する)とする。この信号振幅Vinの情報は駆動トランジスタ121の閾値電圧Vthに足し込む形で保持される。

この結果、駆動トランジスタ121の閾値電圧Vthの変動は常にキャンセルされる形となるので、閾値補正を行なっていることになる。この閾値補正によって、保持容量120に保持されるゲート・ソース間電圧Vgsは、“Vsig +Vth”=“Vin+Vth”となる。また、同時に、このサンプリング期間で移動度補正を実行する。すなわち、第2比較例の画素回路Pにおける駆動タイミングにおいて、サンプリング期間は移動度補正期間を兼ねることとなる。

具体的には、先ず、書込駆動パルスWSをインアクティブLに切り替えた後(t15W)、さらに水平駆動部106は、映像信号線106HSの電位を基準電位Vo(Vofs )から信号電位(Vofs +Vin)に切り替える(t15V)。こうすることで、サンプリングトランジスタ125が非導通(オフ)状態とされた状態で、次のサンプリング動作および移動度補正動作の準備が完了する。次に書込駆動パルスWSをアクティブHにするタイミング(t16_1)まで期間を書込み&移動度補正準備期間Gと称する。

次に、電源供給線105DSL の電位を第1電位Vcc_Hにし、かつ、映像信号線106HSの電位を信号電位(Vofs +Vin)に保持したままで、書込走査部104は、書込駆動パルスWSをアクティブHに切り替え(t16_1)、水平駆動部106が映像信号線106HSの電位を信号電位(Vofs +Vin)から基準電位Vo(Vofs )に切り替えるタイミング(t18_1)までの間での適当なタイミングで、つまり、映像信号線106HSが信号電位(Vofs +Vin)にある時間帯での適当なとき、インアクティブLに切り替える(t17_1)。この書込駆動パルスWSがアクティブHにある期間(t16_1〜t17_1)を、書込み(サンプリング)&移動度補正期間Hと称する。

これにより、駆動トランジスタ121のゲート電位Vgが信号電位(Vofs +Vin)にある状態でサンプリングトランジスタ125が導通(オン)状態となる。したがって、書込み&移動度補正期間Hでは、駆動トランジスタ121のゲート端Gが映像信号Vsig の信号電位(Vofs +Vin)に固定された状態で、駆動トランジスタ121に駆動電流Idsが流れる。

ここで、有機EL素子127の閾値電圧をVthELとしたとき、“Vo−Vth<VthEL”と設定しておくことで、有機EL素子127は、逆バイアス状態におかれ、カットオフ状態(ハイインピーダンス状態)にあるため、発光することはなく、また、ダイオード特性ではなく単純な容量特性を示すようになる。よって駆動トランジスタ121に流れるドレイン電流(駆動電流Ids)は保持容量120の容量値Csと有機EL素子127の寄生容量(等価容量)Celの容量値Celの両者を結合した容量“C=Cs+Cel”に書き込まれていく。これにより、駆動トランジスタ121のドレイン電流は有機EL素子127の寄生容量Celに流れ込み充電を開始する。その結果、駆動トランジスタ121のソース電位Vsは上昇していく。

図4のタイミングチャートでは、この上昇分をΔVで表してある。この上昇分、すなわち移動度補正パラメータである負帰還量ΔVは、閾値補正によって保持容量120に保持されるゲート・ソース間電圧“Vgs=Vin+Vth”から差し引かれることになり、“Vgs=Vin−ΔV+Vth”となるので、負帰還をかけたことになる。このとき、駆動トランジスタ121のソース電位Vsは、ゲート電位Vg(=Vin)から保持容量に保持される電圧“Vgs=Vin−ΔV+Vth”を差し引いた値“−Vth+ΔV”となる。

このようにして、第2比較例の画素回路Pにおける駆動タイミングでは、書込み&移動度補正期間H(t16〜t17)において、信号振幅Vinのサンプリングと移動度μを補正する負帰還量(移動度補正パラメータ)ΔVの調整が行なわれる。書込走査部104は、書込み&移動度補正期間Hの時間幅を調整可能であり、これにより保持容量120に対する駆動電流Idsの負帰還量を最適化することができる。

ここで「負帰還量を最適化する」とは、映像信号電位の黒レベルから白レベルまでの範囲で、どのレベルにおいても適切に移動度補正を行なうことができるようにすることを意味する。ゲート・ソース間電圧Vgsにかける負帰還量は、ドレイン電流Idsの取り出し時間すなわち書込み&移動度補正期間Hに依存しており、この期間を長くとる程、負帰還量が大きくなる。負帰還量ΔVはΔV=Ids・Cel/tである。

この式から明らかなように、駆動トランジスタ121のドレイン・ソース間電流である駆動電流Idsが大きい程、負帰還量ΔVは大きくなる。逆に、駆動トランジスタ121の駆動電流Idsが小さいとき、負帰還量ΔVは小さくなる。このように、負帰還量ΔVは駆動電流Idsに応じて決まる。

また、信号振幅Vinが大きいほど駆動電流Idsは大きくなり、負帰還量ΔVの絶対値も大きくなる。したがって、発光輝度レベルに応じた移動度補正を実現できる。その際、書込み&移動度補正期間Hは必ずしも一定である必要はなく、逆に駆動電流Idsに応じて調整することが好ましい場合がある。たとえば、駆動電流Idsが大きい場合、移動度補正期間tは短めにし、逆に駆動電流Idsが小さくなると、書込み&移動度補正期間Hは長めに設定するのがよい。

また、負帰還量ΔVは、Ids・Cel/tであり、画素回路Pごとに移動度μのばらつきに起因して駆動電流Idsがばらつく場合でも、それぞれに応じた負帰還量ΔVとなるので、画素回路Pごとの移動度μのばらつきを補正することができる。つまり、信号振幅Vinを一定とした場合、駆動トランジスタ121の移動度μが大きいほど負帰還量ΔVの絶対値が大きくなる。換言すると、移動度μが大きいほど負帰還量ΔVが大きくなるので、画素回路Pごとの移動度μのばらつきを取り除くことができる。

このようにして、第2比較例の画素回路Pにおける駆動タイミングでは、書込み&移動度補正期間Hにて、信号振幅Vinのサンプリングと移動度μのばらつきを補正するための負帰還量ΔVの調整が同時に行なわれる。もちろん、負帰還量ΔVは書込み&移動度補正期間Hの時間幅を調整することで最適化可能である。

次に、書込走査部104は、映像信号線106HSの電位が信号電位(Vofs +Vin)にある状態で、書込駆動パルスWSをインアクティブLに切り替える(t17_1)。これにより、サンプリングトランジスタ125が非導通(オフ)状態となり発光期間Iに進む。水平駆動部106は、その後の適当な時点で映像信号線106HSの電位を基準電位Vo(Vofs )に戻す(t18_1)。この後、次のフレーム(もしくはフィールド)に移って、再び、閾値補正準備動作、閾値補正動作、移動度補正動作、および発光動作が繰り返される。

この結果、駆動トランジスタ121のゲート端Gは映像信号線106HSから切り離される。駆動トランジスタ121のゲート端Gへの信号電位(Vofs +Vin)の印加が解除されるので、駆動トランジスタ121のゲート電位Vgは上昇可能となる。

このとき、駆動トランジスタ121に流れる駆動電流Idsは有機EL素子127に流れ、有機EL素子127のアノード電位は駆動電流Idsに応じて上昇する。この上昇分をVelとする。やがて、ソース電位Vsの上昇に伴い、有機EL素子127の逆バイアス状態は解消されるので、駆動電流Idsの流入により有機EL素子127は実際に発光を開始する。このときの有機EL素子127のアノード電位の上昇(Vel)は、駆動トランジスタ121のソース電位Vsの上昇に他ならず、駆動トランジスタ121のソース電位Vsは、“−Vth+ΔV+Vel”となる。

駆動電流Ids対ゲート電圧Vgsの関係は、先のトランジスタ特性を表した式(1)のVgsに“Vin−ΔV+Vth”を代入することで、式(2)のように表すことができる。式(2)において、k=(1/2)(W/L)Coxである。

この式(2)から、閾値電圧Vthの項がキャンセルされており、有機EL素子127に供給される駆動電流Idsは駆動トランジスタ121の閾値電圧Vthに依存しないことが分かる。基本的に駆動電流Idsは映像信号Vsig の信号振幅Vin(詳しくは信号振幅Vinに対応して保持容量120に保持されるサンプリング電圧=Vgs_121)によって決まる。換言すると、有機EL素子127は信号振幅Vinに応じた輝度で発光することになる。

その際、保持容量120に保持される信号振幅Vinの情報は帰還量ΔVで補正されている。この補正量ΔVはちょうど式(2)の係数部に位置する移動度μの効果を打ち消すように働く。したがって、駆動電流Idsは実質的に信号振幅Vinのみに依存することになる。駆動電流Idsは閾値電圧Vthに依存しないので、閾値電圧Vthが製造プロセスにより変動しても、ドレイン・ソース間の駆動電流Idsは変動せず、有機EL素子127の発光輝度も変動しない。

また、駆動トランジスタ121のゲート端Gとソース端Sと間には保持容量120が接続されており、その保持容量120による効果により、発光期間の最初でブートストラップ動作が行なわれる。ブートストラップゲインが1(理想値)であると仮定した場合、駆動トランジスタ121のゲート・ソース間電圧“Vgs=Vin−ΔV+Vth”を一定に維持したまま、駆動トランジスタ121のゲート電位Vgおよびソース電位Vsが上昇する。駆動トランジスタ121のソース電位Vsが“−Vth+ΔV+Vel”となることで、ゲート電位Vgは“Vin+Vel”となる。

このとき、駆動トランジスタ121のゲート・ソース間電圧Vgsは一定であるので、駆動トランジスタ121は、一定電流(駆動電流Ids)を有機EL素子127に流す。その結果、電圧降下が生じ、有機EL素子127のアノード端Aの電位Vel(=ノードND121の電位)は、有機EL素子127に飽和状態での駆動電流Idsという電流が流れ得る電圧まで上昇する。

ここで、有機EL素子127は、発光時間が長くなるとそのI−V特性が変化してしまう。そのため、時間の経過とともに、ノードND121の電位も変化する。しかしながら、このような有機EL素子127の経時劣化によりそのアノード電位が変動しても、保持容量120に保持されたゲート・ソース間電圧Vgsは常に“Vin−ΔV+Vth”で一定に維持される。

駆動トランジスタ121が定電流源として動作することから、有機EL素子127のI−V特性が経時変化し、これに伴って駆動トランジスタ121のソース電位Vsが変化したとしても、保持容量120によって駆動トランジスタ121のゲート・ソース間電位Vgsが一定(≒Vin−ΔV+Vth)に保たれているため、有機EL素子127に流れる電流は変わらず、したがって有機EL素子127の発光輝度も一定に保たれる。

このような、有機EL素子127の特性変動に拘らず、駆動トランジスタ121のゲート・ソース間電圧を一定に維持し輝度を一定に維持する補正のための動作(保持容量120の効果による動作)をブートストラップ動作と呼ぶ。このブートストラップ動作により、有機EL素子127のI−V特性が経時的に変化しても、それに伴う輝度劣化のない画像表示が可能になる。

つまり、第2比較例の画素回路Pとそれを駆動する駆動タイミングでは、電気光学素子の一例である有機EL素子127の電流−電圧特性の変化を補正して駆動電流を一定に維持する駆動信号一定化回路の一例であるブートストラップ回路が構成され、ブートストラップ動作が機能するようになっているのである。よって、有機EL素子127のI−V特性が劣化しても一定電流Idsが常に流れ続けるため、有機EL素子127は画素信号Vsig に応じた輝度で発光を続けることになり輝度が変化することはない。

また、第2比較例の画素回路Pとそれを駆動する駆動タイミングでは、駆動トランジスタ121の閾値電圧Vthを補正して駆動電流を一定に維持する駆動信号一定化回路の一例である閾値補正回路が構成され閾値補正動作が機能するようになっている。駆動トランジスタ121の閾値電圧Vthを反映させたゲート・ソース間電位Vgsとして、当該閾値電圧Vthのばらつきの影響を受けない一定電流Idsを流すことができる。

特に、図示を割愛しているが、1回の閾値補正動作の処理サイクルを1水平期間とし、複数回に亘って閾値補正動作を繰り返すようにすれば、確実に閾値電圧Vthを保持容量120に保持させることができる。閾値電圧Vthの画素間差が確実に除去され、階調に拘らず閾値電圧Vthのばらつきに起因する輝度ムラを抑制できる。

これに対して、閾値補正動作を1回にするなど閾値電圧Vthの補正が不十分な場合は、つまり閾値電圧Vthが保持容量120に保持されていない場合には、異なる画素回路Pの間で、低階調の領域では輝度(駆動電流Ids)に差が出てしまう。よって閾値電圧の補正が不十分な場合は、低階調で輝度のムラが現れ画質を損なうことになる。

加えて、第2比較例の画素回路Pにおける駆動タイミングでは、サンプリングトランジスタ125による信号振幅Vinの保持容量120への書込み動作と連動して駆動トランジスタ121の移動度μを補正して駆動電流を一定に維持する駆動信号一定化回路の一例である移動度補正回路が構成され移動度補正動作が機能するようになっている。駆動トランジスタ121のキャリア移動度μを反映させたゲート・ソース間電位Vgsとして、当該キャリア移動度μのばらつきの影響を受けない一定電流Idsを流すことができる。

つまり、第2比較例の画素回路Pは、駆動タイミングを工夫することで、閾値補正回路や移動度補正回路が自動的に構成され、駆動トランジスタ121の特性ばらつき(本例では閾値電圧Vthおよびキャリア移動度μのばらつき)による駆動電流Idsに与える影響を防ぐために、閾値電圧Vthおよびキャリア移動度μによる影響を補正して駆動電流を一定に維持する駆動信号一定化回路として機能するようになっているのである。

ブートストラップ動作だけでなく、閾値補正動作と移動度補正動作とを実行しているため、ブートストラップ動作で維持されるゲート・ソース間電圧Vgsは、閾値電圧Vthに相当する電圧と移動度補正用の電圧ΔVとによって調整されているため、有機EL素子127の発光輝度は駆動トランジスタ121の閾値電圧Vthや移動度μのばらつきの影響を受けることがないし、有機EL素子127の経時劣化の影響も受けない。入力される信号振幅Vinに対応する安定した階調で表示でき、高画質の画像を得ることができる。

また、第2比較例の画素回路Pは、nチャネル型の駆動トランジスタ121を用いたソースフォロア回路によって構成することができるために、現状のアノード・カソード電極の有機EL素子をそのまま用いても、有機EL素子127の駆動が可能になる。

また、駆動トランジスタ121およびその周辺部のサンプリングトランジスタ125をも含めてnチャネル型のみのトランジスタを用いて画素回路Pを構成することができ、TFT作成においてもアモルファスシリコン(a−Si)プロセスを用いることができるようになるため、TFT基板の低コスト化が図れることになる。

<書込みゲインとブートストラップゲインの関係>

図5は、保持容量120への信号振幅Vinの情報の書込み動作時の書込みゲインと、信号書込み後のブートストラップ動作時のブートストラップゲインと、駆動トランジスタ121のゲート端Gに生じる寄生容量との関係を説明する図である。

ここでは、一例として、補助容量310を備えていない第2比較例の構成において、駆動トランジスタ121のゲート端Gには、寄生容量として、駆動トランジスタ121のゲート端Gとソース端Sと間に形成される寄生容量C125gs(容量値をCgsとする)と、駆動トランジスタ121のゲート端Gとドレイン端Dと間に形成される寄生容量C125gd(容量値をCgdとする)と、サンプリングトランジスタ125の拡散容量としてのゲート端Gとソース端S(ソース端Sを映像信号線106HS側とする場合はドレイン端D)と間に形成される寄生容量C125gs(容量値をCwsとする)とが存在するものとして示している。

ブートストラップ動作が機能する発光期間B,Lでは、駆動トランジスタ121のゲート端Gとソース端Sと間に保持容量120が接続されているので、ソース電位Vsの上昇時に、カップリング電圧がゲート端Gに加わる。ソース電位Vsの上昇に対するゲート電位Vgへのカップリング上昇が100%に近いほど、有機EL素子127の特性変化(劣化を含む)に伴う駆動電圧上昇時の輝度落ちが抑制される。

このソース電位Vsの上昇に対するゲート電位Vgの上昇率をブートストラップゲイン(ブートストラップ動作能力)Gbst0と称する。ブートストラップゲインGbst0は、保持容量120の容量値Cs、駆動トランジスタ121のゲート端Gに形成される寄生容量C121gsの容量値Cgs、寄生容量C121gdの容量値Cgd、および寄生容量C125gsの容量値Cwsを用いて、式(3)のように表すことができる。

したがって、ブートストラップゲインGbst0は、寄生容量C121gdの容量値Cgdや寄生容量C125gsの容量値Cwsが保持容量120の容量値Csに対して十分に小さければ、換言すれば、駆動トランジスタ121のゲート端Gとソース端Sの間に付加される容量値(ここでは容量値Cs)が大きいほど限りなく“1”に近いことになり、有機EL素子127の電流電圧特性の経時変動に対する駆動電流Idsの補正能力が高い。

つまり、画素回路の簡素化を図りつつ、素子の特性ばらつきによる輝度変化を抑制する閾値補正動作や移動度補正動作を実現する方式の開発に当たり、駆動トランジスタ121のゲート端Gに接続される保持容量120以外の素子数を最小限のサンプリングトランジスタ125のみに留めた画素回路Pとすることで、駆動トランジスタ121のゲート端Gに寄生する容量を限りなく小さくでき、このことはブートストラップ動作の補助となり、有機EL素子127の電流電圧特性の経時変動に対する駆動電流Idsの補正能力を向上させることが可能となる。

一方、書込み&移動度補正期間Hにおける信号書込み動作時には、信号振幅Vinの情報を如何に大きく保持容量120に書き込むかが肝要となる。信号振幅Vinに対応する保持容量120に書き込まれる情報の大きさの割合を、書込みゲインGinput と称する。

ここで、書込みゲインGinput は、具体的には、電気回路的に保持容量120と並列に配置される寄生容量を含めた全容量C1と、電気回路的に保持容量120と直列に配置される全容量C2との容量直列回路において、信号振幅Vinを容量直列回路に供給したときに容量C1に配分される電荷量に関係する。式で表せば、書込みゲインGinput =C2/(C1+C2)=1−C1/(C1+C2)となる。

たとえば、図4に示した駆動タイミングでは、書込み&移動度補正期間Hにて、電源駆動パルスDSL が第1電位Vcc_Hの状態で信号書込み(サンプリング)が行なわれるために、書込み動作が開始し、駆動トランジスタ121のゲート電位Vgが上昇した瞬間、ドレイン・ソース間に駆動電流Idsが流れ、この駆動電流Idsが有機EL素子127の寄生容量Celを充電することでソース電位Vsが上昇する。このため、書込み&移動度補正期間Hが長いほどソース電位Vsの上場度合いが大きくなり、発光時の駆動トランジスタ121のゲート・ソース電圧Vgsが小さくなり輝度が取れなくなる。

そこで、書込み&移動度補正期間Hを一般的な書込み期間よりも短くする必要がある。輝度が最も取れるのは、駆動トランジスタ121のゲート電位Vgの上昇カーブとソース電位Vsの上昇カーブの傾きが一致した点であり、そのポイントで書込み動作を終了する必要がある。

映像信号Vsig の信号振幅Vinに対して効率よく輝度を取るためには、書込み時に駆動トランジスタ121のゲート電位Vgの上昇とともに駆動電流Idsが流れてソース電位Vsが上昇しない条件下、すなわち書込み時に駆動トランジスタ121のソース電位Vsが低い状況での、映像信号Vsig (特に信号振幅Vin)に対する容量値Csの保持容量120に保持される電圧割合(書込みゲインGinput )をなるべく高くする必要がある。

このような条件下における書込みゲインGinput0は、保持容量120の容量値Cs、駆動トランジスタ121のゲート端Gに形成される寄生容量C121gsの容量値Cgs、および有機EL素子127の寄生容量Celを用いて、式(4)のように表すことができる。

寄生容量C121gsの容量値Cgsは、保持容量120の容量値Csや有機EL素子127の寄生容量Celに比べると小さいと考えてよく、したがって、書込みゲインGinput0は、保持容量120の容量値Csに対して有機EL素子127の寄生容量Celが十分に大きければ、換言すれば、駆動トランジスタ121のゲート端Gとソース端Sの間に付加される容量値(ここでは保持容量120の容量値Cs)を小さくするか、もしくは、駆動トランジスタ121のソース端S(つまり有機EL素子127のアノード端A)と接地配線Vcath(つまり有機EL素子127のカソード端K)の間に付加される容量値(ここでは有機EL素子127の寄生容量Cel)を大きくすると、限りなく“1”に近いことになり、より信号振幅Vinの大きさに近い電圧情報を保持容量120に書き込むことができる。

ブートストラップゲインGbst0と書込みゲインGinput0との関係を考える。たとえば、ブートストラップゲインGbst0を大きく取ることを考え、保持容量120の容量値Csをレイアウト上大きく取ると、有機EL素子127の寄生容量Celに対して保持容量120の容量値Csが大きくなり、書込みゲインGinput0が小さくなってしまう。書込みゲインGinput0が小さくなると、保持容量120に大きな情報を書き込むには信号振幅Vinのダイナミックレンジを大きく取らなければならなく、消費電力増大に繋がる。

逆に、書込みゲインGinput0を大きく取るために保持容量120の容量値Csを小さくすると、寄生容量C121gdの容量値Cgdや寄生容量C125gsの容量値Cwsに対して保持容量120の容量値Csが小さくなり、ブートストラップゲインGbst0が小さくなってしまい、有機EL素子127の特性変動に対する補正効果が低下し、特性劣化時の輝度落ちが顕著になる。

このように、第2比較例の画素回路Pとそれを駆動する駆動タイミングでは、書込みゲインGinputとブートストラップゲインGbst0とはトレードオフの関係にあり、何れか一方を大きくしようとすると他方が小さくなってしまい、他方に対して悪影響を与えることなく(他方を小さくせずに)、一方を大きくするということができない。

片方のゲインを重視すれば、その分だけもう片方のゲインが疎かにならざるを得ないことはもちろんのこととして、どちらも高いゲインを得ることは不可能である。このため、実際の所は、競合関係となる書込みゲインGinput とブートストラップゲインGbst の間で折り合いを付け、各ゲインが適度なものとなるように、保持容量120の容量値Csと有機EL素子127の寄生容量Celの容量値Celを決定する。

本実施形態では、図2や図2Aに示したように、補助容量310を備えており、書込みゲインGinputを調整できるようになっている。画素回路Pとしては、電気回路上、等価的には、補助容量310が有機EL素子127の寄生容量Celと並列に接続されたものとして動作する。これにより、映像信号線106HSが信号電位(基準電位Vo+信号振幅Vin)にある時間帯にサンプリングトランジスタ125を導通状態にするタイミングで書込駆動パルスWSを書込走査線104WSに出力することで保持容量120に信号振幅Vinの情報を書き込むと同時に駆動トランジスタ121の移動度μに対する補正情報を保持容量120に保持される情報に加える移動度補正を行なう際に、補助容量310を追加したことで、保持容量120に信号振幅Vinの情報を保持するときの書込みゲインGinput を高めることができるようになる。

具体的に説明すると以下の通りである。本実施形態を適用しない比較例2の画素回路Pの場合は、信号振幅Vinに対する、実際に保持される電圧割合(書込みゲインGinput0)は前述の式(4)で表されるのに対して、補助容量310を追加する本実施形態を適用することで、書込みゲインGinput1は、保持容量120の容量値Cs、補助容量310の容量値Csub 、駆動トランジスタ121のゲート端Gに形成される寄生容量C121gsの容量値Cgs、および有機EL素子127の寄生容量Celを用いて、式(5)のように表すことができる。

前述のように寄生容量C121gsの容量値Cgsは相対的に他の容量値に比べて小さいと考えてよい。書込みゲインGinput1は、補助容量310の追加により、等価回路的には、有機EL素子127のアノード端Aとカソード端Kの間に付加される容量値を、有機EL素子127の寄生容量Celと補助容量310の容量値Csub の合成分(Cel+Csub )にすることができる。

その結果、書込みゲインGinput1は書込みゲインGinput0よりも大きくなるので、 第2比較例の画素回路Pよりも、信号振幅Vinの大きさにより近い電圧情報を保持容量120に書き込むことができる。これにより、第2比較例の画素回路Pよりも低い信号振幅で所望の輝度を出すことができ、信号振幅の低減が実現され、低消費電力化に寄与する。

式(5)から明らかなように、補助容量310の容量値Csub が大きいほど書込みゲインGinput1は1に近くなる。換言すれば、容量値Csub を調整することで書込みゲインGinput1を調節できる。このことを利用すると、RGB3画素間で容量値Csub を相対的に調整することで、ホワイトバランスを取ることもできる。すなわち、R,G,Bの各色用の有機EL素子127の発光効率が異なるので、補助容量310がない場合には、同一の駆動電流Ids(つまり同一の信号振幅Vin)のときにはホワイトバランスが取れないので、色別に信号振幅Vinを異ならせることでホワイトバランスを取ることになる。これに対して、補助容量310の容量値Csub をRGB3画素間で相対的に調整することで、同一の駆動電流Ids(つまり同一の信号振幅Vin)のときにでもホワイトバランスが取れるようになる。

加えて、補助容量310を追加することで、閾値補正動作に影響を与えることなく、移動度μの補正に要する時間(移動度補正時間)を調整することができるようにもなる。補助容量310を利用して移動度補正時間を調整可能にすることで、画素回路Pの駆動が高速化しても、十分に移動度の補正を行なうことができるようになる。

すなわち、駆動トランジスタ121のドレイン電流をIds、移動度補正により補正される電圧分をΔVとした場合、移動度補正時間tは(Cel+Csub )×ΔV/Idsで表される。よって、補助容量310の設定により、保持容量120に保持されるホールド電位Vgsばかりでなく移動度補正時間を調整することができるのである。一般に、画素アレイ部102が高精細対応になるほど、画素回路Pと有機EL素子127(発光素子)の接続部の開口率は小さくなり、有機EL素子127の寄生容量Celが小さくなる。すると、補助容量310を配置しない場合にホールド電位Vgsは映像信号Vsig の信号振幅Vinから大きく損失した値となってしまう。このためにも、補助容量310を追加することの効果が大きい。

ところで、補助容量310を備えるか否かに関わらず、閾値補正機能や、移動度補正機能や、ブートストラップ機能を働かせるためには、各種のトランジスタ(本実施形態の画素回路Pではサンプリングトランジスタ125)をオン/オフ制御する必要があり、そのために各種の走査線(本実施形態では書込走査線104WS、電源供給線105DSL 、映像信号線106HS)を画素アレイ部102に縦方向や横方向に形成する必要がある。

各走査線と画素回路Pを構成するトランジスタ(駆動トランジスタ121、サンプリングトランジスタ125)のレイアウトによっては、走査線とトランジスタとが近接して配置されることがある。このとき、走査線とトランジスタの端子配線と間に形成される静電容量を介して、その走査線の電位に対応した不要な信号(ノイズ)がトランジスタのたとえば制御入力端(ゲート)や入出力端(ソースあるいはドレイン)に飛び込む現象が生じ得る。

たとえば、映像信号線106HSの映像信号Vsig の情報がサンプリングトランジスタ125を介さずに寄生容量を介して駆動トランジスタ121の制御入力端側の配線(つまりゲート配線)に飛び込むような事象が生じると、駆動電流Idsに影響を与え、表示画面上にノイズ(縦方向の輝度ムラやカラー表示の場合は色ムラ:縦クロストークと称する)となって現われてしまうということが分った。以下、この問題点とその対策手法について説明する。

<<走査線と画素内配線について>>

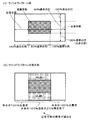

図6〜図8Bは、画素アレイ部102の走査線(垂直配線と水平配線)や画素内の端子配線の配線形態(レイアウト)を説明する図である。ここで、図6は、有機EL素子127や補助容量310などの配置を説明する図である。詳しくは、図6は、一般的な有機EL表示装置における1画素分の層構造の概略を示した図である。ここで、図6(1)は1画素分の平面図であり、図6(2)は図6(1)におけるA−A’線の断面図である。

図7および図7Aは、走査線を含む画素回路Pの従来のレイアウト例を示し、図7Bは、その従来のレイアウト例での画素回路Pの等価回路図である。ここで、図7は、従来のレイアウト例の基本概念を示し、図7Aは図7(2)に対応した詳細例である。

図8〜図8Cは、図7の構成において、黒レベルのウィンドウを表示した場合の各エリアにおける映像信号サンプリング時の駆動トランジスタ121のゲート電位とソース電位について説明する図である。詳細には、図8は、黒ウィンドウパターンBWの一例であり、図8Aは、黒ウィンドウパターン表示時のカップリング現象を画素回路Pの等価回路図上で示したものである。図8Bは、黒ウィンドウパターン表示時に生じ得る輝度ムラ(特に縦クロストーク)の問題点を説明するタイミングチャートである。

図6(1)に示す1画素分の平面図のように、基板101上に下部電極(たとえばアノード電極)504が配置され、その下部電極504上に有機EL素子127の開口部(以下EL開口部と称する)127aが形成されている。下部電極504には接続孔(たとえばTFT−アノードコンタクト)504aが設けられ、この接続孔504aを介して下部電極504下に配された駆動トランジスタ121の入出力端(本例ではソース電極)に下部電極504が接続されるようになっている。

下部電極504の周囲は絶縁膜パターン505で覆われて、有機EL素子127を構成する下部電極504、有機層506、上部電極508が積層されている部分のみが発光有効領域127bとなるように広く露出したEL開口部127aとされている。

図6(2)には、図6(1)におけるA−A’線の断面図が示されている。図6(2)に示すように、基板101上の各画素回路Pに対応する位置に、画素回路を構成する駆動トランジスタ121やサンプリングトランジスタ125などの薄膜トランジスタQや保持容量120(容量値Cs)や補助容量310(容量値Csub )が配置され、その上部に層間絶縁膜502a,502b(酸化膜)が設けられている。

層間絶縁膜502のさらに上部には、薄膜トランジスタQに接続されたソース電極線Qsおよびドレイン電極線Qdが設けられている。また、各素子(薄膜トランジスタQ,保持容量120)を構成する導電層、およびソース電極線Qsおよびドレイン電極線Qd(図では駆動トランジスタ121のソース電極121sのみを示す)を構成する導電層により、画素回路Pを構成する他の配線(図示省略)が形成されている。

そして、ソース電極線Qsおよびドレイン電極線Qdの層を覆う状態で、さらに上層の平坦化膜として機能する層間絶縁膜503が設けられ、この層間絶縁膜503上に有機EL素子127が形成されている。有機EL素子127は、下層側から順に積層された下部電極504、有機層506、および上部電極(たとえばカソード電極)508で構成されており、下部電極504と上部電極508と間に誘電体である有機層506が挟まれた構造であるので、有機EL素子127は容量成分(寄生容量Cel)を持つことになる。

下部電極504は、画素電極としてパターン形成されており、層間絶縁膜502に形成された接続孔504aを介して駆動トランジスタ121のソース電極121sに接続されている。また、下部電極504と対向する上部電極508は全ての画素回路Pを覆うベタ膜として形成されている。

このような層構造を持つ有機EL表示装置1においては、有機EL素子127が配列形成された基板101と反対側から発光光L1を取り出すいわゆるトップエミッション方式として構成することが、有機EL素子101の開口率を確保する上で有効になる。また、このようなトップエミッション方式であれば、有機EL素子127の開口率が、画素回路Pを構成する薄膜トランジスタQのレイアウトには依存しない。このため、さらに複数の薄膜トランジスタQや保持容量120を用いた画素回路Pを各画素に対応させて配置することもできる。

下部電極504は、画素回路Pの配列に対応してマトリクス状に配置される。そして、この下部電極504の隣接画素間には、下部電極504と同一層で構成された補助配線505(補助電極)が配線された構成となっている。補助配線505は、図示を割愛したコンタクトを介して上部電極508のカソード配線と電気的な接続がとられる。

図示を割愛した基板101上の最初に設けられる第1配線層L1は、薄膜トランジスタQ(駆動トランジスタ121やサンプリングトランジスタ125)などの回路素子を形成するレイヤとしても使用される。たとえば、保持容量120(容量値Cs)は、一方の電極が第1配線層L1に形成され、それに対向する電極がポリシリコンで層間絶縁膜502a,502b間に形成されている。補助容量310(容量値Csub )は、一方の電極が第1配線層L1および第2配線層L2に形成され、それらに対向する電極がポリシリコンで層間絶縁膜502a,502b間に形成されている。

第1配線層L1の電極とポリシリコンで第1の補助容量310aが形成され、第2配線層L2の電極とポリシリコンで第2の補助容量310bが形成され、第1配線層L1の電極と第2配線層L1の電極とがコンタクトにより接続されることで、第1の補助容量310aと第2の補助容量310bが並列接続された状態となっている。本実施形態の画素回路Pでは、補助容量310のノードND310を有機EL素子127のカソード配線に接続するようにしているので、第1配線層L1の電極と第2配線層L1の電極を、さらにコンタクトにより補助配線505に接続することで、最終的に上部電極508と接続されるようにしている。

この表示装置1は、基板101と反対側から発光光を取り出すトプエミッション型であるため、下部電極504は遮光性が高く、かつ反射率の高い材料で構成される。一方、上部電極508は、光透過性の高い材料を用いて構成される。したがって、上部電極508の配線抵抗が大きくなる。ベタ配線としても抵抗値の低減には限界がある。補助配線505は、この高抵抗の上部電極508と並列に配線することで、全体としての抵抗値を低減するのに寄与する。

ところで、図2および図2Aに示した画素回路Pの場合、画素アレイ部102においては、少なくとも垂直走査系統に関わる書込走査線104WSおよび電源供給線105DSL が縦/横の一方の配線(たとえば横配線とする)となり、これに対して水平走査系統に関わる映像信号線106HSが縦/横の他方の配線(たとえば縦配線とする)となる。また、有機EL素子127のカソード電位Vcathをベタ配線ではなく通常の配線とする場合であれば、カソード電位Vcath用の配線(以下カソード配線Wcathと称する)が横配線もしくは縦配線となる。

ここで、前述の各配線(書込走査線104WS、電源供給線105DSL 、映像信号線106HS)は、横方向または縦方向に延び、画素アレイ部102の周辺に設けられた対応する走査部(書込走査部104、駆動走査部105、水平駆動部106)と接続される。

画面の左右方向について考察した場合、詳細説明図は割愛するが、1行内の全ての画素回路Pに対して書込駆動パルスWSは書込走査部104から共通に供給されるので、書込駆動パルスWSの波形が配線容量や配線抵抗の影響で、書込走査部104から遠い画素回路P(遠側画素と称する)の方が書込走査部104から近い画素回路P(近側画素と称する)よりも、その波形鈍りが大きくなってしまう。そのため、配線容量や配線抵抗の分布特性が、閾値補正や移動度補正の動作に影響を与えることがある。

同様のことは、電源供給線105DSL や映像信号線106HS(あるいはカソード配線Wcath)についても言えることであり、配線容量や配線抵抗の分布特性が、閾値補正や移動度補正の動作に影響を与えることがある。

これらの点を考慮して、各配線は、一般的に、低抵抗にするべく、アルミニウムAlやモリブデンMoなどによる光透過性を有しない金属配線を使用して配線される。前述のように、縦配線と横配線が必要であるから、基本的には、縦配線と横配線の交差部でのオーバーラップのために、最低でも2層(第1配線層L1,第2配線層L2)の金属配線が必要になる。

2層の金属配線を利用して各配線(書込走査線104WS、電源供給線105DSL 、映像信号線106HS、カソード配線Wcath)を配置する場合、何れを第1配線層L1に配置し何れを第2配線層L2に配置するかで、様々な配線(レイアウト)形態を採り得る。

たとえば、書込走査線104WSと電源供給線105DSL とを上層側および下層側の一方の金属配線にすることが考えられる。このとき、映像信号線106HSに関しては、第1の手法として図7(1)に示すように、画素回路P部分では上層側および下層側の一方の金属配線(図では第2配線層L2)にすると、同一層の書込走査線104WSや電源供給線105DSL と交差する部分はオーバーラップさせる必要があるので、上層側および下層側の他方の金属配線にしてブリッジさせる(異なる層の金属配線をコンタクトで繋ぐ)必要がある。

また、第2の手法として図7(2)に示すように、水平駆動部106Sの全体を上層側および下層側の他方(図では第1配線層L1)の金属配線にすることも考えられる。こうすることで、第1の手法のような他層の金属配線(第2配線層L2)とのブリッジを避けることができる。第1の手法との対比においては、縦配線である映像信号線106HSと横配線との下層側の金属配線とのブリッジの回数を少なくできるので、映像信号線106HSの負荷を軽減することができる利点がある。

第1および第2の手法の何れにおいても、書込走査線104WSと電源供給線105DSL は同一層の金属配線で同一方向にレイアウトされることになり、1画素内では離して(画素回路Pの上端と下端にて)並走させたとしても、隣接する画素回路Pとの関係においては同一層(同じレイヤ)でごく近くを並走(隣接)することになる。また、前述のように、書込走査線104WSおよび電源供給線105DSL は、画素アレイ部102周辺(パネル端)の対応する書込走査部104、駆動走査部105までレイアウトされるため、非常に長い。したがって、配線間スペースが狭いと、対向面積が大きくなり、配線間に形成される静電容量(寄生容量)が大きくなる。また、走査線同士に限らず、走査線と画素内配線と間でも、同様のことが懸念される。

たとえば、図7に示すように、走査線や画素内配線を形成する際に用いられるのは、半導体基板側の第1配線層と、第1配線層L1の上層側に絶縁体(層間絶縁膜502,503:画素回路Pの各構成要素を形成するためのものを含む)を挟んで配される第2配線層L2の2層である。ここで、第2配線層L2の配線はアルミAlなどの低抵抗材料が用いられるのに対して、第1配線層L1の配線は、低抵抗とは言っても、第2配線層L2の配線と比較して抵抗が高い材料(高抵抗材料)、たとえばモリブデンMoなどが使用される。

画素回路Pにおいては、映像信号線106HSは信号振幅Vinの情報を、サンプリングトランジスタ125を介して保持容量120に書き込む必要があり低インピーダンスであることが好ましく、また、電源供給線105DSL はそれそのものが駆動トランジスタ121に対して電源供給能力を持つ必要があり低インピーダンスであることが好ましく、何れも低抵抗化するため、第2配線層L2に設定する。

映像信号線106HSは列方向に延在する縦配線であるのに対して、電源供給線105DSL は、水平期間ごとに第1電位Vcc_Hと第2電位Vcc_Lとでスイッチングするため、行方向に延在する横配線とする。映像信号線106HSと電源供給線105DSL をともに第2配線層L2に設定するには、必然的に、映像信号線106HSと電源供給線105DSL は直交(交差)しなければならない。このような低抵抗線同士が交差する配線態様を実現するためには、第2配線層L2に関しても多層配線技術が必要となる。実際の所は、ブリッジ部分を第1配線層L1を利用して形成することになる。

一方、画素内配線に関しては、配線長が短く配線抵抗の分布特性が問題となることは殆どないので、基本的には、第1配線層L1および第2配線層L2の何れをも採用することができる。そのため、従来のレイアウト例では、図7(1)や図7(2)あるいは図7Aに示すように、トランジスタの端子に接続される配線と同一層に形成している。

このため、画素回路P内において、映像信号線106HSと駆動トランジスタ121のゲート配線312と間で線間容量314(容量値Cp_0)が寄生容量として形成されてしまう。これは、レイアウト効率を考慮してゲート配線312を映像信号線106HSと同一層で形成する場合に並走してしまい、並走部の平行平板容量によって線間容量314が形成されるのである。

したがって、映像信号線106HSの映像信号Vsig の情報がサンプリングトランジスタ125を介さずに線間容量314を介して駆動トランジスタ121のゲート配線312に直接に飛び込むような事象が生じる。この事象が生じると、駆動電流Idsに影響を与え、表示画面上にノイズとなって現われてしまう。

図8〜図8Bは、この現象の典型例を説明するもので、黒ウィンドウパターン表示時の状態を示す。ここでは、黒ウィンドウパターンBWを表示したときに、画面とラインごとの動作を説明している。具体的には、画面の上部と下部に全白が表示される行を配し、画面中央部の黒が表示される行では、1水平期間における中央部の黒の表示期間とその左右に配される白の表示期間とが1:1となる50%表示をしたときの場合を示している。同様に、画面中央部の黒が表示される列では、1垂直期間における中央部の黒の表示期間とその左右上下に配される白の表示期間とが1:1となる50%表示をしたときの場合を示している。なお、ここでは、上下左右の白表示と黒表示が1:1となる50%表示の例で示しているが、黒ウィンドウパターン表示は、この例に限らず、上下あるいは左右の白表示と黒表示が1:1以外の場合であってもよい。

このような黒ウィンドウパターンの映像信号Vsig が映像信号線106HS上に供給されたときに、線間容量314を介してゲート配線312に飛び込むと(図8AのS1)、駆動トランジスタ121のゲート電圧Vgが映像信号Vsig に応じて変化し、白表示部分も輝度が変化し、輝度ムラの一例である縦クロストークが起こってしまう。

詳しくは、図8(2)に示すように、画面の上部と下部に全白が表示される行と画面中央部の黒が表示される行とが存在すると、発光時の駆動トランジスタ121のゲート電圧Vgの波形を見ると、図8Bに示すように、白表示しているA部分では正常であるが(図8B(2))、黒ウィンドウ表示したB点ではウィンドウ部分に位置する映像信号線106HSからゲート配線312への線間容量314を介したフリンジ(容量カップリング)によって電圧降下している(図8B(3))。

そのため、画面の左部と右部に全白が表示される列(以下100%表示の列と称する)と、画面中央部の白と黒が表示される列(以下50%表示の列と称する)との比較では、正常な白表示部分である100%表示の列と比べ、50%表示の列の白表示部分が暗くなる。つまり、同じ大きさの信号振幅Vinに基づく白表示部であっても、100%表示の列の白よりも50%表示の列の白の方が輝度が低下してしまい、表示画像上では、縦クロストークとして視認される。

このように、映像信号線106HSと駆動トランジスタ121のゲート配線312を同一層で形成すると、映像信号線106HSとゲート配線312が並走することで形成される線間容量314を介して映像信号線106HS上の映像信号Vsig がゲート配線312に飛び込むことに起因する列方向のシェーディング(典型例としてはウィンドウパターンによって生じる縦クロストーク)などの輝度ムラが生じてしまうことが問題となる。

<改善手法:基本概念>

図9は、映像信号線106HSとゲート配線312が並走することで形成される線間容量314に基づく縦クロストークを改善する手法の基本概念を説明する図である。ここで、図9(1)は、図7に示した従来のレイアウトにおいて、映像信号線106HSとゲート配線312が並走している部分の構造を説明するものである。図9(2)は、本実施形態で採用する改善手法を説明する図である。

図9(1)に示すように、ガラス基板上に層間絶縁膜(酸化膜)が形成され、その上層に第2配線層L2が設けられる。第2配線層L2の空き部分は平坦化膜として機能する層間絶縁膜503で覆われる。ここで、前述のように、映像信号線106HSとゲート配線312は同一層に形成される。このため、図9(1)に示すように、並走部の平行平板構造によって線間容量314(容量値Cp_0)が形成される。なお、図9(1)は図7(1)に対応して第2配線層L2で線間容量314が形成される状態であるが、図7(2)や図7Aに対応した場合でも同様であり、第1配線層L1で線間容量314が形成されることになる。

前述の説明から理解されるように、映像信号線106HS上の映像信号Vsig に対応したノイズ(以下映像信号飛込みノイズとも称する)が、映像信号線106HSとゲート配線312と間の線間容量314を介して駆動トランジスタ121のゲート配線312に飛び込むことのそもそもの原因は、映像信号線106HSとゲート配線312とが近接して並走することで比較的大きな容量値の線間容量314が形成され、この線間容量314を介して映像信号飛込みノイズが駆動トランジスタ121のゲート配線312に伝達されることにある。したがって、この観点から対策を採ることで、前述の映像信号飛込みノイズに基づく縦クロストークを改善できると考えられる。具体的には、線間容量314の容量値を小さくすればよい。

平行平板電極間によって形成される線間容量314の容量値Cp_0は、導体間に形成される静電容量の定義式に基づき特定できる。すなわち、コンデンサは、対応した電極を持ち、電極間に誘電体が介在することで形成される。その静電容量Cは、コンデンサの導板(複数)の内の1枚の電荷Qをそれらの導板の間の電位差Vで除した値で、その他の導体の影響は無視してよい。具体的には、各導体(電極)の対向間隔t、対向面積A、電極間の物質の比誘電率εとしたとき、C=Q/V=εA/tで規定される。図9に示した例では、導体間の物質は平坦化膜となる。

したがって、静電容量C(つまり線間容量302の容量値Cp_0)を低減するには、比誘電率εの小さな物質を極板間に介在させるか(ε_0>ε_1:第1の手法と称する)、または、段差を設けて極板の対向面積Aを減少させるか(A_0>A_1:第2の手法と称する)、または、極板間の距離tを大きくすればよい(t_0<t_1:第3の手法と称する)ことが分る。もちろん、図9(2)に示すように、これらの3つの手法を任意に組み合わせてもよい(第4の手法と称する)。

上記を踏まえれば、映像信号線106HSと駆動トランジスタ121のゲート配線312と間に形成される寄生容量を十分に小さくなるようにレイアウトする手法としては前記の第1〜第4の手法の何れを採用してもよいのであるが、後述する本実施形態では、特に第4の手法を採用する場合について詳しく説明する。

第4の手法を採用する場合について詳しく説明することにしたのは、以下の理由による。第1の手法において、比誘電率εを変えるには材料を変更する必要があり、これにともない、膜厚、均質性などさまざまなことを考慮しなければならず、簡単にはできない。第2の手法において、たとえば現状のように両配線をアルミニウムAlで配線する場合、この手法では事実上、プロセス数が増加・複雑化する。第3の手法では、現状工程数を変えることなく実現可能であるが、特に横方向は狭く、十分に離すことが難しい。これに対して、第4の手法は、現状工程数を変えることなく実現可能である。また、レイヤが異なるため容量を格段に小さくできる利点もある。

よって、詳細例として説明する本実施形態の改善手法の基本的な考え方は、映像信号線106HSと駆動トランジスタ121のゲート配線312を異なる配線層(別レイヤ)に形成(レイアウト)する点にある。映像信号線106HSと駆動トランジスタ121のゲート配線312を別レイヤに形成するものである限り、基本的には、映像信号線106HSと駆動トランジスタ121のゲート配線312の横方向の位置は不問である。ただし、平面上において横方向の位置に重なりを持ち、縦方向(厚さ方向)で平行平板構造を呈するようになり、容量値が大きくなる。

この点においては、極板の対向間隔tや極板間に介在させる物質の比誘電率εが従前と同じであるものとして、線間容量314の容量値Cp_1を、一般的な対向面積A_0における従前の容量値Cp_0よりも小さくできる方向であって、現実的なレベルで、対向面積A_1の方が従前の対向面積A_0よりも十分に小さいと言える程度にすればよい。

また、別の観点からの規定の手法としては、白表示部分とウィンドウ表示部分の輝度差の側面から規定することが考えられる。すなわち、一般的に、人間の目で輝度差約1%以内であれば視認されないと言われている。したがって、映像信号線106HSと駆動トランジスタ121のゲート配線312と間に形成される線間容量314の容量値Cp_1(換言すれば両配線間隔t_1)が、線間容量314を起因とする映像信号飛込みノイズによる白表示部分とウィンドウ表示部分の白表示エリア同士の輝度差が1.0%以下となるようなものとする。こうすることで、線間容量314の容量値Cp_1にある程度の大きさを持っていても、実質的には、縦クロストークが視認されないレベルとなる。

なお、白表示エリア同士の輝度差が1.0%以下となる線間容量314の容量値Cp_1は、画素定数、EL特性、映像信号Vsig の基準電位Voと信号振幅Vinとの差(映像振幅)によって変化する。

つまり、一般的には、レイアウト効率を考慮した場合に、パターンルールの限界を考慮した最小パターン間隔で各走査線や画素内配線を配置するので、映像信号線106HSと駆動トランジスタ121のゲート配線312を別レイヤに形成するときには完全に重ねて配線することが可能となってしまう。たとえば、映像信号線106HSを第2配線層L2(アルミニウムAl)、ゲート配線312を第1配線層L1(モリブデンMo)で構成することや、逆にゲート配線312を第2配線層L2(アルミニウムAl)、映像信号線106HSを第1配線層L1(モリブデンMo)で構成することができる。モリブデンMo上にアルミニウムAl層を作ることができるのである。

このことにより、層間絶縁膜502を挟んで平行平板容量が形成されてしまうと、別レイヤにして線間容量314の容量値Cp_1を小さくしようとした効果が低減してしまう。このような事態を避けるには、映像信号線106HSと駆動トランジスタ121のゲート配線312を別レイヤに形成すると言うだけでなく、平面上において横方向の別の位置に設ける、つまりオーバーラップさせないことが望ましい。横方向の対向間隔t_1を従前の対向間隔t_0を維持するようにして別レイヤに配置するようにすれば確実である。

こうすることで、極板の対向間隔tや極板間に介在させる物質の比誘電率εが従前と同じであっても、映像信号線106HSと駆動トランジスタ121のゲート配線312と間に形成される線間容量314の容量値Cp_1を従前の容量値Cp_0よりも格段に小さくできる。その結果、線間容量314を介した映像信号飛込みノイズのゲート配線312への飛込みの影響を抑えることができる。以下、第4の手法を採用した本実施形態の対策手法について具体的に説明する。

<改善手法:第1実施形態>

図10および図10Aは、映像信号飛込みノイズに基づく縦クロストークを改善し得るようにした回路配置(レイアウト)の第1実施形態を説明する図である。ここで、図10は、画素回路Pの第1実施形態のレイアウト例の基本概念を示し、図10Aは図10に対応した詳細例(配線の上下関係は無視する)である。

第1実施形態の改善手法のポイントは、映像信号線106HSと駆動トランジスタ121のゲート配線312を別レイヤにレイアウトする点にある。加えて、好ましくは、オーバーラップさせないようにする。後述する第2実施形態との相違点として、映像信号線106HSを第2配線層L2に配置し、駆動トランジスタ121のゲート配線312を第1配線層L1に配置するようにした点に特徴を有する。

たとえば、白表示の信号電圧:5V、黒表示の信号電圧:0Vとし、図7(2)に示す第2の手法のように、映像信号線106HSおよび駆動トランジスタ121のゲート配線312のそれぞれをモリブデンMoで同一層に配線した場合の線間容量314の容量値Cp_0は1.5fF(フェムトファラッド)であるとする。この場合、黒ウィンドウ表示における白表示部分(100%表示の列)とウィンドウ表示部分(50%表示の列)の発光時の駆動トランジスタ121のゲート・ソース間電圧Vgsの差は約0.015Vとなり、白表示エリア同士の輝度差が約2〜3%となった。

表示画面上における各種のノイズに関しては、一般的に、人間の目で輝度差約1%以内であれば視認されないと言われている。したがって、このままでは、映像信号線106HSとゲート配線312と間に形成される線間容量314を起因とする映像信号飛込みノイズによる縦クロストークが視認されてしまうので問題である。

これに対して、前例と同一の画素定数で、白表示の信号電圧:5V、黒表示の信号電圧:0Vとし、図10や図10Aに示す第1実施形態のレイアウト手法のように、映像信号線106HSを第2配線層L2にアルミニウムAlで配置し、駆動トランジスタ121のゲート配線312を第1配線層L1にモリブデンMoで配置することで、それぞれを別レイヤに配線した場合の線間容量314の容量値Cp_1は1.0fFとなった。

これにより、黒ウィンドウ表示における白表示部分(100%表示の列)とウィンドウ表示部分(50%表示の列)の発光時の駆動トランジスタ121のゲート・ソース間電圧Vgsの差は約0.01Vとなり、白表示エリア同士の輝度差が約1%となった。その結果、映像信号線106HSとゲート配線312と間に形成される線間容量314を起因とする映像信号飛込みノイズによる縦クロストークが視認されないレベルとなった。

よって、前例の画素定数の場合には、駆動トランジスタ121のゲート配線312と映像信号線106HSの並走部分に形成されるゲート配線312の容量値Cpを1fF以下にすることが望ましい。

なお、白表示エリア同士の輝度差が1.0%以下となる線間容量314の容量値Cp_1は、画素定数、EL特性、映像信号Vsig の基準電位Voと信号振幅Vinとの差(映像振幅)によって変化するので、別の条件となるときには、それに合わせて、線間容量314の容量値Cp_1が輝度差1%以下を実現するようなレイアウトにする必要が生じる。

このように線間容量314の低容量化を実現する方法としては、この第1実施形態のレイアウト手法のように、ゲート配線312と映像信号線106HSの並走部分を別レイヤで配線することで実現できる。

このとき、映像信号線106HSを第2配線層L2にアルミニウムAlで、駆動トランジスタ121のゲート配線312を第1配線層L1にモリブデンMoで配置すると、モリブデンMo上にアルミニウムAl層を作ることができるが、そのことのよって縦方向(厚さ方向)に平行平板構造が形成され大きな容量を形成するようになるため、映像信号線106HSとゲート配線312はオーバーラップさせないようにすることが望ましい。

このように、画素回路Pを駆動する際、従来レイアウトでは映像信号線106HSの電位変動が駆動トランジスタ121のゲート配線312に影響を与え、縦クロストークとして視認されるという問題があったが、第1実施形態のレイアウトを採り、映像信号線106HSとゲート配線312の並走部分を別レイヤで配線し、線間容量314をたとえば1fF以下のように十分に小さくすることができる。これにより、駆動トランジスタ121のゲート配線312と映像信号線106HSの並走部分にできる寄生容量(線間容量314)をそもそもの原因とするフリンジングによる縦クロストークを、認識不可能な程度に減少させる(抑制する)ことができる。

<改善手法:第2実施形態>

図11および図11Aは、映像信号飛込みノイズに基づく縦クロストークを改善し得るようにした回路配置(レイアウト)の第2実施形態を説明する図である。ここで、図11は、画素回路Pの第2実施形態のレイアウト例の基本概念を示し、図11Aは図11に対応した詳細例(配線の上下関係は無視する)である。

第2実施形態の改善手法のポイントは、第1実施形態と同様に、映像信号線106HSと駆動トランジスタ121のゲート配線312を別レイヤにレイアウトする点にある。加えて、好ましくは、オーバーラップさせないようにする。前述の第1実施形態との相違点として、映像信号線106HSを第1配線層L1に配置し、駆動トランジスタ121のゲート配線312を第2配線層L2に配置するようにした点に特徴を有する。

この第2実施形態のように、映像信号線106HSと駆動トランジスタ121のゲート配線312を配するレイヤ(層)を第1実施形態に対して逆にする場合でも、第1実施形態と同様に、それぞれを別レイヤに配線しており、前例と同一の画素定数のときの線間容量314の容量値Cp_1は1.0fFとなった。白表示の信号電圧:5V、黒表示の信号電圧:0Vとしたときの黒ウィンドウ表示における白表示部分(100%表示の列)とウィンドウ表示部分(50%表示の列)の発光時の駆動トランジスタ121のゲート・ソース間電圧Vgsの差は約0.01Vとなり、白表示エリア同士の輝度差が約1%となった。その結果、映像信号線106HSとゲート配線312と間に形成される線間容量314を起因とする映像信号飛込みノイズによる縦クロストークが視認されないレベルとなる。

映像信号線106HSと駆動トランジスタ121のゲート配線312を第1配線層L1と第2配線層L2の何れに配置するかを問わず、それらを別レイヤに配置し、好ましくはオーバーラップさせない(好ましくは横方向の配線間隔を従前と同じに維持する)ことで、両配線間に生じる寄生容量(線間容量314)を無視できる程度に十分に小さくでき、線間容量314を介したフリンジングによる縦クロストークを解消できるようになる。

以上、本発明について実施形態を用いて説明したが、本発明の技術的範囲は前記実施形態に記載の範囲には限定されない。発明の要旨を逸脱しない範囲で前記実施形態に多様な変更または改良を加えることができ、そのような変更または改良を加えた形態も本発明の技術的範囲に含まれる。

また、前記の実施形態は、クレーム(請求項)にかかる発明を限定するものではなく、また実施形態の中で説明されている特徴の組合せの全てが発明の解決手段に必須であるとは限らない。前述した実施形態には種々の段階の発明が含まれており、開示される複数の構成要件における適宜の組合せにより種々の発明を抽出できる。実施形態に示される全構成要件から幾つかの構成要件が削除されても、効果が得られる限りにおいて、この幾つかの構成要件が削除された構成が発明として抽出され得る。

<駆動タイミングの変形例>

たとえば、画素回路Pが同じであっても、駆動タイミングの側面から様々な変形が可能である。たとえば、電源供給線105DSL の電位が第2電位Vcc_Lから第1電位Vcc_Hに遷移するタイミングを映像信号Vsig の非有効期間である基準電位Vo(Vofs )の期間としつつ、様々な変形が可能である。

たとえば、一変形例として、図示を割愛するが、図4に示した駆動タイミングに対して、書込み&移動度補正期間Hの設定方法を変形することができる。具体的には、先ず映像信号Vsig が基準電位Vo(Vofs )から信号振幅Vinに遷移するタイミングt15Vを図4に示した駆動タイミングよりも1水平期間の後半側にシフトさせて、有効期間である信号振幅Vinの期間を狭くする。

また、閾値補正動作の完了時(閾値補正期間Eの完了時)には、先ず、書込駆動パルスWSをアクティブHにしたままで、水平駆動部106により映像信号線106HSに映像信号Vsig の信号振幅Vinを供給して(t16)、書込駆動パルスWSをインアクティブLにするまで(t17)の間を、保持容量120への画素信号Vsig の書き込み期間とする。この信号振幅Vinは駆動トランジスタ121の閾値電圧Vthに足し込む形で保持される。この結果、駆動トランジスタ121の閾値電圧Vthの変動は常にキャンセルされる形となるので、閾値補正を行なっていることになる。この閾値補正動作によって、保持容量120に保持されるゲート・ソース間電圧Vgsは“Vsig +Vth”となる。また、同時に、信号書込期間t16〜t17で移動度補正を実行する。すなわち、タイミングt16〜t17は、信号書込期間と移動度補正期間の双方を兼ねることとなる。

なお、この移動度補正を実行する期間t16〜t17では、有機EL素子127は実際には逆バイアス状態にあるので発光することはない。この移動度補正期間t16〜t17では、駆動トランジスタ121のゲート端Gが映像信号Vsig のレベルに固定された状態で、駆動トランジスタ121に駆動電流Idsが流れる。以下、図4に示した駆動タイミングと同様である。

この変形例の駆動タイミングでも、駆動トランジスタ121のドレイン端Dに対する電源供給のスイッチング動作は図4に示した駆動タイミングと完全に同じであり、輝度ムラ(特に縦クロストーク)に対する抑制効果は前述の本実施形態と同様に享受できる。

各駆動部(104,105,106)は、水平駆動部106が映像信号線106HSに供給する映像信号Vsig と書込走査部104が供給する書込駆動パルスWSとの相対的な位相差を調整して、移動度補正期間を最適化することができる。補助容量310の容量値Csub を調整することでその移動度補正期間を調整できる。

ただし、書込み&移動度補正準備期間Gが存在せずに、タイミングt16V〜t17Wが書込み&移動度補正期間Hとなる。このため、書込走査線104WSや映像信号線106HSの配線抵抗や配線容量の距離依存の影響に起因する波形特性の相違が書込み&移動度補正期間Hに影響を与えてしまう可能性がある。画面の書込走査部104に近い側と遠い側(すなわち画面の左右)でサンプリング電位や移動度補正時間が異なることになるので、画面の左右で輝度差が生じ、シェーディングとして視認される難点が懸念される。

<画素回路の変形例>

また、画素回路Pの側面からの変更も可能である。たとえば、回路理論上は「双対の理」が成立するので、画素回路Pに対しては、この観点からの変形を加えることができる。この場合、図示を割愛するが、先ず、図2および図2Aに示した画素回路Pがnチャネル型のトランジスタを用いて構成しているのに対し、pチャネル型のトランジスタを用いて画素回路Pを構成する。これに合わせて映像信号Vsig の基準電位Vo(Vofs )に対する信号振幅Vinの極性や電源電圧の大小関係を逆転させるなど、双対の理に従った変更を加える。

たとえば「双対の理」に従った変形態様の画素回路Pでは、pチャネル型の駆動トランジスタ(以下p型駆動トランジスタ121pと称する)のゲート端Gとソース端Sと間に保持容量120を接続し、p型駆動トランジスタ121pのソース端Sを直接に有機EL素子127のカソード端Kに接続する。有機EL素子127のアノード端Aは基準電位としてのアノード電位Vanode にする。このアノード電位Vanode は、基準電位を供給する全画素共通の基準電源(高電位側)に接続する。

p型駆動トランジスタ121pは、そのドレイン端Dが低電圧側の電源電位Vcc_Lに接続され、有機EL素子127を発光させる駆動電流Idsを流す。映像信号線106HSと書込走査線104WSとの交差部にはpチャネル型のサンプリングトランジスタ(以下p型サンプリングトランジスタ125pと称する)を配する。p型サンプリングトランジスタ125pは、ゲート端Gを書込走査部104からの書込走査線104WSに接続し、ドレイン端D(もしくはソース端S)を映像信号線106HSに接続し、ソース端S(もしくはドレイン端D)をp型駆動トランジスタ121pのゲート端Gと保持容量120の一方の端子との接続点に接続する。p型サンプリングトランジスタ125pのゲート端Gには書込走査部104からアクティブLの書込駆動パルスWSを供給する。

このような双対の理を適用してトランジスタをp型にした変形例の有機EL表示装置においても、前述のn型にした有機EL表示装置と同様に、閾値補正動作、移動度補正動作、およびブートストラップ動作を実行することができる。

もちろん、画素回路Pごとに補助容量310を追加することで、書込みゲインやブートストラップゲインを調整したり、あるいは移動度補正期間を調整したり、あるいはカラー表示の場合にはホワイトバランスをとることができる。

このような画素回路Pを駆動する際に、映像信号線106HSの電位変動が駆動トランジスタ121のゲート配線312に影響を与えることで生じ得る縦クロストークに関しては、前述の第1あるいは第2実施形態のレイアウト手法を適用して、映像信号線106HSと駆動トランジスタ121のゲート配線312を別レイヤに配置し、好ましくはオーバーラップさせないことで、両配線間に生じる線間容量314を無視できる程度に十分に小さくでき、線間容量314を介した映像信号飛込みノイズに基づく表示画面上のノイズ(縦クロストーク)を防止できる。

なお、ここで説明した画素回路Pの変形例は、図2および図2Aに示した構成に対して「双対の理」に従った変更を加えたものであるが、回路変更の手法はこれに限定されるものではない。閾値補正動作を実行するに当たり、書込走査部104での線順次走査に合わせて各水平周期内で基準電位Vo(Vofs )と信号電位(Vofs +Vin)で切り替わる映像信号Vsig が映像信号線106HSに伝達されるように駆動を行なうものである限り、2TR構成であるか否かは不問でありトランジスタ数が3個以上であってもよく、それらの全てに、前述の本実施形態の各改善手法を適用できる。こうすることで、線間容量314を介した輝度ムラ(縦クロストーク)を抑制するという本実施形態の思想を適用することができる。

1…表示装置、100…表示パネル部、101…基板、102…画素アレイ部、103…垂直駆動部、104…書込走査部、104WS…書込走査線、105…駆動走査部、105DSL …電源供給線 、106…水平駆動部、106HS…映像信号線、109…制御部、120…保持容量、121…駆動トランジスタ、125…サンプリングトランジスタ、127…有機EL素子、130…インタフェース部、133…垂直IF部、136…水平IF部、200…駆動信号生成部、220…映像信号処理部、310…補助容量、312…駆動トランジスタのゲート配線、314…線間容量(寄生容量)、Cel…寄生容量、P…画素回路、ND121,ND122,ND310…ノード