JP2008009817A - 半導体装置及びデータ転送方法 - Google Patents

半導体装置及びデータ転送方法 Download PDFInfo

- Publication number

- JP2008009817A JP2008009817A JP2006180952A JP2006180952A JP2008009817A JP 2008009817 A JP2008009817 A JP 2008009817A JP 2006180952 A JP2006180952 A JP 2006180952A JP 2006180952 A JP2006180952 A JP 2006180952A JP 2008009817 A JP2008009817 A JP 2008009817A

- Authority

- JP

- Japan

- Prior art keywords

- input

- transfer

- controller

- control unit

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/28—Handling requests for interconnection or transfer for access to input/output bus using burst mode transfer, e.g. direct memory access DMA, cycle steal

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Bus Control (AREA)

Abstract

【解決手段】転送中のデータを一時記憶するセクタバッファ104の入出力ポートP1をシステムバス108とのDMA転送に用い、入出力ポートP2をI/Oコントローラ107とのデータ転送に用い、切替部105はシステムバス108とI/Oコントローラ107を接続するか、セクタバッファ104とI/Oコントローラ107またはシステムバス108を接続するかを切り替え、セクタバッファコントローラ106は入出力ポートP1、P2によるデータ転送を別々に起動し、セクタバッファ104とI/Oコントローラ107間での転送単位分のデータの転送の終了を検出すると、セクタバッファ104とI/Oコントローラ107とのデータ転送を遮断しシステムバス108とI/Oコントローラ107とを接続するための制御信号を切替部105に送出する。

【選択図】図1

Description

メモリカードは、情報端末に搭載されるシステムLSI(Large Scale Integrated circuit)に組み込まれているカードコントローラにより制御される。

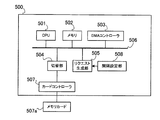

半導体装置500は、CPU501、メモリ502、DMAコントローラ503、切替部504、リクエスト生成部505を有し、これらはシステムバス506に接続されている。図12では、I/Oデバイスとして、メモリカード507aを用いた場合について示しており、半導体装置500は、カードコントローラ507を内蔵している。カードコントローラ507は、切替部504を介してシステムバス506に接続されている。CPU501及びDMAコントローラ503は、システムバス506のマスタであり、カードコントローラ507はスレーブである。

図13は、従来の半導体装置のデータ転送時の信号の様子を示すタイミングチャートである。

PIO転送中は、CPU501が発行するチップセレクト信号/CSaがカードコントローラ507のチップセレクト信号/CSbとして使用される。すなわち、切替部504は、CPU501からの制御信号をカードコントローラ507に伝える。これにより、CPU501の制御のもと、データ(図13のvalid)がメモリ502とカードコントローラ507との間でPIO転送される。

まず、CPU501から、切替部504を介して、カードコントローラ507に対して転送モードの設定や転送コマンドの発行を行う(ステップS50)。

本発明の他の目的は、効率のよい転送処理が可能なデータ転送方法を提供することである。

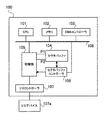

図1は、第1の実施の形態の半導体装置の構成を示す図である。

第1の実施の形態の半導体装置100は、CPU101、メモリ102、DMAコントローラ103、セクタバッファ104、切替部105、セクタバッファコントローラ106、I/Oコントローラ107を有している。また、CPU101、メモリ102、DMAコントローラ103、切替部105、セクタバッファコントローラ106は、システムバス108と接続されている。なお、以下では、システムバス108は、アドレスを伝送するアドレスバス、データを伝送するデータバス、制御信号を伝送する制御線を含むものとする。CPU101及びDMAコントローラ103は、システムバス108のマスタであり、I/Oコントローラ107はスレーブである。

メモリ102は、I/Oコントローラ107に接続されたI/Oデバイス107aにライトするデータや、I/Oデバイス107aからリードされたデータなどを記憶する。

セクタバッファ104は、転送中のデータを一時記憶する一時記憶部である。そして、システムバス108とのDMA転送に用いる入出力ポートP1と、I/Oコントローラ107とのデータ転送に用いる入出力ポートP2とを有している。図1では、この2つの入出力ポートP1、P2を切替部105に接続している。このようなセクタバッファ104は、デュアルポートRAM(Random Access Memory)を用いることで実現可能である。また、2つのシングルポートRAMを用いるようにしてもよい。

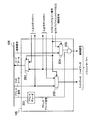

切替部105は、アドレスデコーダ201、セレクタ202、203、204、AND回路205を有している。

セレクタ202は、I/Oデバイス107aへのライトデータとして、システムバス108からのデータか、セクタバッファ104の入出力ポートP2からのデータを用いるかを、セクタバッファコントローラ106で生成される制御信号の1つであるセクタバッファビジー信号に応じて切り替える。

セクタバッファコントローラ106は、システムバス108側とのDMA転送用の起動レジスタ131、I/Oコントローラ107側とのデータ転送用の起動レジスタ132、DMA転送要求信号生成部133、制御信号生成部134、転送単位設定レジスタ135、ステータスレジスタ136、バッファ制御部137を有する。

ステータスレジスタ136は、転送単位分の転送が終了したか否かの状態を記憶する。

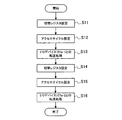

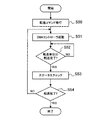

図4は、第1の実施の形態の半導体装置による転送処理を示すフローチャートである。

まずCPU101は、システムバス108から切替部105を介してI/Oコントローラ107に、転送コマンドを発行する(ステップS1)。このときセクタバッファコントローラ106は、図2の切替部105のセレクタ202、203、204に対して、システムバス108と、I/Oコントローラ107を接続させるセクタバッファビジー信号(例えば、“0”)を入力している。これにより転送コマンド(制御信号)は、セレクタ204を介して、AND回路205に入力される。I/Oコントローラ107へ制御信号を送出する際、アドレスデコード信号は、“1”となり、転送コマンドは、AND回路205から出力され、I/Oコントローラ107に入力される。

DMAコントローラ103を起動すると、セクタバッファコントローラ106の転送単位設定レジスタ135に、ステータスチェックを行う転送単位を設定する(ステップS3)。

図5は、第1の実施の形態の半導体装置の転送処理時における信号の様子を示すタイミングチャートである。

まず、図4のステップS1の転送コマンド発行のために、CPU101によるI/Oコントローラ107へのアクセスが行われる。このとき、CPU101から出力されたチップセレクト信号/CS1がI/Oコントローラ107のチップセレクト信号/CS3として使用され、CPU101からの発行されたコマンドがI/Oコントローラ107に転送される。

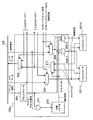

図6は、第2の実施の形態の半導体装置の構成を示す図である。

図1で示した第1の実施の形態の半導体装置100と同一の構成要素については同一符号とし、説明を省略する。

なお、図2で示した第1の実施の形態の半導体装置100の切替部105と同様の構成要素については同一符号としている。

選択信号は、セレクタ213に入力される。そして、セレクタ213は、リード動作時に、I/Oコントローラ107−1、107−2のリードデータのいずれかを選択信号に応じて選択してセレクタ203に入力する。

図3で示した第1の実施の形態の半導体装置100のセクタバッファコントローラ106と同様の構成要素については同一符号としている。

図9は、第2の実施の形態の半導体装置による転送処理を示すフローチャートである。

まず、切替部105aの切替レジスタ212に、例えば、“1”をセットする。これにより、AND回路205−1の出力は有効になり、AND回路205−2の出力は無効(“0”)となる。すなわち、I/Oコントローラ107−1のパスが有効になる(ステップS11)。

そして、図4で示したような転送処理で、I/Oデバイス107a−1との転送処理を行う(ステップS13)。

そして、図4で示したような転送処理で、I/Oデバイス107a−2との転送処理を行う(ステップS16)。

図10、図11は、第2の実施の形態の半導体装置の転送処理時における信号の様子を示すタイミングチャートである。

101 CPU

102 メモリ

103 DMAコントローラ

104 セクタバッファ

105 切替部

106 セクタバッファコントローラ

107 I/Oコントローラ

107a I/Oデバイス

108 システムバス

P1、P2 入出力ポート

Claims (8)

- DMA転送処理を行う半導体装置において、

入出力装置とのデータ転送を制御する入出力制御部と、

転送中のデータを一時記憶し、第1の入出力ポートをシステムバスとのDMA転送に用い、第2の入出力ポートを前記入出力制御部とのデータ転送に用いる一時記憶部と、

前記システムバスと前記入出力制御部を接続するか、前記一時記憶部と前記入出力制御部または前記システムバスを接続するかを切り替える切替部と、

前記第1及び前記第2の入出力ポートによるデータ転送を別々に起動し、前記一時記憶部と前記入出力制御部間での転送単位分の前記データの転送の終了を検出すると、前記一時記憶部と前記入出力制御部とのデータ転送を遮断し前記システムバスと前記入出力制御部とを接続するための制御信号を前記切替部に送出する記憶制御部と、

を有することを特徴とする半導体装置。 - 前記記憶制御部は、起動ビットをセットすることで、前記第1及び前記第2の入出力ポートによるデータ転送を別々に起動させる2つのレジスタを有していることを特徴とする請求項1記載の半導体装置。

- 前記記憶制御部は、前記転送単位を設定するレジスタを有していることを特徴とする請求項1記載の半導体装置。

- 前記記憶制御部は、前記転送単位の前記データの転送が終了したか否かの情報を記憶するステータスレジスタを有していることを特徴とする請求項1記載の半導体装置。

- 前記記憶制御部は、前記入出力制御部のアクセスサイクルを記憶するレジスタを有し、前記アクセスサイクルに応じた制御信号またはアドレス信号を前記入出力制御部に送出することを特徴とする請求項1記載の半導体装置。

- 複数の前記入出力制御部を有し、

前記切替部は、複数の前記入出力制御部のいずれか1つを選択するための情報を記憶するレジスタを有していることを特徴とする請求項1記載の半導体装置。 - 前記一時記憶部は、デュアルポートRAMであることを特徴とする請求項1記載の半導体装置。

- DMA転送処理を行うデータ転送方法において、

第1の入出力ポートをシステムバスとのDMA転送に用い、第2の入出力ポートを入出力装置とのデータ転送を制御する入出力制御部とのデータ転送に用いる一時記憶部の、前記第1及び前記第2の入出力ポートによるデータ転送を別々に起動し、

切替部によって前記システムバスと前記入出力制御部を接続するか、前記一時記憶部と前記入出力制御部または前記システムバスを接続するかを切り替え、

前記一時記憶部と前記入出力制御部間での転送単位分のデータの転送の終了を検出すると、前記切替部によって前記一時記憶部と前記入出力制御部とのデータ転送を遮断し、前記システムバスと前記入出力制御部とを接続することを特徴とするデータ転送方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006180952A JP2008009817A (ja) | 2006-06-30 | 2006-06-30 | 半導体装置及びデータ転送方法 |

| US11/706,983 US7725621B2 (en) | 2006-06-30 | 2007-02-16 | Semiconductor device and data transfer method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006180952A JP2008009817A (ja) | 2006-06-30 | 2006-06-30 | 半導体装置及びデータ転送方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2008009817A true JP2008009817A (ja) | 2008-01-17 |

Family

ID=38878167

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006180952A Pending JP2008009817A (ja) | 2006-06-30 | 2006-06-30 | 半導体装置及びデータ転送方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7725621B2 (ja) |

| JP (1) | JP2008009817A (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5277562B2 (ja) * | 2007-04-19 | 2013-08-28 | 株式会社ニコン | 電子機器、電子カメラおよびデータ転送プログラム |

| TWI389030B (zh) * | 2008-05-07 | 2013-03-11 | 晨星半導體股份有限公司 | 於微處理器下載並執行程式碼的方法與電腦程式產品以及包含該微處理器之通訊裝置 |

| US8949486B1 (en) * | 2013-07-17 | 2015-02-03 | Mellanox Technologies Ltd. | Direct memory access to storage devices |

| US9696942B2 (en) | 2014-03-17 | 2017-07-04 | Mellanox Technologies, Ltd. | Accessing remote storage devices using a local bus protocol |

| US9727503B2 (en) | 2014-03-17 | 2017-08-08 | Mellanox Technologies, Ltd. | Storage system and server |

| US11934658B2 (en) | 2021-03-25 | 2024-03-19 | Mellanox Technologies, Ltd. | Enhanced storage protocol emulation in a peripheral device |

| US11934333B2 (en) | 2021-03-25 | 2024-03-19 | Mellanox Technologies, Ltd. | Storage protocol emulation in a peripheral device |

| US11726666B2 (en) | 2021-07-11 | 2023-08-15 | Mellanox Technologies, Ltd. | Network adapter with efficient storage-protocol emulation |

| US12117948B2 (en) | 2022-10-31 | 2024-10-15 | Mellanox Technologies, Ltd. | Data processing unit with transparent root complex |

| US12007921B2 (en) | 2022-11-02 | 2024-06-11 | Mellanox Technologies, Ltd. | Programmable user-defined peripheral-bus device implementation using data-plane accelerator (DPA) |

| US11886369B1 (en) * | 2023-09-14 | 2024-01-30 | Qualcomm Incorporated | Apparatus and methods for burst communications within die architectures |

| US12547543B2 (en) | 2024-07-31 | 2026-02-10 | Mellanox Technologies, Ltd. | Cache coherency |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03290750A (ja) * | 1990-04-09 | 1991-12-20 | Matsushita Electric Ind Co Ltd | Dma転送方法 |

| JPH08106363A (ja) * | 1994-10-07 | 1996-04-23 | Hitachi Ltd | マルチディスク装置 |

| JPH1091570A (ja) * | 1996-09-13 | 1998-04-10 | Matsushita Electric Ind Co Ltd | データ転送装置 |

| JPH10214237A (ja) * | 1997-01-30 | 1998-08-11 | Nec Corp | バス制御装置 |

| JP2005316700A (ja) * | 2004-04-28 | 2005-11-10 | Sony Corp | データ転送方法および装置 |

| JP2006126938A (ja) * | 2004-10-26 | 2006-05-18 | Canon Inc | データ転送システム及びそのデータ転送方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05173938A (ja) * | 1991-10-08 | 1993-07-13 | Fujitsu Ltd | 間欠dma制御方式 |

| US5889776A (en) * | 1997-01-31 | 1999-03-30 | Alpnet Corporation | Physical layer switch system for ethernet local area network communication system |

| US6330623B1 (en) * | 1999-01-08 | 2001-12-11 | Vlsi Technology, Inc. | System and method for maximizing DMA transfers of arbitrarily aligned data |

-

2006

- 2006-06-30 JP JP2006180952A patent/JP2008009817A/ja active Pending

-

2007

- 2007-02-16 US US11/706,983 patent/US7725621B2/en not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03290750A (ja) * | 1990-04-09 | 1991-12-20 | Matsushita Electric Ind Co Ltd | Dma転送方法 |

| JPH08106363A (ja) * | 1994-10-07 | 1996-04-23 | Hitachi Ltd | マルチディスク装置 |

| JPH1091570A (ja) * | 1996-09-13 | 1998-04-10 | Matsushita Electric Ind Co Ltd | データ転送装置 |

| JPH10214237A (ja) * | 1997-01-30 | 1998-08-11 | Nec Corp | バス制御装置 |

| JP2005316700A (ja) * | 2004-04-28 | 2005-11-10 | Sony Corp | データ転送方法および装置 |

| JP2006126938A (ja) * | 2004-10-26 | 2006-05-18 | Canon Inc | データ転送システム及びそのデータ転送方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20080005387A1 (en) | 2008-01-03 |

| US7725621B2 (en) | 2010-05-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7725621B2 (en) | Semiconductor device and data transfer method | |

| US6950910B2 (en) | Mobile wireless communication device architectures and methods therefor | |

| US7171526B2 (en) | Memory controller useable in a data processing system | |

| JP4768697B2 (ja) | 記憶システム、およびデータ転送方法 | |

| JP2011154556A (ja) | 半導体記憶装置 | |

| US7162556B2 (en) | Matrix type bus connection system and power reduction method therefor | |

| US8850086B2 (en) | SD switch box in a cellular handset | |

| CN107851076B (zh) | 用于控制存储器访问的装置、系统及方法 | |

| TWI471731B (zh) | 記憶體存取方法、記憶體存取控制方法、spi快閃記憶體裝置以及spi控制器 | |

| KR100899514B1 (ko) | 버스트 모드를 지원하는 외부 메모리에 프로세서를 인터페이스하는 방법 | |

| JP2005303718A (ja) | マトリックス状バス接続システム | |

| JPH11232213A (ja) | 入出力装置におけるデータ転送方式 | |

| US7107373B2 (en) | Method of hot switching data transfer rate on bus | |

| JP4723334B2 (ja) | Dma転送システム | |

| JP2004213666A (ja) | Dmaモジュールとその操作方法 | |

| JP2008287557A (ja) | バスシステム及びマイクロコンピュータ | |

| JP2005010966A (ja) | Lsi装置 | |

| JP2007305073A (ja) | データ処理装置及びメモリコントローラチップ | |

| JP2007334600A (ja) | 半導体集積回路装置 | |

| JP2007328647A (ja) | Cpu間のデータ転送方式 | |

| JP2003330871A (ja) | データ転送装置 | |

| JPH0449460A (ja) | Dmaコントローラ | |

| JP2007108858A (ja) | ピン共有装置およびピン共有方法 | |

| JP2005032019A (ja) | Ambaにおけるバス調停システム | |

| WO2006112968A1 (en) | Apparatus to improve bandwidth for circuits having multiple memory controllers |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20080729 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090303 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110512 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110524 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20111108 |