JP2007227697A - 半導体装置および半導体集積装置 - Google Patents

半導体装置および半導体集積装置 Download PDFInfo

- Publication number

- JP2007227697A JP2007227697A JP2006047753A JP2006047753A JP2007227697A JP 2007227697 A JP2007227697 A JP 2007227697A JP 2006047753 A JP2006047753 A JP 2006047753A JP 2006047753 A JP2006047753 A JP 2006047753A JP 2007227697 A JP2007227697 A JP 2007227697A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- transistor

- mos transistor

- bipolar transistor

- protection circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

【課題】十分な静電耐量を有する半導体装置および半導体集積装置を提供する。

【解決手段】 ドレインD1が第1の電位Voに接続され、ゲートG1が駆動回路12に接続され、ソースS1が第2の電位GNDに接続された第1MOSトランジスタM1と、コレクタC1が第1の電位Voに接続され、ベースB1が開放されたバイポーラトランジスタQ1と、ドレインD2がバイポーラトランジスタQ1のエミッタE1に接続され、ゲートG2がソースS2に接続され、ソースS2が第2の電位GNDに接続された第2MOSトランジスタM2とを有する静電保護回路13とを具備する。

静電保護回路13のブレークダウン電圧はバイポーラトランジスタQ1と第2MOSトランジスタM2のブレークダウン電圧の和となり、第1MOSトランジスタM1のブレークダウン電圧より小さく、且つ最大動作電圧より大きいブレークダウン電圧が得られる。

【選択図】 図1

【解決手段】 ドレインD1が第1の電位Voに接続され、ゲートG1が駆動回路12に接続され、ソースS1が第2の電位GNDに接続された第1MOSトランジスタM1と、コレクタC1が第1の電位Voに接続され、ベースB1が開放されたバイポーラトランジスタQ1と、ドレインD2がバイポーラトランジスタQ1のエミッタE1に接続され、ゲートG2がソースS2に接続され、ソースS2が第2の電位GNDに接続された第2MOSトランジスタM2とを有する静電保護回路13とを具備する。

静電保護回路13のブレークダウン電圧はバイポーラトランジスタQ1と第2MOSトランジスタM2のブレークダウン電圧の和となり、第1MOSトランジスタM1のブレークダウン電圧より小さく、且つ最大動作電圧より大きいブレークダウン電圧が得られる。

【選択図】 図1

Description

本発明は、静電保護回路を有する半導体装置および半導体集積装置に関する。

一般に、半導体素子を有する半導体装置においては、外部からの静電気による静電放電(以後、ESD:Electrostatic Dischargeという)から半導体素子を保護するために静電保護回路が用いられている。

従来、ラテラル構造の2重拡散型絶縁ゲート電界効果トランジスタ(以後、LDMOS:Lateral Double Diffused MOSトランジスタという)の静電保護回路の保護素子として、コレクタが電源に接続され、ベースがエミッタに接続され、エミッタが接地されたバイポーラトランジスタが用いられていた。

このバイポーラトランジスタは、所謂逆方向にバイアスされたダイオードとして機能している。

このバイポーラトランジスタは、所謂逆方向にバイアスされたダイオードとして機能している。

しかし、LDMOSトランジスタのブレークダウン電圧はバイポーラトランジスタのブレークダウン電圧より低いため、LDMOSトランジスタの素子サイズを十分大きくして、ESD電荷を分散する必要がある。

そのため、LDMOSトランジスタの素子サイズが必要以上に大きくなるという問題がある。

そのため、LDMOSトランジスタの素子サイズが必要以上に大きくなるという問題がある。

これに対して、LDMOSトランジスタの静電保護回路として、ツェナーダイオードを用いたものが知られている(例えば、特許文献1参照。)。

特許文献1に開示されたLDMOSトランジスタの静電保護回路は、LDMOSトランジスタのドレインとゲートの間およびゲートとソースの間にそれぞれ複数のツェナーダイオードが直列に接続されている。

LDMOSトランジスタのドレインとソースの間に、LDMOSトランジスタのブレークダウン電圧より低い所定の電圧以上のESD電圧が印加されると、ツェナーダイオードがブレークダウンして導通し、LDMOSトランジスタのゲートとソースの間に電圧が印加される。

これにより、LDMOSトランジスタがオンし、ESD電荷はLDMOSトランジスタのドレインからソースを経由して接地電位に放電される。

LDMOSトランジスタのブレークダウン電圧より低い所定の電圧が得られるように、ツェナーダイオードを直列に接続する数を調整し、静電保護回路として機能させている。

然しながら、特許文献1に開示された静電保護回路は、LDMOSトランジスタのドレイン−ゲート間容量などにより、ESD電圧が印加されてからLDMOSトランジスタがオンするまでに時間遅れが生じる問題がある。

ここで、LDMOSトランジスタの素子サイズを小さくしてドレイン−ゲート間容量を減少させれば、オンするまでの時間遅れは改善されるが、逆にオン抵抗が高くなるためESD電荷を充分に放電することができないという問題がある。

このため、LDMOSトランジスタの素子サイズによってESD耐量の違いやバラツキが生じるため、確実な静電保護が行えないという問題がある。

米国特許第6064249号明細書

本発明は、十分な静電耐量を有する半導体装置および半導体集積装置を提供することを目的とする。

本発明の一態様の半導体装置、第1電極が第1の電位線路に接続され、制御電極が駆動回路に接続され、第2電極が第2の電位に接続された第1絶縁ゲート電界効果トランジスタと、第1電極が第1の電位線路に接続され、制御電極が開放された第1バイポーラトランジスタと、第1電極が前記第1バイポーラトランジスタの第2電極に接続され、制御電極が第2電極に接続され、第2電極が第2の電位に接続された第2絶縁ゲート電界効果トランジスタとを有する静電保護回路とを具備することを特徴としている。

また、本発明の一態様の半導体集積装置は、少なくとも、第1電極が第1の電位線路に接続され、制御電極が駆動回路に接続され、第2電極が第2の電位に接続された第1絶縁ゲート電界効果トランジスタと、第1電極が第1の電位線路に接続され、制御電極が開放された第1バイポーラトランジスタと、第1電極が前記第1バイポーラトランジスタの第2電極に接続され、制御電極が第2電極に接続され、第2電極が第2の電位に接続された第2絶縁ゲート電界効果トランジスタとを有する静電保護回路とが、同一半導体チップ上に集積して形成されていることを特徴としている。

本発明によれば、十分な静電耐量を有する半導体装置および半導体集積装置が得られる。

以下、本発明の実施例について図面を参照しながら説明する。

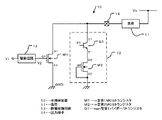

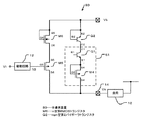

図1は本発明の実施例1に係る半導体装置の構成を示す回路図である。

図1に示すように、本実施例の半導体装置10は、オープンドレインD1(第1電極)が負荷11を介して電源Vo(第1の電位)に接続され、ゲートG1(制御電極)が駆動回路12に接続され、ソースS1(第2電極)が基準電位GND(第2の電位)に接続されたn型の第1絶縁ゲート電界効果トランジスタM1(以後、第1MOSトランジスタという)と、第1電位線路と基準電位GNDとの間第1MOSトランジスタM1に並列接続された静電保護回路13とを具備している。

静電保護回路13は、ベースB1(制御電極)が開放されたnpn型の第1バイポーラトランジスタQ1と、ゲートG2(制御電極)がソースS1(第2電極)に接続されたn型の第2絶縁ゲート電界効果トランジスタM2(以後、第2MOSトランジスタという)とが直列接続されている。

第1MOSトランジスタM1は、高耐圧でオン抵抗の低いラテラル構造の2重拡散型絶縁ゲート電界効果トランジスタ(LDMOSトランジスタ)で、ゲートG1に駆動信号Vinを入力し、オープンドレインD1を出力端子14として、負荷11、例えばソレノイドコイルやモータの巻線を駆動する。

駆動回路12は、制御信号V1に基づいて第1MOSトランジスタM1をオンまたはオフするための、例えば0−5Vの駆動信号V2を出力する。

ベースB1(制御電極)が開放されたnpn型の第1バイポーラトランジスタQ1は、コレクタ−ベース間の少しのリーク電流でもコレクタC1とエミッタE1の間が導通するので、逆方向にバイアスされたダイオードとして動作する。

同様に、ゲートG2がソースS1に接続されたn型の第2MOSトランジスタM2は、寄生ダイオードにより逆方向にバイアスされたダイオードとして動作する。

これにより、第1バイポーラトランジスタQ1のブレークダウン電圧と第2MOSトランジスタM2のブレークダウン電圧との和が静電保護回路13のブレークダウン電圧となる。

一般に、ベースB1が開放された第1バイポーラトランジスタQ1のブレークダウン電圧BVQ1は、ベースB1とエミッタE1が接続された場合のブレークダウン電圧BVM1よりかなり小さい。

そのため、電源電圧Voが第1MOSトランジスタM1のブレークダウン電圧BVM1より低い所定の電圧より高く設定されている場合に、第1MOSトランジスタM1の通常動作時に第1バイポーラトランジスタQ1がブレークダウンしてしまうことがあり、静電保護回路13の保護素子として第1バイポーラトランジスタQ1だけではブレークダウン電圧が不足する。

そこで、第1バイポーラトランジスタQ1に第2MOSトランジスタM2を直列に接続することにより、第1MOSトランジスタの通常動作条件においては静電保護回路13がブレークダウンしないようにすることができる。

即ち、BVM1>BVQ1+BVM2>第1MOSトランジスタM1の最大動作電圧とすることができる。

即ち、BVM1>BVQ1+BVM2>第1MOSトランジスタM1の最大動作電圧とすることができる。

ここで、第1MOSトランジスタM1の最大動作電圧とは、電源電圧Voから負荷11を通してドレインに印加される電圧の最大値をいう。

その結果、第1MOSトランジスタM1の通常動作条件において印加されるドレイン電圧では、静電保護回路13はブレークダウンすることなく、且つ第1MOSトランジスタM1のブレークダウン電圧BVM1より低いESD電圧でブレークダウンさせることが可能である。

具体的には、一般に、第1MOSトランジスタM1のブレークダウン電圧BVM1は、例えば50〜60V程度である。

ベースB1が開放された第1バイポーラトランジスタQ1のブレークダウン電圧BVQ1は、ベースB1に僅かな電流が流れてもオンするので、第1MOSトランジスタM1のブレークダウン電圧BVM1の1/2程度、例えば30〜40V程度である。

ゲートG2がソースS1に接続された第2MOSトランジスタM2のブレークダウン電圧BVM2は、ドレインD2とソースS2間の寄生ダイオードにより、例えば5〜7V程度である。

これにより、静電保護回路13のブレークダウン電圧BVESDは、BVESD=BVQ1+BVM2=35〜47V程度となり、第1MOSトランジスタM1のブレークダウン電圧BVM1より小さく、且つ第1MOSトランジスタM1の最大動作電圧(例えば30V)より大きくすることができる。

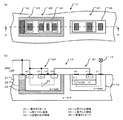

次に、本実施例の半導体集積装置について図2および図3を用いて説明する。図2は半導体装置10が同一チップ上にモノリシックに集積された半導体集積装置を示す図、図3は半導体装置の要部を示す図で、図3(a)は保護回路13の構成を示す平面図、図3(b)は図3(a)のA−A線に沿って切断し矢印方向に眺めた断面図である。

図2に示すように、本実施例の半導体集積装置20は、オープンドレインD1が負荷11を介して電源Voに接続された第1MOSトランジスタM1と、第1MOSトランジスタM1に並列接続された静電保護回路13とを有する複数の半導体装置10が同一チップ21上にモノリシックに集積して形成されている。

更に、半導体集積装置20は、処理回路23が同一チップ21上にモノリシックに集積して形成されている。処理回路23は外部演算部、例えばCPU24から、所定の演算結果を受け取り、負荷11を駆動するために必要な処理を行い、その結果を制御信号V1として駆動回路12へ出力する。

また、半導体チップ21上にはCPUから演算結果を入力し、負荷11を駆動するために必要なボンディングパッド22a〜22eが形成されている。

処理回路23は、例えばp―MOSトランジスタとn−MOSトランジスタのCMOS回路で構成され、第1MOSトランジスタM1のスイッチングノイズの影響を受けないように、ガードリング等でシールドされた領域に形成するのが好ましい。

図3に示すように、静電保護回路13の第2MOSトランジスタM2は電位を固定するためのバックゲートB2がソースS2に接続されており、ゲートG2とソースS2を短絡してバックゲートB2をアノードとし、ドレインD2をカソードとして寄生ダイオード30を形成し、ESD電圧により寄生ダイオード30をブレークダウンさせてドレインD2からバルクを介してバックゲートB2へESD電流を流すようにしたものである。

即ち、第2MOSトランジスタM2は、例えば高耐圧のn型MOSトランジスタまたはn型DMOSトランジスタで、基板、例えばp型シリコン基板31に形成されたn型埋め込み領域32によりp型シリコン基板31と絶縁分離されている。

n型埋め込み領域32の内部にはp型ウェル領域33が形成されている。このn型埋め込み領域32に囲われたp型ウェル領域33をバルクとして、バックゲートB2、ソースS2、ドレインD2およびゲートG2がそれぞれ所定の領域に設けられ、第2MOSトランジスタM2を形成している。

そして、バックゲートB2、ソースS2、ゲートG2およびn型埋め込み領域32は基準電位GNDに接続され、ドレインD2は第1バイポーラトランジスタQ1のエミッタE1に接続されている。

第1バイポーラトランジスタQ1は、p型シリコン基板31に形成されたn型ウェル領域34によりp型シリコン基板31と絶縁分離されている。

n型ウェル領域34の内部には、コレクタ層、ベース層およびエミッタ領域がそれぞれ設けられ、第1バイポーラトランジスタQ1を形成している。

そして、コレクタC1はオープンコレクタとして出力端子14に接続され、ベースB1は開放されている。

n型ウェル領域34の内部には、コレクタ層、ベース層およびエミッタ領域がそれぞれ設けられ、第1バイポーラトランジスタQ1を形成している。

そして、コレクタC1はオープンコレクタとして出力端子14に接続され、ベースB1は開放されている。

ベースB1が開放された第1バイポーラトランジスタQ1は、ベースB1に僅かな電流が流れてもトランジスタがオンするので、逆方向にバイアスされたコレクタC1とベースB1間の等価ダイオード36が形成される。

以上説明したように、本実施例では、静電保護回路13は第1バイポーラトランジスタQ1と第2MOSトランジスタM2の直列回路で構成されている。

その結果、静電保護回路13のブレークダウン電圧を第1MOSトランジスタM1のブレークダウン電圧より低く、且つ第1MOSトランジスタM1の最大動作電圧より高くすることができる。

従って、十分な静電耐量を有する半導体装置およびそれを用いた半導体集積装置を提供することができる。

ここでは、一般的に第2MOSトランジスタM2のサブストレート耐圧は第1バイポーラトランジスタQ1より低いので、第1バイポーラトランジスタQ1を高電位Vo側に接続し、第2MOSトランジスタM2を基準電位GND側に接続した場合について説明したが、第2MOSトランジスタM2のサブストレート耐圧が第1バイポーラトランジスタQ1より高い場合にはいずれの側に接続しても構わない。

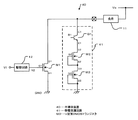

図4は本発明の実施例2に係る半導体装置の構成を示す回路図である。本実施例において、上記実施例1と同一の構成部分には同一符号を付してその部分の説明は省略し、異なる部分について説明する。

本実施例が実施例1と異なる点は、第2MOSトランジスタを2個直列に接続したことにある。

即ち、図4に示すように、本実施例の半導体装置40は、第2MOSトランジスタM2と基準電位GNDの間に、第2MOSトランジスタM2と導電型が等しく、且つドレインD3が第2MをOSトランジスタM2のソースS2に接続され、ゲートG3がソースS3に接続され、ソースS3が基準電位GNDに接続された第3MOSトランジスタM3を有する静電保護回路41を具備している。

これにより、静電保護回路41のブレークダウン電圧は第3MOSトランジスタM3のブレークダウン電圧だけ高くすることが可能である。

第3MOSトランジスタM3は第2MOSトランジスタM2と等しくすることにより、静電保護回路41のブレークダウン電圧BVESDは次式で表される。

BVESD=BVQ1+BVM2+BVM3=BVQ1+2×BVM2

ここで、BVESDは静電保護回路41のブレークダウン電圧、BVM3は第3MOSトランジスタM3のブレークダウン電圧である。

BVESD=BVQ1+BVM2+BVM3=BVQ1+2×BVM2

ここで、BVESDは静電保護回路41のブレークダウン電圧、BVM3は第3MOSトランジスタM3のブレークダウン電圧である。

以上説明したように、本実施例では、静電保護回路41は第2MOSトランジスタM2に直列に接続された第3MOSトランジスタM3を有しているので、静電保護回路41のブレークダウン電圧を第3MOSトランジスタM3のブレークダウン電圧だけ高く設定することができる利点がある。

ここでは、1の第3MOSトランジスタM3を直列に接続する場合について説明したが、第1MOSトランジスタM1のブレークダウン電圧より低い電圧範囲において、更に複数接続しても構わない。

これによれば、静電保護回路41のブレークダウン電圧を離散的に高く設定できる利点がある。

これによれば、静電保護回路41のブレークダウン電圧を離散的に高く設定できる利点がある。

図5は本発明の実施例3に係る半導体装置の構成を示す回路図である。本実施例において、上記実施例1と同一の構成部分には同一符号を付してその部分の説明は省略し、異なる部分について説明する。

本実施例が実施例1と異なる点は、第2MOSトランジスタM2をp型のMOSトランジスタに置き換えたことにある。

即ち、図5に示すように、本実施例の半導体装置50は、ソースS4が第1バイポーラトランジスタQ1のエミッタE1に接続され、ゲートG4がソースS4に接続され、ドレインD4が基準電位GNDに接続されたp型の第4MOSトランジスタM4を有する静電保護回路51を具備している。

第4MOSトランジスタM4は、電位を固定するためのバックゲートがソースS4に接続されており、ゲートG4とソースS4を短絡してバックゲートをカソードとし、ドレインD4をアノードとする寄生ダイオードを形成し、ESD電圧により寄生ダイオードをブレークダウンさせてバックゲートからバルクを介してドレインD4へESD電流を流すようにしたものである。

以上説明したように、本実施例では、静電保護回路51はp型の第4MOSトランジスタM4を有しているので、p型シリコン基板31に半導体装置50を形成する場合に、MOSトランジスタを絶縁分離するための埋め込み領域が不要であり、半導体チップのサイズが縮小できる利点がある。

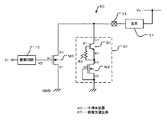

図6は本発明の実施例4に係る半導体装置の構成を示す回路図である。本実施例において、上記実施例1と同一の構成部分には同一符号を付してその部分の説明は省略し、異なる部分について説明する。

本実施例が実施例1と異なる点は、抵抗を介して第1バイポーラトランジスタQ1のベースB1とエミッタE1を接続したことにある。

即ち、図6に示すように、本実施例の半導体装置60は、抵抗R1を介して第1バイポーラトランジスタQ1のベースB1とエミッタE1とが接続された静電保護回路61を具備している。

静電保護回路61のブレークダウン電圧BVESDは、ベースB1とエミッタE1とが接続された第1バイポーラトランジスタQ1のブレークダウン電圧BVQ1Rと、第2MOSトランジスタM2のブレークダウン電圧BVM2の和となる。

一般に、抵抗を介してベースB1とエミッタE1を接続した第1バイポーラトランジスタQ1のブレークダウン電圧BVCERは、ベースB1とエミッタE1を直接接続したときのブレークダウン電圧BVCESと、ベースB1が開放されたときのブレークダウン電圧BVCEOに対して、BVCES>BVCER>BVCEOの関係にある。

その結果、抵抗R1を変えることにより、第1バイポーラトランジスタQ1のブレークダウン電圧BVQ1をBVCEOからBVCESまで連続的に変化させることができる。従って、静電保護回路61のブレークダウン電圧BVESDを連続的に変えることが可能である。

以上説明したように、本実施例では、抵抗R1により静電保護回路61のブレークダウン電圧BVESDを微調整できる利点がある。

図7は本発明の実施例5に係る半導体装置の構成を示す回路図である。本実施例において、上記実施例1と同一の構成部分には同一符号を付してその部分の説明は省略し、異なる部分について説明する。

本実施例が実施例3と異なる点は、電流制御用トランジスタをn型のMOSトランジスタからp型のMOSトランジスタに変更したことにある。

即ち、図6に示すように、本実施例の半導体装置70は、ドレインD5が電源Voに接続され、ゲートG5が駆動回路12に接続され、ソースS5が電源Vbに接続されたp型の第5MOSトランジスタM5と、電源Voと電源Vbとの間に接続された静電保護回路51とを具備している。

以上説明したように、本実施例によれば、静電保護回路51は電流制御用トランジスタがn型の第1MOSトランジスタM1だけでなく、p型の第5MOSトランジスタにも適用できる利点がある。

図8は本発明の実施例6に係る半導体装置の構成を示す回路図である。本実施例において、上記実施例5と同一の構成部分には同一符号を付してその部分の説明は省略し、異なる部分について説明する。

本実施例が実施例5と異なる点は、第5MOSトランジスタM5と静電保護回路51に逆流防止用のダイオードを接続したことにある。

即ち、図8に示すように、本実施例では、ドレインD6が第5MOSトランジスタM5のソースS5に接続され、ゲートG6とソースS6が接続され、ソースS6が電源Vbに接続されたn型の第6MOSトランジスタM6と、コレクタC2が第1バイポーラトランジスタQ1のコレクタC1に接続され、ベースB2とエミッタE2が接続され、エミッタE2が電源Vbに接続されたnpn型の第2バイポーラトランジスタQ2とを具備している。

ゲートG6とソースS6が接続された第6MOSトランジスタM6は、順方向にバイアスされたダイオードとして機能するので、第5MOSトランジスタM5を流れる電流を一方向に制限し、逆流を防止することができる。

同様に、ベースB2とエミッタE2が接続された第2バイポーラトランジスタQ2は、順方向にバイアスされたダイオードとして機能するので、静電保護回路81を流れる電流を一方向に制限し、逆流を防止することができる。

例えば、半導体装置80を車載用途に使用した場合に、セルモータを回転させたときに電源Vbと電源Voの高低関係が一時的に逆転し、半導体装置80に逆電流が流れるのを防止することができる。

ここで、静電保護回路51のブレークダウン電圧は、第2バイポーラトランジスタQ2の順方向電圧分だけ高くなるが、高々0.7V程度でありその影響はわずかである。

以上説明したように、本実施例の半導体装置80は、逆流防止ダイオードとして第6MOSトランジスタM6および第2バイポーラトランジスタQ2を有しているので、半導体装置80に逆電流が流れるのを防止することができる利点がある。その結果、半導体装置80の信頼性が向上し、車載用途などに適している。

また、半導体装置80の製造工程において、第1バイポーラトランジスタQ1の開放されているベースB1が帯電してベースB1とエミッタE1がショートし、第1バイポーラトランジスタQ1の特性が変動する恐れがある。

そのため、図9に示すように、第1バイポーラトランジスタQ1のベースB1とエミッタE1にダイオード、例えばダイオード接続されたバイポーラトランジスタ92を接続しておくことが望ましい。これによれば、特性の安定した半導体装置90が得られる利点がある。

ここでは、第6MOSトランジスタM6および第2バイポーラトランジスタQ2を電源Vb側に接続する場合について説明したが、負荷11が接続された電源Vo側に接続しても構わない。

また、第6MOSトランジスタM6はダイオードとして機能しているので、第2バイポーラトランジスタQ2と同じバイポーラトランジスタに置き換えることもできる。

即ち、第5MOSトランジスタM5の動作電流が大きい場合には基板への寄生電流が少ないMOSトランジスタを使用することが好ましいが、動作電流が少ない場合にはバイポーラトランジスタを使用しても構わない。

即ち、第5MOSトランジスタM5の動作電流が大きい場合には基板への寄生電流が少ないMOSトランジスタを使用することが好ましいが、動作電流が少ない場合にはバイポーラトランジスタを使用しても構わない。

更に、ダイオード92はダイオード接続されたバイポーラトランジスタである場合について説明したが、pn接合ダイオートであっても構わない。

10、40、50、60、70、80、90 半導体装置

11 負荷

12 駆動回路

13、41、51、61、71 静電保護回路

14 出力端子

20 半導体集積装置

21 半導体チップ

22a〜22e ボンディングパッド

23 処理回路

30 寄生ダイオード

31 p型シリコン基板

32 n型埋め込み領域

33 p型ウェル領域

34 n型ウェル領域

36 等価ダイオード

92 ダイオード

M1 n型第1MOSトランジスタ

M2 n型第2MOSトランジスタ

M3 n型第3MOSトランジスタ

M4 p型第4MOSトランジスタ

M5 p型第5MOSトランジスタ

M6 n型第6MOSトランジスタ

Q1 npn型第1バイポーラトランジスタ

Q2 npn型第2バイポーラトランジスタ

R1 抵抗

11 負荷

12 駆動回路

13、41、51、61、71 静電保護回路

14 出力端子

20 半導体集積装置

21 半導体チップ

22a〜22e ボンディングパッド

23 処理回路

30 寄生ダイオード

31 p型シリコン基板

32 n型埋め込み領域

33 p型ウェル領域

34 n型ウェル領域

36 等価ダイオード

92 ダイオード

M1 n型第1MOSトランジスタ

M2 n型第2MOSトランジスタ

M3 n型第3MOSトランジスタ

M4 p型第4MOSトランジスタ

M5 p型第5MOSトランジスタ

M6 n型第6MOSトランジスタ

Q1 npn型第1バイポーラトランジスタ

Q2 npn型第2バイポーラトランジスタ

R1 抵抗

Claims (5)

- 第1電極が第1の電位線路に接続され、制御電極が駆動回路に接続され、第2電極が第2の電位に接続された第1絶縁ゲート電界効果トランジスタと、

第1電極が第1の電位線路に接続され、制御電極が開放された第1バイポーラトランジスタと、第1電極が前記第1バイポーラトランジスタの第2電極に接続され、制御電極が第2電極に接続され、第2電極が第2の電位に接続された第2絶縁ゲート電界効果トランジスタとを有する静電保護回路と、

を具備することを特徴とする半導体装置。 - 前記第2絶縁ゲート電界効果トランジスタに、制御電極が第2電極に接続された同じ導電型の絶縁ゲート電界効果トランジスタが直列接続されていることを特徴とする請求項1に記載の半導体装置。

- 前記第1バイポーラトランジスタの制御電極と第2電極が抵抗を介して接続されていることを特徴とする請求項1に記載の半導体装置。

- 前記第1絶縁ゲート電界効果トランジスタに、制御電極が第2電極に接続された絶縁ゲート電界効果トランジスタが直列接続され、前記静電保護回路に、制御電極が第2電極に接続されたバイポーラトランジスタが直列接続されていることを特徴とする請求項1に記載の半導体装置。

- 少なくとも、

第1電極が第1の電位線路に接続され、制御電極が駆動回路に接続され、第2電極が第2の電位に接続された第1絶縁ゲート電界効果トランジスタと、

第1電極が第1の電位線路に接続され、制御電極が開放された第1バイポーラトランジスタと、第1電極が前記第1バイポーラトランジスタの第2電極に接続され、制御電極が第2電極に接続され、第2電極が第2の電位に接続された第2絶縁ゲート電界効果トランジスタとを有する静電保護回路と、

が同一半導体チップ上に集積して形成されていることを特徴とする半導体集積装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006047753A JP2007227697A (ja) | 2006-02-24 | 2006-02-24 | 半導体装置および半導体集積装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006047753A JP2007227697A (ja) | 2006-02-24 | 2006-02-24 | 半導体装置および半導体集積装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2007227697A true JP2007227697A (ja) | 2007-09-06 |

Family

ID=38549199

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006047753A Pending JP2007227697A (ja) | 2006-02-24 | 2006-02-24 | 半導体装置および半導体集積装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2007227697A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7800180B2 (en) * | 2006-06-29 | 2010-09-21 | Mitsumi Electric Co., Ltd. | Semiconductor electrostatic protection device |

| JP2012146899A (ja) * | 2011-01-14 | 2012-08-02 | Sanyo Semiconductor Co Ltd | 半導体装置 |

| JP2012174740A (ja) * | 2011-02-17 | 2012-09-10 | Sharp Corp | 半導体集積回路のesd保護回路およびそのesd保護素子 |

| US9985433B2 (en) | 2014-03-12 | 2018-05-29 | Kabushiki Kaisha Toshiba | Output circuit |

-

2006

- 2006-02-24 JP JP2006047753A patent/JP2007227697A/ja active Pending

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7800180B2 (en) * | 2006-06-29 | 2010-09-21 | Mitsumi Electric Co., Ltd. | Semiconductor electrostatic protection device |

| JP2012146899A (ja) * | 2011-01-14 | 2012-08-02 | Sanyo Semiconductor Co Ltd | 半導体装置 |

| JP2012174740A (ja) * | 2011-02-17 | 2012-09-10 | Sharp Corp | 半導体集積回路のesd保護回路およびそのesd保護素子 |

| US9985433B2 (en) | 2014-03-12 | 2018-05-29 | Kabushiki Kaisha Toshiba | Output circuit |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102903715B (zh) | 半导体集成电路 | |

| JP4942007B2 (ja) | 半導体集積回路 | |

| KR100392027B1 (ko) | 반도체 집적 회로 | |

| JP4282581B2 (ja) | 静電保護回路 | |

| JP4993092B2 (ja) | レベルシフト回路および半導体装置 | |

| US20080013233A1 (en) | Electrostatic breakdown protection circuit | |

| US5675469A (en) | Integrated circuit with electrostatic discharge (ESD) protection and ESD protection circuit | |

| US10256228B2 (en) | Semiconductor device | |

| US6878996B2 (en) | MOS power transistor | |

| US20060028776A1 (en) | Electrostatic discharge protection for an integrated circuit | |

| US9812437B2 (en) | Semiconductor integrated circuit device, and electronic appliance using the same | |

| US7643258B2 (en) | Methods and apparatus for electrostatic discharge protection in a semiconductor circuit | |

| JP2010129663A (ja) | 半導体装置 | |

| JP3444263B2 (ja) | 制御回路内蔵絶縁ゲート半導体装置 | |

| US8008727B2 (en) | Semiconductor integrated circuit device including a pad and first mosfet | |

| US6833590B2 (en) | Semiconductor device | |

| JP2007227697A (ja) | 半導体装置および半導体集積装置 | |

| US6583475B2 (en) | Semiconductor device | |

| JP4763324B2 (ja) | 静電保護回路及び該静電保護回路を含む半導体装置 | |

| US20050002141A1 (en) | Electrostatic discharge protection circuit | |

| CN100472786C (zh) | 半导体集成电路器件 | |

| CN112951820A (zh) | 静电保护结构和静电保护电路 | |

| JP4106804B2 (ja) | 集積回路用保護装置 | |

| JP2006121014A (ja) | 静電保護回路およびそれを用いた半導体集積装置 | |

| JPH1012828A (ja) | 半導体装置の保護回路 |