JP2006217618A - 出力インピーダンス回路及びこれを適用した出力バッファ回路 - Google Patents

出力インピーダンス回路及びこれを適用した出力バッファ回路 Download PDFInfo

- Publication number

- JP2006217618A JP2006217618A JP2006024716A JP2006024716A JP2006217618A JP 2006217618 A JP2006217618 A JP 2006217618A JP 2006024716 A JP2006024716 A JP 2006024716A JP 2006024716 A JP2006024716 A JP 2006024716A JP 2006217618 A JP2006217618 A JP 2006217618A

- Authority

- JP

- Japan

- Prior art keywords

- output

- mos transistor

- impedance

- power supply

- supply voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0175—Coupling arrangements; Interface arrangements

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0005—Modifications of input or output impedance

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Logic Circuits (AREA)

Abstract

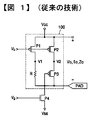

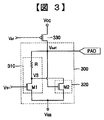

【解決手段】 出力インピーダンス回路は、出力ステージ及びインピーダンス制御ステージを備える。出力ステージは、DCバイアス電圧に対応する出力信号を出力端子を通じて出力し、インピーダンス制御ステージは、出力信号に応答して前記出力ステージに流れる電流を制御する。出力ステージは、抵抗素子及び第1MOSトランジスタを備える。抵抗素子は、一端が出力端子に接続される。第1MOSトランジスタは、一端が抵抗素子の他端に接続され、他端が電源電圧に接続され、ゲートに入力信号が印加される。

【選択図】 図3

Description

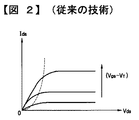

=K1{(Vcc-Vth)aVout1-1/2a2Vout12} …(数式3)

=K1{(Vcc-Vth)aVout1−1/2a2Vout12} + 1/2K2(Vout1−Vth)2

=Vout1{aK1(Vcc-Vth)−K2Vth} - 1/2Vout12(a2K1−K2)+1/2K2Vth2 …(数式5)

=K1{(Vcc-Vth)aVout1-1/2a2Vout12}+K2{(Vout1-Vth)aVout1-1/2a2Vout12}

=Vout1{aK1(Vcc-Vth) - K2Vth} - Vout12(a2K1/K2-aK2+1/2a2) …(数式7)

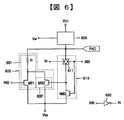

310 出力ステージ

320 インピーダンス制御ステージ

330 駆動トランジスタ

M1 第1MOSトランジスタ

M2 第2MOSトランジスタ

Claims (36)

- 出力信号の電圧レベルが変わっても、前記出力信号が出力される出力端子でのインピーダンス成分が一定である出力インピーダンス回路において、

DCバイアス電圧に対応する電流を前記出力端子に供給する出力ステージと、

前記出力信号に応答して前記出力ステージに流れる電流を制御するインピーダンス制御ステージとを備えることを特徴とする出力インピーダンス回路。 - 前記出力ステージは、

一端が前記出力端子に接続された抵抗素子と、

一端が前記抵抗素子の他端に接続され、他端が第1電源電圧に接続され、ゲートに前記DCバイアス電圧が印加される第1MOSトランジスタとを備えることを特徴とする請求項1に記載の出力インピーダンス回路。 - 前記インピーダンス制御ステージは、

一端が前記抵抗素子及び前記第1MOSトランジスタの共通端子に接続され、他端が前記第1電源電圧に接続され、ゲートに前記出力信号が印加される第2MOSトランジスタを備えることを特徴とする請求項2に記載の出力インピーダンス回路。 - 前記第1電源電圧は、

前記出力インピーダンス回路を含むシステムで用いられる電源電圧よりも低い電圧レベルを有する電圧であることを特徴とする請求項3に記載の出力インピーダンス回路。 - 前記第1MOSトランジスタ及び前記第2MOSトランジスタは、

N型MOSトランジスタであることを特徴とする請求項4に記載の出力インピーダンス回路。 - 前記出力端子は、

半導体装置のパッドであることを特徴とする請求項5に記載の出力インピーダンス回路。 - 前記抵抗素子は、

多結晶シリコン、PSG、及び拡散された活性層のうち一つを利用して形成された抵抗であることを特徴とする請求項2に記載の出力インピーダンス回路。 - 前記出力ステージは、

一端が前記出力端子に接続された抵抗素子と、

一端が前記抵抗素子の他端に接続され、他端が第2電源電圧に接続され、ゲートに前記DCバイアス電圧が印加される第3MOSトランジスタとを備えることを特徴とする請求項1に記載の出力インピーダンス回路。 - 前記インピーダンス制御ステージは、

一端が前記抵抗素子及び前記第3MOSトランジスタの共通端子に接続され、他端が前記第2電源電圧に接続され、ゲートに前記出力信号が印加される第4MOSトランジスタを備えることを特徴とする請求項8に記載の出力インピーダンス回路。 - 前記第2電源電圧は、

前記出力インピーダンス回路を含むシステムで用いられる電源電圧よりも高い電圧レベルを有する電圧であることを特徴とする請求項9に記載の出力インピーダンス回路。 - 前記第3MOSトランジスタ及び前記第4MOSトランジスタは、

P型MOSトランジスタであることを特徴とする請求項10に記載の出力インピーダンス回路。 - 前記出力端子は、

半導体装置のパッドであることを特徴とする請求項11に記載の出力インピーダンス回路。 - 前記抵抗素子は、

多結晶シリコン、PSG、及び拡散された活性層のうち一つを利用して形成された抵抗であることを特徴とする請求項8に記載の出力インピーダンス回路。 - 入力信号に応答して出力信号の電圧レベルが変わっても、前記出力信号が出力される出力端子でのインピーダンス成分が一定であるインピーダンス回路を備える出力バッファ回路において、

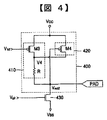

一端が前記出力端子に接続され、他端が高電源電圧に接続され、ゲートに前記入力信号が印加される駆動トランジスタと、

DC電圧を受信して動作し、一端が低電源電圧に接続され、他端が前記出力端子に接続されたインピーダンス回路とを備え、

前記インピーダンス回路は、

前記DCバイアス電圧に対応する電流を前記出力端子に供給する出力ステージと、

前記出力信号に応答して前記出力ステージに流れる電流を制御するインピーダンス制御ステージとを備えることを特徴とする出力バッファ回路。 - 前記出力ステージは、

一端が前記出力端子に接続された抵抗素子と、

一端が前記抵抗素子の他端に接続され、他端が前記低電源電圧に接続され、ゲートに前記DCバイアス電圧が印加される第1MOSトランジスタとを備えることを特徴とする請求項14に記載の出力バッファ回路。 - 前記インピーダンス制御ステージは、

一端が前記抵抗素子及び前記第1MOSトランジスタの共通端子に接続され、他端が前記低電源電圧に接続され、ゲートに前記出力信号が印加される第2MOSトランジスタを備えることを特徴とする請求項15に記載の出力バッファ回路。 - 前記第1MOSトランジスタ及び前記第2MOSトランジスタは、

N型MOSトランジスタであることを特徴とする請求項16に記載の出力バッファ回路。 - 前記駆動トランジスタは、

P型MOSトランジスタであることを特徴とする請求項17に記載の出力バッファ回路。 - 前記出力端子は、

半導体装置のパッドであることを特徴とする請求項18に記載の出力バッファ回路。 - 前記抵抗素子は、

多結晶シリコン、PSG、及び拡散された活性層のうち一つを利用して形成された抵抗であることを特徴とする請求項15に記載の出力バッファ回路。 - 入力信号に応答して出力信号の電圧レベルが変わっても、前記出力信号が出力される出力端子でのインピーダンス成分が一定であるインピーダンス回路を備える出力バッファ回路において、

DC電圧を受信して動作し、一端が高電源電圧に接続され、他端が前記出力端子に接続されたインピーダンス回路と、

一端が前記出力端子に接続され、他端が低電源電圧に接続され、ゲートに前記入力信号が印加される駆動トランジスタとを備え、

前記インピーダンス回路は、

前記DCバイアス電圧に対応する電流を前記出力端子に供給する出力ステージと、

前記出力信号に応答して前記出力ステージに流れる電流を制御するインピーダンス制御ステージとを備えることを特徴とする出力バッファ回路。 - 前記出力ステージは、

一端が前記出力端子に接続された抵抗素子と、

一端が前記抵抗素子の他端に接続され、他端が前記低電源電圧に接続され、ゲートに前記DCバイアス電圧が印加される第1MOSトランジスタとを備えることを特徴とする請求項21に記載の出力バッファ回路。 - 前記インピーダンス制御ステージは、

一端が前記抵抗素子及び前記第1MOSトランジスタの共通端子に接続され、他端が前記低電源電圧に接続され、ゲートに前記出力信号が印加される第2MOSトランジスタを備えることを特徴とする請求項22に記載の出力バッファ回路。 - 前記第1MOSトランジスタ及び前記第2MOSトランジスタは、

N型MOSトランジスタであることを特徴とする請求項23に記載の出力バッファ回路。 - 前記駆動トランジスタは、

P型MOSトランジスタであることを特徴とする請求項24に記載の出力バッファ回路。 - 前記出力端子は、

半導体装置のパッドであることを特徴とする請求項25に記載の出力バッファ回路。 - 前記抵抗素子は、

多結晶シリコン、PSG、及び拡散された活性層のうち一つを利用して形成された抵抗であることを特徴とする請求項22に記載の出力バッファ回路。 - 出力信号の電圧レベルが変わっても、前記出力信号が出力される出力端子でのインピーダンス成分が一定であり、正常動作状態及びハイインピーダンス状態を選択できる出力インピーダンス回路において、

制御信号及び逆制御信号に応答して動作し、前記出力信号を利用して前記出力インピーダンス回路の動作状態を選択するオンオフ信号を出力するオンオフ選択器と、

前記逆制御信号に対応する電流を前記出力端子に供給する出力ステージと、

前記オンオフ信号に応答して前記出力ステージに流れる電流を制御するインピーダンス制御ステージとを備えることを特徴とする出力インピーダンス回路。 - 前記出力ステージは、

一端が前記出力端子に接続された抵抗素子と、

一端が前記抵抗素子の他端に接続され、他端が電源電圧に接続され、ゲートに前記逆制御信号が印加される第1MOSトランジスタとを備えることを特徴とする請求項28に記載の出力インピーダンス回路。 - 前記インピーダンス制御ステージは、

一端が前記抵抗素子及び前記第1MOSトランジスタの共通端子に接続され、他端が前記電源電圧に接続され、ゲートに前記オンオフ信号が印加される第2MOSトランジスタを備えることを特徴とする請求項29に記載の出力インピーダンス回路。 - 前記オンオフ選択器は、

一端に接続された前記出力信号を前記制御信号及び逆制御信号に応答してスイッチングするスイッチと、

一端が前記スイッチの他端に接続され、他端が前記電源電圧に接続され、ゲートに前記逆制御信号が印加される第3MOSトランジスタとを備えることを特徴とする請求項30に記載の出力インピーダンス回路。 - 前記スイッチは、

一端が前記出力端子に接続され、他端が前記第3MOSトランジスタの一端に接続され、前記制御信号及び前記逆制御信号によって動作し、前記制御信号が論理的にハイレベルである時にスイッチがオンになることを特徴とする請求項31に記載の出力インピーダンス回路。 - 前記制御信号及び前記逆制御信号は、

位相が互いに逆相であることを特徴とする請求項28に記載の出力インピーダンス回路。 - 前記出力インピーダンス回路は、

前記逆制御信号の位相を反転させて前記制御信号を出力するインバータをさらに備えることを特徴とする請求項28に記載の出力インピーダンス回路。 - 出力信号の電圧レベルが変わっても、前記出力信号が出力される出力端子でのインピーダンス成分が一定であり、正常動作状態及びハイインピーダンス状態を選択できる出力バッファ回路において、

制御信号及び逆制御信号に応答して動作し、前記出力信号を利用して前記出力インピーダンス回路の動作状態を選択するオンオフ信号を出力するオンオフ選択器と、

前記オンオフ信号に応答して前記逆制御信号に対応する電流を一端に接続された第1電源電圧を通じて他端に接続された前記出力端子に供給する出力インピーダンス回路と、

入力信号に対応する電流を一端に接続された第2電源電圧を通じて他端に接続された出力端子に供給する駆動装置とを備えることを特徴とする出力バッファ回路。 - 前記第1電源電圧は、

前記出力バッファ回路で用いられる電源電圧よりも低い電源電圧であり、

前記第2電源電圧は、

前記出力バッファ回路で用いられる電源電圧よりも高い電源電圧であることを特徴とする請求項35に記載の出力バッファ回路。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2005-0009103 | 2005-02-01 | ||

| KR1020050009103A KR100652398B1 (ko) | 2005-02-01 | 2005-02-01 | 출력 임피던스회로 및 이를 적용한 출력버퍼회로 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006217618A true JP2006217618A (ja) | 2006-08-17 |

| JP5000144B2 JP5000144B2 (ja) | 2012-08-15 |

Family

ID=36980369

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006024716A Expired - Lifetime JP5000144B2 (ja) | 2005-02-01 | 2006-02-01 | 出力インピーダンス回路及びこれを適用した出力バッファ回路 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7471109B2 (ja) |

| JP (1) | JP5000144B2 (ja) |

| KR (1) | KR100652398B1 (ja) |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS56103524A (en) * | 1979-12-21 | 1981-08-18 | Philips Nv | Variable impedance circuit |

| JP2000269782A (ja) * | 1999-03-18 | 2000-09-29 | Hitachi Ltd | Mosトランジスタ抵抗回路 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5241221A (en) * | 1990-07-06 | 1993-08-31 | North American Philips Corp., Signetics Div. | CMOS driver circuit having reduced switching noise |

| JP3050289B2 (ja) | 1997-02-26 | 2000-06-12 | 日本電気株式会社 | 出力バッファ回路の出力インピーダンス調整回路 |

| JPH11163709A (ja) | 1997-11-27 | 1999-06-18 | Nec Corp | 出力インピーダンス調整回路 |

| JP3448231B2 (ja) | 1998-12-10 | 2003-09-22 | 株式会社東芝 | 半導体装置 |

| US6157206A (en) * | 1998-12-31 | 2000-12-05 | Intel Corporation | On-chip termination |

| JP2000310672A (ja) * | 1999-04-28 | 2000-11-07 | Fujitsu Ltd | 半導体装置 |

| KR20010011354A (ko) * | 1999-07-27 | 2001-02-15 | 윤종용 | 반도체 장치의 출력 임피던스 조절 회로 |

| JP3548487B2 (ja) * | 2000-02-23 | 2004-07-28 | Necエレクトロニクス株式会社 | 論理回路 |

| KR100394586B1 (ko) | 2000-11-30 | 2003-08-14 | 삼성전자주식회사 | 임피던스 제어회로 |

| US6563345B2 (en) * | 2001-03-15 | 2003-05-13 | Micron Technology, Inc. | Monotonic dynamic static pseudo-NMOS logic circuits |

| US6486700B1 (en) * | 2001-08-23 | 2002-11-26 | Sun Microsystems, Inc. | One-hot Muller C-elements and circuits using one-hot Muller C-elements |

| US6670824B2 (en) * | 2002-03-20 | 2003-12-30 | Agilent Technologies, Inc. | Integrated polysilicon fuse and diode |

| KR100522179B1 (ko) * | 2003-02-26 | 2005-10-18 | 주식회사 애트랩 | 임피던스 교정기능을 갖는 반도체 장치 |

-

2005

- 2005-02-01 KR KR1020050009103A patent/KR100652398B1/ko not_active Expired - Fee Related

-

2006

- 2006-02-01 US US11/344,592 patent/US7471109B2/en active Active

- 2006-02-01 JP JP2006024716A patent/JP5000144B2/ja not_active Expired - Lifetime

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS56103524A (en) * | 1979-12-21 | 1981-08-18 | Philips Nv | Variable impedance circuit |

| JP2000269782A (ja) * | 1999-03-18 | 2000-09-29 | Hitachi Ltd | Mosトランジスタ抵抗回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5000144B2 (ja) | 2012-08-15 |

| US20060250156A1 (en) | 2006-11-09 |

| KR20060088270A (ko) | 2006-08-04 |

| KR100652398B1 (ko) | 2006-12-01 |

| US7471109B2 (en) | 2008-12-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1980059B (zh) | 电流限制双向mosfet开关 | |

| US7961031B2 (en) | Semiconductor switch circuit | |

| US7733182B2 (en) | Hybrid class AB super follower | |

| US20200280309A1 (en) | High voltage gate driver current source | |

| US10498333B1 (en) | Adaptive gate buffer for a power stage | |

| US11994887B2 (en) | Low dropout linear regulator with high power supply rejection ratio | |

| US20030030482A1 (en) | Semiconductor integrated circuit and reference voltage generating circuit employing it | |

| US7245165B2 (en) | Turn-on bus transmitter with controlled slew rate | |

| US6437638B1 (en) | Linear two quadrant voltage regulator | |

| US11442480B2 (en) | Power supply circuit alternately switching between normal operation and sleep operation | |

| JP3806011B2 (ja) | 電圧検出回路 | |

| US6501252B2 (en) | Power supply circuit | |

| US20080169875A1 (en) | Level-Shifting Buffer | |

| US8008951B2 (en) | High voltage switch utilizing low voltage MOS transistors with high voltage breakdown isolation junctions | |

| US7330056B1 (en) | Low power CMOS LVDS driver | |

| US20240385636A1 (en) | Circuit for generating a reference voltage | |

| US10601416B2 (en) | Gate drive device | |

| JP5000144B2 (ja) | 出力インピーダンス回路及びこれを適用した出力バッファ回路 | |

| US6433636B2 (en) | Operational amplifier designed to have increased output range | |

| KR100846880B1 (ko) | 높고 그리고 넓은 동작 전압 범위를 위한 바이어스 회로를구비한 게이트 드라이버 출력 단 | |

| US6504416B1 (en) | High linearity, low power voltage controlled resistor | |

| JP2006025085A (ja) | Cmos駆動回路 | |

| JP2008219664A (ja) | スイッチング回路 | |

| CN116126065B (zh) | 一种稳压电源及稳压控制方法 | |

| JP2010166359A (ja) | 電流制限回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20080201 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20080620 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090129 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111004 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120110 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120330 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120417 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120516 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5000144 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150525 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |