JP2005295315A - 逐次比較型a/d変換器およびコンパレータ - Google Patents

逐次比較型a/d変換器およびコンパレータ Download PDFInfo

- Publication number

- JP2005295315A JP2005295315A JP2004109077A JP2004109077A JP2005295315A JP 2005295315 A JP2005295315 A JP 2005295315A JP 2004109077 A JP2004109077 A JP 2004109077A JP 2004109077 A JP2004109077 A JP 2004109077A JP 2005295315 A JP2005295315 A JP 2005295315A

- Authority

- JP

- Japan

- Prior art keywords

- input

- inverter

- transistors

- voltage

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000003990 capacitor Substances 0.000 claims description 78

- 238000006243 chemical reaction Methods 0.000 claims description 15

- 230000007423 decrease Effects 0.000 claims description 4

- 239000004065 semiconductor Substances 0.000 abstract description 3

- 238000000034 method Methods 0.000 description 8

- 238000010586 diagram Methods 0.000 description 6

- 238000010168 coupling process Methods 0.000 description 3

- 238000005859 coupling reaction Methods 0.000 description 3

- 230000008878 coupling Effects 0.000 description 2

- 230000003111 delayed effect Effects 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/34—Analogue value compared with reference values

- H03M1/38—Analogue value compared with reference values sequentially only, e.g. successive approximation type

- H03M1/46—Analogue value compared with reference values sequentially only, e.g. successive approximation type with digital/analogue converter for supplying reference values to converter

- H03M1/466—Analogue value compared with reference values sequentially only, e.g. successive approximation type with digital/analogue converter for supplying reference values to converter using switched capacitors

- H03M1/468—Analogue value compared with reference values sequentially only, e.g. successive approximation type with digital/analogue converter for supplying reference values to converter using switched capacitors in which the input S/H circuit is merged with the feedback DAC array

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Theoretical Computer Science (AREA)

- Analogue/Digital Conversion (AREA)

- Manipulation Of Pulses (AREA)

Abstract

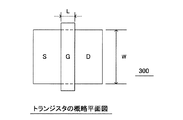

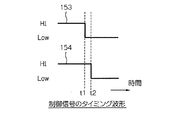

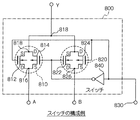

【解決手段】アナログ信号電圧を比較する比較電圧を生成する比較電圧生成回路210と、比較電圧とアナログ信号電圧とを逐次比較して比較結果を出力するコンパレータ220と、比較結果をバス232に接続された出力レジスタ236に出力するとともに、比較結果に応じて決定した比較電圧値を比較電圧生成回路210に供給する比較結果処理回路230とを備え、コンパレータ220のPchTrのドライブ能力がPchTr 101>PchTr 151, PchTr 102>PchTr 152に設定され、ドライブ能力が大きなPchTr 101およびPchTr 102のオン/オフ切替タイミングと、ドライブ能力の小さなPchTr 151およびPchTr 152のオン/オフ切替タイミングがそれぞれゲートに接続した制御入力153,154により変えられている。

【選択図】図1

Description

103,104 インバータ

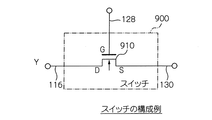

107,109,111,113,115,123 スイッチ

117,118,119,120,121,129 キャパシタ

210 比較電圧生成回路(D/A)

220 コンパレータ

Claims (12)

- アナログ入力電圧と比較電圧とを逐次比較して比較結果を生成する比較手段を備えた逐次比較型A/D変換器において、前記比較手段は、

前記アナログ入力電圧と前記比較電圧とが順次入力される第1のインバータと、

該第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、

該キャパシタの他方の電極に接続された第2のインバータと、

前記第1のインバータの入出力端に並列に接続された第1の帰還スイッチと、

前記第2のインバータの入出力端に並列に接続された第2の帰還スイッチとを含み、

前記第1の帰還スイッチは、前記第1のインバータの入出力端に互いに並列に接続した第1および第2のトランジスタを含み、前記第1のトランジスタは前記第2のトランジスタよりもドライブ能力が大きく形成され、

前記第2の帰還スイッチはさらに、前記第2のインバータの入出力端に互いに並列に接続した第3および第4のトランジスタを含み、前記第3のトランジスタは前記第4のトランジスタよりもドライブ能力が大きく形成され、

前記第1および第3のトランジスタのゲートは共に接続されて第1の制御信号が入力される第1の制御入力端子に接続され、

前記第2および第4のトランジスタのゲートは共に接続されて第2の制御信号が入力される第2の制御入力端子に接続され、

逐次比較動作を行う際に、ドライブ能力が大きい前記第1および第3のトランジスタのオン/オフ切替タイミングと、ドライブ能力が小さい前記第2および第4のトランジスタのオン/オフ切替タイミングとを異ならせて、前記アナログ入力電圧と前記基準電圧との比較を行うことを特徴とする逐次比較型A/D変換器。 - 請求項1に記載の逐次比較型A/D変換器において、前記比較手段は、前記第1および第3のトランジスタをオン状態からオフに切り替えた後に、前記第2および第4のトランジスタをオン状態からオフに切り替えることを特徴とする逐次比較型A/D変換器。

- 請求項1に記載の逐次比較型A/D変換器において、前記第1および第3のトランジスタのゲート幅とゲート長との比(W/L比)が、前記第2および第4のトランジスタのゲート幅とゲート長との比(W/L比)よりも大きく形成されていることにより、前記ドライブ能力が異なることを特徴とする逐次比較型A/D変換器。

- 請求項1に記載の逐次比較型A/D変換器において、該変換器は、CMOS回路にて形成されていることを特徴とする逐次比較型A/D変換器。

- 請求項1に記載の逐次比較型A/D変換器において、該変換器は、前記比較電圧を生成する比較電圧生成手段を備え、該比較電圧生成手段は、

前記アナログ入力電圧と基準電圧とを前記比較電圧に応じてサンプルする複数のスイッチと、

前記複数のスイッチの出力にそれぞれ対応して一方の電極が接続され、前記基準電圧および前記比較電圧を順次ホールドする複数のキャパシタであって、MSBからLSBにかけてそれぞれ容量が小さくなるように重み付けされて接続している複数のキャパシタとを含み、

前記複数のキャパシタの他方の電極が共通に接続されて該接続を該比較電圧生成手段の出力として前記比較電圧を出力し、

前記複数のスイッチは、前記MSBからLSBにかけて、前記複数のキャパシタの容量に比例して、それぞれスイッチサイズが小さくなるように形成されていることを特徴とする逐次比較型A/D変換器。 - アナログ入力電圧と比較電圧とを逐次比較して比較結果を生成する比較手段を備えた逐次比較型A/D変換器において、前記比較手段は、

前記アナログ入力電圧と前記比較電圧とが順次入力される第1のインバータと、

該第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、

該キャパシタの他方の電極に接続された第2のインバータと、

前記第1のインバータの入出力端に並列に接続された第1の帰還スイッチと、

前記第2のインバータの入出力端に並列に接続された第2の帰還スイッチとを含み、

前記第1の帰還スイッチは、前記第1のインバータの入出力端に互いに並列に接続した第1および第2のトランジスタを含み、前記第1のトランジスタは前記第2のトランジスタよりもドライブ能力が大きく形成され、

前記第2の帰還スイッチはさらに、前記第2のインバータの入出力端に互いに並列に接続した第3および第4のトランジスタを含み、前記第3のトランジスタは前記第4のトランジスタよりもドライブ能力が大きく形成され、

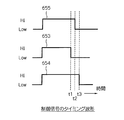

前記第1のトランジスタのゲートは第1の制御信号が入力される第1の制御入力端子に接続され、

前記第3のトランジスタのゲートは第2の制御信号が入力される第2の制御入力端子に接続され、

前記第2および第4のトランジスタのゲートは共に接続されて第3の制御信号が入力される第3の制御入力端子に接続され、

逐次比較動作を行う際に、ドライブ能力が大きい前記第1および第3のトランジスタのオン/オフ切替タイミングと、ドライブ能力が小さい前記第2および第4のトランジスタのオン/オフ切替タイミングとを異ならせて、さらに、第1のトランジスタと第2のトランジスタとのオン/オフ切替タイミングを異ならせて、前記アナログ入力電圧と前記基準電圧との比較を行うことを特徴とする逐次比較型A/D変換器。 - 請求項6に記載の逐次比較型A/D変換器において、前記比較手段は、前記第1のトランジスタをオン状態からオフに切り替えた後、第3のトランジスタをオン状態からオフに切り替え、その後に、前記第2および第4のトランジスタをオン状態からオフに切り替えることを特徴とする逐次比較型A/D変換器。

- 請求項6に記載の逐次比較型A/D変換器において、前記第1および第3のトランジスタのゲート幅とゲート長との比(W/L比)が、前記第2および第4のトランジスタのゲート幅とゲート長との比(W/L比)よりも大きく形成されていることにより、前記ドライブ能力が異なることを特徴とする逐次比較型A/D変換器。

- 請求項6に記載の逐次比較型A/D変換器において、該変換器は、CMOS回路にて形成されていることを特徴とする逐次比較型A/D変換器。

- 請求項6に記載の逐次比較型A/D変換器において、該変換器は、前記比較電圧を生成する比較電圧生成手段を備え、該比較電圧生成手段は、

前記アナログ入力電圧と基準電圧とを前記比較電圧に応じてサンプルする複数のスイッチと、

前記複数のスイッチの出力にそれぞれ対応して一方の電極が接続され、前記基準電圧および前記比較電圧を順次ホールドする複数のキャパシタであって、MSBからLSBにかけてそれぞれ容量が小さくなるように重み付けされて接続している複数のキャパシタとを含み、

前記複数のキャパシタの他方の電極が共通に接続されて該接続を該比較電圧生成手段の出力として前記比較電圧を出力し、

前記複数のスイッチは、前記MSBからLSBにかけて、前記複数のキャパシタの容量に比例して、それぞれスイッチサイズが小さくなるように形成されていることを特徴とする逐次比較型A/D変換器。 - アナログ入力電圧と比較電圧とを逐次比較するコンパレータにおいて、

前記アナログ入力電圧と前記比較電圧とが順次入力される第1のインバータと、

該第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、

該キャパシタの他方の電極に接続された第2のインバータと、

前記第1のインバータの入出力端に並列に接続された第1の帰還スイッチと、

前記第2のインバータの入出力端に並列に接続された第2の帰還スイッチとを含み、

前記第1の帰還スイッチは、前記第1のインバータの入出力端に互いに並列に接続した第1および第2のトランジスタを含み、前記第1のトランジスタは前記第2のトランジスタよりもドライブ能力が大きく形成され、

前記第2の帰還スイッチはさらに、前記第2のインバータの入出力端に互いに並列に接続した第3および第4のトランジスタを含み、前記第3のトランジスタは前記第4のトランジスタよりもドライブ能力が大きく形成され、

前記第1および第3のトランジスタのゲートは共に接続されて第1の制御信号が入力される第1の制御入力端子に接続され、

前記第2および第4のトランジスタのゲートは共に接続されて第2の制御信号が入力される第2の制御入力端子に接続され、

逐次比較動作を行う際に、ドライブ能力が大きい前記第1および第3のトランジスタのオン/オフ切替タイミングと、ドライブ能力が小さい前記第2および第4のトランジスタのオン/オフ切替タイミングとを異ならせて、前記アナログ入力電圧と前記基準電圧との比較を行うことを特徴とするコンパレータ。 - アナログ入力電圧と比較電圧とを逐次比較するコンパレータにおいて、

前記アナログ入力電圧と前記比較電圧とが順次入力される第1のインバータと、

該第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、

該キャパシタの他方の電極に接続された第2のインバータと、

前記第1のインバータの入出力端に並列に接続された第1の帰還スイッチと、

前記第2のインバータの入出力端に並列に接続された第2の帰還スイッチとを含み、

前記第1の帰還スイッチは、前記第1のインバータの入出力端に互いに並列に接続した第1および第2のトランジスタを含み、前記第1のトランジスタは前記第2のトランジスタよりもドライブ能力が大きく形成され、

前記第2の帰還スイッチはさらに、前記第2のインバータの入出力端に互いに並列に接続した第3および第4のトランジスタを含み、前記第3のトランジスタは前記第4のトランジスタよりもドライブ能力が大きく形成され、

前記第1のトランジスタのゲートは第1の制御信号が入力される第1の制御入力端子に接続され、

前記第3のトランジスタのゲートは第2の制御信号が入力される第2の制御入力端子に接続され、

前記第2および第4のトランジスタのゲートは共に接続されて第3の制御信号が入力される第3の制御入力端子に接続され、

逐次比較動作を行う際に、ドライブ能力が大きい前記第1および第3のトランジスタのオン/オフ切替タイミングと、ドライブ能力が小さい前記第2および第4のトランジスタのオン/オフ切替タイミングとを異ならせて、さらに、第1のトランジスタと第2のトランジスタとのオン/オフ切替タイミングを異ならせて、前記アナログ入力電圧と前記基準電圧との比較を行うことを特徴とするコンパレータ。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109077A JP2005295315A (ja) | 2004-04-01 | 2004-04-01 | 逐次比較型a/d変換器およびコンパレータ |

| US11/033,377 US7154423B2 (en) | 2004-04-01 | 2005-01-12 | Successive approximation A/D converter comparing analog input voltage to reference voltages and a comparator for use therein |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004109077A JP2005295315A (ja) | 2004-04-01 | 2004-04-01 | 逐次比較型a/d変換器およびコンパレータ |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005295315A true JP2005295315A (ja) | 2005-10-20 |

| JP2005295315A5 JP2005295315A5 (ja) | 2006-09-28 |

Family

ID=34709187

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004109077A Pending JP2005295315A (ja) | 2004-04-01 | 2004-04-01 | 逐次比較型a/d変換器およびコンパレータ |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7154423B2 (ja) |

| JP (1) | JP2005295315A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPWO2021005654A1 (ja) * | 2019-07-05 | 2021-01-14 |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7315272B2 (en) * | 2005-10-27 | 2008-01-01 | Industrial Technology Research Institute | Inverter-based flash analog-to-digital converter using floating resistor ladder |

| KR100775838B1 (ko) * | 2006-03-23 | 2007-11-13 | 엘지전자 주식회사 | 플라즈마 디스플레이 장치 |

| US20080061842A1 (en) * | 2006-09-07 | 2008-03-13 | Micron Technology, Inc. | Circuit and method for detecting timed amplitude reduction of a signal relative to a threshold voltage |

| US7560959B2 (en) * | 2006-09-18 | 2009-07-14 | Micron Technology, Inc. | Absolute value peak differential voltage detector circuit and method |

| MY149749A (en) * | 2010-12-16 | 2013-10-14 | Mimos Berhad | Dual-function successive approximation analog to digital converter (sa-adc) |

| US8552897B1 (en) * | 2012-03-22 | 2013-10-08 | Analog Devices, Inc. | Reference circuit suitable for use with an analog to digital converter and an analog to digital converter including such a reference circuit |

| CN114586286A (zh) * | 2019-12-27 | 2022-06-03 | 英特尔公司 | 模数转换器及校准模数转换器的方法、校准管线式模数转换器的方法、接收器、基站和移动设备 |

| KR102898433B1 (ko) | 2021-05-24 | 2025-12-09 | 삼성전자 주식회사 | 아날로그-디지털 변환기 및 그의 동작 방법 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH043522A (ja) * | 1990-04-20 | 1992-01-08 | Hitachi Ltd | アナログ集積回路 |

| JPH04222120A (ja) * | 1990-12-21 | 1992-08-12 | Toshiba Corp | 逐次比較型アナログ・デジタル変換器 |

| JPH05335955A (ja) * | 1992-06-03 | 1993-12-17 | Mitsubishi Electric Corp | アナログ/デジタル変換装置 |

| JP2002374169A (ja) * | 2001-06-13 | 2002-12-26 | Matsushita Electric Ind Co Ltd | 逐次比較型a/d変換器 |

| JP2004007131A (ja) * | 2002-05-31 | 2004-01-08 | Oki Electric Ind Co Ltd | チョッパ型コンパレータ |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5421102A (en) * | 1977-07-18 | 1979-02-17 | Toshiba Corp | Semiconductor device circuit |

| JPS5421152A (en) * | 1977-07-18 | 1979-02-17 | Toshiba Corp | Comparison circuit |

| US4348658A (en) * | 1980-05-09 | 1982-09-07 | Motorola, Inc. | Analog-to-digital converter using half range technique |

| US4323887A (en) * | 1980-10-23 | 1982-04-06 | National Semiconductor Corporation | CMOS Analog to digital converter with selectable voltage follower buffering |

| US4641130A (en) * | 1985-03-29 | 1987-02-03 | Rca Corporation | Analog-to-digital converter with scaling of input signal |

| JPH04290310A (ja) * | 1991-03-19 | 1992-10-14 | Fujitsu Ltd | アナログ・デジタルコンバータ |

| US5247299A (en) * | 1992-06-02 | 1993-09-21 | Hewlett-Packard Company | Successive approximation A/D converter correcting for charge injection offset |

| US5570091A (en) * | 1993-09-21 | 1996-10-29 | Yamaha Corporation | Analog-to-digital converter |

| EP0662757A2 (en) * | 1994-01-05 | 1995-07-12 | Texas Instruments Incorporated | Analog-digital conversion system with automatic offset tracking and correcting circuit and method of operation |

| JPH08195655A (ja) | 1995-01-17 | 1996-07-30 | Mitsubishi Electric Corp | チョッパ型電圧比較器 |

| US5539695A (en) * | 1995-01-23 | 1996-07-23 | Solidas Corporation | Fast access multi-bit random access memory |

| IES80452B2 (en) * | 1997-01-22 | 1998-07-29 | Univ Cork | Reduction of comparator power requirement in a switched capacitor adc |

| US6020841A (en) * | 1998-01-20 | 2000-02-01 | Microchip Technology Incorporated | Driver circuit for low voltage operation of a successive approximation register (SAR) analog to digital (A/D) converter and method therefor |

| EP1001534A2 (en) * | 1998-10-07 | 2000-05-17 | Yozan Inc. | Analog to digital converter |

| US6714151B2 (en) * | 2002-06-21 | 2004-03-30 | Fujitsu Limited | A/D converter |

| US6950052B2 (en) * | 2003-06-03 | 2005-09-27 | Silicon Labs Cp, Inc. | Noise cancellation in a single ended SAR converter |

-

2004

- 2004-04-01 JP JP2004109077A patent/JP2005295315A/ja active Pending

-

2005

- 2005-01-12 US US11/033,377 patent/US7154423B2/en not_active Expired - Lifetime

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH043522A (ja) * | 1990-04-20 | 1992-01-08 | Hitachi Ltd | アナログ集積回路 |

| JPH04222120A (ja) * | 1990-12-21 | 1992-08-12 | Toshiba Corp | 逐次比較型アナログ・デジタル変換器 |

| JPH05335955A (ja) * | 1992-06-03 | 1993-12-17 | Mitsubishi Electric Corp | アナログ/デジタル変換装置 |

| JP2002374169A (ja) * | 2001-06-13 | 2002-12-26 | Matsushita Electric Ind Co Ltd | 逐次比較型a/d変換器 |

| JP2004007131A (ja) * | 2002-05-31 | 2004-01-08 | Oki Electric Ind Co Ltd | チョッパ型コンパレータ |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPWO2021005654A1 (ja) * | 2019-07-05 | 2021-01-14 | ||

| WO2021005654A1 (ja) * | 2019-07-05 | 2021-01-14 | サンケン電気株式会社 | A/d変換回路 |

| US11689211B2 (en) | 2019-07-05 | 2023-06-27 | Sanken Electric Co., Ltd. | Analog-to-digital converter |

| JP7380688B2 (ja) | 2019-07-05 | 2023-11-15 | サンケン電気株式会社 | A/d変換回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7154423B2 (en) | 2006-12-26 |

| US20050146456A1 (en) | 2005-07-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN111865320B (zh) | 一种低功耗逐次逼近型模数转换器 | |

| US8089388B2 (en) | Folding analog-to-digital converter | |

| US20100060500A1 (en) | Analog/Digital Converter Assembly and Corresponding Method | |

| KR0173858B1 (ko) | 아날로그-디지털 변환방법 및 장치 | |

| CN102204107A (zh) | 逐次逼近型ad转换电路 | |

| US6229472B1 (en) | A/D converter | |

| US20090201051A1 (en) | Sample-and-Hold Circuit and Pipeline Ad Converter Using Same | |

| JP2019097121A (ja) | ラッチドコンパレータ | |

| US6563449B2 (en) | Successive comparison analog-to-digital converter | |

| WO2007088175A1 (en) | A/d converter comprising a voltage comparator device | |

| US20090045995A1 (en) | Comparator and analog-to-digital converter using the same | |

| US20060158362A1 (en) | D/A conversion circuit and A/D conversion circuit | |

| JP2005295315A (ja) | 逐次比較型a/d変換器およびコンパレータ | |

| US7030791B2 (en) | A/D conversion device having input level shift and output correction function | |

| JPWO2016203522A1 (ja) | 逐次比較型a/d変換装置 | |

| US8766844B2 (en) | Analog-digital converter | |

| JP4424406B2 (ja) | 直並列型アナログ/デジタル変換器及びアナログ/デジタル変換方法 | |

| US6271691B1 (en) | Chopper type voltage comparison circuit | |

| JP2009246752A (ja) | パイプラインa/d変換器 | |

| US7030802B2 (en) | AD converter | |

| US6927723B2 (en) | A/D converter and A/D conversion method | |

| JP4639162B2 (ja) | アナログ・ディジタル変換器 | |

| JP3993819B2 (ja) | Ad変換器 | |

| JP2018064188A (ja) | 逐次比較型ad変換装置 | |

| JP2004260263A (ja) | Ad変換器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060811 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060811 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080925 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080930 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081201 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20081218 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20090323 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20090609 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090909 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20090917 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20091127 |