JP2005293574A - ホールをもつシステムメモリアドレスをサポートするデータ処理システム及びコンピュータプログラム - Google Patents

ホールをもつシステムメモリアドレスをサポートするデータ処理システム及びコンピュータプログラム Download PDFInfo

- Publication number

- JP2005293574A JP2005293574A JP2005076077A JP2005076077A JP2005293574A JP 2005293574 A JP2005293574 A JP 2005293574A JP 2005076077 A JP2005076077 A JP 2005076077A JP 2005076077 A JP2005076077 A JP 2005076077A JP 2005293574 A JP2005293574 A JP 2005293574A

- Authority

- JP

- Japan

- Prior art keywords

- logical

- memory

- physical

- physical address

- address range

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/0292—User address space allocation, e.g. contiguous or non contiguous base addressing using tables or multilevel address translation means

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/10—Address translation

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Memory System Of A Hierarchy Structure (AREA)

- Memory System (AREA)

- Executing Machine-Instructions (AREA)

Abstract

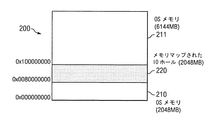

【解決手段】論理区画をサポートするように構成されたプロセッサにより稼動されるオペレーティング・システムのシステムメモリに対して割り振られた第1の物理アドレス範囲を仮想化して、第1の論理アドレス範囲を生成する。第2の物理アドレス範囲を仮想化して、第2の論理アドレス範囲を生成する。第1及び第2の物理アドレス範囲は不連続である。第1及び第2の物理アドレス範囲の仮想化は、第1の論理アドレス範囲及び第2の論理アドレス範囲が連続するようにされる。第1の物理アドレス範囲及び第2の物理アドレス範囲の中間にあるメモリマップされた入力/出力物理アドレス範囲を仮想化して、第3の論理アドレス範囲を生成する。第3の論理アドレス範囲の最下部の論理アドレスは、第1及び第2の論理アドレス範囲のそれぞれの最上部の論理アドレスを超える。

【選択図】図1

Description

102、104:プロセッサ

106:システムバス

108:メモリコントローラ/キャッシュ

109:ローカルメモリ

110:I/Oブリッジ

112:I/Oバス

114、122、124:PCIバスブリッジ

115:ファームウェア

116、126、128:PCIバス

118:モデム

120:ネットワーク・アダプタ

130:グラフィックス・アダプタ

132:ハードディスク

Claims (20)

- ホールをもつメモリアドレスをサポートするための方法であって、コンピュータにより実施されるステップからなり、

論理区画をサポートするように構成されたプロセッサにより稼動されるオペレーティング・システムのシステムメモリに対して割り振られた第1の物理アドレス範囲を仮想化して、第1の論理アドレス範囲を生成し、

前記オペレーティング・システムのシステムメモリに対して割り振られた、前記第1の物理アドレス範囲とは不連続の第2の物理アドレス範囲を仮想化して、前記第1の論理アドレス範囲に連続する第2の論理アドレス範囲を生成し、

前記第1及び第2の物理アドレス範囲の中間にあるメモリマップされた入力/出力物理アドレス範囲を仮想化して、第3の論理アドレス範囲を生成する、

ステップを含み、

前記第3の論理アドレス範囲の最下部の論理アドレスが、前記第1及び第2の論理アドレス範囲のそれぞれの最上部の論理アドレスを超えることを特徴とする方法。 - 前記第1の物理アドレス範囲と、前記第2の物理アドレス範囲と、前記メモリマップされた入力/出力物理アドレス範囲とを仮想化するステップが、物理アドレス及び対応する論理アドレスを定義するマッピング・テーブルを維持することを含む請求項1に記載の方法。

- 前記マッピング・テーブルを維持することが、さらに、該マッピング・テーブルを、前記第1及び第2の物理アドレス範囲の1つに割り振られた、該第1及び第2の物理アドレス範囲にアクセスするオペレーティング・システムには利用不可能な物理アドレス・スペースに維持することを含む請求項2に記載の方法。

- 前記第3の論理アドレス範囲が、前記第1の論理アドレス範囲及び前記第2の論理アドレス範囲と不連続である請求項1に記載の方法。

- 前記第1の物理アドレス範囲及び前記第2物理アドレス範囲の少なくとも1つの一部を、論理区画管理ソフトウェア層に割り振ることをさらに含む請求項1に記載の方法。

- 前記メモリマップされた入力/出力物理アドレス範囲が、キャッシュ禁止アドレスに対して割り振られる請求項1に記載の方法。

- 不連続物理メモリ範囲を連続論理アドレス範囲に仮想化するためのコンピュータ可読媒体におけるコンピュータプログラムであって、

システムメモリに対して割り振られたメモリデバイスの第1及び第2の不連続物理アドレス範囲、及び、前記第1及び第2の物理アドレス範囲の中間にあるメモリマップされた入力/出力物理アドレス範囲を含む第3の物理アドレス範囲のための論理対物理メモリアドレス変換を格納する第1の命令を含み、前記論理対物理メモリアドレス変換により与えられる前記第3の物理アドレス範囲の最下部の論理アドレスが、該論理対物理メモリアドレス変換により与えられる、前記第1及び第2の不連続物理アドレス範囲に対応する前記第1及び第2の論理アドレス範囲の最上部より大きいものであり、

前記第1の命令の実行に応答して、論理アドレスを対応する物理アドレスに変換するための第2の命令、

を含むコンピュータプログラム。 - 前記論理対物理メモリの変換が、前記メモリデバイスにアクセスするオペレーティング・システムには利用不可能であるマッピング・テーブルに格納された請求項7に記載のコンピュータプログラム。

- 前記マッピング・テーブルが、前記第1及び第2の物理アドレス範囲の少なくとも1つに維持された請求項8に記載のコンピュータプログラム。

- 前記第2の命令が、論理区画機能を与える請求項7に記載のコンピュータプログラム。

- 前記第2の命令が、前記第1及び第2の物理アドレス範囲の少なくとも1つに維持された請求項7に記載のコンピュータプログラム。

- 前記第2の命令が、データ処理システムの入力及び出力装置をもつオペレーティング・システムとインターフェースする請求項7に記載のコンピュータプログラム。

- 前記第2の命令が、前記第1及び第2の論理アドレス範囲を含む連続論理アドレス範囲を、前記オペレーティング・システムに提示する請求項12に記載のコンピュータプログラム。

- 前記第3の物理アドレス範囲が、キャッシュ禁止のメモリマップされた入力/出力アドレスに対して割り振られた請求項8に記載のコンピュータプログラム。

- 不連続のシステムメモリアレイをサポートするデータ処理システムであって、

第1及び第2のそれぞれの物理アドレス範囲を有するシステムメモリに対して割り振られた第1及び第2の不連続物理メモリアレイと、前記第1及び第2の物理アドレス範囲の中間に第3の物理アドレス範囲を有する第3の物理メモリアレイと、データ・セットと、命令のセットとを含むメモリ、及び

論理区画をサポートするように構成されたプロセッサ、

を備え、前記プロセッサには、前記第1及び第2の不連続メモリアレイへのアクセスに対して、前記命令の実行に応答して、連続論理アドレス範囲が提示されることを特徴とするデータ処理システム。 - 前記データ・セットが、論理対物理メモリアドレス変換を定義するマッピング・テーブルである請求項15に記載のデータ処理システム。

- 前記命令のセットが、論理区画管理を与える請求項15に記載のデータ処理システム。

- 前記データ・セットが、前記第1及び第2の物理アドレス範囲の少なくとも1つにおけるメモリに維持された請求項15に記載のデータ処理システム。

- 前記命令のセットが、前記第1及び第2の物理アドレス範囲の少なくとも1つにおけるメモリに維持された請求項15に記載のデータ処理システム。

- 第2の論理アドレス範囲が前記第3の物理アドレス範囲にマップされて、前記第2の論理アドレス範囲の最下部の論理アドレスは、前記連続論理アドレス範囲の最上部の論理アドレスより大きいものである請求項15に記載のデータ処理システム。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/814,733 US7426625B2 (en) | 2004-03-31 | 2004-03-31 | Data processing system and computer program product for support of system memory addresses with holes |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005293574A true JP2005293574A (ja) | 2005-10-20 |

| JP4143616B2 JP4143616B2 (ja) | 2008-09-03 |

Family

ID=35049895

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005076077A Expired - Fee Related JP4143616B2 (ja) | 2004-03-31 | 2005-03-16 | ホールをもつメモリアドレスをサポートするための方法及びコンピュータプログラム |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7426625B2 (ja) |

| JP (1) | JP4143616B2 (ja) |

| KR (1) | KR100773001B1 (ja) |

| CN (1) | CN100385420C (ja) |

| TW (1) | TWI340898B (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010186465A (ja) * | 2008-12-08 | 2010-08-26 | Nvidia Corp | ヘテロジニアス処理ユニットのための集中デバイス仮想化レイヤ |

Families Citing this family (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007141066A (ja) * | 2005-11-21 | 2007-06-07 | Toshiba Corp | 情報処理装置およびメモリアドレス空間割り当て方法 |

| US7685401B2 (en) * | 2006-12-27 | 2010-03-23 | Intel Corporation | Guest to host address translation for devices to access memory in a partitioned system |

| US8141093B2 (en) * | 2007-11-15 | 2012-03-20 | International Business Machines Corporation | Management of an IOV adapter through a virtual intermediary in an IOV management partition |

| CN101203019B (zh) * | 2007-11-20 | 2011-01-05 | 中兴通讯股份有限公司 | 通讯设备逻辑地址与物理地址的互换方法及装置 |

| US8209554B2 (en) * | 2009-02-23 | 2012-06-26 | International Business Machines Corporation | Applying power management on a partition basis in a multipartitioned computer system |

| US9195581B2 (en) * | 2011-07-01 | 2015-11-24 | Apple Inc. | Techniques for moving data between memory types |

| US20130219146A1 (en) * | 2012-02-16 | 2013-08-22 | Micron Technology, Inc. | Method, device and system for a configurable address space for non-volatile memory |

| US20130219105A1 (en) * | 2012-02-16 | 2013-08-22 | Micron Technology, Inc. | Method, device and system for caching for non-volatile memory device |

| US20150310787A1 (en) * | 2013-10-21 | 2015-10-29 | Pixtronix, Inc. | Ems displays incorporating conductive edge seals and methods for manufacturing thereof |

| US10114752B2 (en) | 2014-06-27 | 2018-10-30 | International Business Machines Corporation | Detecting cache conflicts by utilizing logical address comparisons in a transactional memory |

| US20150378904A1 (en) * | 2014-06-27 | 2015-12-31 | International Business Machines Corporation | Allocating read blocks to a thread in a transaction using user specified logical addresses |

| US10095417B1 (en) * | 2016-12-13 | 2018-10-09 | EMC IP Holding Company LLC | Method and system for improving flash storage read performance in partially programmed blocks |

| US10289550B1 (en) | 2016-12-30 | 2019-05-14 | EMC IP Holding Company LLC | Method and system for dynamic write-back cache sizing in solid state memory storage |

| US10338983B2 (en) | 2016-12-30 | 2019-07-02 | EMC IP Holding Company LLC | Method and system for online program/erase count estimation |

| US11069418B1 (en) | 2016-12-30 | 2021-07-20 | EMC IP Holding Company LLC | Method and system for offline program/erase count estimation |

| US10403366B1 (en) | 2017-04-28 | 2019-09-03 | EMC IP Holding Company LLC | Method and system for adapting solid state memory write parameters to satisfy performance goals based on degree of read errors |

| US10290331B1 (en) | 2017-04-28 | 2019-05-14 | EMC IP Holding Company LLC | Method and system for modulating read operations to support error correction in solid state memory |

| US11099980B2 (en) * | 2018-05-09 | 2021-08-24 | International Business Machines Corporation | Host aware update write |

Family Cites Families (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0658649B2 (ja) * | 1985-10-28 | 1994-08-03 | 株式会社日立製作所 | 仮想記憶装置における領域管理方法 |

| JPS6419446U (ja) | 1987-07-21 | 1989-01-31 | ||

| JPH0813814B2 (ja) | 1988-10-18 | 1996-02-14 | ダイセル化学工業株式会社 | 縮合複素環化合物の製造法 |

| US5117350A (en) * | 1988-12-15 | 1992-05-26 | Flashpoint Computer Corporation | Memory address mechanism in a distributed memory architecture |

| JPH02189655A (ja) | 1989-01-18 | 1990-07-25 | Fujitsu Ltd | 情報処理装置の絶対アドレス変換方式 |

| US5297270A (en) * | 1989-11-13 | 1994-03-22 | Zenith Data Systems Corporation | Programmable cache memory which associates each section of main memory to be cached with a status bit which enables/disables the caching accessibility of the particular section, and with the capability of functioning with memory areas of varying size |

| JPH03288267A (ja) | 1990-04-04 | 1991-12-18 | Toshiba Corp | 医用画像データ伝送方式 |

| WO1994014119A1 (en) * | 1992-12-07 | 1994-06-23 | Raxco, Incorporated | Apparatus and method for moving open files |

| EP0608622A1 (en) * | 1993-01-29 | 1994-08-03 | International Business Machines Corporation | Multiprocessor system with multilevel caches |

| EP0610583A1 (en) | 1993-02-08 | 1994-08-17 | International Business Machines Corporation | Multizone relocation facility computer memory system |

| US5548746A (en) * | 1993-11-12 | 1996-08-20 | International Business Machines Corporation | Non-contiguous mapping of I/O addresses to use page protection of a process |

| JP3505231B2 (ja) | 1994-09-30 | 2004-03-08 | 株式会社東芝 | コンピュータシステム |

| JP3540388B2 (ja) | 1994-09-30 | 2004-07-07 | 株式会社東芝 | コンピュータシステム |

| SG45399A1 (en) | 1994-01-12 | 1998-01-16 | Sun Microsystems Inc | Logically addressable physical memory for a virtual memory computer system that support multiple page sizes |

| US5675761A (en) * | 1994-05-16 | 1997-10-07 | International Business Machines Corporation | Method and system for providing discontiguous drive support |

| JP3740195B2 (ja) | 1994-09-09 | 2006-02-01 | 株式会社ルネサステクノロジ | データ処理装置 |

| US5581768A (en) * | 1995-02-27 | 1996-12-03 | Intel Corporation | Method and apparatus for executing applications in place from write once/seldom memories |

| US6256710B1 (en) * | 1995-04-28 | 2001-07-03 | Apple Computer, Inc. | Cache management during cache inhibited transactions for increasing cache efficiency |

| JPH0922377A (ja) * | 1995-07-07 | 1997-01-21 | Ekushingu:Kk | メモリマップアドレス変換回路 |

| US6061773A (en) * | 1996-05-03 | 2000-05-09 | Digital Equipment Corporation | Virtual memory system with page table space separating a private space and a shared space in a virtual memory |

| US5819298A (en) * | 1996-06-24 | 1998-10-06 | Sun Microsystems, Inc. | File allocation tables with holes |

| US5873124A (en) * | 1997-02-06 | 1999-02-16 | Microsoft Corporation | Virtual memory scratch pages |

| US5940868A (en) * | 1997-07-18 | 1999-08-17 | Digital Equipment Corporation | Large memory allocation method and apparatus |

| US6226730B1 (en) * | 1998-06-05 | 2001-05-01 | Intel Corporation | Achieving page hit memory cycles on a virtual address reference |

| JP2000347929A (ja) | 1999-06-09 | 2000-12-15 | Nec Eng Ltd | メモリic |

| US6629111B1 (en) * | 1999-10-13 | 2003-09-30 | Cisco Technology, Inc. | Memory allocation system |

| US6505269B1 (en) * | 2000-05-16 | 2003-01-07 | Cisco Technology, Inc. | Dynamic addressing mapping to eliminate memory resource contention in a symmetric multiprocessor system |

| US6877158B1 (en) * | 2000-06-08 | 2005-04-05 | International Business Machines Corporation | Logical partitioning via hypervisor mediated address translation |

| KR100392382B1 (ko) * | 2001-07-27 | 2003-07-23 | 한국전자통신연구원 | 동적 크기 변경 및 메타 데이터 양의 최소화를 위한 논리볼륨 관리 방법 |

| US6564299B1 (en) * | 2001-07-30 | 2003-05-13 | Lsi Logic Corporation | Method and apparatus for defining cacheable address ranges |

| US7055015B2 (en) * | 2002-02-25 | 2006-05-30 | Ricoh Company, Ltd. | Information processing apparatus in which processes can reduce overhead of memory access and efficiently share memory |

| US20030188062A1 (en) * | 2002-03-28 | 2003-10-02 | Luse Paul E. | Device resource allocation |

| US6904490B2 (en) * | 2002-10-10 | 2005-06-07 | International Business Machines Corporation | Method and system of managing virtualized physical memory in a multi-processor system |

-

2004

- 2004-03-31 US US10/814,733 patent/US7426625B2/en not_active Expired - Fee Related

-

2005

- 2005-02-18 CN CNB2005100093115A patent/CN100385420C/zh not_active Expired - Fee Related

- 2005-03-10 TW TW094107357A patent/TWI340898B/zh not_active IP Right Cessation

- 2005-03-16 JP JP2005076077A patent/JP4143616B2/ja not_active Expired - Fee Related

- 2005-03-31 KR KR1020050027195A patent/KR100773001B1/ko not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010186465A (ja) * | 2008-12-08 | 2010-08-26 | Nvidia Corp | ヘテロジニアス処理ユニットのための集中デバイス仮想化レイヤ |

Also Published As

| Publication number | Publication date |

|---|---|

| CN100385420C (zh) | 2008-04-30 |

| JP4143616B2 (ja) | 2008-09-03 |

| KR20060045387A (ko) | 2006-05-17 |

| TW200602865A (en) | 2006-01-16 |

| CN1677370A (zh) | 2005-10-05 |

| KR100773001B1 (ko) | 2007-11-05 |

| US7426625B2 (en) | 2008-09-16 |

| US20050223185A1 (en) | 2005-10-06 |

| TWI340898B (en) | 2011-04-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4143616B2 (ja) | ホールをもつメモリアドレスをサポートするための方法及びコンピュータプログラム | |

| US10423435B1 (en) | Page swapping in virtual machine environment | |

| JP4288295B2 (ja) | 論理パーティションにおけるメモリへのアクセス | |

| JP6050262B2 (ja) | 仮想ディスクストレージ技術 | |

| US9183157B2 (en) | Method for creating virtual machine, a virtual machine monitor, and a virtual machine system | |

| US6877158B1 (en) | Logical partitioning via hypervisor mediated address translation | |

| US8533418B2 (en) | Memory allocation with identification of requesting loadable kernel module | |

| US8359449B2 (en) | Prioritizing virtual real memory paging based on disk capabilities | |

| EP2350833B1 (en) | Opportunistic page largification | |

| EP2581828B1 (en) | Method for creating virtual machine, virtual machine monitor and virtual machine system | |

| KR100992034B1 (ko) | 동적 논리적 파티션 기능을 갖는 컴퓨팅 환경에서의 컴퓨터메모리 관리 | |

| US7506343B2 (en) | System and method for passing information from one device driver to another | |

| CN117743205A (zh) | 用dram作为可按字节寻址存储器的缓存的方法和装置 | |

| JP2004127291A (ja) | 連続したメモリ・アドレスを提供する方法、システムおよびコンピュータ・ソフトウェア | |

| JP2024512960A (ja) | ページ移行を提供するためのシステム及び方法 | |

| US8612691B2 (en) | Assigning memory to on-chip coherence domains | |

| US20060010276A1 (en) | Isolation of input/output adapter direct memory access addressing domains | |

| US8375194B2 (en) | System and method for freeing memory | |

| JP4405435B2 (ja) | 動的なホスト区画ページ割り当てのための方法および装置 | |

| CN112817756B (zh) | 计算机可读取存储介质、内存管理单元的虚拟化方法和装置 | |

| JP3808058B2 (ja) | 複数のホストが圧縮データを記憶するメモリ・セクタの集合を共用できるようにするための装置 | |

| CN114461391A (zh) | 一种可重映射的gpu主存访问管理方法和系统 | |

| CN115934581B (zh) | 一种跨进程内存的处理方法及系统 | |

| US20070162638A1 (en) | Generic DMA memory space mapping | |

| HK1160944B (en) | Opportunistic page largification |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080311 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080418 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080610 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080616 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110620 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |