JP2005292925A - メモリコントローラ、フラッシュメモリシステム、並びに、フラッシュメモリの制御方法 - Google Patents

メモリコントローラ、フラッシュメモリシステム、並びに、フラッシュメモリの制御方法 Download PDFInfo

- Publication number

- JP2005292925A JP2005292925A JP2004103307A JP2004103307A JP2005292925A JP 2005292925 A JP2005292925 A JP 2005292925A JP 2004103307 A JP2004103307 A JP 2004103307A JP 2004103307 A JP2004103307 A JP 2004103307A JP 2005292925 A JP2005292925 A JP 2005292925A

- Authority

- JP

- Japan

- Prior art keywords

- data

- flash memory

- user data

- capacity

- additional data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 230000015654 memory Effects 0.000 title claims abstract description 168

- 238000000034 method Methods 0.000 title claims description 35

- 230000006870 function Effects 0.000 claims abstract description 34

- 230000005540 biological transmission Effects 0.000 abstract 1

- 238000010586 diagram Methods 0.000 description 16

- 230000000630 rising effect Effects 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 2

- 238000007599 discharging Methods 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000010365 information processing Effects 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Abstract

【課題】 フラッシュメモリにユーザデータと付加データとを書込む際の処理効率を向上させる。

【解決手段】 フラッシュメモリシステム1は、ホストシステム4に着脱自在に取付けられ、ホストシステム4から供給されるユーザデータとそれに対応する付加データとをフラッシュメモリ2に書込む。ここで、フラッシュメモリシステム1を構成するメモリコントローラ3は、ホストシステム4から与えられたユーザデータと、ユーザデータに対応する付加データとを保持する機能と、保持されているユーザデータ及び付加データをフラッシュメモリに転送するデータ転送機能とを備え、フラッシュメモリ2内のページに、ユーザデータと付加データとを交互に複数組書込み、且つ、ユーザデータと付加データとを連続した位置に書込む。これにより、アドレスの送信回数を減じることができる。

【選択図】 図1

【解決手段】 フラッシュメモリシステム1は、ホストシステム4に着脱自在に取付けられ、ホストシステム4から供給されるユーザデータとそれに対応する付加データとをフラッシュメモリ2に書込む。ここで、フラッシュメモリシステム1を構成するメモリコントローラ3は、ホストシステム4から与えられたユーザデータと、ユーザデータに対応する付加データとを保持する機能と、保持されているユーザデータ及び付加データをフラッシュメモリに転送するデータ転送機能とを備え、フラッシュメモリ2内のページに、ユーザデータと付加データとを交互に複数組書込み、且つ、ユーザデータと付加データとを連続した位置に書込む。これにより、アドレスの送信回数を減じることができる。

【選択図】 図1

Description

本発明は、メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びに、フラッシュメモリの制御方法に関する。

近年、メモリーカードやシリコンディスクといったメモリシステムにて使用される半導体メモリに、フラッシュメモリが広く採用されている。フラッシュメモリは、不揮発性メモリの一種である。フラッシュメモリに格納されたデータは、電力が供給されていないときでも保持されていることが要求される。

NAND型フラッシュメモリは、上記のメモリシステムで特に多く用いられるフラッシュメモリの一種である。NAND型フラッシュメモリに含まれている複数のメモリセルのそれぞれは、他のメモリセルとは独立して、論理値“1”を示すデータが格納されている消去状態から、論理値“0”を示すデータが格納されている書込状態へと変化することができる。これとは対照的に、書込状態から消去状態へと変化するときには、各メモリセルは他のメモリセルと独立して変化することができない。このときには、ブロックと称される予め定められた数のメモリセルが、全て同時に消去状態になる。

この一括消去動作は、一般的に、“ブロック消去”と称されている。NAND型フラッシュメモリに対する書込処理若しくは読出処理は、ページと称される予め定められた数のメモリセル単位で処理が行なわれる。消去処理の単位であるブロックは複数のページで構成されている。

NAND型フラッシュメモリは、各メモリセルを消去状態から書込状態に変化させる場合や、書込状態から消去状態に変化させる場合に、メモリセルに高電圧を印加して、電子の注入や排出を行なっている。この電子の注入や排出が正常に行なわれなかった場合や、メモリセルが劣化した場合に、各メモリセルが消去状態から書込状態に、又は書込状態から消去状態に正常に変化しないことがある。このような不具合を検出、訂正するため、各ページにはホストシステム側から供給されるユーザデータの他に、エラーコレクションコードが書込まれる。ここで、ユーザデータ以外の付加データ(エラーコレクションコード等)は、ページ内の冗長領域に割当てられているメモリセルに書込まれる。

例えば、下記特許文献1では、各ページの先頭から512バイトの領域を、ユーザデータ等を書込むユーザ領域に割当て、その後の領域を、エラーコレクションコード等の付加データを書込む冗長領域に割当てている。

特開2001−297038号公報

上述のように、従来は、ページ内の先頭から一定の領域を、ユーザデータ等を書込むユーザ領域に割当て、その後の領域をエラーコレクションコード等の付加データを書込む冗長領域に割当てていた。フラッシュメモリに書込まれるユーザデータは、通常、フラッシュメモリの外部に設けたバッファに保持された後、フラッシュメモリに転送される。このバッファの容量は、通常、各ページ内のユーザ領域と同一の容量に設定される。

しかし、フラッシュメモリの外部に設けるバッファの容量を、各ページ内のユーザ領域と同一にするためには、フラッシュメモリのページの容量に応じてバッファの容量を変更しなければならない。一方、フラッシュメモリの外部に設けるバッファの容量を、フラッシュメモリのページの容量と同一にしない場合は、1ページ分のデータを書込む際に、バッファからフラッシュメモリへの転送を、複数回に分けて行なわなければならない場合が生じる。1ページ分のユーザデータを複数回に分けて転送する場合には、冗長領域に書込む付加データ(エラーコレクションコード等)も複数回に分けて転送される。このユーザデータの転送と付加データ(エラーコレクションコード等)の転送は、交互に行なわれるため、アドレス等の設定を頻繁に変更しなければならず処理効率が良くなかった。

そこで、本発明は、1ページ分のデータを書込む際に、ユーザデータの転送と付加データの転送を複数回に分けて行なわなければならない場合の処理効率を向上させたメモリコントローラ及びフラッシュメモリシステム、並びに、フラッシュメモリの制御方法を提供することを目的とする。

上記目的を達成するために、本発明の第1の観点に係るメモリコントローラは、ホストシステム側から供給されるユーザデータを保持する第1のデータ保持機能と、前記ユーザデータに対応する付加データを保持する第2のデータ保持機能と、前記第1のデータ保持機能に保持されているユーザデータと前記第2のデータ保持機能に保持されている付加データとをフラッシュメモリに転送するデータ転送機能とを備え、前記フラッシュメモリ内のページに、前記ユーザデータと該ユーザデータに対応する前記付加データとを複数組書込み、且つ、該ユーザデータと該ユーザデータに対応する該付加データとを連続した位置に書込む構成にされていることを特徴とする。

なお、前記ページの容量が、前記第1のデータ保持機能の容量と前記第2のデータ保持機能の容量とを併せた容量の整数倍であってもよい。

また、前記ページの容量が2112バイトであり、前記第1のデータ保持機能の容量が512バイトであり、前記第2のデータ保持機能の容量が16バイトであってもよい。

上記目的を達成するために、本発明の第2の観点に係るフラッシュメモリシステムは、上記、本発明の第1の観点に係るメモリコントローラのいずれかとフラッシュメモリとを備えることを特徴とする。

上記目的を達成するために、本発明の第3の観点に係るフラッシュメモリの制御方法は、第1のデータ保持機能に保持されているホストシステム側から供給されたユーザデータをフラッシュメモリに転送する処理と、第2のデータ保持機能に保持されている前記ユーザデータに対応する付加データをフラッシュメモリに転送する処理を交互に複数回繰り返すことにより、前記フラッシュメモリ内のページに、前記ユーザデータと該ユーザデータに対応する前記付加データとを複数組書込み、且つ、該ユーザデータと該ユーザデータに対応する該付加データを連続して書込むことを特徴とする。

なお、前記ページの容量が、前記第1のデータ保持機能の容量と前記第2のデータ保持機能の容量を併せた容量の整数倍であってもよい。

また、前記ページの容量が2112バイトであり、前記第1のデータ保持機能の容量が512バイトであり、前記第2のデータ保持機能の容量が16バイトであってもよい。

本発明によれば、ユーザデータと付加データをそれぞれ複数回に分けて転送する場合に、転送データがユーザデータから付加データに変る場合、又は付加データからユーザデータに変る場合に、書込先のアドレスを変更することなく処理を続行できる。したがって、書込処理の処理効率を向上させることができる。

以下、図面に基づき、本発明の実施形態について詳細に説明する。

[フラッシュメモリシステム1の説明]

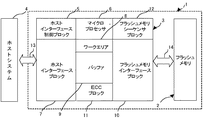

図1は、本発明に係るフラッシュメモリシステム1を概略的に示すブロック図である。

[フラッシュメモリシステム1の説明]

図1は、本発明に係るフラッシュメモリシステム1を概略的に示すブロック図である。

図1に示したようにフラッシュメモリシステム1は、フラッシュメモリ2と、それを制御するメモリコントローラ(以下、単にコントローラという)3とで構成されている。

フラッシュメモリシステム1は、通常、ホストシステム4に着脱可能に装着されて使用され、ホストシステム4に対して一種の外部記憶装置として用いられる。

尚、ホストシステム4としては、文字、音声、あるいは画像情報等の種々の情報を処理するパーソナルコンピュータやデジタルスチルカメラをはじめとする各種情報処理装置が挙げられる。

フラッシュメモリシステム1は、通常、ホストシステム4に着脱可能に装着されて使用され、ホストシステム4に対して一種の外部記憶装置として用いられる。

尚、ホストシステム4としては、文字、音声、あるいは画像情報等の種々の情報を処理するパーソナルコンピュータやデジタルスチルカメラをはじめとする各種情報処理装置が挙げられる。

フラッシュメモリ2は、ページ単位で読出し又は書込みを行い、ブロック単位で消去を実行するデバイスである。例えば、1ブロックは32ページで構成され、1ページは512バイトのユーザ領域と16バイトの冗長領域で構成されている。

コントローラ3は、ホストインターフェース制御ブロック5と、マイクロプロセッサ6と、ホストインターフェースブロック7と、ワークエリア8と、バッファ9と、フラッシュメモリインターフェースブロック10と、ECC(エラー・コレクション・コード)ブロック11と、フラッシュメモリシーケンサブロック12とから構成されている。

これら機能ブロックによって構成されるコントローラ3は、一つの半導体チップ上に集積されている。以下に各ブロックの機能を説明する。

マイクロプロセッサ6は、コントローラ3を構成する各機能ブロック全体の動作を制御する機能ブロックである。

マイクロプロセッサ6は、コントローラ3を構成する各機能ブロック全体の動作を制御する機能ブロックである。

ホストインターフェース制御ブロック5は、ホストインターフェースブロック7の動作を制御する機能ブロックである。ここで、ホストインターフェース制御ブロック5は、ホストインターフェースブロック7の動作を設定する動作設定レジスタ(図示せず)を備えており、この動作設定レジスタに基づきホストインターフェースブロック7は動作する。

ホストインターフェースブロック7は、ホストシステム4とデータ、アドレス情報、ステータス情報及び外部コマンド情報の授受を行なう機能ブロックである。すなわち、フラッシュメモリシステム1がホストシステム4に装着されると、フラッシュメモリシステム1とホストシステム4は、外部バス13を介して相互に接続され、かかる状態において、ホストシステム4よりフラッシュメモリシステム1に供給されるデータ等は、ホストインターフェースブロック7を入口としてコントローラ3の内部に取り込まれる。フラッシュメモリシステム1からホストシステム4に供給されるデータ等は、ホストインターフェースブロック7を出口としてホストシステム4に供給される。

さらに、ホストインターフェースブロック7は、ホストシステム4より供給されるホストアドレス及び外部コマンドを一時的に格納するタスクファイルレジスタ(図示せず)及びエラーが発生した場合にセットされるエラーレジスタ(図示せず)等を有している。

ワークエリア8は、フラッシュメモリ2の制御に必要なデータが一時的に格納される作業領域であり、複数のSRAM(Static Random Access Memory)セルによって構成される機能ブロックである。

バッファ9は、フラッシュメモリ2から読出したデータ及びフラッシュメモリ2に書込むデータを一時的に保持する機能ブロックである。すなわち、フラッシュメモリ2から読出したデータは、ホストシステム4の受取準備ができるまでバッファ9に保持される。フラッシュメモリ2に書込むデータは、フラッシュメモリ2の書込準備ができるまでバッファ9に保持される。

フラッシュメモリシーケンサブロック12は、内部コマンドに基づきフラッシュメモリ2の動作を制御する機能ブロックである。フラッシュメモリシーケンサブロック12は、複数のレジスタ(図示せず)を備え、この複数のレジスタに内部コマンドを実行する際に必要な情報が設定される。この複数のレジスタに内部コマンドを実行する際に必要な情報が設定されると、フラッシュメモリシーケンサブロック12は、その情報に基づいて処理を実行する。ここで、「内部コマンド」とは、コントローラ3からフラッシュメモリ2に与えられるコマンドであり、ホストシステム4からフラッシュメモリシステム1に与えられるコマンドの「外部コマンド」とは、区別される。

フラッシュメモリインターフェースブロック10は、内部バス14を介して、フラッシュメモリ2とデータ、アドレス情報、ステータス情報、内部コマンド情報及びデバイスID情報等の授受を行う機能ブロックである。

ECCブロック11は、フラッシュメモリ2に書込むデ―タに付加されるエラーコレクションコードを生成するとともに、読出しデータに付加されたエラーコレクションコードに基づいて、読出したデータに含まれる誤りを検出・訂正する機能ブロックである。

[フラッシュメモリ2の説明]

図1のフラッシュメモリ2は、NAND型メモリである。NAND型フラッシュメモリは、ストレージデバイスへの用途として(ハードディスクの代わりになるものとして)開発された不揮発性メモリである。このNAND型フラッシュメモリは、ランダムアクセスを行なうことができず、書込みと読出しはページ単位で、消去はブロック単位で行なわれる。データの上書きができないので、データを書込むときは、消去されている領域にデータの書込みが行なわれる。

図1のフラッシュメモリ2は、NAND型メモリである。NAND型フラッシュメモリは、ストレージデバイスへの用途として(ハードディスクの代わりになるものとして)開発された不揮発性メモリである。このNAND型フラッシュメモリは、ランダムアクセスを行なうことができず、書込みと読出しはページ単位で、消去はブロック単位で行なわれる。データの上書きができないので、データを書込むときは、消去されている領域にデータの書込みが行なわれる。

フラッシュメモリ2は、このような特徴を有するため、通常、データの書替を行なう場合には、ブロック消去されている消去済ブロックに新たなデータ(書替後のデータ)を書込み、古いデータ(書替前のデータ)が書込まれていたブロックを消去するという処理を行なっている。このようなデータの書替を行なった場合、書替後のデータは書替前と異なるブロックに書込まれるため、ホストシステム4側から与えられるアドレスに基づく論理ブロックアドレスと、フラッシュメモリ2内でのブロックアドレスである物理ブロックアドレスとの対応関係は、データを書替える毎に動的に変化する。この論理ブロックアドレスと物理ブロックアドレスとの対応関係は、通常、その対応関係を示したアドレス変換テーブルによって管理されており、アドレス変換テーブルは、後述する対応論理ブロックアドレスに基づいて作成される。

ここで、上記ブロックとページの関係を説明する。

図2(a),(b)は、ブロックとページの関係を示す説明図てある。

ブロック及びページの構成は、フラッシュメモリ2の仕様によって異なるが、一般的なフラッシュメモリでは、図2(a)に示したように、1ブロックが32ページ(P0〜P31)で構成される。各ページが512バイトのユーザ領域と16バイトの冗長領域で構成されている。又、記憶容量の増加に伴い、図2(b)に示したように、1ブロックが64ページ(P0〜P63)で構成され、各ページが2048バイトのユーザ領域と64バイトの冗長領域で構成されているものも提供されている。

図2(a),(b)は、ブロックとページの関係を示す説明図てある。

ブロック及びページの構成は、フラッシュメモリ2の仕様によって異なるが、一般的なフラッシュメモリでは、図2(a)に示したように、1ブロックが32ページ(P0〜P31)で構成される。各ページが512バイトのユーザ領域と16バイトの冗長領域で構成されている。又、記憶容量の増加に伴い、図2(b)に示したように、1ブロックが64ページ(P0〜P63)で構成され、各ページが2048バイトのユーザ領域と64バイトの冗長領域で構成されているものも提供されている。

ユーザ領域は、主に、ホストシステム4から供給されるデ―タが記憶される領域であり、冗長領域は、エラーコレクションコード、対応論理ブロックアドレス及びブロックステータス等の付加データが記憶される領域である。

エラ―コレクションコードは、ユーザ領域に記憶されているデータに含まれる誤りを検出、訂正するための付加データであり、外部のECCブロックによって生成される。対応論理ブロックアドレスは、そのブロックにデータが格納されている場合に、そのブロックがどの論理ブロックアドレスに対応するかを示している。

尚、そのブロックにデータが格納されていない場合は、対応論理ブロックアドレスも格納されていないので、対応論理ブロックアドレスが格納されているか否かで、そのブロックが消去済ブロックであるか否かを判断することもできる。つまり、対応論理ブロックアドレスが格納されていない場合は、消去済ブロックであると判断される。

ブロックステータスは、そのブロックが不良ブロック(正常にデータの書込み等を行なうことができないブロック)であるか否かを示すフラグであり、そのブロックが不良ブロックであると判断された場合には、不良ブロックであることを示すフラグが設定される。

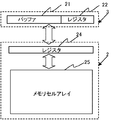

次に、フラッシュメモリ2の回路構成について説明する。

フラッシュメモリ2は、一般的なNAND型フラッシュメモリと同様に、メモリ書込みデータ若しくは読出しデータを保持するためのレジスタと、データを記憶するメモリセルアレイによって構成されている。メモリセルアレイは、複数のメモリセルが直列に接続されたメモリセル群を複数備えており、ワード線によってメモリセル群の特定のメモリセルが選択される。このワード線によって選択されたメモリセルとレジスタの間で、データの複写(レジスタからメモリセルへの複写、若しくはメモリセルからレジスタへの複写)が行なわれる。

フラッシュメモリ2は、一般的なNAND型フラッシュメモリと同様に、メモリ書込みデータ若しくは読出しデータを保持するためのレジスタと、データを記憶するメモリセルアレイによって構成されている。メモリセルアレイは、複数のメモリセルが直列に接続されたメモリセル群を複数備えており、ワード線によってメモリセル群の特定のメモリセルが選択される。このワード線によって選択されたメモリセルとレジスタの間で、データの複写(レジスタからメモリセルへの複写、若しくはメモリセルからレジスタへの複写)が行なわれる。

メモリセルアレイを構成するメモリセルは、2つのゲートを備えたMOSトランジスタで構成されている。ここで、上側のゲートはコントロールゲートと、下側のゲートはフローティングゲートと呼ばれており、フローティングゲートに電荷(電子)を注入若しくはフローティングゲートから電荷(電子)を排出することによって、データの書込み若しくはデータの消去を行なっている。このフローティングゲートは周囲を絶縁体で囲まれているので、注入された電子は長期間にわたって保持される。

尚、フローティングゲートに電子を注入するときは、コントロールゲートが高電位側となる高電圧を印加して電子を注入し、フローティングゲートから電子を排出するときは、コントロールゲートが低電位側となる高電圧を印加して電子を排出する。ここで、フローティングゲートに電子が注入されている状態(書込状態)が、論理値の「0」のデータに対応し、フローティングゲートから電子が排出されている状態(消去状態)が、論理値の「1」のデータに対応する。

[動作の説明]

次に、ホストシステムから供給されるユーザデータが、フラッシュメモリ2に書込まれる過程を、図3を参照して説明する。

図3は、フラッシュメモリシステムの動作の説明図である。

[動作の説明]

次に、ホストシステムから供給されるユーザデータが、フラッシュメモリ2に書込まれる過程を、図3を参照して説明する。

図3は、フラッシュメモリシステムの動作の説明図である。

図3のバッファ21と付加データ用レジスタ22は、図1のコントローラ3内に構成されており、バッファ21にはホストシステム4から供給されるユーザデータが保持され、付加データ用レジスタ22にはエラーコレクションコード等の付加データが設定されている。

一方、レジスタ24とメモリセルアレイ25は、フラッシュメモリ2内に構成されており、レジスタ24はコントローラ3から供給されるデータ又はメモリセルアレイ25から出力されたデータを保持し、メモリセルアレイ25はコントローラ3から供給されるデータを記憶する。ここで、レジスタ24の容量は、フラッシュメモリ2のページの容量と同一になっている。

ホストシステム4から供給されるユーザデータをフラッシュメモリ2に書込むときは、ホストシステム4から供給されるユーザデータがバッファ21に保持され、バッファ21に保持されたユーザデータに対して作成されたエラーコレクションコードやその他の付加データが、付加データ用レジスタ22に設定される。バッファ21に保持されたユーザデータと付加データ用レジスタ22に設定された付加データは、フラッシュメモリ2に転送され、フラッシュメモリ2内のレジスタ24に保持される。レジスタ24に保持されたユーザデータと付加データは、コントローラ3から指定されたページに複写(記憶)される。

従来のフラッシュメモリでは、図4に示したように、ページ内の先頭側の領域にユーザ領域が割当てられ、ページ内の末尾側の領域に冗長領域が割当てられていた。

図4(a),(b)は、従来の書込み状況を示す模式図である。

図4(a)に示した例では、先頭側の512バイトがユーザ領域に割当てられ、末尾側の16バイトが冗長領域に割当てられている。図4(b)に示した例では、先頭側の2048バイトがユーザ領域に割当てられ、末尾側の64バイトが冗長領域に割当てられている。このように、ユーザ領域はページ内の先頭側に、冗長領域はページ内の末尾側に、それぞれ固めて割当てられていた。

図4(a),(b)は、従来の書込み状況を示す模式図である。

図4(a)に示した例では、先頭側の512バイトがユーザ領域に割当てられ、末尾側の16バイトが冗長領域に割当てられている。図4(b)に示した例では、先頭側の2048バイトがユーザ領域に割当てられ、末尾側の64バイトが冗長領域に割当てられている。このように、ユーザ領域はページ内の先頭側に、冗長領域はページ内の末尾側に、それぞれ固めて割当てられていた。

尚、フラッシュメモリ2への書込処理では、フラッシュメモリ2内のレジスタに保持されたデータが、フラッシュメモリ2内のページに複写されるので、フラッシュメモリ2内のレジスタにユーザデータと付加データとを転送するときには、ページ内のユーザ領域と冗長領域の割当てに従って、データの転送を行なわなければならない。つまり、ページ内の先頭側の領域にユーザ領域が割当てられ、ページ内の末尾側の領域に冗長領域が割当てられている場合は、レジスタ内の先頭側の領域にユーザデータ(ユーザ領域に書込まれるデータ)が保持され、末尾側の領域に付加データ(冗長領域に書込まれるデータ)が保持されるようにデータの転送を行なわなければならない。

次に、コントローラ内の512バイトのバッファと16バイトの付加データ用レジスタを用いて、ユーザ領域が2048バイトのページ(図4(b))にデータを書込む場合の処理について、図面を参照して説明する。

図5は、従来の書込処理でフラッシュメモリ2内のレジスタに保持されたデータを示す図である。図6は、本発明に係る書込処理でフラッシュメモリ2内のレジスタに保持されたデータを示すである。

図5は、従来の書込処理でフラッシュメモリ2内のレジスタに保持されたデータを示す図である。図6は、本発明に係る書込処理でフラッシュメモリ2内のレジスタに保持されたデータを示すである。

尚、書込処理では、上述のようにフラッシュメモリ内のレジスタに保持されたデータが、書込先のページに複写されるので、レジスタに保持されるユーザデータと付加データの配列と、書込先のページに複写されるデータのユーザデータと付加データの配列は同一になる。よって、フラッシュメモリ内のレジスタで、ユーザデータが保持される領域が、ページ内のユーザ領域に対応し、付加データが保持される領域が、ページ内の冗長領域に対応する。このため、以下の説明では、フラッシュメモリ内のレジスタに保持されるユーザデータと付加データの配列を中心に説明する。

図5に示した従来の書込処理では、フラッシュメモリに対して、次のような順序でユーザデータと付加データが転送される。ステップ0でユーザデータが転送され、ステップ1で付加データが転送され、ステップ2でユーザデータが転送され、ステップ3で付加データが転送され、ステップ4でユーザデータが転送され、ステップ5で付加データが転送され、ステップ6でユーザデータが転送され、ステップ7で付加データが転送される。

ここで、ステップ1で転送される付加データはステップ0で転送されるユーザデータに対応し、ステップ3で転送される付加データはステップ2で転送されるユーザデータに対応し、ステップ5で転送される付加データはステップ4で転送されるユーザデータに対応し、ステップ7で転送される付加データはステップ6で転送されるユーザデータに対応する。又、ステップ0、ステップ2、ステップ4及びステップ6で転送されるユーザデータは、レジスタの先頭側の領域からこの順番で保持され、ステップ1、ステップ3、ステップ5及びステップ7で転送される付加データは、ユーザデータの後にこの順番で保持される。

図6(a)に示した本発明に係る書込処理では、フラッシュメモリに対して、次のような順番でユーザデータと付加データが転送され、転送された順番でフラッシュメモリ内のレジスタに保持される。ステップA0でユーザデータが転送され、ステップA1で付加データが転送され、ステップA2でユーザデータが転送され、ステップA3で付加データが転送され、ステップA4でユーザデータが転送され、ステップA5で付加データが転送され、ステップA6でユーザデータが転送され、ステップA7で付加データが転送される。ここで、ステップA1で転送される付加データはステップA0で転送されるユーザデータに対応し、ステップA3で転送される付加データはステップA2で転送されるユーザデータに対応し、ステップA5で転送される付加データはステップA4で転送されるユーザデータに対応し、ステップA7で転送される付加データはステップA6で転送されるユーザデータに対応する。

つまり、本発明に係る書込処理では、512バイトのユーザデータとこれに対応する16バイトの付加データがレジスタ内の連続した領域に保持される。又、ユーザデータと付加データとは、レジスタ内の領域に交互に配列される。これに対応して、レジスタに保持されていたデータが複写されるページ内の領域も、512バイトのユーザ領域と16バイトの冗長領域が交互に割当てられる。

図6(a)に示した例では、512バイトのバッファと16バイトの付加データ用レジスタを用いて書込処理を行なったが、図6(b)に示した例では、1024バイトのバッファと32バイトの付加データ用レジスタを用いて書込処理を行なっている。1024バイトのバッファと32バイトの付加データ用レジスタを用いて書込処理を行なった場合も、ユーザデータとこれに対応する付加データがレジスタ内の連続した領域に保持される。又、ユーザデータと付加データは、レジスタ内の領域に交互に配列される。但し、1024バイトのバッファと32バイトの付加データ用レジスタを用いて書込処理を行なっているので、ページ内の領域には、1024バイトのユーザ領域と32バイトの冗長領域が交互に割当てられる。

次に、図5に示した従来の書込処理でフラッシュメモリに供給される信号と、図6(a)に示した本発明に係る書込処理でフラッシュメモリに供給される信号について図面を参照して説明する。

図7は、従来の書込処理でフラッシュメモリ2に供給される信号の波形図であり、図8は、図6(a)に示した本発明に係る書込処理でフラッシュメモリ2に供給される信号の波形図である。

図7に示した波形図で、S11は、コマンド、アドレス及びデータ(ユーザデータ、付加データ等)等を供給するデータバスに出力されるデータ信号である。S12は、データバスに出力されている信号がコマンドを示す信号であるときに高レベルとなるコマンドラッチイネーブル信号である。S13は、データバスに出力されている信号がアドレスを示す信号であるときに高レベルとなるアドレスラッチイネーブル信号である。S14は、データバスにコマンド、アドレス及びデータが出力されているときに低レベルから高レベルに変化するライトイネーブル信号である。尚、コマンドラッチイネーブル信号、アドレスラッチイネーブル信号及びライトイネーブル信号以外の制御信号については図示していない。又、以下の説明で、データバスに出力されるコマンドを示す信号をコマンド信号と言い、アドレスを示す信号をアドレス信号と言い、ユーザデータを示す信号をユーザデータ信号と言い、付加データを示す信号を付加データ信号と言う。

図7は、従来の書込処理でフラッシュメモリ2に供給される信号の波形図であり、図8は、図6(a)に示した本発明に係る書込処理でフラッシュメモリ2に供給される信号の波形図である。

図7に示した波形図で、S11は、コマンド、アドレス及びデータ(ユーザデータ、付加データ等)等を供給するデータバスに出力されるデータ信号である。S12は、データバスに出力されている信号がコマンドを示す信号であるときに高レベルとなるコマンドラッチイネーブル信号である。S13は、データバスに出力されている信号がアドレスを示す信号であるときに高レベルとなるアドレスラッチイネーブル信号である。S14は、データバスにコマンド、アドレス及びデータが出力されているときに低レベルから高レベルに変化するライトイネーブル信号である。尚、コマンドラッチイネーブル信号、アドレスラッチイネーブル信号及びライトイネーブル信号以外の制御信号については図示していない。又、以下の説明で、データバスに出力されるコマンドを示す信号をコマンド信号と言い、アドレスを示す信号をアドレス信号と言い、ユーザデータを示す信号をユーザデータ信号と言い、付加データを示す信号を付加データ信号と言う。

図7に示した従来の書込処理における波形図では、まず、データバスに書込コマンドに対応するコマンド信号Cが出力され、続いて、ステップ0に対応するアドレス信号A0、ユーザデータ信号D0〜D511及びアドレス変更コマンドに対応するコマンドC”が順次出力され、その後、ステップ1に対応するアドレス信号A1及び付加データ信号D0’〜D15’が順次出力される。以下同様に、ステップ2、ステップ4及びステップ6に対応するアドレス信号、ユーザデータ信号及びアドレス変更コマンドに対応するコマンドC”が順次出力され、その後にステップ3、ステップ5及びステップ7に対応するアドレス信号及び付加データ信号が順次出力される。以上の処理で、フラッシュメモリ内のレジスタに保持されたデータは、データ複写に対応するコマンド信号C’によって、レジスタから書込み先ページに複写される。尚、データバスに出力された信号は、ライトイネーブル信号(S14)の立上りでフラッシュメモリに取込まれ、コマンドラッチイネーブル信号(S12)が高レベルのときに取込まれた信号はコマンド信号と判断され、アドレスラッチイネーブル信号(S13)が高レベルのときに取込まれた信号はアドレス信号と判断される。

図7に示した従来の書込処理における波形図では、各ステップの最初にアドレス変更コマンドに対応するコマンドC”とアドレス信号が出力されている。これは、各ステップの変り目でアドレスが不連続になるため、書込先のアドレスを指定しているからである。尚、指定されたアドレスは、ライトイネーブル信号の立上りでカウントアップされるので、アドレス信号で書込先のアドレスを指定しなかった場合、ユーザデータ信号若しくは付加データ信号に対応するデータは連続したアドレスに順次取込まれる。

図8に示した波形図で、S21は、コマンド、アドレス及びデータ(ユーザデータ、付加データ等)等を供給するデータバスに出力されるデータ信号である。S22は、データバスに出力されている信号がコマンドを示す信号であるときに高レベルとなるコマンドラッチイネーブル信号である。、S23は、データバスに出力されている信号がアドレスを示す信号であるときに高レベルとなるアドレスラッチイネーブル信号である。S24は、データバスにコマンド、アドレス及びデータが出力されているときに低レベルから高レベルに変化するライトイネーブル信号である。

図8に示した本発明に係る書込処理における波形図では、まず、データバスに書込コマンドに対応するコマンド信号Cが出力され、続いて、ステップA0に対応するアドレス信号A0及びユーザデータ信号D0〜D511が順次出力され、更に、ステップA1に対応する付加データ信号D0’〜D15’が順次出力される。以下同様に、ステップA2、ステップA4及びステップA6に対応するユーザデータ信号と、ステップA3、ステップA5及びステップA7に対応する付加データ信号が、ステップA2、ステップA3、…、ステップA7の順で出力される。以上の処理で、フラッシュメモリ内のレジスタに保持されたデータは、データ複写に対応するコマンド信号C’によって、レジスタから書込み先ページに複写される。

尚、データバスに出力された信号は、ライトイネーブル信号(S24)の立上りでフラッシュメモリに取込まれ、コマンドラッチイネーブル信号(S22)が高レベルのときに取込まれた信号はコマンド信号と判断され、アドレスラッチイネーブル信号(S23)が高レベルのときに取込まれた信号はアドレス信号と判断される。

図8に示した本発明に係る書込処理における波形図では、ステップ0の最初にアドレス信号が出力され、それ以降のステップ1〜7では、アドレス変更コマンドに対応するコマンド信号やアドレス信号が出力されない。これは、ステップ0〜7で出力されるユーザデータ信号若しくは付加データ信号に対応するデータが、ずっと連続したアドレスに順次取込まれるからである。

以上のように、本実施形態のフラッシュメモリシステム1では、ユーザデータと付加データを転送する場合に、転送データがユーザデータから付加データに変る場合、又は付加データからユーザデータに変る場合に書込先のアドレスを変更する必要がない。したがって、書込処理の処理効率を向上させることができる。

1 フラッシュメモリシステム

2 フラッシュメモリ

3 メモリコントローラ

4 ホストシステム

2 フラッシュメモリ

3 メモリコントローラ

4 ホストシステム

Claims (7)

- ホストシステム側から供給されるユーザデータを保持する第1のデータ保持機能と、

前記ユーザデータに対応する付加データを保持する第2のデータ保持機能と、

前記第1のデータ保持機能に保持されているユーザデータと前記第2のデータ保持機能に保持されている付加データとをフラッシュメモリに転送するデータ転送機能とを備え、

前記フラッシュメモリ内のページに、前記ユーザデータと該ユーザデータに対応する前記付加データとを複数組書込み、且つ、該ユーザデータと該ユーザデータに対応する該付加データとを連続した位置に書込む構成にされていることを特徴とするメモリコントローラ。 - 前記ページの容量が、前記第1のデータ保持機能の容量と前記第2のデータ保持機能の容量とを併せた容量の整数倍であることを特徴とする請求項1記載のメモリコントローラ。

- 前記ページの容量が2112バイトであり、

前記第1のデータ保持機能の容量が512バイトであり、

前記第2のデータ保持機能の容量が16バイトである、

ことを特徴とする請求項1又は2記載のメモリコントローラ。 - 請求項1乃至3のいずれか1項記載のメモリコントローラとフラッシュメモリと、を備えることを特徴とするフラッシュメモリシステム。

- 第1のデータ保持機能に保持されているホストシステム側から供給されたユーザデータをフラッシュメモリに転送する処理と、第2のデータ保持機能に保持されている前記ユーザデータに対応する付加データをフラッシュメモリに転送する処理を交互に複数回繰り返すことにより、

前記フラッシュメモリ内のページに、前記ユーザデータと該ユーザデータに対応する前記付加データとを複数組書込み、且つ、該ユーザデータと該ユーザデータに対応する該付加データを連続して書込むことを特徴とするフラッシュメモリの制御方法。 - 前記ページの容量が、前記第1のデータ保持機能の容量と前記第2のデータ保持機能の容量を併せた容量の整数倍であることを特徴とする請求項5記載のフラッシュメモリの制御方法。

- 前記ページの容量が2112バイトであり、前記第1のデータ保持機能の容量が512バイトであり、前記第2のデータ保持機能の容量が16バイトであることを特徴とする請求項5又は6記載のフラッシュメモリの制御方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004103307A JP2005292925A (ja) | 2004-03-31 | 2004-03-31 | メモリコントローラ、フラッシュメモリシステム、並びに、フラッシュメモリの制御方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004103307A JP2005292925A (ja) | 2004-03-31 | 2004-03-31 | メモリコントローラ、フラッシュメモリシステム、並びに、フラッシュメモリの制御方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005292925A true JP2005292925A (ja) | 2005-10-20 |

Family

ID=35325827

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004103307A Pending JP2005292925A (ja) | 2004-03-31 | 2004-03-31 | メモリコントローラ、フラッシュメモリシステム、並びに、フラッシュメモリの制御方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005292925A (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008112335A (ja) * | 2006-10-31 | 2008-05-15 | Tdk Corp | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法 |

| JP2013016148A (ja) * | 2011-06-08 | 2013-01-24 | Panasonic Corp | メモリコントローラ、不揮発性記憶装置 |

| JP2013050938A (ja) * | 2011-08-01 | 2013-03-14 | Toshiba Corp | メモリ・デバイス |

| US8656252B2 (en) | 2011-06-08 | 2014-02-18 | Panasonic Corporation | Memory controller and non-volatile storage device |

| US8856427B2 (en) | 2011-06-08 | 2014-10-07 | Panasonic Corporation | Memory controller and non-volatile storage device |

| JPWO2017183153A1 (ja) * | 2016-04-21 | 2018-07-19 | 富士通フロンテック株式会社 | 書込制御プログラム、書込制御装置および書込制御方法 |

-

2004

- 2004-03-31 JP JP2004103307A patent/JP2005292925A/ja active Pending

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008112335A (ja) * | 2006-10-31 | 2008-05-15 | Tdk Corp | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法 |

| JP2013016148A (ja) * | 2011-06-08 | 2013-01-24 | Panasonic Corp | メモリコントローラ、不揮発性記憶装置 |

| US8656252B2 (en) | 2011-06-08 | 2014-02-18 | Panasonic Corporation | Memory controller and non-volatile storage device |

| US8856427B2 (en) | 2011-06-08 | 2014-10-07 | Panasonic Corporation | Memory controller and non-volatile storage device |

| US8898420B2 (en) | 2011-06-08 | 2014-11-25 | Panasonic Corporation | Non-volatile storage device and a memory controller controlling parity tables of recording regions of the non-volatile storage device |

| JP2013050938A (ja) * | 2011-08-01 | 2013-03-14 | Toshiba Corp | メモリ・デバイス |

| JPWO2017183153A1 (ja) * | 2016-04-21 | 2018-07-19 | 富士通フロンテック株式会社 | 書込制御プログラム、書込制御装置および書込制御方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2004507007A (ja) | 不揮発性メモリに対する信頼性の高いデータコピー処理を行うための新規の方法および構造 | |

| JP2006018373A (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| US9383929B2 (en) | Data storing method and memory controller and memory storage device using the same | |

| JP4697146B2 (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法 | |

| JP4373943B2 (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP4661191B2 (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP2005292925A (ja) | メモリコントローラ、フラッシュメモリシステム、並びに、フラッシュメモリの制御方法 | |

| JP4177292B2 (ja) | メモリンコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP4661369B2 (ja) | メモリコントローラ | |

| JP4661497B2 (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP2007034581A (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP4194518B2 (ja) | メモリコントローラ、フラッシュメモリシステム、並びに、フラッシュメモリの制御方法 | |

| JP4000124B2 (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びに、フラッシュメモリの制御方法 | |

| JP4177301B2 (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP4235595B2 (ja) | メモリコントローラ、メモリコントローラを備えるフラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP4366283B2 (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム | |

| JP4332108B2 (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP4609406B2 (ja) | メモリコントローラ、メモリコントローラを備えるフラッシュメモリシステム、並びに、フラッシュメモリの制御方法 | |

| JP4661748B2 (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリの制御方法 | |

| JP4655034B2 (ja) | メモリコントローラ及びフラッシュメモリシステム並びにフラッシュメモリの制御方法 | |

| JP4304167B2 (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP3934659B1 (ja) | メモリコントローラ及びフラッシュメモリシステム | |

| JP4254930B2 (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP2006178909A (ja) | メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法 | |

| JP2005293177A (ja) | メモリコントローラ及びフラッシュメモリシステム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070221 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070227 |

|

| A02 | Decision of refusal |

Effective date: 20070703 Free format text: JAPANESE INTERMEDIATE CODE: A02 |