JP2005291758A - 半導体集積回路のテスト方法及び半導体集積回路のテストプログラム生成プログラム - Google Patents

半導体集積回路のテスト方法及び半導体集積回路のテストプログラム生成プログラム Download PDFInfo

- Publication number

- JP2005291758A JP2005291758A JP2004103522A JP2004103522A JP2005291758A JP 2005291758 A JP2005291758 A JP 2005291758A JP 2004103522 A JP2004103522 A JP 2004103522A JP 2004103522 A JP2004103522 A JP 2004103522A JP 2005291758 A JP2005291758 A JP 2005291758A

- Authority

- JP

- Japan

- Prior art keywords

- test

- failure detection

- patterns

- detection rate

- program

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 35

- 238000010998 test method Methods 0.000 title claims abstract description 21

- 238000012360 testing method Methods 0.000 claims abstract description 303

- 238000001514 detection method Methods 0.000 claims description 95

- 238000003860 storage Methods 0.000 claims description 14

- 238000000034 method Methods 0.000 claims description 11

- 238000004904 shortening Methods 0.000 abstract description 4

- 230000002950 deficient Effects 0.000 description 9

- 238000004806 packaging method and process Methods 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 1

Images

Landscapes

- Tests Of Electronic Circuits (AREA)

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

Abstract

【課題】

歩留りを殆ど変化させることなく、試験時間の短縮を図ることが可能な、半導体集積回路のテスト方法及びテストプログラムを提供すること。

【解決手段】

本発明にかかるテスト方法は、まず、基準テストパタンを生成する(S1)。次に、故障検出率とテストパタン数の対応を求める(S22)。また、故障検出率を設定する(S23)。設定された故障検出率に基づいて、故障検出率とテストパタン数の対応を参照して、当該故障検出率を達成するためのテストパタン数を算出し、算出されたテストパタン数分の、基準テストパタンに含まれるテストパタンをウェハ試験用テストパタンとしてウェハ試験用テストプログラムを作成する(S3)。パッケージ試験用テストパタンは、基準テストパタンを用いる。

【選択図】 図1

歩留りを殆ど変化させることなく、試験時間の短縮を図ることが可能な、半導体集積回路のテスト方法及びテストプログラムを提供すること。

【解決手段】

本発明にかかるテスト方法は、まず、基準テストパタンを生成する(S1)。次に、故障検出率とテストパタン数の対応を求める(S22)。また、故障検出率を設定する(S23)。設定された故障検出率に基づいて、故障検出率とテストパタン数の対応を参照して、当該故障検出率を達成するためのテストパタン数を算出し、算出されたテストパタン数分の、基準テストパタンに含まれるテストパタンをウェハ試験用テストパタンとしてウェハ試験用テストプログラムを作成する(S3)。パッケージ試験用テストパタンは、基準テストパタンを用いる。

【選択図】 図1

Description

本発明は、半導体集積回路のテスト方法及び半導体集積回路のテストプログラム生成プログラムに関するものであり、より詳しくは、例えば、ウェハ試験やパッケージ試験等の複数の試験を行なう場合におけるテストプログラムの生成に関する。

従来より半導体集積回路に対しては、様々な試験(テスト)が行なわれている(例えば、特許文献1等)。半導体集積回路の試験には、ウェハ状態で行なわれるウェハ試験やパッケージ化後に行なわれるパッケージ試験がある。

図4は、第1の従来例にかかるテスト方法を示すフローチャートである。このテスト方法では、まず、ウェハ試験とパッケージ試験の両方に適用する1つのテストパタンを生成する(S1)。1種類のテストパタンの生成には、例えば、コンピュータ2台で2日を要する。生成したテストパタンを記憶手段に格納する(S2)。そして、このテストパタンに基づき、テストプログラムを作成する(S3)。作成したテストプログラムに基づき、ウェハ試験用テストプログラム(S41)とパッケージ試験用のテストプログラム(S42)を作成する。

半導体ICは、図4に示されるように、ウェハ製造(S101)、ウェハ試験(S102)、パッケージング(S103)、パッケージ試験(S104)及び出荷(S105)の各工程を経て、製造、試験及び出荷が行なわれる。作成されたウェハ試験用テストプログラム(S41)に基づいてウェハ試験(S102)が実行され、良品/不良品の判定が行なわれる。また、パッケージ試験用のテストプログラム(S42)に基づいてパッケージ試験(S104)が実行され、良品/不良品の判定が行なわれる。

図5は、第2の従来例にかかるテスト方法を示すフローチャートである。このテスト方法では、まず、検出率の異なるウェハ試験用とパッケージ試験用の別々のテストパタンを生成する(S11、S12)。生成したテストパタンをそれぞれ記憶手段に格納する(S21、S22)。そして、ウェハ試験用テストパタンに基づいてウェハ試験用テストプログラムを作成し(S31)、記憶手段に格納する(S41)。また、パッケージ試験用テストパタンに基づいてパッケージ試験用テストプログラムを作成し(S32)、記憶手段に格納する(S42)。

そして、作成されたウェハ試験用テストプログラム(S41)に基づいてウェハ試験(S102)が実行され、良品/不良品の判定が行なわれる。また、パッケージ試験用のテストプログラム(S42)に基づいてパッケージ試験(S104)が実行され、良品/不良品の判定が行なわれる。

特開平9−127213号公報

上述の第1の従来例にかかるテスト方法によれば、ウェハ状態で行なわれるウェハ試験と、パッケージ化後のパッケージ試験とにおいて、同じテストパタンで実行するが、当該テストパタンは故障検出率を高くできるように作成された全部のテストパタンで実行されるため、ウェハ試験とパッケージ試験で同じテスト時間がかかり、テスト時間が長くなるという問題点があった。

上述の第2の従来例にかかるテスト方法によれば、テスト時間を短縮するために、ウェハ試験用とパッケージ試験用でテストパタンの異なる故障検出率のテストパタンを使用しようとすると、パッケージ試験用とウェハ試験用とで別々にテストパタンを作成する必要がある。そのため、テストパタン生成に余分な時間と、2つのテストパタンを記憶するハードウェアリソースが必要になる。この第2の従来例においては、パタン数と検出率対応情報がないため、テストパタンを生成した後では、走行パタン数を変更できないという問題点もある。

本発明は、かかる問題を解消するためになされたものであり、歩留りを殆ど変化させることなく、試験時間の短縮を図ることが可能な、半導体集積回路のテスト方法及びテストプログラム生成プログラムを提供することにある。

本発明にかかるテスト方法は、半導体集積回路に対して少なくとも第1の試験と第2の試験を実行する半導体集積回路のテスト方法であって、作成された基準テストパタンの、前記半導体集積回路に対する故障検出率とテストパタン数の対応を求めるステップと、前記第1の試験に対する故障検出率を設定するステップと、前記設定された故障検出率に基づいて、前記故障検出率とテストパタン数の対応を参照して、当該故障検出率を達成するためのテストパタン数を算出するステップと、算出されたテストパタン数分の、前記基準テストパタンに含まれるテストパタンを第1の試験用テストパタンとして第1の試験用テストプログラムを作成するステップとを備えたものである。

ここで、前記基準テストパタンを第2の試験用テストパタンとして第2の試験用テストプログラムを作成するステップを備えることが好ましい。

さらに、前記第2の試験に対する故障検出率を設定するステップと、前記設定された故障検出率に基づいて、前記故障検出率とテストパタン数の対応を参照して、当該第2の試験に対する故障検出率を達成するためのテストパタン数を算出するステップと、算出されたテストパタン数分の、前記基準テストパタンに含まれるテストパタンを第2の試験用テストパタンとして第2の試験用テストプログラムを作成するステップとを備えるようにしてもよい。

前記故障検出率とテストパタン数の対応は、当該故障検出率とテストパタン数を対応付けたテーブルにより記憶手段に格納されることが望ましい。

また、前記第1の試験用テストプログラムにより、前記半導体集積回路に対して第1の試験を実行するステップと、前記第2の試験用テストプログラムにより、前記半導体集積回路に対して第2の試験を実行するステップとを備えるようにしてもよい。

好適な実施の形態において、前記第1の試験は、ウェハ試験であり、前記第2の試験はパッケージ試験である。

本発明にかかるテストプログラム生成プログラムは、半導体集積回路に対して第1の試験を実行するための第1の試験用テストプログラムと、第2の試験を実行するための第2の試験用テストプログラムを生成するためのテストプログラム生成プログラムであって、当該テストプログラム生成プログラムは、コンピュータに対して、基準テストパタンの、前記半導体集積回路に対する故障検出率とテストパタン数の対応を求めるステップと、前記第1の試験に対する故障検出率の設定するステップと、前記設定された故障検出率に基づいて、前記故障検出率とテストパタン数の対応を参照して、当該故障検出率を達成するためのテストパタン数を算出するステップと、算出されたテストパタン数分の、前記基準テストパタンに含まれるテストパタンを第1の試験用テストパタンとして第1の試験用テストプログラムを作成するステップとを実行させるものである。

ここで、前記基準テストパタンを第2の試験用テストパタンとして第2の試験用テストプログラムを作成するステップをさらにコンピュータに実行させることが好ましい。

また、前記第2の試験に対する故障検出率を設定するステップと、前記設定された故障検出率に基づいて、前記故障検出率とテストパタン数の対応を参照して、当該第2の試験に対する故障検出率を達成するためのテストパタン数を算出するステップと、算出されたテストパタン数分の、前記基準テストパタンに含まれるテストパタンを第2の試験用テストパタンとして第2の試験用テストプログラムを作成するステップをさらにコンピュータに実行させるようにしてもよい。

また、前記故障検出率とテストパタン数の対応は、当該故障検出率とテストパタン数を対応付けたテーブルにより記憶手段に格納されることが望ましい。

好適な実施の形態において、前記第1の試験は、ウェハ試験であり、前記第2の試験はパッケージ試験である。

本発明によれば、歩留りを殆ど変化させることなく、試験時間の短縮を図ることが可能な、半導体集積回路のテスト方法及びテストプログラム生成プログラムを提供することができる。

図1は、本発明にかかる半導体集積回路のテスト方法を示すフローチャートである。図に示されるように、半導体ICは、ウェハ製造(S101)、ウェハ試験(S102)、パッケージング(S103)、パッケージ試験(S104)及び出荷(S105)の各工程を経て、製造、試験及び出荷が行なわれる。当該ウェハ試験(S102)、パッケージ試験(S104)は、テストパタンに従う信号を入力端子に入力し、出力端子より出力される信号を検出する試験の他、いわゆるスキャンテストも含まれる。

本発明にかかる半導体集積回路のテスト方法においては、まず、基準となるテストパタン(以下、基準テストパタン)を作成する(S1)。基準テストパタンは、周知のテストパタン作成装置によって作成され、当該テストパタン作成装置の内部記憶手段又は外部記憶手段に格納される(S21)。作成されるテストパタン数は、試験対象となる半導体集積回路の構成によって大きく異なるが、例えば、500から数1000である。

基準テストパタンを作成する際に、同時に、故障検出率を算出し、当該故障検出率をパタン数と関連付けて記憶手段に格納しておく。この処理は、テストパタン作成装置によって実行することも可能であるが、テストパタン作成装置より基準テストパタンを出力し、出力された基準テストパタンに基づきテストプログラム作成装置により実行することも可能である。

テストプログラム作成装置は、例えば、テストプログラム生成プログラムをコンピュータにインストールすることにより構成される。当該コンピュータは、CPU、ROM、RAM、ハードディスク等のハードウェア構成を有するとともに、OS(Operation System)プログラム及びテストプログラム生成プログラム等のアプリケーションプログラムをハードディスク上に格納している。そして、適宜、これらのプログラムをRAM上に展開した上で、CPUにより所定の処理を実行する。

ここで、故障検出率について説明しておく。この故障検出率は、例えば、次の式によって算出する。

故障検出率=(S0+S1)/(S*2) ・・・ (1)

式(1)において、S0は所定のテストパタンで一度でも"0"になったノードの数、S1は所定のテストパタンで一度でも"1"になったノードの数、Sは全ノード数である。なお、ここで「ノード」とは、IC内部のそれぞれの信号線のことである。式(1)では故障モデルとして、縮退故障モデルを用いているため、テストパタンからより多くのノードが"0"及び"1"にセットされるパタンを検索すれば良い。この式は、全ノードの数の内のどれだけのノードが"0"及び"1"にセットされているか表したものなので、値が大きいと検出率が高いということになる。なお、縮退故障モデルは、単に一例にすぎないので、他の故障を検出したいならば、その故障モデルに見合った式を用いれば良い。

故障検出率=(S0+S1)/(S*2) ・・・ (1)

式(1)において、S0は所定のテストパタンで一度でも"0"になったノードの数、S1は所定のテストパタンで一度でも"1"になったノードの数、Sは全ノード数である。なお、ここで「ノード」とは、IC内部のそれぞれの信号線のことである。式(1)では故障モデルとして、縮退故障モデルを用いているため、テストパタンからより多くのノードが"0"及び"1"にセットされるパタンを検索すれば良い。この式は、全ノードの数の内のどれだけのノードが"0"及び"1"にセットされているか表したものなので、値が大きいと検出率が高いということになる。なお、縮退故障モデルは、単に一例にすぎないので、他の故障を検出したいならば、その故障モデルに見合った式を用いれば良い。

故障検出率は、具体的には、試験対象となる半導体集積回路において論理演算により求めることが可能であり、コンピュータにより求めることが可能である。

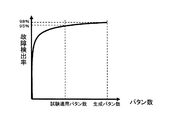

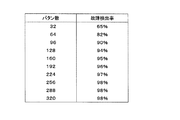

故障検出率とパタン数の対応を示すグラフを図2に示す。図に示されるように、故障検出率は、パタン数を増加させるに伴って増加する。しかしながら、パタン数の増加に伴う故障検出率の増加率は、パタン数の増加に伴って低下する。この例では、95%の故障検出率を得るためのパタン数は、98%の故障検出率を得るためのパタン数は約半分であり、後半の故障検出率の増加率は極めて低い。尚、パタン数の削減割合は回路の構成により異なる。

また、故障検出率とパタン数を関連付けることにより得られるテーブルの例を図3に示す。このテーブルは、図2に示すグラフの値を離散的な数値で表わしたものである。この例では、パタン数が256で故障検出率が98%に達し、その後320までパタン数を増加させても故障検出率は殆ど変化しない。他方、95%の故障検出率を得るためのパタン数は160であり、98%の故障検出率を得るためのパタン数256よりも極めて少ないことが判る。

また、ユーザは、テストプログラム作成装置に対してキーボード等の入力手段により故障検出率を入力して設定する。入力された故障検出率はテストプログラム作成装置における所定の記憶手段中に格納される。この故障検出率は、ウェハ試験、パッケージ試験のそれぞれにおいて、ユーザが必要と判断し、設定したものである。例えば、ウェハ試験を95%、パッケージ試験を98%と設定することができる。このとき、パッケージ試験の方が、ウェハ試験よりも後に実行されるため、より厳密なテストを行なう必要があるとの観点からすれば、ウェハ試験よりもパッケージ試験の方が故障検出率が高くなるように設定すべきである。他方、初期段階で厳しいテストを課す方が作業効率が高まるという観点に立てば、パッケージ試験よりもウェハ試験の方が故障検出率が高くなるように設定する。いずれにしても、本発明の実施の形態によれば、ウェハ試験とパッケージ試験とで、試験時間を短縮化するという観点から、異なる故障検出率を設定する必要がある。

次に、基準テストパタン(S21)、故障検出率とパタン数を関連付けたテーブル(S22)、設定された故障検出率(S23)に基づいて、テストプログラムを生成する(S3)。

まず、ウェハ試験用テストプログラムの作成処理について説明する。ユーザは、テストプログラム作成装置に対してウェハ試験用テストプログラムの作成要求を入力する。この作成要求は、必ずしもユーザにより発生する必要はなく、テストプログラム作成装置内部において発生してもよい。テストプログラム作成装置は、インストールされたテストプログラム生成プログラムが起動することにより、当該作成要求に応じて、別途設定されたウェハ試験の故障検出率に基づいて故障検出率とパタン数を関連付けたテーブルを参照し、設定された故障検出率にするために必要なテストパタン数を算出する。図3に示す例において、設定されたウェハ試験の故障検出率が95%の場合には、パタン数160が算出される。尚、設定された故障検出率と同じ値が当該テーブル上にない場合には、当該テーブルにある値を内挿することにより対応するパタン数を算出してもよいし、設定された故障検出率よりも高い故障検出率で最も近い値の故障検出率をテーブル上で選択して、当該選択された故障検出率に対応するパタン数を抽出することによってパタン数を算出してもよい。

テストプログラム作成装置は、このようにしてパタン数を算出すると、記憶手段に格納された基準テストパタンのうち、当該パタン数分のテストパタンをウェハ試験用のテストパタンとする。図3に示す例では、160のテストパタンがウェハ試験用のテストパタンとされ、ウェハ試験用テストプログラムが生成される(S41)。

次に、パッケージ試験用テストプログラムの作成処理について説明する。ユーザは、テストプログラム作成装置に対してパッケージ試験用テストプログラムの作成要求を入力する。この作成要求は、必ずしもユーザにより発生する必要はなく、テストプログラム作成装置内部において発生してもよい。テストプログラム作成装置は、インストールされたテストプログラム生成プログラムが起動することにより、当該作成要求に応じて、別途設定されたウェハ試験の故障検出率に基づいて故障検出率とパタン数を関連付けたテーブルを参照し、設定された故障検出率にするために必要なテストパタン数を算出する。図3に示す例において、設定されたパッケージ試験の故障検出率が98%の場合には、パタン数256が算出される。このとき、予めパッケージ試験の故障検出率として設定した値が、基準テストパタンを生成する際に設定された故障検出率の値と同じであれば、特にパタン数の算出を行なう必要がない。

テストプログラム作成装置は、このようにしてパタン数を算出すると、記憶手段に格納された基準テストパタンのうち、当該パタン数分のテストパタンをパッケージ試験用のテストパタンとする。図3に示す例では、256のテストパタンがパッケージ試験用のテストパタンとされ、パッケージ試験用テストプログラムが生成される(S42)。このとき、予めパッケージ試験の故障検出率として設定した値が、基準テストパタンを生成する際に設定された故障検出率の値と同じであれば、単純に、基準テストパタンの全パタンをパッケージ試験用テストパタンとしてパッケージ試験用テストプログラムを生成すればよい。

作成されたウェハ試験用テストプログラムは、ウェハ試験(S102)において用いられ、同じく作成されたパッケージ試験用テストプログラムは、パッケージ試験(S104)において用いられる。

このように、本発明にかかる半導体集積回路の試験方法によれば、テストプログラムを作成する際には、複数の試験のうち少なくとも一つの試験で用いられるテストパタン数について故障検出率とパタン数の対応から必要なパタン数を算出しているため、歩留りを殆ど低下させることなく、パタン数を削減することができ、試験時間を短縮化できる。

また、ウェハ試験とパッケージ試験で故障検出率を変更することにより、一つテストパタンから、故障検出率の異なるテストプログラムを作成するようにしているため、テストパタンの生成は、一度のみでよい。従って、テストパタンの生成時間を短縮することができる。また、本発明によれば、テストパタン生成を2度行なわないため、テストパタン生成に要する時間、テストパタンを記憶するためのディスクのハードウェアリソースの削減が可能となる。

この例では、特にパッケージ試験においては、従来と同程度の故障検出率で試験を行なうため、不良品が最終的に顧客に流出することはない。

尚、上述の例では、ウェハ試験とパッケージ試験を例示したが、これに限らず他の試験であってもよい。

S1 テストパタン生成

S21 テストパタン

S22 故障検出率とパタン数対応

S23 故障検出率設定

S3 テストプログラム生成

S41 ウェハ試験用テストプログラム

S42 パッケージ試験用テストプログラム

S21 テストパタン

S22 故障検出率とパタン数対応

S23 故障検出率設定

S3 テストプログラム生成

S41 ウェハ試験用テストプログラム

S42 パッケージ試験用テストプログラム

Claims (11)

- 半導体集積回路に対して少なくとも第1の試験と第2の試験を実行する半導体集積回路のテスト方法であって、

作成された基準テストパタンの、前記半導体集積回路に対する故障検出率とテストパタン数の対応を求めるステップと、

前記第1の試験に対する故障検出率を設定するステップと、

前記設定された故障検出率に基づいて、前記故障検出率とテストパタン数の対応を参照して、当該故障検出率を達成するためのテストパタン数を算出するステップと、

算出されたテストパタン数分の、前記基準テストパタンに含まれるテストパタンを第1の試験用テストパタンとして第1の試験用テストプログラムを作成するステップとを備えた半導体集積回路のテスト方法。 - 前記基準テストパタンを第2の試験用テストパタンとして第2の試験用テストプログラムを作成するステップをさらに備えたことを特徴とする請求項1記載の半導体集積回路のテスト方法。

- 前記第2の試験に対する故障検出率を設定するステップと、

前記設定された故障検出率に基づいて、前記故障検出率とテストパタン数の対応を参照して、当該第2の試験に対する故障検出率を達成するためのテストパタン数を算出するステップと、

算出されたテストパタン数分の、前記基準テストパタンに含まれるテストパタンを第2の試験用テストパタンとして第2の試験用テストプログラムを作成するステップとをさらに備えたことを特徴とする請求項1記載の半導体集積回路のテスト方法。 - 前記故障検出率とテストパタン数の対応は、当該故障検出率とテストパタン数を対応付けたテーブルにより記憶手段に格納されることを特徴とする請求項1記載の半導体集積回路装置のテスト方法。

- 前記第1の試験用テストプログラムにより、前記半導体集積回路に対して第1の試験を実行するステップと、

前記第2の試験用テストプログラムにより、前記半導体集積回路に対して第2の試験を実行するステップとをさらに備えたことを特徴とする請求項1記載の半導体集積回路のテスト方法。 - 前記第1の試験は、ウェハ試験であり、前記第2の試験はパッケージ試験であることを特徴とする請求項1記載の半導体集積回路のテスト方法。

- 半導体集積回路に対して第1の試験を実行するための第1の試験用テストプログラムと、第2の試験を実行するための第2の試験用テストプログラムを生成するためのテストプログラム生成プログラムであって、

当該テストプログラム生成プログラムは、コンピュータに対して、

基準テストパタンの、前記半導体集積回路に対する故障検出率とテストパタン数の対応を求めるステップと、

前記第1の試験に対する故障検出率の設定するステップと、

前記設定された故障検出率に基づいて、前記故障検出率とテストパタン数の対応を参照して、当該故障検出率を達成するためのテストパタン数を算出するステップと、

算出されたテストパタン数分の、前記基準テストパタンに含まれるテストパタンを第1の試験用テストパタンとして第1の試験用テストプログラムを作成するステップとを実行させるテストプログラム生成プログラム。 - 前記基準テストパタンを第2の試験用テストパタンとして第2の試験用テストプログラムを作成するステップをさらにコンピュータに実行させることを特徴とする請求項7記載のテストプログラム生成プログラム。

- 前記第2の試験に対する故障検出率を設定するステップと、

前記設定された故障検出率に基づいて、前記故障検出率とテストパタン数の対応を参照して、当該第2の試験に対する故障検出率を達成するためのテストパタン数を算出するステップと、

算出されたテストパタン数分の、前記基準テストパタンに含まれるテストパタンを第2の試験用テストパタンとして第2の試験用テストプログラムを作成するステップをさらにコンピュータに実行させることを特徴とする請求項7記載のテストプログラム生成プログラム。 - 前記故障検出率とテストパタン数の対応は、当該故障検出率とテストパタン数を対応付けたテーブルにより記憶手段に格納されることを特徴とする請求項7記載のテストプログラム生成プログラム。

- 前記第1の試験は、ウェハ試験であり、前記第2の試験はパッケージ試験であることを特徴とする請求項7記載のテストプログラム生成プログラム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004103522A JP2005291758A (ja) | 2004-03-31 | 2004-03-31 | 半導体集積回路のテスト方法及び半導体集積回路のテストプログラム生成プログラム |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004103522A JP2005291758A (ja) | 2004-03-31 | 2004-03-31 | 半導体集積回路のテスト方法及び半導体集積回路のテストプログラム生成プログラム |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005291758A true JP2005291758A (ja) | 2005-10-20 |

Family

ID=35324869

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004103522A Withdrawn JP2005291758A (ja) | 2004-03-31 | 2004-03-31 | 半導体集積回路のテスト方法及び半導体集積回路のテストプログラム生成プログラム |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005291758A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9666304B2 (en) | 2014-04-02 | 2017-05-30 | Samsung Electronics Co., Ltd. | Method of testing semiconductor memory device, test device, and computer readable recording medium for recording test program for semiconductor memory device |

-

2004

- 2004-03-31 JP JP2004103522A patent/JP2005291758A/ja not_active Withdrawn

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9666304B2 (en) | 2014-04-02 | 2017-05-30 | Samsung Electronics Co., Ltd. | Method of testing semiconductor memory device, test device, and computer readable recording medium for recording test program for semiconductor memory device |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20160378646A1 (en) | Method and system for generating functional test cases for software systems | |

| CN104950248B (zh) | 加速硬件木马触发的电路安全可测性设计方法及对硬件木马的检测方法 | |

| JP5762542B2 (ja) | 半導体プロセスレシピの検証のコンピュータ実装方法及び持続性コンピュータ可読媒体 | |

| US20060091928A1 (en) | Clock scaling circuit | |

| JP4908281B2 (ja) | 消費電力解析プログラム、消費電力解析方法及び消費電力解析装置 | |

| CN110032505A (zh) | 软件质量确定装置、软件质量确定方法和软件质量确定程序 | |

| US20110295536A1 (en) | Clock jitter analyzing method and apparatus | |

| JP2000235507A (ja) | システムの信頼性設計装置及び方法並びにシステムの信頼性設計用ソフトウェアを記録した記録媒体 | |

| JP4925200B2 (ja) | 半導体ウェハ検査装置 | |

| JP2005291758A (ja) | 半導体集積回路のテスト方法及び半導体集積回路のテストプログラム生成プログラム | |

| JP5179861B2 (ja) | 半導体装置 | |

| JP4496006B2 (ja) | 故障候補特定システムおよび故障候補特定方法 | |

| CN120066511A (zh) | 数据解析、协议解析器的生成方法、装置、设备及介质 | |

| JP6199813B2 (ja) | フォーマル検証装置およびプログラム | |

| JP2014241066A (ja) | 組込みシステムのテスト方法 | |

| JP4541196B2 (ja) | 故障検出改善装置、故障検出改善プログラム、故障検出改善方法 | |

| JP2011089833A (ja) | 半導体装置ならびに半導体装置のテストパターン生成方法 | |

| JP2011008620A (ja) | 検証装置、検証方法、及びプログラム | |

| JP3722690B2 (ja) | 信頼性検証装置 | |

| Heloue et al. | Efficient block-based parameterized timing analysis covering all potentially critical paths | |

| CN112433700B (zh) | 机器人应用的开发运行方法、装置、电子设备以及介质 | |

| CN120447958B (zh) | 一种基于低代码平台的逻辑检查方法、装置及计算机设备 | |

| JP6658297B2 (ja) | テストケース生成方法、テストケース生成プログラムおよびテストケース生成装置 | |

| US9274172B2 (en) | Selective test pattern processor | |

| JP2012033091A (ja) | 半導体回路およびそのテスト方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070110 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20070507 |