JP2004297048A - 集積回路、該集積回路を有する半導体表示装置及び集積回路の駆動方法 - Google Patents

集積回路、該集積回路を有する半導体表示装置及び集積回路の駆動方法 Download PDFInfo

- Publication number

- JP2004297048A JP2004297048A JP2004063307A JP2004063307A JP2004297048A JP 2004297048 A JP2004297048 A JP 2004297048A JP 2004063307 A JP2004063307 A JP 2004063307A JP 2004063307 A JP2004063307 A JP 2004063307A JP 2004297048 A JP2004297048 A JP 2004297048A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- active layer

- thin film

- film transistor

- integrated circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Abstract

【解決手段】 DRAMを有する集積回路であって、DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、薄膜トランジスタは、活性層と、活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、データに従って薄膜トランジスタのドレイン電圧を制御することで、チャネル形成領域における正孔の蓄積の有無を選択し、正孔の蓄積の有無を把握することでデータを読み出すことを特徴とする集積回路。

【選択図】 図2

Description

金属触媒を用いて結晶化された半導体膜は、例えば特開2001−5426号公報に記載されているように、結晶粒界において異なる二つの結晶粒が極めて整合性よく接合することが実証されている。即ち、結晶粒界において結晶格子が連続的に連なり、結晶欠陥等に起因するトラップ準位を非常に作りにくい構成となっている。その結果、電子正孔対の生成の核となる場所が少なく、電荷保持特性の高い薄膜トランジスタを実現することができ、特に多値化に伴う保持時間の短縮化を抑えることができる。る。そして、単結晶のトランジスタに比べて、然程工程を複雑化させずに、2つ目のゲート電極の作製工程を容易に追加することができる。従って、単結晶の場合と異なり、工程の複雑化によるコストの上昇を抑えることができる。

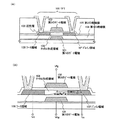

101 第1のゲート電極

102 第2のゲート電極

103 活性層

104 第1の絶縁膜

105 第2の絶縁膜

106 ソース領域

107 ドレイン領域

108 チャネル形成領域

Claims (16)

- DRAMを有し、

前記DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、

前記薄膜トランジスタは、活性層と、前記活性層を間に挟んで重なり合っている第1の電極及び第2の電極とを有することを特徴とする集積回路。 - DRAMを有し、

前記DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、

前記薄膜トランジスタは、活性層と、前記活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、

データに従って前記薄膜トランジスタのドレイン電圧を制御することで、前記チャネル形成領域における正孔の蓄積の有無を選択し、

前記正孔の蓄積の有無を把握することで前記データを読み出すことを特徴とする集積回路。 - 請求項2において、前記正孔の蓄積の有無は、前記薄膜トランジスタのドレイン電流または前記薄膜トランジスタの閾値電圧を用いて把握することを特徴とする集積回路。

- DRAMを有し、

前記DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、

前記薄膜トランジスタは、活性層と、前記活性層が有するチャネル形成領域を間に挟んで重なり合っている第1の電極及び第2の電極とを有しており、

前記チャネル形成領域に蓄積された正孔の量によって情報を格納し、前記正孔はインパクトイオン化によって前記チャネル形成領域に蓄積することを特徴とする集積回路。 - 請求項4において、前記メモリセルに格納された情報は、前記薄膜トランジスタのドレイン電流または閾値電圧を用いて読み出すことを特徴とする集積回路。

- DRAMを有し、

前記DRAMには、記憶素子を備えたメモリセルが複数設けられており、

前記記憶素子として、第1の電極と、第2の電極と、活性層と、第1の絶縁膜と、第2の絶縁膜とを有する薄膜トランジスタを用いており、

前記第1の電極は前記第1の絶縁膜を間に挟んで前記活性層と重なっており、

前記第2の電極は前記第2の絶縁膜を間に挟んで前記活性層と重なっており、

前記第1の電極と前記第2の電極は、前記活性層が有するチャネル形成領域を間に挟んで重なっていることを特徴とする集積回路。 - DRAMを有し、

前記DRAMには、第1の薄膜トランジスタ及び第2の薄膜トランジスタを備えたメモリセルが複数設けられており、

前記第1の薄膜トランジスタは、第1の電極と、第2の電極と、活性層と、第1の絶縁膜と、第2の絶縁膜とを有し、

前記活性層は、チャネル形成領域と、前記チャネル形成領域を間に挟んで存在するソース領域及びドレイン領域とを有し、

前記第1の電極は前記第1の絶縁膜を間に挟んで前記活性層と重なっており、

前記第2の電極は前記第2の絶縁膜を間に挟んで前記活性層と重なっており、

前記第1の電極と前記第2の電極は、前記チャネル形成領域を間に挟んで重なっており、

前記第2の薄膜トランジスタによって、前記ドレイン領域に与えられる電位が制御されていることを特徴とする集積回路。 - DRAMを有し、

前記DRAMには、薄膜トランジスタを備えたメモリセルが複数設けられており、

前記薄膜トランジスタは、第1の電極と、第2の電極と、活性層と、第1の絶縁膜と、第2の絶縁膜とを有し、

前記活性層は、チャネル形成領域と、前記チャネル形成領域を間に挟んで存在するソース領域及びドレイン領域とを有し、

前記第1の電極は前記第1の絶縁膜を間に挟んで前記活性層と重なっており、

前記第2の電極は前記第2の絶縁膜を間に挟んで前記活性層と重なっており、

前記第1の電極と前記第2の電極は、前記活性層を間に挟んで重なっており、

前記チャネル形成領域は、前記第1の電極及び前記第2の電極と重なる領域と、前記第1の電極と前記第2の電極のうち、前記第2の電極のみと重なる領域とを有しており、

前記第2の電極のみと重なる領域は、前記第1の電極及び前記第2の電極と重なる領域よりも、前記ドレイン領域側に存在することを特徴とする集積回路。 - 第1の電極、第2の電極及び活性層を有する薄膜トランジスタを各メモリセルに備えたDRAMと、前記薄膜トランジスタのドレイン電圧を制御する第1の手段と、前記第1の電極の電位を制御する第2の手段と、前記活性層のチャネル形成領域における正孔の蓄積量を把握する第3の手段とを有し、

前記第1の電極及び前記第2の電極は、前記活性層を間に挟んで重なり合っており、

前記第1の手段及び前記第2の手段を用いて前記電荷の蓄積量を制御することで、データを書き込み、前記第3の手段によって前記正孔の蓄積量を把握することで前記データを読み出すことを特徴とする集積回路。 - 第1の電極、第2の電極及び活性層を有する薄膜トランジスタを各メモリセルに備えたDRAMと、前記薄膜トランジスタのドレイン電圧を制御する第1の手段と、前記第1の電極の電位を制御する第2の手段と、前記活性層のチャネル形成領域における正孔の蓄積量を把握する第3の手段とを有し、

前記第1の電極及び前記第2の電極は、前記活性層を間に挟んで重なり合っており、

前記第1の手段及び前記第2の手段を用いて前記電荷の蓄積量を制御することで、3値以上のデータを書き込み、前記第3の手段によって前記正孔の蓄積量を把握することで前記データを読み出すことを特徴とする集積回路。 - 請求項9または請求項10において、

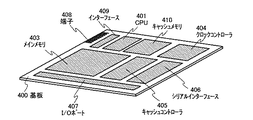

前記正孔の蓄積量は、前記薄膜トランジスタのドレイン電流、前記薄膜トランジスタの閾値電圧または前記活性層に含まれるソース領域とドレイン領域間の電圧を用いて把握することを特徴とする集積回路。 - DRAMを有する集積回路と、前記集積回路によって駆動が制御される画素部とを有し、

前記DRAMには、記憶素子を備えたメモリセルが複数設けられており、

前記記憶素子として、第1の電極と、第2の電極と、活性層と、第1の絶縁膜と、第2の絶縁膜とを有する第2の薄膜トランジスタを用いており、

前記第1の電極は前記第1の絶縁膜を間に挟んで前記活性層と重なっており、

前記第2の電極は前記第2の絶縁膜を間に挟んで前記活性層と重なっており、

前記第1の電極と前記第2の電極は、前記活性層が有するチャネル形成領域を間に挟んで重なっていることを特徴とする半導体表示装置。 - 各メモリセルに薄膜トランジスタを備えたDRAMを有し、

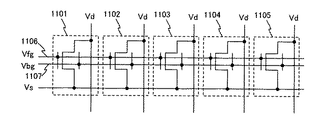

前記薄膜トランジスタは、活性層と、前記活性層を間に挟んで重なり合っている第1の電極及び第2の電極とを有し、

データの書き込みは、前記第2の電極の電位を制御することで前記薄膜トランジスタをオンにし、前記薄膜トランジスタのドレイン電圧を制御することで前記活性層が有するチャネル形成領域に電荷を蓄積し、前記電荷の蓄積量を前記第1の電極の電位で制御することによって行ない、

前記データの読み出しは、前記薄膜トランジスタのドレイン電流または閾値電圧を用いて行なうことを特徴とする集積回路の駆動方法。 - 各メモリセルに薄膜トランジスタを備えたDRAMを有し、

前記薄膜トランジスタは、活性層と、前記活性層を間に挟んで重なり合っている第1の電極及び第2の電極とを有し、

前記第2の電極の電位を制御することで前記薄膜トランジスタをオンにし、前記薄膜トランジスタのドレイン電圧を制御することで前記活性層が有するチャネル形成領域に電荷を蓄積し、前記電荷の蓄積量を前記第1の電極の電位で制御することによって、3値以上のデータの書き込みを行ない、

前記薄膜トランジスタのドレイン電流または閾値電圧を用いて前記データの読み出しを行なうことを特徴とする集積回路の駆動方法。 - 各メモリセルに薄膜トランジスタを備えたDRAMを有し、

前記薄膜トランジスタは、第1の電極と、第2の電極と、活性層と、第1の絶縁膜と、第2の絶縁膜とを有し、前記第1の電極は前記第1の絶縁膜を間に挟んで前記活性層と重なっており、前記第2の電極は前記第2の絶縁膜を間に挟んで前記活性層と重なっており、前記第1の電極と前記第2の電極は、前記活性層が有するチャネル形成領域を間に挟んで重なっており、

データの書き込みは、前記第2の電極の電位を制御することで前記薄膜トランジスタをオンにし、前記薄膜トランジスタのドレイン電圧を制御することで前記チャネル形成領域に電荷を蓄積し、前記電荷の蓄積量を前記第1の電極の電位で制御することによって行ない、

前記データの読み出しは、前記薄膜トランジスタのドレイン電流または閾値電圧を用いて行なうことを特徴とする集積回路の駆動方法。 - 各メモリセルに薄膜トランジスタを備えたDRAMを有し、

前記薄膜トランジスタは、第1の電極と、第2の電極と、活性層と、第1の絶縁膜と、第2の絶縁膜とを有し、前記第1の電極は前記第1の絶縁膜を間に挟んで前記活性層と重なっており、前記第2の電極は前記第2の絶縁膜を間に挟んで前記活性層と重なっており、前記第1の電極と前記第2の電極は、前記活性層が有するチャネル形成領域を間に挟んで重なっており、

前記第2の電極の電位を制御することで前記薄膜トランジスタをオンにし、前記薄膜トランジスタのドレイン電圧を制御することで前記活性層が有するチャネル形成領域に電荷を蓄積し、前記電荷の蓄積量を前記第1の電極の電位で制御することによって、3値以上のデータの書き込みを行ない、

前記薄膜トランジスタのドレイン電流または閾値電圧を用いて前記データの読み出しを行なうことを特徴とする集積回路の駆動方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004063307A JP2004297048A (ja) | 2003-03-11 | 2004-03-08 | 集積回路、該集積回路を有する半導体表示装置及び集積回路の駆動方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003065393 | 2003-03-11 | ||

| JP2003065314 | 2003-03-11 | ||

| JP2004063307A JP2004297048A (ja) | 2003-03-11 | 2004-03-08 | 集積回路、該集積回路を有する半導体表示装置及び集積回路の駆動方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011072882A Division JP2011205103A (ja) | 2003-03-11 | 2011-03-29 | 半導体表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004297048A true JP2004297048A (ja) | 2004-10-21 |

| JP2004297048A5 JP2004297048A5 (ja) | 2007-04-19 |

Family

ID=33424763

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004063307A Withdrawn JP2004297048A (ja) | 2003-03-11 | 2004-03-08 | 集積回路、該集積回路を有する半導体表示装置及び集積回路の駆動方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2004297048A (ja) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007019357A (ja) * | 2005-07-11 | 2007-01-25 | Hitachi Ltd | 半導体装置 |

| JP2007503678A (ja) * | 2003-05-13 | 2007-02-22 | イノヴァティーヴ シリコン, インコーポレーテッド | 半導体メモリ素子及び該素子を動作させる方法 |

| JP2007194267A (ja) * | 2006-01-17 | 2007-08-02 | Toshiba Corp | 半導体記憶装置 |

| JP2012212907A (ja) * | 2005-02-10 | 2012-11-01 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| KR20120129785A (ko) * | 2011-05-19 | 2012-11-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 기억 장치 및 그 제작 방법 |

| JP2017005271A (ja) * | 2009-06-30 | 2017-01-05 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| CN109246363A (zh) * | 2018-07-18 | 2019-01-18 | 中国科学院国家空间科学中心 | 一种dmd系统及其存取方法 |

| JP2020061581A (ja) * | 2010-08-27 | 2020-04-16 | 株式会社半導体エネルギー研究所 | 半導体装置 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08316337A (ja) * | 1995-05-12 | 1996-11-29 | Nec Corp | 半導体記憶装置 |

| JP2000223589A (ja) * | 1999-02-02 | 2000-08-11 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

| JP2002246571A (ja) * | 2001-02-15 | 2002-08-30 | Toshiba Corp | 半導体メモリ装置 |

| JP2002343886A (ja) * | 2001-03-15 | 2002-11-29 | Toshiba Corp | 半導体メモリ装置 |

| JP2003031693A (ja) * | 2001-07-19 | 2003-01-31 | Toshiba Corp | 半導体メモリ装置 |

| JP2003051599A (ja) * | 2001-05-24 | 2003-02-21 | Semiconductor Energy Lab Co Ltd | 半導体装置及び電子機器 |

-

2004

- 2004-03-08 JP JP2004063307A patent/JP2004297048A/ja not_active Withdrawn

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08316337A (ja) * | 1995-05-12 | 1996-11-29 | Nec Corp | 半導体記憶装置 |

| JP2000223589A (ja) * | 1999-02-02 | 2000-08-11 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

| JP2002246571A (ja) * | 2001-02-15 | 2002-08-30 | Toshiba Corp | 半導体メモリ装置 |

| JP2002343886A (ja) * | 2001-03-15 | 2002-11-29 | Toshiba Corp | 半導体メモリ装置 |

| JP2003051599A (ja) * | 2001-05-24 | 2003-02-21 | Semiconductor Energy Lab Co Ltd | 半導体装置及び電子機器 |

| JP2003031693A (ja) * | 2001-07-19 | 2003-01-31 | Toshiba Corp | 半導体メモリ装置 |

Cited By (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007503678A (ja) * | 2003-05-13 | 2007-02-22 | イノヴァティーヴ シリコン, インコーポレーテッド | 半導体メモリ素子及び該素子を動作させる方法 |

| US8604547B2 (en) | 2005-02-10 | 2013-12-10 | Semiconductor Energy Laboratory Co., Ltd. | Memory element and semiconductor device |

| JP2012212907A (ja) * | 2005-02-10 | 2012-11-01 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| JP2007019357A (ja) * | 2005-07-11 | 2007-01-25 | Hitachi Ltd | 半導体装置 |

| JP2007194267A (ja) * | 2006-01-17 | 2007-08-02 | Toshiba Corp | 半導体記憶装置 |

| US11417754B2 (en) | 2009-06-30 | 2022-08-16 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| JP2017005271A (ja) * | 2009-06-30 | 2017-01-05 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9985118B2 (en) | 2009-06-30 | 2018-05-29 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US20180233589A1 (en) | 2009-06-30 | 2018-08-16 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US10418467B2 (en) | 2009-06-30 | 2019-09-17 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US10790383B2 (en) | 2009-06-30 | 2020-09-29 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| JP2020061581A (ja) * | 2010-08-27 | 2020-04-16 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2021073738A (ja) * | 2010-08-27 | 2021-05-13 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR20120129785A (ko) * | 2011-05-19 | 2012-11-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 기억 장치 및 그 제작 방법 |

| KR102035988B1 (ko) | 2011-05-19 | 2019-10-25 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 기억 장치 및 그 제작 방법 |

| JP2012256877A (ja) * | 2011-05-19 | 2012-12-27 | Semiconductor Energy Lab Co Ltd | 半導体記憶装置およびその作製方法 |

| CN109246363A (zh) * | 2018-07-18 | 2019-01-18 | 中国科学院国家空间科学中心 | 一种dmd系统及其存取方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8049219B2 (en) | Integrated circuit, semiconductor device comprising the same, electronic device having the same, and driving method of the same | |

| JP7154448B2 (ja) | 半導体装置 | |

| JP7282134B2 (ja) | 半導体装置 | |

| JP6392824B2 (ja) | 半導体装置 | |

| TWI573250B (zh) | 半導體裝置 | |

| US8779433B2 (en) | Semiconductor device | |

| JP5912572B2 (ja) | 半導体装置及び半導体装置の作製方法 | |

| JP6379263B2 (ja) | 半導体装置 | |

| US8576636B2 (en) | Semiconductor device | |

| TW201250931A (en) | Semiconductor device | |

| WO2018197988A1 (ja) | 半導体装置、および半導体装置の作製方法 | |

| JP2004297048A (ja) | 集積回路、該集積回路を有する半導体表示装置及び集積回路の駆動方法 | |

| JP4666783B2 (ja) | 半導体装置の作製方法 | |

| US20220262858A1 (en) | Memory device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070302 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070302 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100108 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110222 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110329 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120105 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120215 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120904 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20121012 |