CN1146982C - 半导体器件的制造方法 - Google Patents

半导体器件的制造方法 Download PDFInfo

- Publication number

- CN1146982C CN1146982C CNB981167616A CN98116761A CN1146982C CN 1146982 C CN1146982 C CN 1146982C CN B981167616 A CNB981167616 A CN B981167616A CN 98116761 A CN98116761 A CN 98116761A CN 1146982 C CN1146982 C CN 1146982C

- Authority

- CN

- China

- Prior art keywords

- film

- mentioned

- make

- dielectric film

- amorphous

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims abstract description 77

- 239000004065 semiconductor Substances 0.000 title claims description 25

- 238000001039 wet etching Methods 0.000 claims abstract description 20

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims abstract description 16

- 239000001257 hydrogen Substances 0.000 claims abstract description 16

- 229910052739 hydrogen Inorganic materials 0.000 claims abstract description 16

- 238000010438 heat treatment Methods 0.000 claims abstract description 11

- 239000010410 layer Substances 0.000 claims description 31

- 238000005260 corrosion Methods 0.000 claims description 29

- 230000007797 corrosion Effects 0.000 claims description 29

- 239000013078 crystal Substances 0.000 claims description 27

- 238000004519 manufacturing process Methods 0.000 claims description 24

- 238000002955 isolation Methods 0.000 claims description 23

- 239000011229 interlayer Substances 0.000 claims description 18

- 239000003518 caustics Substances 0.000 claims description 11

- 238000002425 crystallisation Methods 0.000 claims description 8

- 230000008025 crystallization Effects 0.000 claims description 8

- QGZKDVFQNNGYKY-UHFFFAOYSA-O Ammonium Chemical compound [NH4+] QGZKDVFQNNGYKY-UHFFFAOYSA-O 0.000 claims description 7

- KRHYYFGTRYWZRS-UHFFFAOYSA-M Fluoride anion Chemical compound [F-] KRHYYFGTRYWZRS-UHFFFAOYSA-M 0.000 claims description 7

- 230000004888 barrier function Effects 0.000 claims description 6

- XKRFYHLGVUSROY-UHFFFAOYSA-N argon Substances [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 claims description 5

- 229910052786 argon Inorganic materials 0.000 claims description 5

- -1 argon ion Chemical class 0.000 claims description 5

- 229910052454 barium strontium titanate Inorganic materials 0.000 claims description 3

- 239000000758 substrate Substances 0.000 claims description 3

- 150000002500 ions Chemical class 0.000 claims 3

- 239000003990 capacitor Substances 0.000 abstract description 10

- DDFHBQSCUXNBSA-UHFFFAOYSA-N 5-(5-carboxythiophen-2-yl)thiophene-2-carboxylic acid Chemical compound S1C(C(=O)O)=CC=C1C1=CC=C(C(O)=O)S1 DDFHBQSCUXNBSA-UHFFFAOYSA-N 0.000 abstract description 9

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 abstract description 7

- 229910052710 silicon Inorganic materials 0.000 abstract description 7

- 239000010703 silicon Substances 0.000 abstract description 7

- 238000005516 engineering process Methods 0.000 description 18

- 238000005229 chemical vapour deposition Methods 0.000 description 11

- 238000001259 photo etching Methods 0.000 description 11

- 229910004298 SiO 2 Inorganic materials 0.000 description 6

- 238000009792 diffusion process Methods 0.000 description 6

- 230000003071 parasitic effect Effects 0.000 description 5

- 238000001020 plasma etching Methods 0.000 description 5

- 229910002367 SrTiO Inorganic materials 0.000 description 4

- 238000000151 deposition Methods 0.000 description 4

- 238000001312 dry etching Methods 0.000 description 4

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 4

- 229920005591 polysilicon Polymers 0.000 description 4

- 239000007787 solid Substances 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 238000010849 ion bombardment Methods 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 1

- 229910052788 barium Inorganic materials 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 229910052712 strontium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

- H01L28/55—Capacitors with a dielectric comprising a perovskite structure material

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Inorganic Chemistry (AREA)

- General Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Materials Engineering (AREA)

- Semiconductor Memories (AREA)

- Semiconductor Integrated Circuits (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

在把采用BST膜作为介电膜的电容器组合到DRAM的工艺中,用湿法腐蚀方法选择性地清除此膜以制作接触孔。为此,在硅片的整个表面上制作底电极然后制作非晶膜。在此膜上制作结晶态顶电极之后,执行灯加热以便仅仅使与电极相接触的区域结晶。然后用氢和氟化铵(1∶2)的溶液执行湿法腐蚀,这就使得有可能仅仅选择性地清除非晶区域。

Description

技术领域

本发明涉及到半导体衬底上制作有电容器的半导体器件的制造方法。

背景技术

诸如DRAM(动态随机存取存储器)的集成电路中组合有电容器的半导体器件已为人所知。

新近已提出用BaTiO3和SrTiO3作为电容器介电膜的技术。

例如,下列文献就公开了这种技术:

(1)S.Yamamichi et al.,1995 IEDM Technical Digest,p.119;

(2)K.P.Lee et al.,1995 IEDM Technical Digest,p.910;

(3)日本专利公开No.50395/95。

如上述文献(1)和(2)所公开的那样,用BaTiO3和SrTiO3作为介电膜改善了介电膜的绝缘性能,因而可为集成度高的半导体器件制作介电常数高的电容器。这一技术可望被千兆位规模大容量DRAM这样的半导体器件所采用。

而且,如文献(3)所公开的,当用二对或更多对顶电极和底电极以及一层BaTiO3介电膜制作二个或更多个电容器时,借助于制作一个不与顶电极及底电极接触的用来降低介电常数的非晶介电膜的区域,可降低寄生电容。

图12剖面图示出了常规DRAM主要部位的结构。

图12示出了用作器件隔离膜的二氧化硅膜1202以及作为硅片表面上MOS晶体管一部分的扩散层1203a和1203b。在片子1201的整个表面上,制作了层间隔离膜1204、氮化硅膜1205、例如由多晶硅制成的层间互连膜1206a以及由Ru、RuO2或Pt制成的导电膜。层间互连膜1206a和导电膜1206b组成底电极1206。

介电膜1207和顶电极1208层叠在导电膜1206b和氮化硅膜1205上。而层间隔离膜1209制作在顶电极1208和介电膜1207上。

在隔离膜1209表面上制作互连图形1210和1211。互连图形1210和扩散层1203b用层间互连膜1212连接,而互连图形1211和顶电极1208用层间互连膜1213连接。

为了在具有这种结构的DRAM中制作薄膜1212,必须制作一个穿透薄膜1204、1205、1207和1209的接触孔。

然而,当介电膜1207由BaTiO3膜或SrTiO3膜组成时,用诸如RIE(反应离子刻蚀)的干法腐蚀方法难以清除介电膜1207,因此难以制作接触孔。这是由于Ba、Sr、Ti形成的化合物和腐蚀气体组分(例如Cl)的熔点高,亦即挥发性低。

若代之以使用湿法腐蚀,则可容易地清除由BaTiO3和SrTiO3组成的介电膜1207。但由于湿法腐蚀的各向异性小,故对于集成度高的DRAM难以使用湿法腐蚀。

上述文献(3)中公开的技术,只改变了含有BaTiO3和其它非晶组分的介电膜的一部分,它能够减小寄生电容的介电常数,但不能完全消除寄生电容。这一技术仍然解决不了难以制作上述接触孔的问题。

虽然此处使用DRAM作为例子来进行解释,但对于集成度高的半导体器件都有这种问题。

发明内容

本发明的目的是提供一种用湿法腐蚀方法方便而准确地清除半导体器件电容器介电膜的方法。

为此目的,本发明包含下列步骤:(a)制作一个底电极,此底电极带有制作在半导体衬底的层间隔离膜中的层间互连膜,以及制作在上述层间隔离膜上的与层间互连膜相接触的导电图形;(b)在上述层间隔离膜和上述导电图形上制作非晶或晶体介电膜;(c)在上述介电膜上制作覆盖部分介电膜的顶电极;(d)改变上述介电膜,使至少上述顶电极下方区域成为晶体而其它区域成为非晶;以及(e)用湿法腐蚀方法,采用一种对非晶的腐蚀速率高于对晶体的腐蚀速率的腐蚀剂,清除上述介电膜非晶区域的一部分或全部。

若采用这一制造方法,则由于使用了湿法腐蚀,腐蚀将很容易,而且由于所用的腐蚀剂对非晶的腐蚀速率高于对晶体的腐蚀速率而可能得到足够各向异性的腐蚀。

附图说明

以下参照附图来描述本发明的进一步目的和优点:

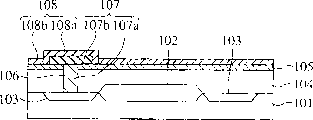

图1和图2是工艺剖面图,示出了根据第一实施例的半导体器件的制造方法;

图3指出了灯加热时间与根据第一实施例的介电膜的结晶速度之间的关系;

图4和图5描述了第一实施例的效果;

图6-9是工艺剖面图,示出了根据第二实施例的半导体器件的制造方法;

图10和图11工艺剖面图,示出了根据第四实施例的半导体器件的制造方法;而

图12剖面图示出了常规半导体器件主要部位的结构。

具体实施方式

以下参照附图,用举例的方法来描述本发明应用于DRAM的实施例.图中各组成部分的尺寸、形状和位置关系只是初略的表示以有利于理解本发明,而下面描述中的数值条件只是一些例子。

第一实施例

下面参照图1-5来描述根据本发明第一实施例的制造方法。

图1和图2是工艺剖面图,示出了根据第一实施例的DRAM的制造方法。

(1)首先,在硅片101表面上制作将成为器件隔离膜的SiO2膜102和将成为MOS晶体管或相似器件一部分的扩散层103。用CVD(化学气相沉积)之类的方法,在此片子101上制作例如700-1000nm厚的将成为层间隔离膜的SiO2膜和例如10-100nm厚的非晶SiN膜105。

然后用普通光刻之类的技术在SiO2膜104和SiN膜105中制作接触孔106。再用溅射之类的方法,在整个表面上沉积多晶硅,并借助于在表面上执行回腐蚀而制作层间互连膜107a。在此层上,用CVD之类的沉积工艺和图形化工艺,制作含有势垒层和Ru层、RuO2层、Ir层、IrO2层、Pt层中至少一种层(晶体膜)的导电层107b,使总厚度为例如20-100nm。这一导电层107b和上述的互连膜107a组成底电极107。

然后用CVD之类的方法,在整个表面上制作厚度例如为20-100nm的BST(钛酸锶钡)膜108。借助于设定沉积温度为500℃或更低,可将BST膜108制成晶体膜上的结晶体和非晶膜上的非晶体。在本实施例中,107b层是结晶体,而膜105是非晶体,因此,晶体BST膜108a被制作在107b层上,而非晶BST膜108b被制作在膜105上(见图1(A))。若沉积温度被设定为500℃或更高,则导电膜107b和SiN膜105上的BST膜都是结晶体。

(2)用溅射、CVD或其它方法,在BST膜108的整个表面上制作至少由Ru、RuO2、Ir、IrO2、Pt之一构成的膜109,使总厚度为例如30-200nm(见图1(B))。

(3)借助于用普通光刻之类的方法对膜109进行图形化,制作顶电极110(见图1(C))。

(4)用灯在例如400℃的温度下,对整个表面进行加热。借助于这一处理,只有与电极110相接触的上述非晶膜108b的区域结晶并成为晶体膜108c(见图1(D))。

图3示出了灯加热处理时间与BST膜108b结晶速度之间的关系。在图3中,横坐标表示灯加热时间,纵坐标表示BST膜108b的X射线衍射峰强度(任意值)。

如图3中的a所示,即使用灯加热,不与电极110相接触的BST膜108b的部位也不结晶。另一方面,如图3中的b所示,用400℃灯加热大约60秒钟,与电极110相接触的部位却完全结晶了。

这样,在非晶膜108b上制作晶体膜110之后,灯加热就使得有可能在与晶体膜110相接触的区域中选择性地使非晶膜结晶。

(5)只有BST膜108b的非晶区域被湿法腐蚀清除(见图2(A))。此处只要对非晶的腐蚀速率高于对晶体的腐蚀速率,任何腐蚀剂都可以使用,而本实施例中采用了氢和铵的氟化物(1∶2)溶液。

图4示出了采用氢和铵的氟化物(1∶2)溶液作为BST膜腐蚀剂时的腐蚀速率,其中横坐标表示氢和铵氟化物(1∶2)的浓度,而纵坐标表示腐蚀速率。

如图4所示,当采用氢和铵的氟化物(1∶2)溶液作为腐蚀剂时,不管浓度如何,晶体的腐蚀速率(见a)都低于非晶的腐蚀速率(见b)。

图5示出了当采用氢和铵的氟化物(1∶2)溶液作为BST膜的腐蚀剂时的晶体腐蚀速率对非晶腐蚀速率的比率,其中横座标表示氢和铵的氟化物(1∶2)的浓度,而纵坐标表示腐蚀速率之比率。

如图5所示,采用氢和铵的氟化物(1∶2)溶液作为腐蚀剂,使得非晶的腐蚀速率成为晶体腐蚀速率的三倍或更大。这就使得有可能在清除非晶膜108b时,将晶体膜108c中的腐蚀深度控制在108膜厚度的1/3以内。

(6)然后用RIE之类,只清除SiN膜105的暴露区域(见图2(B))。

(7)用CVD之类的方法,在整个表面上制作作为层间隔离膜的SiO2膜111(见图2(C))。

(8)最后,用普通光刻之类的技术,在SiO2膜111上制作接触孔112和穿通孔113。并且在用溅射之类的方法于整个表面上淀积多晶硅之后,借助于采用普通光刻之类的图形化,制作层间互连膜114、115和互连图形116、117。

在本实施例中,清除SiN膜105之后,制作了接触孔112(见上述工艺(6)和(8)),但在制作接触孔112的腐蚀过程中,无需清除膜105就可在膜105中制作另一窗口。

于是,在本实施例中,在非晶膜108b上制作电极110之后执行灯加热,以便只使与电极110相接触的非晶部位结晶,并在后续的腐蚀工序中,使用氢和氟化铵(1∶2)的溶液执行湿法腐蚀。这使得有可能选择性地清除非晶膜108b(亦即不制作电极110处的那部分BST膜)。

由于不制作电容器的区域中的BST膜可被完全清除,故本方法也可有效地防止寄生电容的产生。

第二实施例

下面参照图6和图7来描述根据本发明第二实施例的制造方法。

图6和图7工艺剖面图示出了根据第二实施例的DRAM的制造方法。

(1)首先,以与第一实施例相同的方法,在硅片601的表面上相继制作作为器件隔离层的SiO2膜602、扩散膜603、作为层间隔离膜的SiO2膜604以及非晶SiN膜605,然后用普通光刻之类的技术在SiO2膜604和SiN膜605中制作接触孔606。借助于制作结构与第一实施例相同的层间互连膜607a和导电膜607b而形成底电极。

然后用与第一实施例相同的方法,制作与电极607相接触的区域为晶体而其它区域为非晶的BST膜608,从而形成结构与第一实施例相同的顶电极。然后以与第一实施例相同的方式执行灯加热,以便形成与电极609相接触的区域608a为晶体而其它区域608b为非晶的BST膜。再在整个表面上制作SiO2膜610(见图6(A))。

(2)用普通干法腐蚀之类的方法制作穿通孔611,使部分非晶膜608b暴露出来(见图6(B))。

(3)用湿法腐蚀方法清除非晶膜608b的暴露部位(见图6(C))。在本实施例中,也可用氢和氟化铵(1∶2)的溶液作为腐蚀剂。

(4)在清除SiN膜605的暴露部位之后,用普通干法腐蚀之类的技术,清除所有的膜610(见图7(A))。

(5)用CVI之类的方法,在整个表面上制作将成为层间隔离膜的SiO2膜612(见图7(B))。

(6)最后,用普通光刻之类的技术,在膜612中制作接触孔613和穿通孔614。并在用溅射之类的方法于整个表面上淀积多晶硅之后,用普通光刻之类的图形化方法制作层间互连膜615、616以及互连图形617、618。

这样,在本实施例中,在非晶BST膜608b上制作电极610之后,也执行灯加热,以便只使与电极609相接触的那部分BST膜结晶,并在后续的腐蚀工序中,用氢和氟化铵(1∶2)的溶液执行湿法腐蚀。因此,在本实施例中,只有BST膜608b所希望的区域能够被简单的工序清除。

第三实施例

下面参照图8和图9来描述根据本发明的第三实施例的制造方法。

图8和图9剖面图示出了根据第三实施例的DRAM的制造方法。

(1)首先,用与第一和第二实施例相同的方法,在硅片801表面上相继制作将成为器件隔离膜的SiO2膜802、扩散层803、将成为层间隔离膜的SiO2膜804以及非晶SiN膜805,然后用普通光刻之类的技术,在膜804和膜805中制作接触孔806。借助于制作结构与第一实施例相同的层间互连膜807a和导电膜807b而形成底电极807。

然后用CVD方法、反应溅射方法或其它方法,在整个表面上制作厚度例如为20-100nm的BST膜808。在本实施例中,借助于将淀积温度设定为500℃或更高,此BST膜808被制成晶体。

用溅射方法、CVD方法或其它方法,在BST膜808的整个表面上制作至少由Ru、RuO2、Ir、IrO2、Pt之一制成的膜809,使总厚度为例如30-200nm。

然后用CVD之类的方法,在整个表面上制作SiO2层810(见图8(A))。

(2)借助于用普通图形化之类的技术对层809和810进行图形化,制作顶电极811和掩模图形812(见图8(B))。

(3)用例如10-20kV的加速电压和1×1013-1×1015的剂量,将氩离子之类注入到整个表面。这就在BST膜808的暴露区域上施加了离子轰击,从而形成非晶区域808a(见图8(C))。

(4)用湿法腐蚀方法,仅仅清除非晶区域808a(见图9(A))。在本实施例中,任何腐蚀剂只要对非晶的腐蚀速率高于对晶体的腐蚀速率,例如氢和氟化铵(1∶2)的溶液,也都可以使用。

(5)用RIE之类的方法清除膜805的暴露部分(见图9(B))。

(6)在清除掩模图形812之后,制作将成为层间隔离膜的SiO2膜813。并在于此膜813中制作接触孔814和穿通孔815之后,用与第一实施例相同的方法制作层间互连膜816和817以及互连图形818和819(见图9(C))。

在本实施例中,接触孔814是在清除805膜之后制作的(见上述工序(6)和(8)),但在腐蚀制作接触孔814的过程中,无需清除膜805,也可以在膜805中制作另一个窗口。

这样,在本实施例中,氩离子被注入到晶体BST膜808的特定区域以将此区域改变成非晶态,并在后续的腐蚀工序中,用氢和氟化铵(1∶2)的溶液执行湿法腐蚀。这使得有可能选择性地清除BST膜808的非晶区域808a。

由于在不制作电容器的区域中的BST膜可被完全地清除,故此方法也可有效地防止寄生电容的产生。

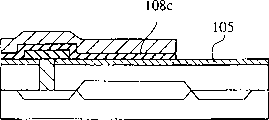

第四实施例

下面参照图10和图11来描述根据本发明第四实施例的制造方法。

图10和图11工艺剖面图示出了根据第四实施例的DRAM的制造方法。

(1)首先,用与上述各实施例相同的方法,在硅片1001表面上相继制作将成为器件隔离膜的SiO2膜1002、扩散膜1003、将成为层间隔离膜的SiO2膜1004以及非晶SiN膜1005,然后用普通光刻之类的技术,在SiO2、膜1004和SiN膜1005中制作接触孔1006。并借助于制作结构与第一实施例相同的层间互连膜1007a和导电层1007b而形成底电极1007。

然后制作与第三实施例相同的晶体BST膜1008。用溅射方法、CVI方法或其它方法制作至少由Ru、RuO2、Ir、IrO2、Pt之一构成的层,使总厚度为例如30-200nm,再用溅射方法制作与第一实施例相似的顶电极1009。

然后用CVD之类的方法在整个表面上制作SiO2层1010(见图10(A))。

(2)用普通干法腐蚀技术制作穿通孔1011,使一部分BST膜1008暴露出来(见图10(B))。

(3)以例如10-20kV的加速电压和1×1013-1×1015的剂量,将氩离子之类注入到整个表面中。这就在晶体膜1008的暴露部位施加了离子轰击,从而使该区域变成非晶态。

湿法腐蚀仅仅清除膜1008的非晶区域(见图10(C))。在本实施例中,氢和氟化铵(1∶2)的溶液也可用作腐蚀剂。

(4)用RIE之类的方法清除膜1005的暴露部位,然后完全清除SiO2膜1010(见图11(A))。

(5)在整个表面上制作将成为层间隔离膜的SiO2膜1011(见图11(B))。

(6)最后,用普通光刻之类的技术,在SiO2膜1011中制作接触孔1012和穿通孔1013。用溅射之类的方法在整个表面上淀积多晶硅之后,借助于用普通光刻之类的方法进行图形化而制作层间互连膜1014和1015以及互连图形1016和1017。

这样,在本实施例中,氩离子被注入到晶体BST膜1008的特定区域中,将此部分改变成非晶态,并在后续的腐蚀工序中执行采用氢和氟化铵(1∶2)溶液的湿法腐蚀。因此,在本实施例中,仅仅BST膜的所希望的区域可被简单的工艺清除。

如上所述,本发明使得有可能用湿法腐蚀方法容易而精确地清除待要制作在半导体器件中的电容器的介电膜。

Claims (9)

1.一种半导体器件的制造方法,它包含下列步骤:

(a)制作一个底电极,此底电极带有制作在半导体衬底的层间隔离膜中的层间互连膜,以及制作在上述层间隔离膜上的与层间互连膜相接触的导电图形;

(b)在上述层间隔离膜和上述导电图形上制作非晶或晶体介电膜;

(c)在上述介电膜上制作覆盖部分介电膜的顶电极;

(d)改变上述介电膜,使至少上述顶电极下方区域成为晶体而其它区域成为非晶;以及

(e)用湿法腐蚀方法,采用一种对非晶的腐蚀速率高于对晶体的腐蚀速率的腐蚀剂,清除上述介电膜非晶区域的一部分或全部。

2.根据权利要求1的半导体器件制造方法,其中所述的步骤(b)是制作上述介电膜的步骤,使上述层间隔离膜上的区域成为非晶,而上述的步骤(d)是借助于加热此顶电极而只使上述顶电极下方的上述介电膜结晶的步骤。

3.根据权利要求2的半导体器件制造方法,其中所述的加热是灯加热。

4.根据权利要求1的半导体器件制造方法,其中所述的步骤(b)是制作上述晶体介电膜的步骤,而上述的步骤(d)是在制作覆盖上述顶电极的掩膜之后注入离子的步骤,使上述介电膜的离子注入区改变成非晶态。

5.根据权利要求4的半导体器件制造方法,其中所述的离子注入是氩离子注入。

6.根据权利要求1的半导体器件制造方法,其中所述的步骤(e)是用湿法腐蚀方法清除上述介电膜非晶区域的一部分或全部,以便在上述层间隔离膜中制作穿通孔的步骤。

7.根据权利要求1的半导体器件制造方法,其中所述的上述步骤(a)制作的导电图形带有为接触上述层间互连膜而制作的势垒层以及制作在此势垒层上的由Ru、RuO2、Ir、IrO2和Pt之一组成的层。

8.根据权利要求1的半导体器件制造方法,其中所述的上述步骤(b)制作的介电层是钛酸锶钡。

9.根据权利要求1的半导体器件制造方法,其中所述的步骤(e)是用氢和铵的氟化物(1∶2)来执行湿法腐蚀的步骤。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP28571597A JP3979711B2 (ja) | 1997-10-17 | 1997-10-17 | 半導体装置の製造方法 |

| JP285715/97 | 1997-10-17 | ||

| JP285715/1997 | 1997-10-17 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1215228A CN1215228A (zh) | 1999-04-28 |

| CN1146982C true CN1146982C (zh) | 2004-04-21 |

Family

ID=17695096

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB981167616A Expired - Fee Related CN1146982C (zh) | 1997-10-17 | 1998-07-31 | 半导体器件的制造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US5940677A (zh) |

| JP (1) | JP3979711B2 (zh) |

| KR (1) | KR100326910B1 (zh) |

| CN (1) | CN1146982C (zh) |

| TW (1) | TW383487B (zh) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6258655B1 (en) * | 1999-03-01 | 2001-07-10 | Micron Technology, Inc. | Method for improving the resistance degradation of thin film capacitors |

| US20050191765A1 (en) * | 2000-08-04 | 2005-09-01 | Cem Basceri | Thin film capacitor with substantially homogenous stoichiometry |

| US6617266B2 (en) | 2001-04-12 | 2003-09-09 | Applied Materials, Inc. | Barium strontium titanate annealing process |

| US6593181B2 (en) | 2001-04-20 | 2003-07-15 | International Business Machines Corporation | Tailored insulator properties for devices |

| KR20030013123A (ko) * | 2001-08-07 | 2003-02-14 | 삼성전자주식회사 | 커패시터를 갖는 반도체 장치 및 그의 제조 방법 |

| KR20030057204A (ko) * | 2001-12-28 | 2003-07-04 | 동부전자 주식회사 | 절연막의 습식식각 또는 화학적 건식식각을 이용한 반도체커패시터 제조방법 |

| JP3621695B2 (ja) * | 2002-07-29 | 2005-02-16 | 株式会社東芝 | 半導体装置及び素子形成用基板 |

| US6734057B2 (en) * | 2002-09-27 | 2004-05-11 | Infineon Technologies Ag | Method of patterning capacitors and capacitors made thereby |

| US6784478B2 (en) * | 2002-09-30 | 2004-08-31 | Agere Systems Inc. | Junction capacitor structure and fabrication method therefor in a dual damascene process |

| CN102403227B (zh) * | 2010-09-17 | 2013-10-23 | 中芯国际集成电路制造(北京)有限公司 | 台阶状硅锗源/漏结构的制造方法 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0516031A1 (en) * | 1991-05-29 | 1992-12-02 | Ramtron International Corporation | Stacked ferroelectric memory cell and method |

| JPH0750395A (ja) * | 1993-08-06 | 1995-02-21 | Hitachi Ltd | 半導体記憶装置およびその製造方法 |

| US5555486A (en) * | 1994-12-29 | 1996-09-10 | North Carolina State University | Hybrid metal/metal oxide electrodes for ferroelectric capacitors |

-

1997

- 1997-10-17 JP JP28571597A patent/JP3979711B2/ja not_active Expired - Fee Related

-

1998

- 1998-05-19 US US09/081,562 patent/US5940677A/en not_active Expired - Lifetime

- 1998-05-20 TW TW087107785A patent/TW383487B/zh not_active IP Right Cessation

- 1998-07-31 CN CNB981167616A patent/CN1146982C/zh not_active Expired - Fee Related

- 1998-10-12 KR KR1019980042539A patent/KR100326910B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| JPH11121695A (ja) | 1999-04-30 |

| KR100326910B1 (ko) | 2002-09-05 |

| TW383487B (en) | 2000-03-01 |

| US5940677A (en) | 1999-08-17 |

| KR19990037030A (ko) | 1999-05-25 |

| JP3979711B2 (ja) | 2007-09-19 |

| CN1215228A (zh) | 1999-04-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1122306C (zh) | 制造半导体器件电容器的方法 | |

| CN1129171C (zh) | 半导体器件的电容器的形成方法 | |

| US6509277B1 (en) | Method of manufacturing semiconductor integrated circuit device having insulatro film formed from liquid containing polymer of silicon, oxygen, and hydrogen | |

| CN1177357C (zh) | 具有最小覆盖电容的金属氧化物半导体场效应晶体管 | |

| CN1220257C (zh) | 半导体器件及其制造方法 | |

| US5721171A (en) | Method for forming controllable surface enhanced three dimensional objects | |

| CN1202728A (zh) | 一种半导体器件及制造该半导体器件的方法 | |

| CN1146982C (zh) | 半导体器件的制造方法 | |

| CN1641843A (zh) | 半导体器件及其制造方法 | |

| CN1181529C (zh) | 半导体装置的电容器的制造方法 | |

| CN1172361C (zh) | 半导体装置的电容器的制造方法 | |

| CN1203534C (zh) | 减轻由于金属氧化物陶瓷的移动物质扩散造成的金属氧化物陶瓷退化 | |

| CN1269202C (zh) | 电容器及其制造方法 | |

| CN1163965C (zh) | 半导体存储器件的电容器及其制造方法 | |

| CN1280392A (zh) | 半导体存储元件的电容器及其制造方法 | |

| CN1122311C (zh) | 具有金属硅化物薄膜的半导体器件及制造方法 | |

| CN1334966A (zh) | 减少移动离子从金属氧化物陶瓷向衬底的扩散 | |

| CN1202004A (zh) | 集成电路制造方法 | |

| CN1770392A (zh) | 形成铁电膜的方法及使用其形成电容器和存储器件的方法 | |

| CN1311896A (zh) | 制造叠层超晶格材料和制造包括该材料的电子器件的低温处理方法 | |

| CN1266749C (zh) | 半导体器件的制造方法 | |

| US11978626B2 (en) | Method of treating target film and method of manufacturing semiconductor device | |

| CN2879423Y (zh) | 具有电容器的半导体器件 | |

| JPH08335680A (ja) | 高密度、高誘電率メモリ装置内の内部電極形成方法並びに装置 | |

| CN1153280C (zh) | 嵌入式动态随机存储器的制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C19 | Lapse of patent right due to non-payment of the annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |