CN100565807C - 在电荷擦除光学曝光工具中去除吸波长的气体的方法 - Google Patents

在电荷擦除光学曝光工具中去除吸波长的气体的方法 Download PDFInfo

- Publication number

- CN100565807C CN100565807C CNB2007101287719A CN200710128771A CN100565807C CN 100565807 C CN100565807 C CN 100565807C CN B2007101287719 A CNB2007101287719 A CN B2007101287719A CN 200710128771 A CN200710128771 A CN 200710128771A CN 100565807 C CN100565807 C CN 100565807C

- Authority

- CN

- China

- Prior art keywords

- wavelength

- electric charge

- integrated circuit

- gas

- wafer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims abstract description 52

- 230000003287 optical effect Effects 0.000 title claims abstract description 13

- 230000008569 process Effects 0.000 claims abstract description 42

- 230000005855 radiation Effects 0.000 claims abstract description 39

- 239000007789 gas Substances 0.000 claims description 12

- 238000010521 absorption reaction Methods 0.000 claims description 7

- 239000011261 inert gas Substances 0.000 claims description 7

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 claims description 4

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 4

- 239000000203 mixture Substances 0.000 claims description 3

- 229910052786 argon Inorganic materials 0.000 claims description 2

- 239000001307 helium Substances 0.000 claims description 2

- 229910052734 helium Inorganic materials 0.000 claims description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 claims description 2

- 229910052757 nitrogen Inorganic materials 0.000 claims description 2

- 238000009825 accumulation Methods 0.000 abstract description 34

- 230000035508 accumulation Effects 0.000 description 32

- 235000012431 wafers Nutrition 0.000 description 27

- 238000012545 processing Methods 0.000 description 12

- 230000000694 effects Effects 0.000 description 9

- 238000004519 manufacturing process Methods 0.000 description 9

- 239000000463 material Substances 0.000 description 8

- 238000005516 engineering process Methods 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 238000001228 spectrum Methods 0.000 description 6

- 239000000523 sample Substances 0.000 description 5

- 238000013461 design Methods 0.000 description 4

- 239000010453 quartz Substances 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 3

- 238000004140 cleaning Methods 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 230000006870 function Effects 0.000 description 3

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 3

- 230000003595 spectral effect Effects 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- 238000000137 annealing Methods 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 239000011248 coating agent Substances 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000011109 contamination Methods 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 230000004927 fusion Effects 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 208000013935 Electric injury Diseases 0.000 description 1

- 239000011149 active material Substances 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 125000004429 atom Chemical group 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 230000006378 damage Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 230000001066 destructive effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 239000002784 hot electron Substances 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 229910052753 mercury Inorganic materials 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 150000003254 radicals Chemical class 0.000 description 1

- 230000008672 reprogramming Effects 0.000 description 1

- 230000027756 respiratory electron transport chain Effects 0.000 description 1

- 238000006748 scratching Methods 0.000 description 1

- 230000002393 scratching effect Effects 0.000 description 1

- 230000011218 segmentation Effects 0.000 description 1

- 239000002023 wood Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66825—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a floating gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/268—Bombardment with radiation with high-energy radiation using electromagnetic radiation, e.g. laser radiation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28158—Making the insulator

- H01L21/28167—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation

- H01L21/28176—Making the insulator on single crystalline silicon, e.g. using a liquid, i.e. chemical oxidation with a treatment, e.g. annealing, after the formation of the definitive gate conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- High Energy & Nuclear Physics (AREA)

- Ceramic Engineering (AREA)

- Optics & Photonics (AREA)

- Electromagnetism (AREA)

- Health & Medical Sciences (AREA)

- Toxicology (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Crystallography & Structural Chemistry (AREA)

- General Chemical & Material Sciences (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Solid State Image Pick-Up Elements (AREA)

Abstract

一种用于通过光学手段减少集成电路中的电荷累积的过程包括将所述集成电路或者其中部分暴露在宽带辐射源下。该过程有效地减少了在制造集成电路中产生的电荷累积。

Description

本案系母案(申请日:2002.12.02,申请号:02823776.5,发明名称:用于擦除在制造集成电路过程中累积的电荷的方法和设备)的分案。

发明背景

本公开文件总体上涉及用于制造集成电路的过程和设备,更具体说,涉及用于通过光学手段去除或减少在制造集成电路器件期间所产生的电荷累积的过程和设备。

在工业上已经提出或者使用了多种采用非易失性存储器(NVM)阵列的集成电路。非易失性存储器阵列通常基于浮栅技术。这种技术指的是通过氧化物层或电介质层将电荷转移到导电的浮栅,然后在该浮栅处存储或者去除电荷。采用浮栅技术的非易失性存储器阵列器件的实例是可擦可编程只读存储器(“EPROM”)器件,该器件可被读取、擦除和写入(即可编程)。EPROM一般使用浮栅场效应晶体管,该晶体管具有取决于在该浮栅上电荷存在或缺失的双态。通过将电荷即电子存储在浮栅中,从而将数据存储在非易失性存储器器件中。

可以获得多种EPROM。在传统的和最基本的形式中,EPROM通过电学的方法进行编程,并且通过暴露在紫外光下进行擦除。这些类型的EPROM通常指的是紫外可擦除可编程只读存储器(“UVEPROM”)。通过在UVEPROM晶体管的漏极和源极之间通以高电流同时给栅极施加正电势来编程UVEPROM。在栅极上的正电势吸引从漏极到源极的沟道电流的高能(即热)电子,在该沟道电流中电子转移或者注入浮栅中并且在浮栅中被俘获。基于这种技术的UVEPROM被设计为通过光学手段擦除它们的电荷。在这种方法中,当需要重新编程时可以通过将该器件暴露在紫外光下来除去存储的电荷。

在图1中示出UVEPROM的一个实例。该器件统一标为10,它包括形成在n型衬底16上的源区12和漏区14。栅氧化物膜18形成在位于源区12和漏区14之间沟道之上的衬底表面上。由p型多晶硅等构成的浮栅电极20典型地布置在栅氧化物膜18上。因为UVEPROM被设计为通过光学手段来擦除它们的电荷,所以在制造过程中可以通过将这些器件暴露在紫外光下来去除在制造过程中产生的任意电荷累积。

另一种形式的EPROM是可通过电学手段擦除的可编程只读存储器,该存储器还被称作为“EEPROM”或“E2PROM”。通常是借助于已知的Fowler-Nordheim隧道效应来电学地编程和擦除EEPROM。在工作期间,这些器件并不是被设计为通过光学手段进行擦除。因此,在制造集成电路期间可能产生危险的电荷累积。

还有另一种形式的EPROM是“快可擦编程只读存储器”,它使用热电子进行编程,并且使用Fowler-Nordheim隧道效应现象进行擦除。可以以“快速”或者批量方式来擦除快可擦编程只读存储器,其中阵列中的所有单元或部分阵列可以使用Fowler-Nordheim隧道效应同时进行擦除。快可擦编程只读存储器通常称作是“闪存单元”或者“闪存器件”。类似于EEPROM器件,在制造快可擦编程只读存储器器件期间所产生的电荷累积并没有被设计成通过光学手段进行擦除。如在图2中所示,实例性的EEPROM或者快可擦编程只读存储器器件通常包括布置在浮栅20上的附加导电栅层22。

在制造集成电路期间,众所周知的是,在诸如EPROM器件的浮栅上(如果可以应用的话)以及/或者在该集成电路的其他区域上会产生不希望的电荷累积。如果这些电荷累积没有被除去或者被中和,则这些电荷累积可能导致高电压并对电路造成电损伤。通常在制造集成电路的众多处理步骤中的一步或者多步中容易产生电荷累积。例如,在退火处理期间、金属抛光或刻蚀处理期间、在通孔和焊盘形成步骤之后等都可能产生电荷累积。集成电路典型地使用3到5层导电金属层,这些金属层在制造期间包括大约5个到大约7个对于电荷累积有贡献的处理步骤。在制造器件时擦除这些电荷累积是重要的。

当前的制造过程致力于擦除在制造集成电路期间产生的电荷累积,特别是通过使用诸如在上面提到的EEPROM和闪存的非易失性存储器器件的集成电路来擦除电荷累积。可以使用电探针来提供与电路的临时连接以便施加所需要的电压,从而实现对电荷积累的擦除。然而,这种方法耗费时间并且对于大批量的生产来讲不是切实可行的。使用电探针的擦除时间典型地大于大约10分钟时间/每个晶片,并且根据特定电路设计可能大于1小时/每个晶片。

通过将该集成电路暴露在窄带辐射源下也可除去电荷累积。当前的用于除去电荷的过程使用水银电极灯,该灯产生波长大约为254nm的窄带波谱。水银灯发射高能光子,高能光子穿过集成电路堆从而将能量传给存储的电子和其他存在的电荷。这些赋能电子克服先前限制电子和其他电荷的能量壁垒,在集成电路内部电子和电子空穴或正电荷之间重新复合。在窄带UV光下的曝光还增加了在该集成电路其他区域上的电荷迁移率。

在UVEPROM中,通过在窄带辐射源下曝光来除去电荷累积通常被认为是有效的,这是由于这种类型的器件在最初就被配置成用于在工作期间通过光学手段进行擦除。布置在浮栅上的氧化物层或者电介质层对于由水银灯发射的波长大约为254nm的窄带辐射来说是透明的。

然而,使用窄带光源的当前处理过程对于除去其他类型集成电路器件中的电荷累积来说是无效的,这些器件诸如包含布置在浮栅电极(例如EEPROM,闪存等)上的导电(例如金属)栅层的器件,或者其他的包含在浮栅存储器单元上的多层金属线的器件。如图2中所示,导电栅层22的存在起到了阻挡入射辐射到达下面浮栅电极20的作用,这大大降低了它的擦除效率。结果,当前的曝光工具需要长的曝光时间(即根据特定的IC设计对于每个晶片需要大约大于1或者2个小时)来减少电荷累积。

曝光时间直接取决于光源的强度(以及其他因素)。在曝光工具中所使用的当前人工光源的光源强度被限制在(例如)平均每平方厘米约30毫瓦功率(mW/cm2),当灯是新的时候可以达到大约60mW/cm2。然而,所使用的窄带光源产生包括离散和窄谱线的发射信号,在每条谱线处具有低的总输出强度。尽管在某种程度上可以改变现有技术光源的波谱输出,但是得到的谱线并不包含偏离原发射(约254nm)的很大的功率或光强度输出。

用于减少电荷累积的当前光源依赖于使用内部电极的灯泡技术。已知的是:使用内部电极的灯泡强度会大大减少灯泡的使用寿命。用户常常在替换这些灯泡之前需要将强度降低到(相比较于新的灯泡)50%以便使替换的成本最小化。结果,灯泡随着时间越来越恶化,将导致生产量的减少。使用现有技术灯泡所产生的其他问题包括灯的长冷却时间(达到几个小时),以至替换灯泡常常需要相当长时间来使灯泡冷却。另外,这些类型的灯泡在灯关闭之后重新点亮时呈现出高的故障率。最终,许多集成电路制造商典型地在灯泡的非使用期间不关闭灯泡,这样对于灯泡来讲大大影响了可使用的工作寿命并增加了操作成本。

使用现有技术光源除了没有效率之外,而且当前的曝光工具具有相对大的台面面积,这需要相当大的占地面积。另外,这种曝光工具典型地要求将晶片手动装载到工具中。这个过程是今天在加工中仅剩的时常需要人工操作的步骤。人工操作有严重的缺陷,可能会造成晶片断裂或者晶片损伤(例如划伤)、需要额外的劳动投资、有可能造成晶片污染并且不易提供用于自动化的晶片跟踪。

显然需要一种用于减少在生产集成电路期间的电荷累积的改进过程,特别是对于那些使用非易失性存储器器件的集成电路更是如此。先进的设计规则进一步缩小了用于制造集成电路的图形。同时,因为还缩小了线和空间的最小尺寸,所以添加了更多的金属线层,其中的金属线更为靠近。最终结果是:对于给定窄带波长的光来说更难穿透IC结构和擦除在制造过程期间所产生的电荷累积。

发明内容

在此所公开的是用于除去在生产集成电路期间所产生的电荷累积的过程和设备。在一个实施方案中,一种用于除去生产集成电路期间的电荷累积的过程包括将该集成电路曝光在一种强度的宽带辐射图案下一段时间,所述的强度和时间可以有效地减少在制造集成电路期间累积的电荷。

在另一个实施方案中,一种用于减少制造集成电路期间在浮栅电极上的电荷累积的过程包括:将该集成电路放置在处理室中,其中该集成电路包括浮栅电极;并且在将该集成电路曝光在一种强度的宽带辐射图案下一段时间,所述的强度和时间可以有效地减少在制造集成电路期间累积的电荷。

优选地是,该宽带辐射图案包括至少一种大约小于280nm的波长,FWHM大约大于10nm。

通过下面附图和详细说明解释了上面说明的特征和其他特征。

附图说明

现在参考附图,其中相同的附图标记表示相同的部分:

图1说明现有技术的UVEPROM器件;

图2说明现有技术的EEPROM器件;

图3说明一种实例性的、用于擦除制造集成电路期间的电荷累积的曝光工具;

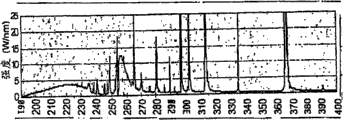

图4图解说明用于电荷擦除的一种无电极微波驱动灯泡的宽带波谱输出;以及

图5图解说明在EEPROM中存储的电荷是作为暴露在宽带辐射光源的曝光时间的函数。

具体实施方式

一种用于减少在制造集成电路期间的电荷累积的过程包括将该集成电路曝光在一种强度的宽带辐射图案下一段时间,所述的强度和时间可以有效地减少在制造集成电路期间累积的电荷。在一种优选的实施方案中,在使用非易失性存储器器件制造集成电路期间使用这种过程。在制造过程的各个阶段可以使用该过程,并且优选地是,在已知对于电荷累积有贡献的处理步骤期间实施该过程,诸如在等离子体灰化或者刻蚀处理之后、退火处理、在通孔和焊盘形成步骤之后等。该过程优选地是在形成至少一个导电层之后使用。

虽然不想受到原理的限制,但是已知的是诸如在上面提到的某些处理对于电荷累积是有贡献的。出于解释目的,制造导电的金属层的布线图案通常包括等离子体调解的刻蚀处理,其中将气体混合物暴露于能量源并且分离该气体以产生等离子体。该等离子体含有活性物质,这些物质包括高能原子、自由基、离子、电子和光子。这些物质,根据它们的浓度和能级,可能造成在集成电路内部的不同程度的电荷累积。

如在此所使用的,术语“宽带”辐射源指的是具有至少一种波长带的辐射源,该波长带具有大约大于10nm的半峰宽,更加优选地是该半峰宽大约大于15nm,甚至更加优选地是大约大于20nm。术语半峰宽(FWHM)在此定义为当降低到峰值的一半时或者是最大值的一半时跨越波长曲线的宽度。

图3说明一种实例性的曝光工具100,其适于减少在制造集成电路期间的电荷累积。该曝光工具100一般包括处理室112和辐射源室113。该处理室112包括夹盘114,在夹盘上布置晶片116。可选地是,可以调节夹盘114或者处理室112以提供在处理期间用于加热晶片的热源(没有示出)。一种任选加热的实例是一种加热的夹盘。曝光工具100进一步包括辐射源118和布置在辐射源118与夹盘114之间的板120。对管道122进行布置,使其与处理室112之间有液体流动,从而净化该室112并调节处理室112内部的压力等。曝光工具100还可包括其他的特征以用于在晶片表面提供均匀曝光,所述附加特征诸如在授予Matthews等人的专利号为No.4885047的美国专利中所描述的结构特征,其整体引入作为参考。对于晶片表面的均匀曝光将减少对于过度曝光的需要,以确保减少具有非易失性存储器阵列的晶片的所有区域中的电荷累积,从而增加生产量。

板120起到隔离辐射源118与下面处理的晶片116的作用。有利地使用板120来消除从辐射源118到晶片116的特殊污染,将辐射源118与处理室112隔离以提供单独的通道,并且另外(如果存在的话)允许使用气体来冷却辐射源和微波腔(没有示出)。该板还允许在没有干扰光源工作的情况下,在处理室中使用特殊选择的处理气体。采用这种方式,可以布置管道使其与辐射源室113和处理室112之间有液体流动以便净化包含在那里的吸收气体环境,将在下面进一步详细地讨论。

板120优选地是由在工作环境下不退化的物质制成的。优选地,板120是由对于希望辐射具有足够的透过率的石英制造的,以用于减少电荷累积。可以使用除了石英之外的其他材料,只要这些材料具有上面的特征。例如,可能优选地是将晶片暴露在具有小于220nm波长的辐射下以擦除电荷。这种石英材料的实例是市场上可获得的、由位于West Berlin,NJ的Dynasil公司生产的、商标名为Dynasil1000的石英材料。通过传统的安装方式将板120安装在处理室112中,该处理室可能包括适当的衬垫。优选地是,板120和夹盘114是圆盘形状,以便与被处理的晶片116的形状一致。优选地是辐射源118发射具有至少一种大约小于280nm的波长的宽带辐射图案,其波长优选地为大约180nm到大约280nm,更加优选地是大约180nm到大约250nm。至少一种优选的波长的FWHM是大约大于10nm,更加优选的是大于20nm。

在优选的实施方案中,辐射源118使用微波驱动的无电极灯泡和分段的反射镜来给晶片提供充分均匀的宽带辐射图案。在Wood等人的美国专利No 5541475中公开了适当的微波驱动无电极灯泡。已经发现了一种性能良好的示例性微波驱动无电极的灯泡,该灯泡可从市场上获得,商标名为HL灯泡,部件编号203662,由位于Rockville,Maryland的Axcelis Technologies公司生产。在图4中示出由这种宽带紫外辐射源所产生的波谱,应当注意的是存在相当数量的小于280nm的波谱成份。

该过程包括将晶片116装载到处理室112中,并且将晶片116暴露在由辐射源118发射的宽带辐射图案下。优选地是,将处理室112配置成实现晶片116的自动处理,而不用手动处理晶片116。在优选的实施方案中,该过程包括使用一种或者多种惰性气体来除去在处理室112内部的空气从而净化处理室112,然后将晶片116暴露在宽带辐射图案下。用于净化处理室112空气的适当的惰性气体包括,但不局限于氮气、氩气、氦气、包括至少一种上述气体的组合物等。

空气包括大约21%的氧气。众所周知,氧气吸收波长小于大约200nm的辐射并且反应形成臭氧等产物。该臭氧的产生反过来加大波长吸收,臭氧开始吸收波长高达250nm的辐射并且继续吸收较低的波长。最终降低了处理效率。在将晶片116暴露在宽带辐射图案之前净化处理室112和辐射源室113,从而减少波长吸收并因此提高处理效率。

将集成电路暴露给宽带辐射具有许多优点。例如使得建设性和破坏性的干涉效应最小化。如果集成电路内部的单层膜厚度是波长的整数倍或者半整数倍则产生干涉,并且可能导致有过多或者过少的照明光穿过而到达较低的层。对于使用单波长的窄带辐射源来讲,该干涉效应可能严重限制或者降低用于减少电荷累积的效率。作为对照地是,来自宽带辐射的干涉效应被最小化,这是由于它使用了包括多个波长的宽带辐射图案,所述的多个波长不受干涉的影响,即对于给定的膜厚度来讲是非破坏性的或者是非建设性的。另外,对于各种大小的功能部件来讲,宽带辐射的使用确保了:在宽带辐射图案下,各种波长中的至少一些波长在该功能部件附近(避免阴影)发生折射,并且穿透到典型地布置着存储器阵列的层堆底部。另外,已经发现:可以通过将晶片暴露在较短的波长(小于280nm)来大大提高处理效率。较短波长比较长波长具有较高的光子能量,并且因此能够给电荷施加更多的能量,这样就允许电荷(例如电子)更有效地克服表征电荷累积的能量壁垒。

实例1

在这个实例中,将晶片暴露在由FUSION PS3曝光工具所产生的宽带辐射图案下。该曝光工具装备有HL灯泡并且产生在图4中所示的波谱图形。FUSION PS3曝光工具是在市场上可获得的、由位于Rockville,MD的Axcelis Technologies公司生产的曝光工具。每个晶片包括多个管芯,所述多个管芯包含非易失性存储器(NVM或者闪存)结构,使用电探针将该结构预先编程到充电状态。该非易失性存储器结构包括导电的栅极,导电的栅极布置在基于250nm设计规则的浮栅电极上面。在微波电路中供给磁控管的电功率是4500瓦(W),微波电路到灯泡的传输效率降低到大约67%(即对于灯泡大约是3000瓦)。

对于不同的晶片组改变曝光时间,并将栅极上的电荷绘制成时间的函数。由存储的电荷所产生的电压在编程状态下被归一化为“1”。根据制造商的规格,对于可接受的“擦除”状态,可接受的界限被预定为归一化的编程状态的百分比,并通过在图5中所示的上面水平虚线来限定。图5说明非易失性存储器结构的电荷状态是暴露给宽带辐射源的曝光时间的函数。

该结果清楚表明:对于非易失性存储器结构,将存储的电荷降低到可接受的水平是在1分钟以内发生的,这在生产量和电荷累积的减少效率方面表现出相当大的商业优势。从延长的曝光以及将电荷累积维持在可接受的界限以下的效应可以看出,该过程窗口是强壮的。也就是说,过度曝光或者过度擦除都不是问题。应当注意的是,充电的状态不能完全从浮栅中通过光学手段除去。降低电荷累积到0需要诸如使用电探针等的电输入端。然而,这种低压电平充电状态(如在图5中所示的上限)可被接受作为“擦除状态”,或者更具体说被接受作为相对于“电擦除状态”的“UV-擦除状态”。如在前面所讨论的,使用电探针来减少电荷累积非常费时并且在生产中不是切实可行的。

虽然了参考实例性的实施方案说明本发明,但是本领域的技术人员应当理解,在没有背离本发明范围的情况下可以进行各种改变和等效替换。例如,虽然解释和说明的是EEPROM阵列,但所公开的同样适用于其他在单元中使用浮栅的非易失性存储器阵列,并且甚至适用于非存储器集成电路或者集成电路的非存储器部分。另外,在没有背离本发明的基本范围的情况下可以进行许多改变来根据本发明的教导调整特定的情况或者材料。因此,本发明的目的不是限制所公开的特定实施方案作为执行本发明的最好的模式,本发明将包括所有落入附带权利要求书范围内的实施方案。

被要求保护的是。

Claims (3)

1.一种用于在电荷擦除光学曝光工具中去除吸收180nm到200nm的波长的气体的方法,其中该光学曝光工具包括与处理室进行光通信的辐射源室,该方法包括:

使用惰性气体来净化该辐射源室,所述惰性气体对于被周围预先净化的气体吸收的波长来说是透明的;以及

使用惰性气体来净化该处理室,所述惰性气体对于180nm到200nm的波长来说是透明的。

2.根据权利要求1的方法,其中该惰性气体选自包括氮气、氦气、氩气、以及包含至少一种上述气体的组合物的组。

3.根据权利要求1的方法,其中吸收波长的气体包括空气。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/000772 | 2001-11-30 | ||

| US10/000,772 US6605484B2 (en) | 2001-11-30 | 2001-11-30 | Process for optically erasing charge buildup during fabrication of an integrated circuit |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028237765A Division CN100336205C (zh) | 2001-11-30 | 2002-12-02 | 用于擦除在制造集成电路过程中累积的电荷的方法和设备 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101145520A CN101145520A (zh) | 2008-03-19 |

| CN100565807C true CN100565807C (zh) | 2009-12-02 |

Family

ID=21692962

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2007101287719A Expired - Fee Related CN100565807C (zh) | 2001-11-30 | 2002-12-02 | 在电荷擦除光学曝光工具中去除吸波长的气体的方法 |

| CNB028237765A Expired - Fee Related CN100336205C (zh) | 2001-11-30 | 2002-12-02 | 用于擦除在制造集成电路过程中累积的电荷的方法和设备 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028237765A Expired - Fee Related CN100336205C (zh) | 2001-11-30 | 2002-12-02 | 用于擦除在制造集成电路过程中累积的电荷的方法和设备 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US6605484B2 (zh) |

| EP (1) | EP1451868A2 (zh) |

| JP (1) | JP4784851B2 (zh) |

| KR (1) | KR20040068925A (zh) |

| CN (2) | CN100565807C (zh) |

| AU (1) | AU2002346599A1 (zh) |

| WO (1) | WO2003049182A2 (zh) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6787484B2 (en) * | 2002-12-17 | 2004-09-07 | Taiwan Semiconductor Manufacturing Co., Ltd | Method of reducing visible light induced arcing in a semiconductor wafer manufacturing process |

| US20050250346A1 (en) * | 2004-05-06 | 2005-11-10 | Applied Materials, Inc. | Process and apparatus for post deposition treatment of low k dielectric materials |

| US20060251827A1 (en) * | 2005-05-09 | 2006-11-09 | Applied Materials, Inc. | Tandem uv chamber for curing dielectric materials |

| US20060249175A1 (en) * | 2005-05-09 | 2006-11-09 | Applied Materials, Inc. | High efficiency UV curing system |

| CN103364706B (zh) * | 2013-07-26 | 2017-03-08 | 上海华虹宏力半导体制造有限公司 | 验收测试装置及一次性可编程器件的验收测试方法 |

| CN103820772B (zh) * | 2014-02-12 | 2016-07-06 | 清华大学 | 去除pecvd装置的电荷的系统及其控制方法 |

| US9576801B2 (en) * | 2014-12-01 | 2017-02-21 | Qualcomm Incorporated | High dielectric constant/metal gate (HK/MG) compatible floating gate (FG)/ferroelectric dipole non-volatile memory |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US541475A (en) * | 1895-06-25 | Crank-planer | ||

| US4179627A (en) * | 1977-06-10 | 1979-12-18 | Tom Swift Enterprises, Inc. | Electrical apparatus |

| JPH0212195B2 (zh) * | 1980-05-30 | 1990-03-19 | Gee Aa Oo G Fuyuuru Automatsuioon Unto Oruganizatsuioon Mbh | |

| US4665426A (en) * | 1985-02-01 | 1987-05-12 | Advanced Micro Devices, Inc. | EPROM with ultraviolet radiation transparent silicon nitride passivation layer |

| US4885047A (en) | 1986-08-11 | 1989-12-05 | Fusion Systems Corporation | Apparatus for photoresist stripping |

| JPH01310577A (ja) | 1988-06-08 | 1989-12-14 | Seiko Instr Inc | 半導体不揮発性メモリ |

| JPH04152519A (ja) * | 1990-10-16 | 1992-05-26 | Oki Electric Ind Co Ltd | 半導体装置の製造方法 |

| US5170091A (en) * | 1990-12-10 | 1992-12-08 | Ultraviolet Energy Generators, Inc. | Linear ultraviolet flash lamp with self-replenishing cathode |

| US5117312A (en) * | 1991-01-04 | 1992-05-26 | Fusion Systems Corporation | Apparatus including concave reflectors and a line of optical fibers |

| ATE194748T1 (de) * | 1992-09-30 | 2000-07-15 | Fusion Lighting Inc | Elektrodenlose lampe mit drehender birne |

| US5712715A (en) * | 1992-12-23 | 1998-01-27 | Lucent Technologies Inc. | Optical transmission system with spatially-varying Bragg reflector |

| US5541475A (en) | 1993-04-16 | 1996-07-30 | Fusion Lighting, Inc. | Electrodeless lamp with profiled wall thickness |

| FR2707796B1 (fr) * | 1993-06-30 | 1995-10-06 | Sgs Thomson Microelectronics | Procédé de gravure sous plasma d'une couche conductrice sur une tranche de silicium avec interposition d'une couche isolante mince. |

| US5530247A (en) * | 1994-08-05 | 1996-06-25 | Trw Inc. | Millimeter wave imager device using pyroelectric effect |

| US5587330A (en) * | 1994-10-20 | 1996-12-24 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US5633424A (en) * | 1994-12-29 | 1997-05-27 | Graves; Clinton G. | Device and methods for plasma sterilization |

| US5656521A (en) * | 1995-01-12 | 1997-08-12 | Advanced Micro Devices, Inc. | Method of erasing UPROM transistors |

| US5648669A (en) * | 1995-05-26 | 1997-07-15 | Cypress Semiconductor | High speed flash memory cell structure and method |

| JP3502498B2 (ja) * | 1996-01-22 | 2004-03-02 | 大日本スクリーン製造株式会社 | 基板処理装置 |

| JP3872535B2 (ja) * | 1996-03-14 | 2007-01-24 | 株式会社オーク製作所 | ワークの電荷の消去中和装置 |

| EP0848422B1 (en) * | 1996-12-16 | 2002-03-27 | STMicroelectronics S.r.l. | Process for the manufacture of floating-gate non-volatile memories |

| US6081334A (en) * | 1998-04-17 | 2000-06-27 | Applied Materials, Inc | Endpoint detection for semiconductor processes |

| US6369420B1 (en) * | 1998-07-02 | 2002-04-09 | Silicon Storage Technology, Inc. | Method of self-aligning a floating gate to a control gate and to an isolation in an electrically erasable and programmable memory cell, and a cell made thereby |

| US6091652A (en) * | 1998-12-11 | 2000-07-18 | Lsi Logic Corporation | Testing semiconductor devices for data retention |

| US6207989B1 (en) | 1999-03-16 | 2001-03-27 | Vantis Corporation | Non-volatile memory device having a high-reliability composite insulation layer |

| US6350651B1 (en) * | 1999-06-10 | 2002-02-26 | Intel Corporation | Method for making flash memory with UV opaque passivation layer |

| US6350699B1 (en) * | 2000-05-30 | 2002-02-26 | Sharp Laboratories Of America, Inc. | Method for anisotropic plasma etching using non-chlorofluorocarbon, fluorine-based chemistry |

-

2001

- 2001-11-30 US US10/000,772 patent/US6605484B2/en not_active Expired - Fee Related

-

2002

- 2002-12-02 KR KR10-2004-7008048A patent/KR20040068925A/ko not_active Application Discontinuation

- 2002-12-02 EP EP02784670A patent/EP1451868A2/en not_active Withdrawn

- 2002-12-02 JP JP2003550278A patent/JP4784851B2/ja not_active Expired - Fee Related

- 2002-12-02 AU AU2002346599A patent/AU2002346599A1/en not_active Abandoned

- 2002-12-02 CN CNB2007101287719A patent/CN100565807C/zh not_active Expired - Fee Related

- 2002-12-02 CN CNB028237765A patent/CN100336205C/zh not_active Expired - Fee Related

- 2002-12-02 WO PCT/US2002/038310 patent/WO2003049182A2/en active Application Filing

-

2003

- 2003-02-18 US US10/248,779 patent/US6803319B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US6605484B2 (en) | 2003-08-12 |

| US20030104644A1 (en) | 2003-06-05 |

| JP2005512324A (ja) | 2005-04-28 |

| CN100336205C (zh) | 2007-09-05 |

| EP1451868A2 (en) | 2004-09-01 |

| CN101145520A (zh) | 2008-03-19 |

| AU2002346599A1 (en) | 2003-06-17 |

| US6803319B2 (en) | 2004-10-12 |

| JP4784851B2 (ja) | 2011-10-05 |

| CN1596467A (zh) | 2005-03-16 |

| WO2003049182A2 (en) | 2003-06-12 |

| KR20040068925A (ko) | 2004-08-02 |

| US20030180976A1 (en) | 2003-09-25 |

| WO2003049182A3 (en) | 2003-09-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI549163B (zh) | 減少摻質擴散之表面穩定化製程 | |

| TWI598704B (zh) | 用於改良之元件完整性之光阻剝除處理 | |

| CN100565807C (zh) | 在电荷擦除光学曝光工具中去除吸波长的气体的方法 | |

| US20050156286A1 (en) | Method for improving a physical property defect value of a gate dielectric | |

| TW201921514A (zh) | 選擇性氮化製程所用的方法與設備 | |

| JP2008515200A (ja) | フラッシュランプアニール装置 | |

| JP4437641B2 (ja) | 熱処理装置 | |

| US5776811A (en) | Simplified process for fabricating flash eeprom cells | |

| US6828623B1 (en) | Floating gate memory device with homogeneous oxynitride tunneling dielectric | |

| JP2005072291A (ja) | 熱処理装置および熱処理装置の洗浄方法 | |

| CN100437913C (zh) | 蚀刻金属氧化物半导体栅极构造的氮氧化方法 | |

| US6991987B1 (en) | Method for producing a low defect homogeneous oxynitride | |

| US6627501B2 (en) | Method of forming tunnel oxide layer | |

| JP4891272B2 (ja) | フラッシュメモリの製造方法 | |

| JP3872535B2 (ja) | ワークの電荷の消去中和装置 | |

| US6128232A (en) | Method for erasing a non-volatile memory array | |

| TW550793B (en) | Pre-erase manufacturing method | |

| JPH05251428A (ja) | 絶縁膜形成方法およびこの絶縁膜を用いた不揮発性半導体装置 | |

| Mastrapasqua | Low voltage flash memory by use of a substrate bias | |

| TWI397072B (zh) | 非揮發性記憶體之固有啟始電壓的測定方法 | |

| US6939766B1 (en) | Method for fabricating a flash memory device | |

| KR100542395B1 (ko) | 낸드 플래시 소자의 제조 방법 | |

| KR100235105B1 (ko) | 복다중 금속 산화 질화 산화막 반도체 플래쉬 아이피롬 셀 | |

| KR100678295B1 (ko) | 반도체 소자 제조 방법 | |

| EP1046173B1 (en) | Method of erasing a non-volatile memory |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20091202 Termination date: 20141202 |

|

| EXPY | Termination of patent right or utility model |