CN100419701C - 针对故障状态的自主总线重新配置的方法和装置 - Google Patents

针对故障状态的自主总线重新配置的方法和装置 Download PDFInfo

- Publication number

- CN100419701C CN100419701C CNB2004800261966A CN200480026196A CN100419701C CN 100419701 C CN100419701 C CN 100419701C CN B2004800261966 A CNB2004800261966 A CN B2004800261966A CN 200480026196 A CN200480026196 A CN 200480026196A CN 100419701 C CN100419701 C CN 100419701C

- Authority

- CN

- China

- Prior art keywords

- fault

- signal

- electronic unit

- signal conductor

- bus

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/16—Error detection or correction of the data by redundancy in hardware

- G06F11/20—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements

- G06F11/2002—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements where interconnections or communication control functionality are redundant

- G06F11/2005—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements where interconnections or communication control functionality are redundant using redundant communication controllers

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/16—Error detection or correction of the data by redundancy in hardware

- G06F11/20—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L12/00—Data switching networks

- H04L12/28—Data switching networks characterised by path configuration, e.g. LAN [Local Area Networks] or WAN [Wide Area Networks]

- H04L12/40—Bus networks

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Quality & Reliability (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Debugging And Monitoring (AREA)

- Small-Scale Networks (AREA)

- Dc Digital Transmission (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

Abstract

公开了一种允许具有在信号导线有故障的信号总线的电子系统以降低的性能加以操作的方法与装置。在信号总线上把数据块从第一电子单元传递至第二电子单元。传输序列使用所有无故障信号导线,使用完成传输所需的最小数目的节拍发送数据块。

Description

技术领域

总体上讲,本发明涉及一种具有通过信号总线耦接的部件的电子系统。更具体地讲,本发明涉及一种信号总线中的一个或多个信号导线上具有故障的信号总线。

背景技术

一般情况下,电子系统包括通过信号导线互连的多个电子单元。通常,这些由铜、铝或其它这样的材料形成的信号导线为导电路径。此外,光纤也可以传导信号。

例如,半导体芯片驱动和接收电耦接到使用引线接合或倒装(flip)芯片技术模块上的信号导线的信号。通常,还使用铜管脚、焊柱或其它手段把这些模块耦接到印刷线路板(PWB)信号导线。PWB上的信号导线把各个模块彼此连接,并且把信号传送至PWB的边缘连接器或电缆连接器。PWB边缘连接器和电缆连接器用于使用背板或电缆把一个PWB与另一个PWB互相连接。即使是在半导体芯片中,极细的电导线也能够在芯片上的电路和逻辑单元之间传送信号。

把一组逻辑上相关的信号导线称为信号总线。例如,通过信号总线把处理器芯片连接于存储器控制芯片,所述信号总线具有规定数目的信号导线,数据基本上并行地在这些信号导线上流动。即,如果使用8位总线把处理器芯片耦接到存储器控制,则处理器芯片基本上同时发送8位(一个字节)的数据,信号总线的每一信号导线上一位。例如,处理器芯片一次一个字节地把地址发送到该实例的存储器控制芯片上,并且一次一个字节地从存储器控制芯片接收返回的数据。

经济和物理的因素限制了可用于互连电子元件的信号导线的数目。例如,模块和卡之间的每一互连,成本大约为一美分。对价格高度敏感的电子单元上的大量互连是不合理的。而且,当把众多的部件安装在PWB上时,大量的互连在PWB中强加了额外的布线层,提高了PWB的成本。当使用众多的互连时,电子单元之间的电缆连接变得十分昂贵,并且较厚,从可靠性角度而言,众多的电缆导线很难加以处理,成本很高,而且十分麻烦。在一定程度上,不仅成本变高、不可靠,而且物理上也不可能添加更多的互连。

通常,一个电子单元必须把数据块发送到另一个电子单元。数据块常常是相当大的。例如,在某些现代计算机系统中的高速缓冲器行是64字节或者128字节长。如果把该块(即高速缓冲器行)在8字节的信号总线上发送,则分别需要8或16个总线周期(节拍)完成该传递。在许多应用中,在具有更少信号导线的信号总线上传递更大的数据块。

今天的电子系统被希望可靠地操作。商务运作所依赖的商用计算机系统的故障时间可能导致难以估量的销售金钱损失。另外,这样的故障时间还可能伤害客户,使他们转向竞争对手。许多商用系统被指望每周7天、每天24小时(即连续地)运行。导致高峰使用运行中断的无法预料的故障是非常严重的问题。通常,如果发生故障,这样的商用系统的用户也希望连续的操作,即使是性能略有下降。然后,用户可以计划在更方便的时候纠正故障。军事系统也严重依赖电子系统,而且更倾向于被粗鲁地使用和面对恶劣的环境。在作战环境下,对于用户来说,电子系统的总故障很可能会导致严重的后果。在作战情况下,备用件(新的电缆、新的PWB等)可能是无法得到的。因此,在许多军事应用中,以略下降的性能继续运作是人们更加希望的。

信号总线具有一个或多个与信号总线相关的信号导线,典型的,信号总线具有8的倍数条信号导线。通常,单个的额外信号导线带有奇偶性校验位。例如,具有8条信号导线的信号总线还具有带有奇偶性校验的第九(奇偶性校验)条信号导线。发送单元上的奇偶性校验生成器产生关于奇偶性校验的逻辑值,以致总线上逻辑“1”的数目总为奇数(或者,在另一个实施例中,总为偶数)。接收单元上的奇偶性校验检验器检验所接收的逻辑“1”的数目(即“奇”数或“偶”数)是否为所期望的。这样的奇偶性校验生成/检验系统可以检测信号总线上的单个故障,但不能纠正故障。当检测到奇偶性校验错误时,信号总线不再能够用于传输数据。可以使用额外的信号导线实现“错误纠正代码”(ECC),在许多应用中,ECC可以纠正单个故障并检测两个故障。ECC的使用导致了与额外信号导线相关的额外开销。循环冗余码(CRC)还使用用于发现和解决传输数据过程中的错误的另一种技术。

许多现代的电子系统具有执行“连线测试”规程的能力,以确定信号总线中的故障细节。例如,第一电子单元驱动信号导线上的逻辑“1”和“0”的预先确定的模式。通过信号导线耦接到第一电子单元的第二电子单元从信号导线接收数据,并且把所接收的模式与预先确定的模式进行比较。如果所接收的模式与预先确定的模式不同,则信号导线、驱动器或者接收器出现故障。这样的路径将使具有或不具有奇偶性校验的信号总线不可使用。即使使用具有单个错误纠正和双错误检测的ECC的信号总线,也难以保证,因为ECC总线中的另一个故障将使甚至ECC总线不可使用。两条信号导线中的故障还将使甚至具有单个位纠正的ECC的信号总线不可使用。

美国专利5,440,538公开了一种通信系统和方法,用于在通信信道上通信。优选地包括高速多路复用器和去多路复用器集成电路的替换的开关与到冗余空闲链接的错误链接相匹配,以允许通信继续穿过信道。

美国专利6,018,810公开了一种计算机系统中的容错64位数据宽度外围元件互连(PCI)总线系统,其可以从在64位数据宽度PCI总线的上或下32位分区上发生的故障(或多个故障)中恢复。

美国专利5,717,852公开了如果当数据经由总线在主总线和从总线之间被传递时,在总线上发生故障,则经由总线的数据传递被终止。然后所述数据经由无故障总线被重新传递。

发明内容

根据第一方面,提供了一种方法,用于在具有“K”条信号导线的信号总线上,把“J”位的数据块从第一电子单元发送到第二电子单元,其中,0~“K-1”条信号导线出现故障,该方法包括步骤:识别信号总线中故障信号导线和无故障信号导线;使用由识别信号总线中故障信号和无故障信号导线的步骤所发现的信息,设置第一电子单元中和第二电子单元中信号导线的故障状态;确定信号总线中的故障信号导线的数目“F”;确定信号总线中无故障信号导线的数目“K-F”;以及使用“J/(K-F)”个节拍(beat),如果存在余数则再加上一个额外的节拍,在“K-F”条无故障信号导线上发送“J”位的数据块。

在优选的实施例中,该方法包括:从第一电子单元上的“J”位的数据块中选择“K-F”位的位组;使用信号总线中“K-F”条无故障信号导线,使用信号总线的节拍,从第一电子单元向第二电子单元发送“K-F”位的位组;重复以上的步骤,直至发送了所有“K-F”位的组;以及使用某些或全部“K-F”条无故障信号导线,使用信号总线的额外的节拍,把第一电子单元上的“J”位的数据块的任何剩余的位发送到第二电子单元。

优选地提供一种允许具有故障信号导线的信号总线以略降低的性能加以操作的方法与装置。

在优选的实施例中,发送步骤还包括步骤:从“J”位的数据块中选择“K”位的数据组;使用“K-F”条无故障信号的导线,在节拍上发送“K”位数据组的“K-F”位;存储由于信号总线中的“F”条故障信号导线而不能在该节拍上发送的“K”位组中的“F”位;重复以上三个步骤,直至已经选择了“J”位的数据块的所有“J”位;以及使用一个或更多的“K-F”条无故障信号导线,在一个或多个额外的节拍上发送所存储的“F”位。

在优选的实施例中,存储“F”位的步骤还包括把“F”位中的至少一位移位到移位寄存器的第一端点的步骤。

在优选的实施例中,还包括把移位寄存器的至少一位发送到无故障信号导线的步骤。

在优选的实施例中,还包括移动移位寄存器中的特定的位,以调整该特定的位,用于耦接到无故障信号导线的步骤。

在优选的实施例中,还包括步骤:在第二电子单元中,对于“J/(K-F)”个节拍,每一个节拍存储“K-F”位;以及如果“J/(K-F)”产生余数,则在额外的节拍中,存储剩余的位。

本发明优选地提供这样的方法与装置:允许具有通过信号总线耦接到第二电子单元的第一电子单元的电子系统连续地、但不降级的操作,其中信号总线中的信号导线有故障。对信号总线中的无故障信号导线优选地加以识别,而且第一电子单元优选地利用所有无故障信号导线,使用最小数目的节拍(总线周期)以完成传输,把传输序列中的数据块发送到第二电子单元。把第一电子单元优选地设计成在具有“K”条信号导线的信号总线上发送具有“J”位的数据块。第二电子单元优选地接收该数据块。例如,电子系统使用“连线测试”或其它机制识别信号总线中的故障信号导线和无故障信号导线,并且优选地把一条或多条故障信号导线的标识存储在第一电子单元和第二电子单元中。根据优选的实施例,“F”是信号总线中故障信号导线的数目。第一电子单元优选地使用故障信号导线的标识以改变其传输,在剩余的“K-F”条信号导线上发送“J”位的块作为传输序列,使用一个或多个额外的节拍完成该传输。第二电子单元优选地使用故障信号导线的标识,根据该传输序列,在无故障的“K-F”条信号导线上接收“J”位的块。

在实施例中,在需要在含有“K”条信号导线的信号总线上传输包括有“J”位的数据块的电子系统中,当无信号导线出现故障时,在传输序列中使用“J/K”个总线周期(节拍)以完成传送。当信号总线中的“F”条信号导线发生故障时,传输序列所需要的节拍的数目为“J/(K-F)”,如果除法留下余数,则再加上一个额外的节拍。

在具有含“K”条信号导线的信号总线的实施例中,“F”条信号导线发生故障,传输序列每节拍从包含“J”位数据的数据块中选择“K”位。对于“J/K”个节拍中的每一个,发送“K-F”位,并且对于随后的传输每节拍存储F位。使用“J(K-F)-J/K”个额外的节拍(如果除法留下余数,则再加上一个节拍)发送来自在“J/K”个节拍期间未加以发送的每一节拍的所存储的位。

在具有含“K”条信号导线的信号总线的实施例中,“F”条信号导线发生故障,传输序列从包含“J”位的数据的第一电子单元中的数据块中每节拍选择“K-F”位。对于J/(K-F)个节拍中的每一个发送“K-F”位。如果除法留下余数,则使用一个额外的节拍。

根据另一方面,提供了一种用于把“J”位的数据块从第一电子单元发送到第二电子单元的装置,包括:第一数据块,位于第一电子单元中,含有用于传输的“J”位;存储器,位于第二电子单元中,能够容纳具有“J”位的第二数据块;信号总线,具有“K”条把第一电子单元耦接到第二电子单元的信号导线,所述信号总线具有“F”条故障信号导线和“K-F”条无故障信号导线;诊断单元,耦接到第一电子单元和第二电子单元,能够识别信号总线上的“F”条故障信号导线和“K-F”条无故障信号导线,并且把故障标识信息存储在第一电子单元中和第二电子单元中;以及驱动定序器,位于第一电子单元中,其响应于故障标识信息,使用“J/(K-F)”个节拍,如果存在余数,则加上额外的节拍,仅使用“K-F”条无故障的导线。发送“J”位数据。

在优选的实施例中,通过一次选择“K”位的组而选择第一数据块。

在一个优选的实施例中,驱动定序器能够一次从第一数据块中选择“K-F”位,并且把所选的“K-F”位驱动于信号总线的“K-F”条无故障信号导线上,如果“J/(K-F)”具有余数,则驱动定序器还能够选择附加节拍的比“K-F”位少的位。

在优选的实施例中,驱动定序器还包括能够被禁止的驱动器;其中,驱动定序器将耦接到故障信号导线的驱动器禁止。

在优选的实施例中,第二电子单元还包括耦接到信号总线和诊断单元的接收定序器,该接收定序器能够一次把“K-F”位存储于第二数据块中,从信号总线的“K-F”条无故障信号导线中接收该“K-F”位,如果“J/(K-F)”具有余数,则该接收定序器还能够存储比“K-F”位少的位。

根据另一个方面,提供了一种用于在信号总线上把数据块从第一电子单元发送到第二电子单元的方法,包括步骤:识别信号总线中的无故障信号导线;以及使用传输序列,把数据块从第一电子单元发送到第二电子单元,所述传输序列利用信号总线中的所有无故障信号导线;其中,所述传输序列使用最小数目的节拍以完成数据块的传输。

在优选的实施例中,以上段落所描述的方法还包括步骤:识别信号总线中的故障信号导线;以及把耦接到故障信号导线的驱动器切换为高阻抗状态。

在优选的实施例中,在加电序列期间,识别无故障信号导线。

在优选的实施例中,作为奇偶性校验错误、错误纠正代码错误、或循环冗余检查错误的结果,通过所执行的连线测试识别无故障信号导线。

附图说明

现在,将仅以举例的方式,并参照下列附图,描述本发明的实施例。

然而,应该加以注意的是,附图仅说明了本发明的典型的实施例,因此,不应将它们视为对本发明范围的限制,就本发明而言,也可接纳其它同等有效的实施例。

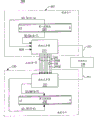

图1根据优选的实施例,示出了由信号总线所耦接的具有双电子单元的高级方框图。每一个电子单元具有用于数据块的存储器。在信号总线的一个信号导线上示出了示例性的故障。

图2A和2B(根据优选的实施例)分别对于无故障的信号总线和故障信号导线的信号总线示出了每一节拍上所发送的数据的时序图和描述。

图3根据优选的实施例,示出了驱动信号总线上的数据块的电子单元的详细的方框图。示出了驱动定序器的扩展的方框图。

图4根据优选的实施例,示出了当在具有故障信号导线的信号总线上发送数据的节拍时,图3中所描述的驱动位寄存器块的内容。

图5根据优选的实施例,示出了电子单元的扩展的方框图,所述电子单元接收由驱动电子单元在具有故障信号导线的信号总线上发送的数据块。

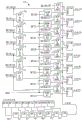

图6根据优选的实施例,示出了图5中所描述的分配器块的一位(one-bit)部分的细节。

图7示出了本发明的第二实施例的高级方框图。经由具有故障信号导线的信号总线,驱动电子单元(该示例性的图中的驱动芯片)耦接到第二电子单元(该示例性的图中的接收芯片)。根据是否识别出故障信号导线,从将被发送的数据块中选择不同大小的数据组。

图8A和8B根据本发明的实施例,示出了正常数据传输(即没有识别出故障信号导线)的时序图,以及当已识别出故障信号导线时的数据传输的时序图。

图9根据第二实施例,示出了图7中所描述的驱动器控制块的详细的方框图。

图10根据第二实施例,示出了图7中所描述的接收器控制块的详细的方框图。

图11根据第二实施例,示出了把正确的数据锁存于图7中所描述的接收寄存器的特定位中的控制逻辑的详细的方框图。

图12是本发明的实施例中所公开的方法的高级流程图。

图13是根据本发明的实施例示出了图12的流程图的框304的详细扩展的流程图。

图14是根据本发明的实施例示出了图12的流程图的框304的详细的可选扩展的流程图。

具体实施方式

优选地提供了这样的方法与装置:允许具有通过信号总线耦接到第二电子单元的第一电子单元的电子系统的连续地、但不降级的操作,其中信号总线中的信号导线有故障。对信号总线中的无故障信号导线加以识别,而且第一电子单元利用所有无故障信号导线,使用最小数目的节拍(总线周期)以完成传输,把传输序列中的数据块发送到第二电子单元。把第一电子单元设计成能够在具有“K”条信号导线的信号总线上发送具有“J”位的数据块。第二电子单元接收所述数据块。电子系统使用“连线测试”或其它机制识别信号总线中的故障信号导线,并且把故障信号导线的标识存储在第一电子单元和第二电子单元中。故障信号导线的数目为“F”。第一电子单元使用故障信号导线的标识改变其传输,在无故障的“K-F”条信号导线上发送“J”位的块,使用一个或多个额外的节拍完成该传输。第二电子单元使用故障信号导线的标识,以在无故障的“K-F”条信号导线上接收“J”位的块。总体上讲,尽管“F”可以是最高为“K-1”的任何数目,但为了简单起见,在以下的示例中假设单个故障。此外,为了简单起见,以下的示例假设采用在其上传送64位的数据块的8位的信号总线。

图1示出了总体被表示为100的电子系统的高级方框图。电子系统100包括第一电子单元1,以下将其称为芯片1,以及第二电子单元5,以下将其称为芯片5。电子单元1和电子单元5可以为任何电子部件,包括但不局限于半导体芯片、模块、印刷线路板(PWB)、或电子封装件。为了加以解释,把“芯片”用于提供具体的示例。芯片1包括第一数据块10,必须使用定义了在每一节拍(总线周期)上将加以发送的许多位以及完成这一传输需要多少个节拍的传输序列,把第一数据块10驱动至芯片5,在该处,所述第一数据块10将被存储在第二数据块50中。在成功的传递之后,第二数据块50与启动传输之前的第一数据块10相同。通常,把第一数据块10和第二数据块50存储在每一芯片上的一个或多个寄存器中,但也可以将它们存储在任何形式的存储器中,诸如高速缓冲存储器或其它存储器。在信号总线95上把来自第一数据块10的数据从芯片1传递至芯片5。图1的示例中的第一数据块包含8个字节(即64位)。在图1中,把信号总线95示出为具有8条信号导线。由于先前所讨论的经济和物理方面的考虑,信号总线通常“较窄”(即,具有相当少的信号导线),比加以传递的数据块中的位的数目要窄得多。尽管出于示例的目的,把信号总线95示出为具有8条信号导线,但也可以考虑更宽或更窄的信号总线,而且信号总线还可以包含奇偶性校验、或者错误纠正代码信号导线。在信号导线上不存在故障(包括驱动器或接收器故障)的情况下,使用8个信号总线周期(节拍)把第一数据块10中的所有数据传递于芯片5。在每一节拍期间发送8位(一个字节)的信息的选择组。选择组是从用于传送至驱动信号总线95的驱动器的输入端的第一数据块10(或者从以下将讨论的其它存储器)中所选择的位组。在本例中,按预先确定的次序,依次顺序地从数据块10中选择字节0~7,如图1中的10A~10H所示,并且在信号总线95上一次一个字节地发送它们。芯片5接收每一个字节,并且将每一字节存储在第二数据块50的字节0~7中,如50A~50H所示。

尽管把第一数据块10和第二数据块50示出为具有一个字节宽的总线,该总线把第一数据块10和第二数据块50的数据的每一个字节分别耦接到驱动定序器11和接收定序器51,但也可以考虑其它的实现。在一个实施例(未示出)中,例如,第一数据块50为移位寄存器,其中,一次把数据移位8位,并且仅把该移位寄存器的单个的字节耦接到驱动定序器11。在另一个实施例(未示出)中,第一数据块10为8位寄存器的寄存器栈;该寄存器栈具有能够对栈中的任何一个寄存器进行寻址的相关联的3位地址。在芯片5中,对于第二数据块50,考虑了类似的实施例。

图1中示出了信号总线95的信号导线之一中的故障96。故障96把信号总线部分95B与信号总线部分95B′分开。故障96可以为信号导线的不连续,或断开,有时将其称为“开路”。故障96也可能是与电源的不希望的连接。无论在哪种情况下,由部分95B和部分95B′组成的信号导线都不能够可靠地发送信息。然而,故障96也可以是信号总线95上两个信号之间的短路,于是信号总线95将具有两个故障,而本例假设仅具有单个的故障。除这些示例性的图中所示的逻辑框外,还需要额外的逻辑框以容纳两个故障。然而,如本领域技术人员将欣赏的,额外的逻辑类似于所示出的逻辑,。

在系统停止或响应奇偶性校验检查、CRC、或ECC错误的“连线测试”期间,对故障进行识别,并且将其存储在诊断单元98中。经由信号导线91和信号导线92,进行通报故障的通信。信号导线91和92可以为单个的信号导线,也可以为具有多条信号导线的总线。诊断单元98为任何一种检查电子系统的故障的单元。例如,在IBM iSeries计算机中,把诊断单元称为“服务处理器”。

图2A示出了当信号总线95不具有故障时,在第一数据块10中的正常数据的传递期间所执行的传输序列。在第一节拍期间,传递字节0。在第二节拍期间,传送字节1。在第八节拍上,传递最后的字节,字节7。

图2B示出了当信号总线95中的信号导线之一具有故障时,在信号总线95上完成第一数据块10中的数据传递的传输序列。为了示例性的目的,由于该故障,信号总线95的信号导线“Z”上的位不能得以传递。芯片1的驱动定序器11知道该故障,但为数据传递的前8个节拍中的每一个选择一个字节的选择组(在本例中)。这类似于无故障存在时的操作。图2B表明不传递每一节拍的位“Z”。(例如,字节0而不是位“Z”意味着:由于信号导线“Z”上的故障96,在节拍1期间,把字节0传送至驱动器的数据输入端,但不传递字节0的位“Z”。有利的是,把位“Z”的驱动器置于非导通状态(通常将其称为“禁止的”或“三稳态(tristate)的”),因为所识别的故障可能是短路,并且如果故障为到地电源的短路,而且特定位为逻辑“1”,则将会耗散大量的电能。驱动定序器11(参见图1)存储在前8个节拍期间不发送的8位,并对于每一节拍存储位“Z”。在第九节拍期间,把包括所存储的8个“Z”位的选择组传送至驱动器。传递这些“Z”位中的7个“Z”位。由于故障,在第九节拍上不传递第八个“Z”位。然后使用信号总线95中的无故障信号导线,在第十节拍上传递第八个“Z”位。

第一数据块10中的位的数目(64位)以及信号总线95中的信号导线的数目(8条)仅为示例值,可以考虑任何大小的数据块和总线中任何数目的信号导线。而且,在某些电子系统中,数据块可以为可变的,在数据块的数据部分的传输之前具有所发送的“报头”,报头包括关于将加以发送的块的大小的信息。为了进行这一讨论,将把报头视为数据块的一部分。

图3示出了芯片1,并附有驱动定序器11的详细的方框图。把驱动多路复用器20耦接到第一数据块10的8个字节中的每一个上,并且可以把第一数据块10的8个字节中的任何一个选择为驱动多路复用器20的输出。也可以通过耦接35而把驱动多路复用器20耦接到驱动位寄存器27。通过信号30把驱动节拍控制器23耦接到驱动多路复用器20,所述信号30决定了驱动多路复用器20将选择9个字节(即来自第一数据块10的8个字节和来自驱动位寄存器27的1个字节)中的哪一个字节。把所选择的字节耦接到驱动器24的数据输入端。也把所选择的字节耦接到驱动选择21。来自驱动节拍控制器23的信号34告诉驱动选择21信号总线95中的哪一条信号导线有故障。如以上所解释的,由于信号总线95中的信号导线上的故障96,所以必须将所选择的当前字节中的位存储在驱动位寄存器27中,以用于后面的传输。把所选择的位耦接到驱动位寄存器27,并且将其存储于驱动位寄存器27中,由来自驱动节拍控制器23的信号32对所述驱动位寄存器27加以控制。有利的是,驱动位寄存器27为移位寄存器,但也可以考虑其它的实施例。在8个节拍之后,驱动位寄存器27包含全部因故障96而不能加以传输的8位(来自字节0~7的每个的1位)。在第九节拍上,在驱动节拍控制器23的控制下,由驱动多路复用器20通过信号30,选择驱动位寄存器27中的8位。再次在信号总线95上发送这8位中的7位。由于故障96,1位仍不能加以发送.驱动节拍控制器23经由耦接32进一步用信号通知驱动位寄存器27把驱动位寄存器27中的位加以“旋转(rotate)”。在图3中,信号33把驱动位寄存器27的第一端耦接到驱动位寄存器27的第二端。在旋转期间,把驱动位寄存器27的最右侧的7位左移1位的位置,并且把最左侧的位旋转为变成最右侧的位。在第十节拍期间,在驱动节拍控制器23的控制下,由驱动多路复用器20再次选择驱动位寄存器27的目前所旋转的内容。再次在信号总线95上发送7位,而且因本例的故障96,1位不能加以发送。然而,由于驱动位寄存器27上的旋转操作,在第九节拍上没有被发送的位被驱动到不同的信号导线上,并在第十节拍上被成功发送。如果把电子系统设计成支持多于一个的故障信号导线,则复制驱动位寄存器27(未示出),以容纳不能够在特定节拍上加以传递的额外的位,而且把驱动选择21设计成从驱动多路复用器20的输出中选择额外的位,并且把额外的位存储在驱动位寄存器27的副本中.尽管出于示例的目的描述了驱动位寄存器27中的“旋转”操作,但也可考虑适合于移动对于第十节拍不可加以传输而被传送至无故障信号导线的位的驱动寄存器27中的位的任何预先确定的移动。在另一个实施例(未示出)中,驱动多路复用器20具有耦接到驱动位寄存器27的第九输入位,如以上所描述的,但另外还具有耦接到驱动位寄存器27的位的第十输入字节,具有以预定次序耦接到驱动多路复用器20的驱动位寄存器27的位,这不同于驱动位寄存器27的第九字节耦接。驱动节拍控制器23将控制驱动多路复用器20选择第九节拍期间的第九输入字节耦接和第十节拍期间的第十输入字节耦接。

图4示出了每一节拍之前驱动位寄存器27的内容。位“Z”为将不在具有故障的信号总线95中的信号导线上加以驱动的数据的位。在节拍1之前,没有已经移位于驱动位寄存器27中的位。在节拍1期间,把字节0的位“Z”移位于驱动位寄存器27的最右位的位置中。在节拍2期间,把字节1的位“Z”移位于驱动位寄存器27的最右位的位置中。在节拍8(如图4中预9节拍所示)之后,把关于每一字节的位“Z”存储在驱动位寄存器27中。如先前所描述的,在第九节拍期间,由驱动多路复用器20选择这8位。在第九节拍之后,如先前所描述的,在驱动位寄存器27上进行旋转操作,并且在图4中,把关于第十节拍所选择的数据示出为“预节拍10”。所有“Z”位保留在驱动位寄存器27中,但都被旋转了一位的位置,并因此将对它们加以传送,以由驱动器24在信号总线95上的不同的信号导线上加以驱动。从而,在第十节拍上成功地传递不能够在第九节拍上加以传递的“Z”位。

图5示出了芯片5的扩展的方框图。接收定序器51包含适合于接收信号总线95上的信号的接收器60。接收定序器51还具有接收器节拍控制器61,通过信号92把接收器节拍控制器61耦接到先前所描述的诊断单元98。诊断单元98告诉接收器节拍控制器61:信号总线95中的信号导线是否有发生故障的,如果有的话。

通过信号55(其可以包含多个信号),把分配器63耦接到内部总线56上的接收器60和接收器节拍控制器61。分配器63能够把接收器60输出的信号分配到第二数据块50中的适当的位。在不存在故障的情况下,在8个节拍(在本例中)的每一节拍期间,分配器63简单地把一个字节的数据从内部总线56移至第二数据块50的适当的字节。当信号导线“Z”上存在故障96(根据以上的讨论)上时,需要在两个额外的节拍(在本例中)。在第九节拍期间,内部总线56具有7个有效位和1个无效位。在第九节拍上,把内部总线56上的8位中的每一位驱动至第二数据块50的字节中的每一个(即字节0~7)的相应的“第Z个”位。在第九节拍之后,第二数据块50包含63个有效位和1个无效位。在第十节拍期间,内部总线56再次具有7个有效位和1个无效位。有效位中的6个为在第九节拍期间成功写入第二数据块50中的简单数据。在第十节拍期间,把第七有效位导向(direct)包含第二数据块50中余下的无效位的字节的“第Z个”位。例如,如果在信号总线95的位2上存在故障96,则在第十节拍上写入第二数据块50中的位为字节2的位2;然而,对于该写入的数据来自信号总线95的位3,因为已在驱动位寄存器27中将所传输的数据旋转了一位,如以上所解释的。

图6更详细地示出了对于分配器63的一位执行分配功能的逻辑63A的示例性的集合。在所示出的例子中,寄存器位70是第二数据块50的一位;字节“M”的位“N”。把寄存器位70的数据输入端D耦接到选择器72,所述选择器72对于任何小于10的节拍选择“rcvr位N”,即内部总线56的“第N个”位。在第十节拍上,在传输之前,选择“rcvr位N(旋转过的)”,以说明由驱动位寄存器27所执行的数据的旋转。输入端C上的信号对寄存器位70的数据输入端D上的数据记时。“CLK”是系统时钟,根据图6中所示的逻辑表达式而被选通。当激活CLK以及确认(assert)了“节拍M”时,寄存器位70将接收时钟。例如,在第二节拍上,将对字节2的所有位记时。如果信号总线95上的位“N”出现故障,则在第九节拍期间寄存器位70也将接收时钟(在CLK激活期间)。例如,如果信号总线95的位2出现故障,以及寄存器位70为第二数据块50中的任何字节的位2,则将对寄存器位70记时。如果这是必须被写入第二数据块50的最后的一位,则在第十节拍期间,也将对寄存器位70记时(在CLK激活期间)。继续其中信号总线95的位2出现故障的例子,如果寄存器位70表示字节2的位2,则寄存器位70将在第十周期上接收时钟。分配器63接收关于信号总线95上的哪一位发生故障(如果有的话)以及当前节拍是什么的信息。

图7示出了本发明的另一个实施例。这该实施例也提供了继续电子系统的操作的能力,所述电子系统在信号总线中的信号导线上具有故障,实际上,该实施例在无故障和有故障操作的情况下使用了与先前的实施例相同的周期数目。在选择的方式方面,该实施例有所不同,以下将对此加以解释。图7的实施例示出了与图1的诊断单元98相同的诊断单元298,其能够识别信号总线上的故障,并且能够把故障的标识传递于第一电子单元和第二电子单元。

芯片201(如以上所述,为了示例性地目的而使用“芯片”,事实上,芯片201可以为模块、PWB、电子封装、或者任何其它的电子单元)需要把第一数据块201传递于芯片205中的第二数据块250。如同驱动芯片201,接收芯片205旨在表示任何电子单元。在图7所示的例子中,第一数据块201具有64位(0~63),第二数据块250具有64位(0~63)。第一数据块201和第二数据块250可以物理地驻留在一个或多个寄存器、高速缓冲存储器、移位寄存器或者任何其它的存储机制中。信号总线295具有8位。把包括第一部分295B和第二部分295B′的信号导线示出为具有故障296。故障296可以为开路或短路,其中每一种类型的故障都使信号导线无法操作。如同图1的故障96,故障296可以是信号总线295的信号导线之间的短路,但为了简单起见,本例讨论了信号故障.信号NEN是“不使能”信号,通常将其用于逻辑地禁止(三稳态)信号总线295上的驱动器。尽管是可选的,但还是将其示出以解释如何将其与其它信号逻辑地相组合,以禁止整个信号总线295上的所有驱动器,或者仅禁止耦接到具有故障的信号导线的单个的驱动器.

在不存在故障296的情况下,驱动定序器211在内部总线SEL8A(0~7)上从第一数据块201中一次选择8位的“无故障选择组”,并且对于8个节拍中的每一个基本上并行地驱动这8位。接收定序器251从每一个节拍中接收数据的8位,并且在SEL8B(0~7)上把这8位传递于第二数据块250中的适当的位。如以前一样,诊断单元298分别经由信号291和292向驱动定序器211和接收定序器251通知信号导线中故障296的存在及其标识。

如果故障296存在,则驱动定序器211在内部总线SEL7A(0~6)上从第一数据块201中一次(在本例中为节拍1~9)选择7位的“故障选择组”,并且在信号总线295的7条无故障信号导线上传递7个所选择的位。然后,接收定序器251在SEL7B(0~6)上每个节拍接收这7位,并且把它们传递于第二数据块250。在第十节拍(在本例中)上,选择最后一位,在本例中为位63,并且在不具有故障的信号导线上将其加以发送,而且把最后一位存储在第二数据块250的正确的位中。图8A和8B示出了当无故障存在时的8个节拍和所发送的数据,以及当故障存在时的10个节拍和在每一节拍期间所发送的位。

图9示出了驱动定序器211的示例性的实施例。位故障寄存器259具有8位,每一位相应于信号总线295中的信号导线。如果信号导线具有故障,则把位故障寄存器259中的相应的位设置为逻辑“1”;否则把相应的位设置为逻辑“0”。因此,BF(0)=“1”意味着信号总线295的位0上存在故障。一连串的OR门产生以具有逻辑“1”的位故障寄存器259中的位开始的逻辑“1”。例如,如果BF(3)=“1”,则F0、F1=F2为“0”,但F3、F4、F5、F6以及BITFAULT为“1”。

如果BIT FAULT=“1”,则存在故障,而且数据传递(在本例中)将由10个节拍组成,前9个节拍的每一个中的7位,以及第十节拍中的1位。

如果BIT FAULT=“0”,则选择器AA0~AA7从总线SEL8A(0~7)中选择数据。如果BIT FAULT=1,则选择器AA0~AA7从SEL7A(0~6)中选择数据,尽管可以对某些或全部这样的位进行移位,如马上将加以描述的。选择器A0~A5提供把SEL7A(0~6)的所有位移位至无故障信号导线的机制。

例如,假设BUS(0),其为信号总线295的信号导线位(0),已被识别为具有故障(该故障可能包括BUS(0)的驱动器、信号导线、以及接收器电路)。BUS(0)的驱动器具有使能输入端E,如果输入端E处于逻辑“0”,则其禁止该驱动器。当BUS(0)具有故障时,BF(0)=“1”。BF(0)是到NORA0的输入;BF(0)=“1”确保将BUS(0)的驱动器的禁止。F0控制选择器A0;F0=“1”选择选择器A0中的SEL7A(0),通过选择器AA1,把选择器A0耦接到BUS(1)的驱动器的数据输入端D。相类似,把SEL7A(1)传送至BUS(2)的驱动器的输入端D;把SEL7A(2)传送至BUS(3)的驱动器的输入端D,等等。把SEL7A(6)直接传送至SELAA7,并且在BUS(7)上对SEL7A(6)加以驱动。以这种方式,旁路BUS(0),并且在无故障信号导线BUS(1~7)上驱动SEL7A的7位。

作为第二个例子,但更加简洁,如果BUS(4)上存在故障,则传送SEL7A(0),并且在BUS(0)上驱动SEL7A(0);在BUS(1)上驱动SEL7A(1);在BUS(2)上驱动SEL7A(2);在BUS(3)上驱动SEL7A(3)。在BUS(5)上驱动SEL7A(4);在BUS(6)上驱动SEL7A(5);在BUS(7)上驱动SEL7A(6)。BF(4)禁止BUS(4)的驱动器。再次,在无故障信号导线上传送SEL7A的7位。

可以通过确认NEN=“1”而完全禁止信号总线295,NEN=“1”是关于NOR A0~A7的确认信号,确保了所有8个驱动器上使能的输入端上的逻辑“0”。NEN是当设计人员希望能够逻辑地禁止信号总线295上的所有驱动器时所使用的可选的信号。

本领域技术人员将会意识到,尽管为了简单起见,所示出的详细的逻辑仅支持单个的故障信号导线,但也可以把额外的选择组(例如,分别容纳两或三条有故障信号导线的“SEL6A”、“SEL5A”)耦接到额外的选择器,以在当“F”变大时,传送较少的信号导线。

图10示出了接收定序器251的实施例。接收位故障寄存器260包括与位故障寄存器259相同的位模式,每一位相应于信号总线295中的信号导线。在信号292上从诊断单元298加载接收位故障寄存器260。再次提供如所描述的一连串OR门,以产生逻辑“1”,所述逻辑“1”中包括并跟随接收位故障寄存器260中的逻辑“1”位。例如,如果RBF(0)=“1”,则RF0、RF1、RF2、RF3、RF4、RF5、RF6以及RECEIVE BIT FAULT均为“1”。

接收器B0~B7分别接收BUS(0~7),并且分别输出SEL8B(0~7)。如果信号导线上存在故障,则仅发送7位(在7个无故障信号导线上),并且必须把这7位适当地从SEL8B(0~7)映射至SEL7B(0~6)。该映射有效地相应于由驱动定序器211所进行的映射,以把7位转向(steer)信号总线295的7个无故障信号导线。

RF0~RF7和选择器B0~B6提供该映射。如果RBF(0)=“1”(表示信号总线295的信号导线位“0”中的故障),则RF0=“1”,而且控制选择器B0以对于输出选择SEL8B(1)作为SEL7B(0)。相类似,使用信号RF1、RF2、RF3、RF4、RF5以及RF6,把SEL8B(2)驱动至SEL7B(1);把SEL8B(3)驱动至SEL7B(2);把SEL8B(4)驱动至SEL7B(3);把SEL8B(5)驱动至SEL7B(4);把SEL8B(6)驱动至SEL7B(5);以及把SEL8B(7)驱动至SEL7B(6)。相类似,如果BUS(6)有故障,则把BUS(0~5)传送至SEL7B(0~5),以及把BUS(7)传送至SEL7B(6)。

在所设计来容纳更多的单个故障信号导线的实施例(未示出)中,使用额外的选择器和OR,其中额外的选择器用于把信号从无故障信号导线传送至具有耦接到第二数据块250的较少信号的信号组,例如,如以上所描述的,在实施例中容纳两个故障信号,(使用以上的命令约定),要求信号的“SEL6B”集合以及信号的SEL7B集合。

图11示出了用于将所接收的适当的位选通于接收寄存器250的正确的位的详细逻辑的实施例。来自诊断单元298的信号292包括节拍编号。在可选的实施例(未示出)中,接收定序器251自己统计节拍。组译码278使用节拍编号和接收位故障(图10的接收位故障寄存器260)产生8位的“en 8-bitgroup”的字,对于每一节拍使能其的每一位,以控制当无故障存在于信号总线295中时,对于具体节拍,必须从SEL8B接收数据的接收器寄存器250中的8位的时钟。组译码278也输出10位的字,“en 7-bit group”,对于当故障存在于信号总线295的信号导线上时所发生的10个节拍中的每一个,使能其中的一位。把寄存器位272的数据输入端(接收寄存器250中的特定的位“X”)耦接到选择器270,当RECEIVE BITFAULT=“1”时,选择器270选择总线SEL7B的位“M”,当RECEIVE BIT FAULT=“0”时,选择总线SEL8B的位“N”。例如,把SEL7B(0)耦接到接收寄存器250的位0、6、13、55以及64。把SEL7B(1)耦接到位1、7、14...56。把SEL8B(0)耦接到位0、7、15、56。

AND门271接收第一输入端上的系统时钟CLK。把AND门271的第二输入端耦接到由如图10中所示而产生的RECEIVE BIT FAULT所控制的选择器277。如果存在故障,则RECEIVE BIT FAULT=“1”,选择器277将选择“EN 7-BIT GROUP(A)”,其中“A”为10位的字的位,施加于寄存器位272位于其中的第二数据块250的特定的7位组的“EN 7-BIT GROUP”274。例如,第二数据块250的位0~6位于由节拍1发送的所传递的7位的位组中,且在第一节拍期间EN 7-BIT GROUP的位0将为“1”,以对那7个寄存器位使能时钟。注意,(在本例中)当对于第十节拍的“EN 7-BIT GROUP”中的位为“1”时,仅影响接收器寄存器250的一个寄存器位(即位63)。

如以上所讨论的,在实施例中,容纳了额外的故障信号导线。例如,如果准备容纳两个故障信号导线,则组译码278必须使能6位的组以及7位的组和8位的组。选择器270必须具有对于适当的“SEL6B”位的另一个输入端,并且选择器277必须容纳对于适当的“EN 6-BIT GROUP”位的第三输入端,如本领域技术人员将会意识到的。

图12示出了传输序列方法300的高级流程图,所述传输序列方法300允许在信号总线上把数据块从第一电子单元传递于第二电子单元,信号总线可以具有故障信号导线。该方法开始于框301。在框302中,诊断单元确定信号总线中故障和无故障信号导线。第一电子单元经由信号总线、使用利用了所有无故障信号导线的传输序列、使用最小数目的节拍,把第一数据块传递于第二电子单元。第一电子单元必须把“J”位的数据块发送到“K”位的信号总线的第二电子单元。“F”为诊断单元所识别的故障信号导线的数目。如果“F”=0,则没有识别出故障。本发明优选地考虑到最多为“K-1”的故障数目。在框303中,诊断单元在第一(驱动)电子单元中和第二(接收)电子单元中设置故障状态。在框304中,在信号总线中的无故障信号导线上使用用于完成该传递的足够的总线周期(节拍)发送“J”位的数据块。第二电子单元在无故障信号导线上接收“J”位的数据块。框305结束该方法。有利的是,禁止耦接到故障信号导线的驱动器。

图13示出了方法320的流程图,其为方法300的框304的实施例。该方法开始于框321。在框322中,初始化节拍计数。在框323中,选择一个字节的数据。所选择的位的数目为将在其上传递数据块的信号总线中的全部信号导线的数目,此处使用“字节”是为了示例性的目的,假设了一个字节宽的信号总线。为了示例性的目的,假设了64位的数据块,但本发明优选地不局限于64位的数据块。为了简单起见,假设了单个故障信号导线,但也可以假设最多为“K-1”的任何数目的故障位,如以上所解释的。在框324中,存储用于在故障信号导线上发送的所选择的字节的位。有利的是,把该位存储在移位寄存器中,而且移位寄存器可以具有其响应于控制信号所旋转的位。在框325中,把所选择的字节传送至驱动器的数据输入端,并且在信号总线上对其加以驱动。故障信号导线不能够发送被传送至耦接到故障信号导线的驱动器的数据输入端的位,而且,有利的是,禁止(也称为三稳态的,或者将其切换为高阻抗状态)驱动器,以防止在故障为短路的情况下流动的可能的高电流。在将驱动器禁止的情况下,“高阻抗”意味着驱动器的输出至少为高于被驱动的传输线的阻抗大小的一个量级,而且通常为几百千欧姆,甚至数兆欧姆。在框326中,作出检查以了解是否已经完成正常(不存在故障信号导线)传输所需的节拍数目。如果没有完成,则框342递增节拍计数,并且将控制传递于框323。如果已经达到了正常的节拍计数,则框327检查是否已识别出故障。如果没有识别出故障,则传输已经完成。如果识别出了故障,则框328选择所存储的位的字节(在本例中,为将在8位的总线上发送的64位的数据块,并假设单个的故障,从而导致8个所存储的位),并且把它们传送至信号总线的驱动器的数据输入端。在另一个节拍上发送8位中的7位,如以上所解释的。框329旋转所存储的数据中的位,使得可以把所有位移至不同的、预先确定的位置。所先前所解释的,有利的是,所存储的位位于能够位旋转的移位寄存器中,其中把所有位移动一个位置,并且把一端上的位旋转至另一端上的第一位的位置。在框340中,再次选择所存储的位,而且把它们传送至信号总线上的驱动器的数据输入端,并在最后的节拍上对它们加以驱动。此时,把不能够在先前总线节拍上发送的位导向不同的驱动器,并且在无故障信号导线上成功地被驱动。第二(接收)电子单元知道故障信号导线,并将所述第二(接收)电子单元设计成知道当故障信号导线存在时所使用的传输协议,而且能够适当地把所发送的位移入第二电子单元中的存储器的正确的位的位置。

图14示出了图12的框304的第二实施例。在信号总线上把数据块从第一电子单元传递于第二电子单元的方法开始于框361。在框362中,对节拍计数进行初始化,根据将加以传递的位的总数目和信号总线中可用的无故障信号导线的数目确定所需的节拍的数目。在框363中,选择来自将加以传递的块中的数据组,该组的大小等于信号总线中无故障信号导线的数目。在框364中,由第一电子单元在无故障信号导线上把所选择的数据组发送到第二电子单元。框365确定是否已完成了最后一个节拍;如果没有完成,则框366递增位计数器,并且把控制传递于框363。如果已经完成最后一个节拍,则把控制传递于框367,框367完成该方法。

尽管以上的描述对于的是本发明的实施例,但可以在不背离本发明的基本范围的情况下,设计本发明的其它的和进一步的实施例,本发明的范围由以下权利要求加以确定。

Claims (13)

1. 一种方法,用于在具有“K”条信号导线的信号总线上,把“J”位的数据块从第一电子单元发送到第二电子单元,其中,0~“K-1”条信号导线出现故障,该方法包括步骤:识别信号总线中的故障信号导线和无故障信号导线;使用由识别信号总线中故障信号导线和无故障信号导线的步骤所发现的信息,设置第一电子单元中和第二电子单元中信号导线的故障状态;确定信号总线中的故障信号导线的数目“F”,确定信号总线中无故障信号导线的数目“K-F”;以及使用“J/(K-F)”个节拍,如果存在余数则再加上额外的节拍,在“K-F”条无故障信号导线上发送“J”位的数据块,其中,所述发送步骤还包括步骤:从“J”位的数据块中选择“K”位的数据组;使用“K-F”条无故障信号导线,在一个节拍上发送“K”位的数据组的“K-F”位;存储由于信号总线中“F”条故障信号导线而不能在该节拍上发送的“K”位的数据组中的“F”位;重复以上三个步骤,直至已经选择了“J”位的数据块的所有“J”位;以及使用一个或更多的“K-F”条无故障信号导线,在一个或多个额外的节拍上发送所存储的“F”位。

2. 根据权利要求1所述的方法,所述存储“F”位的步骤还包括把“F”位中的至少一位移位到移位寄存器的第一端点的步骤。

3. 根据权利要求2所述的方法,还包括把移位寄存器的至少一位发送到无故障信号导线的步骤。

4. 根据权利要求3所述的方法,还包括移动移位寄存器中的特定的位,以调整该特定的位,以耦接到无故障信号导线的步骤。

5. 根据权利要求1所述的方法,还包括步骤:在第二电子单元中,对于“J/(K-F)”个节拍,每一个节拍存储“K-F”位;以及如果“J/(K-F)”产生余数,则在额外的节拍中存储剩余的位。

6. 一种方法,用于在具有“K”条信号导线的信号总线上,把“J”位的数据块从第一电子单元发送到第二电子单元,其中,0~“K-1”条信号导线出现故障,该方法包括步骤:识别信号总线中的故障信号导线和无故障信号导线;使用由识别信号总线中故障信号导线和无故障信号导线的步骤所发现的信息,设置第一电子单元中和第二电子单元中信号导线的故障状态;确定信号总线中的故障信号导线的数目“F”;确定信号总线中无故障信号导线的数目“K-F”;以及使用“J/(K-F)”个节拍,如果存在余数则再加上额外的节拍,在“K-F”条无故障信号导线上发送“J”位的数据块,所述方法还包括步骤:从第一电子单元上的“J”位的数据块中选择“K-F”位的位组;使用信号总线中“K-F”条无故障信号导线,使用信号总线的节拍,从第一电子单元到第二电子单元发送“K-F”位的位组;重复以上的步骤,直至发送了所有“K-F”位组;以及使用某些或全部“K-F”条无故障信号导线,使用信号总线的额外的节拍,把第一电子单元上的“J”位的数据块的任何剩余的位发送到第二电子单元,其中,当在无故障信号导线上发送K-F位的位组时,保持J位数据块的位次序。

7. 根据权利要求1到6中的任何一个所述的方法,其中,在加电序列期间,识别无故障信号导线。

8. 根据权利要求1到6中的任何一个所述的方法,通过执行连线测试来识别无故障信号导线,其中,所述连线测试包括奇偶性校验错误、错误纠正代码错误、或循环冗余校验错误的处理。

9. 根据权利要求1到6中的任何一个所述的方法,还包括响应于识别信号总线中的故障信号导线,把耦接到故障信号导线的驱动器切换为高阻抗状态。

10. 一种装置,用于把“J”位的数据块从第一电子单元发送到第二电子单元,包括:第一数据块,位于第一电子单元中,含有用于发送的“J”位;存储器,位于第二电子单元中,能够容纳具有“J”位的第二数据块;信号总线,具有“K”条把第一电子单元耦接到第二电子单元的信号导线,该信号总线具有“F”条故障信号导线和“K-F”条无故障信号导线;诊断单元,耦接到第一电子单元和第二电子单元,能够识别信号总线上的“F”条故障信号导线和“K-F”条无故障信号导线,并且把故障标识信息存储在第一电子单元中和第二电子单元中;以及驱动定序器,位于第一电子单元中,其响应于故障标识信息,使用“J/(K-F)”个节拍,如果存在余数,则加上额外的节拍,仅使用“K-F”条无故障信号导线发送“J”位的数据,其中,用于发送的驱动定序器还包括:用于从“J”位的数据块中选择“K”位的数据组的设备;用于使用“K-F”条无故障信号导线在一个节拍上发送“K”位数据组的“K-F”位的设备;用于将由于信号总线中的“F”条故障信号导线而不能在所述节拍上被发送的“F”位存储在“K”位的数据组中的设备;用于使得能够重复位的选择、发送和存储直至已经选择了“J”位数据块中的所有“J”位的设备;以及用于使用一条或多条无故障信号导线在一个或多个额外节拍上发送所存储的“F”位的设备。

11. 根据权利要求10所述的装置,所述驱动定序器还包括能够被禁止的驱动器;其中,所述驱动定序器禁止被耦接到故障信号导线的驱动器。

12. 根据权利要求10所述的装置,所述第二电子单元还包括耦接到信号总线和诊断单元的接收定序器,该接收定序器能够一次把“K-F”位存储于第二数据块中,即存储从信号总线的“K-F”条无故障信号导线中所接收的“K-F”位,如果“J/(K-F)”具有余数,则该接收定序器还能够存储比“K-F”位少的位。

13. 一种装置,用于把“J”位的数据块从第一电子单元发送到第二电子单元,包括:第一数据块,位于第一电子单元中,含有用于发送的“J”位;存储器,位于第二电子单元中,能够容纳具有“J”位的第二数据块;信号总线,具有“K”条把第一电子单元耦接到第二电子单元的信号导线,该信号总线具有“F”条故障信号导线和“K-F”条无故障信号导线;诊断单元,耦接到第一电子单元和第二电子单元,能够识别信号总线上的“F”条故障信号导线和“K-F”条无故障信号导线,并且把故障标识信息存储在第一电子单元中和第二电子单元中;驱动定序器,位于第一电子单元中,其响应于故障标识信息,使用“J/(K-F)”个节拍,如果存在余数,则加上额外的节拍,仅使用“K-F”条无故障信号导线发送“J”位的数据,其中,所述驱动定序器还包括:用于从第一电子单元上的“J”位的数据块中选择“K-F”位的位组的设备;用于使用信号总线中的“K-F”条无故障信号导线并且使用信号总线上的一个节拍将“K-F”位的位组从第一电子单元发送到第二电子单元的设备;用于使得能够重复位的选择、发送和存储直至已经发送了所有“K-F”位组的设备;以及用于使用某些或全部“K-F”条无故障信号导线并且使用信号总线的额外的节拍,把第一电子单元上的“J”位的数据块的任何剩余的位发送到第二电子单元的设备,其中,所述装置是可操作的,以当在无故障信号导线上发送K-F位的位组时,保持J位数据块的位次序。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/660,217 US7392445B2 (en) | 2003-09-11 | 2003-09-11 | Autonomic bus reconfiguration for fault conditions |

| US10/660,217 | 2003-09-11 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1849589A CN1849589A (zh) | 2006-10-18 |

| CN100419701C true CN100419701C (zh) | 2008-09-17 |

Family

ID=34273623

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2004800261966A Expired - Fee Related CN100419701C (zh) | 2003-09-11 | 2004-09-10 | 针对故障状态的自主总线重新配置的方法和装置 |

Country Status (9)

| Country | Link |

|---|---|

| US (1) | US7392445B2 (zh) |

| EP (1) | EP1683018B1 (zh) |

| JP (1) | JP4392025B2 (zh) |

| KR (1) | KR20060061359A (zh) |

| CN (1) | CN100419701C (zh) |

| AT (1) | ATE367606T1 (zh) |

| DE (1) | DE602004007681T2 (zh) |

| TW (1) | TWI300527B (zh) |

| WO (1) | WO2005024633A1 (zh) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20070233930A1 (en) * | 2006-03-14 | 2007-10-04 | International Business Machines Corporation | System and method of resizing PCI Express bus widths on-demand |

| US8953292B2 (en) * | 2007-05-30 | 2015-02-10 | Infineon Technologies Ag | Bus interface and method for short-circuit detection |

| WO2009144824A1 (ja) * | 2008-05-30 | 2009-12-03 | 富士通株式会社 | 情報処理装置、転送回路及び情報処理装置のエラー制御方法 |

| JP5163298B2 (ja) * | 2008-06-04 | 2013-03-13 | 富士通株式会社 | 情報処理装置、データ伝送装置及びデータ伝送方法 |

| KR101593702B1 (ko) | 2009-03-22 | 2016-02-15 | 엘지전자 주식회사 | 무선 통신 시스템에서 참조 신호 전송 방법 및 장치 |

| WO2015006946A1 (en) * | 2013-07-18 | 2015-01-22 | Advanced Micro Devices, Inc. | Partitionable data bus |

| US9454419B2 (en) | 2013-07-18 | 2016-09-27 | Advanced Micro Devices, Inc. | Partitionable data bus |

| US10642951B1 (en) * | 2018-03-07 | 2020-05-05 | Xilinx, Inc. | Register pull-out for sequential circuit blocks in circuit designs |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5440538A (en) * | 1993-09-23 | 1995-08-08 | Massachusetts Institute Of Technology | Communication system with redundant links and data bit time multiplexing |

| US5717852A (en) * | 1993-03-10 | 1998-02-10 | Hitachi, Ltd. | Multiple bus control method and a system thereof |

| US6018810A (en) * | 1997-12-12 | 2000-01-25 | Compaq Computer Corporation | Fault-tolerant interconnection means in a computer system |

| CN1423198A (zh) * | 2001-11-29 | 2003-06-11 | 三星电子株式会社 | 用于有效地补偿故障信号线的数据总线装置和控制方法 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR2473820A1 (fr) * | 1980-01-11 | 1981-07-17 | Telecommunications Sa | Procede et systeme d'initialisation de la securisation d'une ligne d'une artere de transmission numerique |

| JP2825630B2 (ja) * | 1990-09-07 | 1998-11-18 | 株式会社日立製作所 | 回線切替方式 |

| US5678065A (en) * | 1994-09-19 | 1997-10-14 | Advanced Micro Devices, Inc. | Computer system employing an enable line for selectively adjusting a peripheral bus clock frequency |

| US5875301A (en) * | 1994-12-19 | 1999-02-23 | Apple Computer, Inc. | Method and apparatus for the addition and removal of nodes from a common interconnect |

| US5867645A (en) | 1996-09-30 | 1999-02-02 | Compaq Computer Corp. | Extended-bus functionality in conjunction with non-extended-bus functionality in the same bus system |

| US6366557B1 (en) * | 1997-10-31 | 2002-04-02 | Nortel Networks Limited | Method and apparatus for a Gigabit Ethernet MAC (GMAC) |

| JP3994360B2 (ja) * | 1998-05-20 | 2007-10-17 | ソニー株式会社 | 情報処理装置、情報処理方法、および記録媒体 |

| US7100071B2 (en) * | 1998-07-16 | 2006-08-29 | Hewlett-Packard Development Company, L.P. | System and method for allocating fail-over memory |

| US6466718B1 (en) * | 1999-12-29 | 2002-10-15 | Emc Corporation | Method and apparatus for transmitting fiber-channel and non-fiber channel signals through common cable |

| US6574753B1 (en) * | 2000-01-10 | 2003-06-03 | Emc Corporation | Peer link fault isolation |

| JP2003014819A (ja) * | 2001-07-03 | 2003-01-15 | Matsushita Electric Ind Co Ltd | 半導体配線基板,半導体デバイス,半導体デバイスのテスト方法及びその実装方法 |

| US6898730B1 (en) * | 2001-11-30 | 2005-05-24 | Western Digital Technologies, Inc. | System and method for fail-over switching in a disk storage medium |

| JP4188602B2 (ja) * | 2002-01-10 | 2008-11-26 | 株式会社日立製作所 | クラスタ型ディスク制御装置及びその制御方法 |

| US6918068B2 (en) * | 2002-04-08 | 2005-07-12 | Harris Corporation | Fault-tolerant communications system and associated methods |

| US7362697B2 (en) * | 2003-01-09 | 2008-04-22 | International Business Machines Corporation | Self-healing chip-to-chip interface |

| US7194581B2 (en) * | 2003-06-03 | 2007-03-20 | Intel Corporation | Memory channel with hot add/remove |

-

2003

- 2003-09-11 US US10/660,217 patent/US7392445B2/en not_active Expired - Fee Related

-

2004

- 2004-08-31 TW TW093126168A patent/TWI300527B/zh not_active IP Right Cessation

- 2004-09-10 KR KR1020067003363A patent/KR20060061359A/ko active IP Right Grant

- 2004-09-10 JP JP2006525832A patent/JP4392025B2/ja not_active Expired - Fee Related

- 2004-09-10 EP EP04787128A patent/EP1683018B1/en not_active Expired - Lifetime

- 2004-09-10 WO PCT/EP2004/052135 patent/WO2005024633A1/en active IP Right Grant

- 2004-09-10 CN CNB2004800261966A patent/CN100419701C/zh not_active Expired - Fee Related

- 2004-09-10 AT AT04787128T patent/ATE367606T1/de not_active IP Right Cessation

- 2004-09-10 DE DE602004007681T patent/DE602004007681T2/de not_active Expired - Lifetime

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5717852A (en) * | 1993-03-10 | 1998-02-10 | Hitachi, Ltd. | Multiple bus control method and a system thereof |

| US5440538A (en) * | 1993-09-23 | 1995-08-08 | Massachusetts Institute Of Technology | Communication system with redundant links and data bit time multiplexing |

| US6018810A (en) * | 1997-12-12 | 2000-01-25 | Compaq Computer Corporation | Fault-tolerant interconnection means in a computer system |

| CN1423198A (zh) * | 2001-11-29 | 2003-06-11 | 三星电子株式会社 | 用于有效地补偿故障信号线的数据总线装置和控制方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI300527B (en) | 2008-09-01 |

| KR20060061359A (ko) | 2006-06-07 |

| DE602004007681D1 (de) | 2007-08-30 |

| US7392445B2 (en) | 2008-06-24 |

| DE602004007681T2 (de) | 2008-04-30 |

| JP4392025B2 (ja) | 2009-12-24 |

| ATE367606T1 (de) | 2007-08-15 |

| TW200516402A (en) | 2005-05-16 |

| EP1683018A1 (en) | 2006-07-26 |

| US20050058086A1 (en) | 2005-03-17 |

| WO2005024633A1 (en) | 2005-03-17 |

| EP1683018B1 (en) | 2007-07-18 |

| CN1849589A (zh) | 2006-10-18 |

| JP2007505380A (ja) | 2007-03-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US20240161795A1 (en) | Memory buffer with data scrambling and error correction | |

| US8140936B2 (en) | System for a combined error correction code and cyclic redundancy check code for a memory channel | |

| US6035414A (en) | Reliability of crossbar switches in an information processing system | |

| US9348785B2 (en) | Flexible and expandable memory architectures | |

| US8645747B2 (en) | Cable redundancy and failover for multi-lane PCI express IO interconnections | |

| US6882082B2 (en) | Memory repeater | |

| US20130080825A1 (en) | Cable redundancy and failover for multi-lane pci express io interconnections | |

| JP4072424B2 (ja) | メモリシステム及びその制御方法 | |

| US20060026349A1 (en) | System, method and storage medium for providing a serialized memory interface with a bus repeater | |

| EP1683017A2 (en) | Early crc delivery for partial frame | |

| JPH054699B2 (zh) | ||

| US20100005335A1 (en) | Microprocessor interface with dynamic segment sparing and repair | |

| EP0333593B1 (en) | A data processing system capable of fault diagnosis | |

| CN100419701C (zh) | 针对故障状态的自主总线重新配置的方法和装置 | |

| US7673170B2 (en) | Personal computer bus protocol with error correction mode | |

| US7328368B2 (en) | Dynamic interconnect width reduction to improve interconnect availability | |

| US5790810A (en) | Input/output unit for a processor of a computer system having partitioned functional elements that are selectively disabled | |

| US7471623B2 (en) | Systems and methods for a unified computer system fabric | |

| SU783795A2 (ru) | Процессор | |

| JPH08272703A (ja) | バス制御システム | |

| JP4497963B2 (ja) | ストレージ装置 | |

| JPH04302333A (ja) | データ処理装置 | |

| JPH09282109A (ja) | ディスクアレイ装置 | |

| JPH05347653A (ja) | データ伝送障害検出方式 | |

| JPH05113939A (ja) | データ転送装置および方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20080917 Termination date: 20100910 |