CN100380819C - 数据传输控制装置及电子设备 - Google Patents

数据传输控制装置及电子设备 Download PDFInfo

- Publication number

- CN100380819C CN100380819C CNB2005100535341A CN200510053534A CN100380819C CN 100380819 C CN100380819 C CN 100380819C CN B2005100535341 A CNB2005100535341 A CN B2005100535341A CN 200510053534 A CN200510053534 A CN 200510053534A CN 100380819 C CN100380819 C CN 100380819C

- Authority

- CN

- China

- Prior art keywords

- data transfer

- synchronizing signal

- transfer controller

- interface

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/14—Digital output to display device ; Cooperation and interconnection of the display device with other functional units

- G06F3/1423—Digital output to display device ; Cooperation and interconnection of the display device with other functional units controlling a plurality of local displays, e.g. CRT and flat panel display

- G06F3/1431—Digital output to display device ; Cooperation and interconnection of the display device with other functional units controlling a plurality of local displays, e.g. CRT and flat panel display using a single graphics controller

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/003—Details of a display terminal, the details relating to the control arrangement of the display terminal and to the interfaces thereto

- G09G5/006—Details of the interface to the display terminal

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2213/00—Indexing scheme relating to interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F2213/0038—System on Chip

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2370/00—Aspects of data communication

- G09G2370/10—Use of a protocol of communication by packets in interfaces along the display data pipeline

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/12—Synchronisation between the display unit and other units, e.g. other display units, video-disc players

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Human Computer Interaction (AREA)

- Computer Graphics (AREA)

- Computer Hardware Design (AREA)

- General Engineering & Computer Science (AREA)

- Information Transfer Systems (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Digital Computer Display Output (AREA)

- Liquid Crystal Display Device Control (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Controls And Circuits For Display Device (AREA)

Abstract

本发明公开了一种用简单处理再生同步信号的数据传输控制装置和包含该装置的电子设备。该数据传输控制装置(30)包括:链路控制器(100),用于分析通过串行总线从主机侧数据传输控制装置(10)接收到的包;接口电路(110),用于产生接口信号,并将产生的接口信号输出到接口总线。从主机侧数据传输控制装置(10)通过串行总线传输的包,包括用于设置同步信号码的同步信号码域;接口电路(110)基于设置在包的所述同步信号码,产生包括在接口信号的同步信号FPFRAME、FPLINE。

Description

技术领域

本发明涉及一种数据传输控制装置及电子设备。

背景技术

近年来,以降低EMI噪声等为目的的接口,如LVDS(低压差动信号传输技术:Low Voltage Differential Signaling)等的高速串行传输接口已经被引起关注。在该高速串行传输中,发送电路利用差动信号(Differential Signals)发送串行化了的数据,接收电路将差动信号差动放大,从而实现数据传输。DVI(数字显示接口:DigitalVisual Interface)等的接口作为这种高速串行接口已被众所周知。

普通手机包括:第一设备区,设有输入电话号码与字符的按钮;第二设备区,设有主LCD(液晶显示器:Liquid Crystal Display)、子LCD、或者相机;以及连接区,比如连接第一设备区与第二设备区的铰链等。这种情况下,通过使用了差动信号的串行传输方式,进行第一设备区的第一基板与第二设备区的第二基板之间的数据传输,可减少通过连接区的配线的数量,达到较好效果。

然而,当采用串行传输方式进行这种连接区的数据传输时,最好能尽量减少进行串行传输控制的主机侧数据传输控制装置以及目标侧数据传输控制装置的功耗。另外也最好能尽量减少通过串行总线传输的数据量。而且,最好还能尽量减少访问主机侧数据传输控制装置,并进行各种设定的系统装置(CPU、显示控制器等)的处理负荷。

另外,当系统装置向主机侧数据传输控制装置输出RGB接口的同步信号的时候,需要目标侧数据传输控制装置用简单的处理再生该同步信号,输出到与接口总线连接的装置。

专利文献1:日本特开2001-222249号公报

发明内容

鉴于上述技术问题,本发明的目的在于提供一种对同步信号进行简单处理就可以再生的数据传输控制装置及包括该数据传输控制装置的电子设备。

本发明涉及一种用于控制数据传输的数据传输控制装置,通过串行总线与主机侧数据传输控制装置连接,通过接口总线与一个或多个装置连接,其包括:链路控制器,用于分析通过串行总线从主机侧数据传输控制装置接收到的包;以及接口电路,用于产生接口信号,并将产生的接口信号输出到接口总线;从所述主机侧数据传输控制装置通过串行总线传输的包,包括用于设置同步信号码的同步信号码域;所述链路控制器对所述同步信号进行分析,所述同步信号设定在从主机侧数据传输控制装置传输的包的所述同步信号码域中;所述接口电路基于所述链路控制器对所述同步信号码的分析结果,产生包括在接口信号的同步信号,且输出到所述一个或多个装置中。

根据本发明,在包的同步信号码域设置同步信号的包,通过串行总线从主机侧数据传输控制装置传输。并且,基于设置在该包中的同步信号码产生被包括在接口信号的同步信号。这样,只需在包中设置同步信号码,就可以生成同步信号,用简单的处理再生同步信号。

在本发明中,所述链路控制器,在显示期间从主机侧数据传输控制装置接收数据域中设置有数据的显示期间包;在非显示期间从主机侧数据传输控制装置接收数据域中未设置数据的非显示期间包。

这样,在非显示期间,数据域中未设置数据的数据量少的包,通过串行总线传输,提高数据传输的效率。

在本发明中,所述链路控制器,当从主机侧数据传输控制装置接收到数据域中设置有数据的显示周期包时,向所述接口电路输出含有设置在包中的所述同步信号码的包头和设置在包中的数据;当从主机侧数据传输控制装置接收到数据域中未设置数据的非显示周期包时,向所述接口电路输出含有设置在包中的所述同步信号码的包头。

本发明涉及一种用于控制数据传输的数据传输控制装置,通过系统总线与系统装置连接,通过串行总线与目标侧数据传输控制装置连接,其包括:接口电路,用于执行所述用于控制数据传输的数据传输控制装置和系统装置之间的接口处理,所述系统装置是外部装置;以及链路控制器,用于产生通过串行总线传送给目标侧数据传输控制装置的包;所述接口电路从所述系统装置接收同步信号,所述链路控制器,将与从所述系统装置接收的同步信号相应的同步信号码设置在包的同步信号码域,并将设置有所述同步信号码的包发送到目标侧数据传输控制装置。

根据本发明,接收来自系统装置的同步信号,在包的同步信号码域设置对应于该同步信号的同步信号码域。并且,该包通过串行总线被传输至目标侧数据传输控制装置。这样,目标侧数据传输控制装置基于包括在包的同步信号码,产生包括在接口信号的同步信号,用简单的处理再生同步信号。

在本发明中,所述链路控制器,在显示期间产生在所述同步信号码域设置同步信号码、数据域中设置有数据的显示期间包;在非显示期间产生在同步信号码域设置同步信号码、数据域中未设置数据的非显示期间包。

这样,在非显示期间,数据域中未设置数据的数据量少的包,通过串行总线传输,提高数据传输的效率。

在本发明中,所述接口电路包括:第一边缘检测器,用于检测来自所述系统装置的垂直同步信号的边缘,并输出第一边缘检测信号;第二边缘检测器,用于检测来自所述系统装置的水平同步信号的边缘,并输出第二边缘检测信号;采集电路,基于给定的时钟信号对所述第一边缘检测信号和第二边缘检测信号进行采集处理,确定设置在包的所述同步信号码。

这样,由于可以基于频率不太高的时钟信号进行采集处理,因此可以实现数据传输控制装置的低耗电。

在本发明中,所述采集电路包括计数器,所述计数器基于所述第一边缘检测信号和第二边缘检测信号进行计数处理,所述采集电路基于所述计数器的计数结果判断显示期间和非显示期间。

这样,可以用简单的处理对显示期间和非显示期间进行判断。

本发明涉及一种电子设备,其包括:上述任何一项中所述的目标侧数据传输控制装置;主机侧数据传输控制装置,通过串行总线与所述目标侧数据传输控制装置连接;以及一个或者多个装置,通过接口总线与所述目标侧数据传输控制装置连接。

本发明涉及一种电子设备,其包括:上述任何一项中所述的主机侧数据传输控制装置;目标侧数据传输控制装置,通过串行总线与所述主机侧数据传输控制装置连接;以及一个或者多个装置,通过接口总线与所述目标侧数据传输控制装置连接。

附图说明

图1是主机侧、目标侧的数据传输控制装置的构成例。

图2是RGB接口信号示意图。

图3A和3B是本实施形式的方法图。

图4A和4B是RGB接口信号的信号波形图。

图5是定时信息示意图。

图6A和6B是包的格式图。

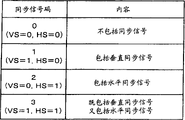

图7是同步信号码示意图。

图8是利用同步信号码产生同步信号的方法图。

图9是反映本发明处理过程的流程图。

图10是主机侧收发器以及目标侧收发器图。

图11是主机侧链路控制器和接口电路图。

图12是目标侧链路控制器和接口电路图。

图13A、13B是主机侧RGB接口电路以及目标侧RGB接口电路图。

图14是电子设备图。

具体实施方式

下面,详细说明本发明的优选实施例。并且,下面描述的实施例并不是对权利要求所保护范围的不当限定,在实施例中所描述的结构并不都是本发明解决技术问题所必须的。

1.数据传输控制装置的构成例

图1是主机侧传输控制装置10和目标侧传输控制装置30的构成例的示意图。在本实施方式中,所说的系统总线和接口总线之间的桥接功能通过使用这些主机侧传输控制装置10和目标侧传输控制装置30来实现。数据传输控制装置10和30不限于图1所示的结构,可省略图1中的某些电路模块,或者改变电路模块之间的连接方式,或者增加不同于图1的其他电路模块。例如,主机侧传输数据传输控制装置10可以省去收发器20,目标侧传输控制装置30可省去收发器40。

主机(TX)端数据传输控制器10和目标(RX)端数据传输控制器30通过差动信号(differential signals)的串行总线传输包。具体地说,通过电流驱动(或者电压驱动)串行总线的差动信号线(differential signal lines)进行包的发送接收。

主机侧数据传输控制装置10包括接口电路92,该接口电路92用于完成该数据传输装置10与CPU、显示控制器等的系统装置5之间的接口处理工作。而且,连接系统装置5与接口电路92的系统总线包括用于传输芯片选择信号CS1和CS2的信号线。系统总线还包括用于传输HSYNC/RD、VSYNC/WR、CLK/A0和D[17:0]的信号的信号线。这些信号线作为RGB接口总线或者MPU(MicroProcessor Unit)接口总线使用。

这些信号线作为RGB接口总线使用时,信号HSYNC/RD、VSYNC/WR、CLK/A0和D[17:0]分别用作水平同步信号、垂直同步信号、时钟信号和数据信号。比如,D[17:0]中的D[5:0]、D[11:6]和D[17:12]分别用作R(红)、G(绿)、B(蓝)数据信号。另一方面,这些信号线作为MPU接口总线使用时,HSYNC/RD、VSYNC/WR、CLK/A0和D[17:0]分别用作读信号、写信号、地址0信号(指令/参数识别信号)和数据信号。

系统总线包括用于传输SCS、SR/W、SA0、SIO、和SCK的信号的信号线。这些信号用作串行接口信号。具体地说,SCS、SR/W、SA0、SIO、和SCK分别用作串行接口的芯片选择信号、读/写信号、地址0信号、数据信号和时钟信号。再者,在5针的串行接口中,这些信号SCS、SR/W、SA0、SIO、SCK全部被使用。另一方面,在4针的串行接口中,不使用SR/W,在3针的串行接口中,不使用SR/W与SA0。

信号ITN是自主机侧数据传输控制装置10向系统装置5的中断信号。端子CNF[2:0]用于决定系统装置5和主机侧数据传输控制装置10之间的接口类型。根据CNF[2:0]的设定,将系统装置5和主机侧数据传输装置10之间的接口设置为RGB接口和80MPU接口,也可设置为RGB接口和68MPU接口,可仅设置为80MPU接口,也可仅设置为68MPU接口,或者仅设置为串行接口。

主机侧数据传输控制装置10包括进行链路层处理的链路控制器90(链路层电路)。该链路控制器90产生通过串行总线(LVDS)传输到目标侧数据传输控制装置30的包(请求包、流包等),并进行将生成的包发送的处理。具体地说,链路控制器90启动发送事务处理,并指示收发器20发送生成的包。

主机侧数据传输控制装置10包括执行物理层处理等的收发器20(PHY)。该收发器20将由链路控制器90指示的包通过串行总线向目标侧数据传输控制装置30发送。收发器20也接收来自目标侧数据传输控制器30的包。这种情况下,链路控制器90分析接收到的包,进行链路层(事务处理层)的处理。

主机侧数据传输控制装置10包括内部寄存器250。该内部寄存器250包括诸如端口访问寄存器、配置寄存器、LVDS寄存器、中断控制寄存器和目标(RX)端寄存器等。系统装置5通过系统总线向内部寄存器250写入地址(命令)或数据(参数),或者从内部寄存器250中读取读数据、状态信息等。另外内部寄存器250中的目标侧寄存器的内容被传输到目标侧数据传输控制装置30的内部寄存器350。即,目标侧的内部寄存器350变为主机侧的内部寄存器250的子设备(影子寄存器)。

目标侧数据传输控制装置30包括执行物理层处理等的收发器40(PHY)。通过串行总线,该收发器40接收来自主机侧数据传输控制装置10的包。该收发器40还向主机侧数据传输控制装置10发送包。这种情况下,链路控制器100生成要发送的包,并指示发送生成的包。

目标侧数据传输控制装置30包括链路控制器100(链路层电路)。该链路控制器100进行链路层(事务处理层)的处理,接收来自主机侧数据传输控制装置10的包,分析接收到的包。信号TGINT是从目标侧传输控制器30至主机侧数据传输控制装置10的中断信号。

目标侧数据传输控制装置30包括接口电路110,该接口电路110进行该数据传输控制装置30和LCD1、LCD2、通用装置GD(这些装置GD广义上为第一~第N装置)等之间的接口处理。该接口电路110产生各种接口信号(第一~第N接口信号),将产生的接口信号输出至接口总线。具体地讲,该接口电路110包括RGB接口电路310、MPU接口电路320、串行接口电路330(这些接口电路广义上为第一~第N接口电路)。而且,RGB接口电路310、MPU接口电路320和串行接口电路330分别产生和输出RGB接口信号、MPU接口信号和串行接口信号。LCD1和LCD2是显示面板和驱动显示面板的显示驱动器的总称。

接口总线包括传输FPCS1、FPCS2、FPCS3、VCIN1、VCIN2、WAIT等信号的信号线,以及RGB/MPU、SERIAL和I2C(内部集成电路:Inter Integrated Circuit)等的总线。FPCS1、FPCS2和FPCS3是芯片选择信号。VCIN1和VCIN2是标识已经写完一帧的信号,WAIT是等待请求信号。RGB/MPU总线是RGB或者MPU的接口总线。该RGB/MPU总线与系统装置端一样,包括水平同步信号(读信号)、垂直同步信号(写信号)、时钟信号、地址0信号和数据信号等。此外,SERIAL总线是串行接口总线,包括串行传输的读/写信号、地址0信号、数据信号、时钟信号等。此外,I2C总线是利用两条信号线(时钟信号和数据信号)完成比较近距离串行传输的总线。

目标侧数据传输控制装置30包括内部寄存器350。该内部存储器350存储用于规定从接口电路110输出的接口信号的信号形式(输出格式)的接口信息等。具体地讲,内部寄存器350存储定时信息等,该定时信息用于特别指定接口信号的信号电平发生变化的定时。这种情况下,在主机侧的内部寄存器250中存储的信息中目标侧所需要的信息通过串行总线(差动信号线)被传输到目标侧上,并写入目标侧的内部寄存器350。

以下为简化说明,重点表述主机侧数据传输控制装置10向目标侧数据传输控制装置30发送包时的本实施例的配置和动作情况,同时,目标侧数据传输控制装置30向主机侧数据传输控制装置10发送包时的配置和动作情况,与上面相同。

2.基于同步信号码生成同步信号

在本实施方式中,在从主机侧通过差动信号(也可以是单端传输)的串行总线向目标侧传输的包,设置同步信号码域。并且,基于设置在该同步信号码域的同步信号码,目标侧接口电路产生同步信号输出到接口总线。

例如在图2中,示出了系统装置5输出的接口信号的例子。在图2中,VSYNC是垂直同步信号、HSYNC是水平同步信号。另外,D[17:0]是数据信号(RGB数据信号、像素数据信号)。

如图3所示,主机侧接口电路92从系统装置5(CPU、显示控制器等)接收图2所示的同步信号VSYNC、HSYNC。并且,从系统装置5也接收数据信号D[17:0]。

从系统装置5接收VSYNC、HSYNC的主机侧接口电路92,进行VSYNC、HSYNC的检测处理。并且,主机侧的链路控制器90基于该检测结果,将对应于从系统装置5接收的VSYNC、HSYNC的同步信号码如图3(A)所示设置在包(包头)的同步信号码域。例如,当检测出VSYNC的时候,将表示VSYNC被检测出的同步信号码设置在包中。当检测出HSYNC的时候,将表示HSYNC被检测出的同步信号码设置在包中。另外,当检测出VSYNC、HSYNC的时候,将表示VSYNC、HSYNC被检测出的同步信号码设置在包中。在存在数据信号D[17:0]的显示期间中,在包的数据域设置对应于D[17:0]的数据。之后,将产生的包通过差动信号的串行总线发送到目标侧数据传输控制装置30。

目标侧的链路控制器100分析从主机侧接收的包,检测设置在包中的同步信号码。当设置在包中的同步信号码被检测出的时候,目标侧的接口电路110基于检测出的同步信号码,产生同步信号FPFRAME、FPLINE,并输出到接口总线。FPFRAME、FPLINE分别相当于垂直同步信号、水平同步信号。目标侧的接口电路110,将对应于设置在包的数据域的数据的数据信号FPDAT[17:0]输出到接口总线。如上所述,利用包括在包中的同步信号码产生同步信号,可以用简单处理再生同步信号。

另外,在本实施方式中,如图3(A)所示,在显示期间,主机侧的链路控制器90产生在同步信号码域设置同步信号码、数据域中设置有数据的显示期间包。另一方面,如图3(B)所示,主机侧的链路控制器90在非显示期间产生在同步信号码域设置同步信号码、数据域中未设置数据的非显示期间包。

并且,目标侧的链路控制器100在图3(A)的显示期间,从主机侧传输控制装置10接收数据域中设置有数据的显示期间包。另一方面,在图3(B)的非显示期间,从主机侧传输控制装置10接收数据域在未设置数据的非显示期间包。

这样,在非显示期间,可以减少通过串行总线传输的数据量,提高数据传输效率。

3.基于定时信息生成接口信号

在本实施例中,目标(RX)接口电路110依照事先设置的定时信息自动产生接口信号(接口控制信号和数据信号)。具体地说,在目标侧内部寄存器350中设定用于特别指定接口信号的信号电平的变定时的定时信息。接口电路110从内部寄存器350中读出该定时信息。接口电路110产生以按照定时信息的定时进行信号电平变化的接口信号,并输出接口信号。具体地说,例如,RGB接口电路310产生按照该定时信息的接口信号。

内部寄存器350的定时信息,通过串行总线(LVDS),根据接收到的来自主机侧数据传输装置10的包被设定。也就是说,作为数据传输的起始设置,系统装置5在主机侧的内部寄存器250中设置接口信号的定时信息。利用内部寄存器250所包含的寄存传输开始寄存器,系统装置5命令寄存器传输开始。于是,写入到内部寄存器250的接口信号的定时信息通过串行总线从主机侧数据传输控制装置10包传输到目标侧传输控制装置30。具体地说,例如,在包的数据域上设置定时信息,并被进行包传输。而且,传输的定时信息写入到目标侧的寄存器350上。

上述初始设置完成后,系统装置5写入数据(命令、参数)至内部寄存器250的端口写寄存器。于是,通过串行总线,主机侧数据传输控制装置10发送数据域中含有数据的包至目标侧传输控制装置30。依照设置在内部寄存器350的定时信息的所指明的时限,接口电路110接口信号至接口总线,该接口信号包括包中设有数据的信号。具体地说,通过RGB总线,构成接口信号的接口控制信号(水平同步信号,垂直同步信号等)和数据信号输出至LCD1的RGB端口。这样,LCD1能够根据RGB数据执行显示操作。

例如普通的手机包括:第一设备区(第一单元),设有输入电话号码或者字符的按钮;第二设备区(第二单元),设有主显示器、子显示器、或者相机;以及用来连接第一设备区和第二设备区的连接区(铰接区)。这种情况下,在第一设备区中设置系统装置5,在第二设备区中设置作为主显示器的LCD1和作为子显示器的LCD2。

不过,按照以前的做法,图2所示的垂直同步信号VSYNC、水平同步信号HSYNC,以及数据信号D[17:0]等,由系统装置5直接输出到LCD1上。因此,通过第一设备区与第二设备区之间连接区的配线数目大大增加,连接区的设计变得困难。另外,也可能产生EMI噪声。

关于此问题,在本发明的实施例中,通过串行总线,定时信息和数据从主机侧传输至目标侧。因此,根据本实施例,通过将串行总线的配线区设置在第一设备区与第二设备区的连接区上,从而能够减少通过该连接区的配线线数,使连接区的设计变得容易。除此之外,也可有效降低EMI噪声的发生。

作为诸如比较例可以使用下面的方法。值得注意的是,在高频(比如,两倍于像素时钟的频率)采样时钟信号下,主机侧数据传输控制装置10从图2所示的系统装置5采集到接口信号VSYNC、HSYNC和D[17:0],并且把采集到的结果信息通过串行总线发送至目标侧数据传输控制装置30。而且,通过使目标侧数据传输控制装置30重新产生采集结果信息,将与系统装置5输出的图2所示的信号VSYNC、HSYNC和D[17:0]相同的接口信号输出到LCD1。

但是,按照比较例的方法,由于主机侧数据传输控制装置10的采样时钟信号频率提高,功耗也变大。除此之外,由于串行总线的传输数据数量(通信量)的提高,不能实现有效的数据传输。

关于上述问题,在本实施例中,定时信息的传输先于数据的传输,根据该定时信息,接口电路110(RGB接口电路310)自动产生接口信号。这样,主机侧数据传输控制装置10无需在高频采样时钟信号下从系统装置5采集接口信号VSYNC、HSYNC和D[17:0],由此,可有效降低功耗。除此之外,即使不从主机侧向目标侧逐次地传输接口信息所涉及的细节信息,也能产生信号电平以适当定时发生变化的接口信号。因此,通过串行总线的传输数据数量可降低,为此,可实现有效的数据传输。

4.接口信号的信号波形

图4(A)和4(B)表示了由接口电路110的RGB接口电路310产生的RGB接口信号的信号波形实例。图4(A)和4(B)中,FPFRAME是垂直同步信号,FPLINE是水平同步信号,FPDAT[17:0]是RGB数据信号,FPDRDY是数据准备信号,FPSHIFT是时钟信号(像素时钟信号)。这些信号是RGB总线接口信号。

如图4(A)所示,当信号FPFRAME处在激活状态,信号FPLINE只激活预设次数时,从无显示期间(前边缘)转移到显示期间,首行(第一扫描线)的数据信号FPDAT[17:0]输出。而且,当所有行的数据信号输出后,显示期间转移到无显示期间(后边缘)。

图4(B)是将一行数据信号传输的状态放大的信号波形图。例如,信号FPDRDY激活后,一行成分的数据信号FPDATA[17:0]的各位与时钟信号FPSHIFT的诸如上升沿同步输出。

根据本实施例,图4(A)中t1=VT,t2=VPW,t3=VDPS和t4=VDP作为定时信息,设置在目标侧的内部寄存器350中。图4(B)中t2=HT、t3=HPW、t4=HDPS和t5=HDP作为定时信息设置在内部寄存器350中。

图5所示,HT(水平总和:Horizontal Total)是水平同步期间的长度。HDP(水平显示期间:Horizontal Display Period)是水平同步期间上显示期间长度。HDPS(水平显示期间开始点:HorizontalDisplay Period Start position)是水平同步期间中显示期间的开始位置。HPW(水平脉冲宽度:Horizontal Pulse Width)是水平同步信号的脉冲宽度。VT(垂直总和:Vertical Total)是垂直同步期间长度。VDP(垂直显示期间:Vertical Display Period)是垂直同步期间中显示期间长度。VDPS(垂直显示期间开始点:Vertical Display PeriodStart position)是垂直同步期间中显示期间的开始点。VPW(垂直脉冲宽度:Vertical Pulse Width)是垂直同步信号的脉冲宽度。

本实施例中,这些定时信息(HT、HDP、HDPS、HPW、VT、VDP、VDPS和VPW)在初始化时由系统装置5写入主机侧的内部寄存器250中。其后,这些定时信息通过串行总线发送到目标侧,写入到目标侧的内部寄存器350。利用这种定时信息,容易自动生成图4(A)和4(B)表示的RGB接口信号。在此,将定时信息HT、HDP、HDPS、HPW、VT、VDP、VDPS和VPW作为可以任意值设定的定时信息,不需要全部存储于内部寄存器350中,可以将其中的一部分设为固定值。例如,定时信息HPW和VPW可以被设为固定值,且可以不必作为定时信息存储于内置寄存器350中。

5.包结构

图6(A)和6(B)示出了通过串行总线(LVDS)传输的包的格式实例。每个包的域构成和域配置不限于图6(A)和6(B)所示的例子,可以有各种变形例。

图6(A)所示的请求包(写请求包或者读请求包)是请求写入或者读出数据(参数)的包。该写请求包包括应答请求、包类型、标签、重试、地址长度、数据长度、地址(命令)、连续、地址自动刷新、刷新次数、端口号、数据(参数)和CRC(循环冗余码校验:Cyclic Redundancy Check)的域。读请求包不包括数据域。

这里,应答请求域是用于通知是否进行基于应答包的信息交换。包类型域是通知包的类型的域。本实施例中,包类型包括写请求包、读请求包、响应包、应答包、连续包等。标签是用于表示当前事务是否进行重试的域。地址大小域是用于通知设置在包地址域中的地址的大小的域。数据长度域是用于通知写数据和读数据的长度的域。地址(命令)域是用于通知数据存取目的地(读目的地或者写目的地)的地址的域。地址自动刷新域是用于设定地址自动刷新的模式的域,刷新次数域是用于设定地址自动刷新的数目的域。端口号码域是用于设定端口号码的域。数据(参数)域是用于设定由包传输的数据的域。CRC域是用于对包包头和包数据进行错误校验的域。

图6(B)的连续包是用于进行数据(参数)连续传输的包。该连续传输是指发送方和接收方保持同步的同时进行高速和连续的数据传输。该连续包包括包类型、标签、数据长度、地址(命令)、同步信号码、端口号码、数据(参数)和CRC的域。

6.同步信号码

图7表示了设置在包的同步信号域中的同步信号码的实例。“0”(VS=0、HS=0)同步信号码表示包不包括同步信号。也就是说,由于同步信号(垂直同步信号和水平同步信号)不在主机侧被检测,因此不需要在目标侧输出同步信号。“1”(VS=1、HS=0)同步信号码表示包包括垂直同步信号。也就是说,由于垂直同步信号已经在主机侧被检测,需要在目标侧输出垂直同步信号。“2”(VS=0、HS=1)同步信号码表示包包括水平同步信号。也就是说,由于水平同步信号已经在主机侧检测,需要在目标侧输出水平同步信号。“3”(VS=1,HS=1)同步信号码表示包包括垂直同步信号和水平同步信号。也就是说,由于垂直同步信号和水平同步信号已经在主机侧被检测,需要在目标侧输出垂直同步信号和水平同步信号。

如图6(B)所示,在本实施例中,通过串行总线(LVDS))))从主机侧数据传输控制装置10传输的包含有用于设置同步信号码的同步信号码域。而且,在本实施例中,接口电路110(RGB接口电路310)根据包中设置的同步信号码而产生同步信号(垂直同步信号、水平同步信号)。具体地说,根据内部寄存器350(定时信息寄存器)上设置的定时信息(HT、HDP、HDPS、HPW、VT、VDP、VDPS和VPW)和包中设置的同步信号码,产生同步信号。

例如,假设系统装置5输出如图2所示的RGB接口信号VSYNC、HSYNC、和D[17:0]到主机侧数据传输控制装置10。这种情况下,主机侧数据传输控制装置10检测输入的垂直同步信号VSYNC和水平同步信号HSYNC。当诸如检测到垂直同步信号VSYNC时,如图7所示。主机侧数据控制装置10产生同步信号码设置为VS=1、HS=0的包,并发送生成包到目标侧传输控制装置30。同样,当检测到水平同步信号HSYNC时,主机侧数据控制装置10产生同步信号码设置为VS=0、HS=1的包,并发送生成包到目标侧传输控制装置30。而且,当垂直同步信号VSYNC和水平同步信号HSYNC两个都检测到时,主机侧数据控制装置10产生同步信号码设置为VS=1、HS=1的包,并发送生成包到目标侧传输控制装置30。

并且,目标侧数据传输控制装置30的链路控制器100分析从主机侧数据传输控制装置10接收到的包中携带的同步信号码。根据包中含有的同步信号码,如图8所示,接口电路110的RGB接口电路310产生的信号FPFRAME和FPLINE。这些信号FPFRAME和FPLINE对应于图2所示的垂直同步信号VSYNC和水平同步信号HSYNC。

具体地说,由图8中A1和A2接收的包PK1、PK2、PK12和PK13携带的同步信号码为VS=1、HS=1。因此,这种情况下,如A3和A4所示,将信号FPFRAME和FPLINE共同激活并输出。由A5接收到的包PK3~PK11携带的同步信号码为VS=0、HS=1。因此,这种情况下,如A6所示,每当A6接收到包,信号FPLINE才被激活并输出。

在本实施例中,信号FPFRAME、FPLINE和FPDAT的信号电平的精确变化定时可根据设置在内部寄存器350的定时信息(HT、HDP、HDPS、HPW、VT、VDP、VDPS和VPW)进行调整。也就是说,由主机侧数据传输控制装置10仅接收通知哪个同步信号发生了变化的信息(同步信号码),并按照数据传输前传输来的定时信息微整使同步信号或者数据信号发生改变的实际定时。

当目标侧数据传输控制装置30接收到诸如VS=1和HS=1的包PK1时,如图8由B 1所示,将信号FPFRAME激活(低电平)后,并经过预定期间(图3(B)中t1)后,如B2所示,将信号FPLINE激活(低电平)。其后,当经过定时信息HPW(图4(B)中t2)时,如B3所示,将信号FPLINE设为非激活(高电平)。

接着,目标侧数据传输控制装置30接收到VS=1和HS=1的包PK2,经过定时信息HT的期间(图4(B)中t2)时,如B4所示,将信号FPLINE激活。其后,当经过定时信息HPW的期间时,如B5所示,将信号FPLINE设为非激活。

接着,当目标侧数据传输控制装置30接收到VS=0和HS=1的包PK3、从B1的定时经过定时信息VPW的期间(图4(A)中t2)时,如B6所示,将信号FPFRAME设为非激活(高电平)。当定时信息VDPS的期间(图4(A)中t3)从B2的定时中经过时,如B7所示,将信号FPLINE激活。接着,当定时信息HPW的期间(图4(A)中t3)从B7的定时中经过时,如B8所示,将信号FPLINE设为非激活。而且,当定时信息HDPS的期间(图4(B)中t4)从B7的定时中经过时,如B9所示,开始首行数据信号FPDAT的输出。

如上所述,在本实施例中,在数据传输以前,定时信息从主机侧传输到目标侧,并且设置在内部寄存器350中。其后,包含同步信号码的包从主机侧传输到目标侧。于是,目标侧的接口电路110,根据设置在内部寄存器350的定时信息微调输出定时的同时,该接口电路110输出由同步信号码指示输出的同步信号到接口总线。这样,在主机侧,通过高频的时钟信号从系统装置5采集接口信号不是必须,由此,功耗可降低。此外,由于通过串行总线从主机侧到目标侧的数据传输数量可降低,从而可实现有效数据传输。

7.非显示期间包

在本实施例中,如图8所示,即使在非显示期间VNDP中,含有同步信号码的包必须从主机侧传输到目标侧,。然而,数据信号FPDAT可只在显示期间被输出,而不需要在非显示期间VNDP输出。

因此,本实施例中,在显示期间VDP中,数据域中设置有数据的显示期间的包(连续包)由主机侧传输至目标侧,另一方面。在非显示期间VNDP中,数据域中未设置数据的非显示期间的包由主机侧传输至目标侧。具体地说,主机侧数据传输控制装置10的链路控制器90,在显示期间VDP中,产生同步信号码设置在同步信号码域和数据设置在数据域的显示期间包,并输出该包到目标侧数据传输控制装置30。另一方面,链路控制器90,在非显示期间VNDP中,产生同步信号码设置在同步信号码域和数据不设置在数据域的非显示期间包,并输出该包到目标侧数据传输控制装置30。

在显示期间VDP中,目标侧数据传输控制装置30的链路控制器100接收到来自主机侧数据传输控制装置10的数据设置在数据域的显示期间包。另一方面,在非显示期间VNDP中,链路控制器100接收到来自主机侧数据传输控制装置10的数据不设置在数据域的非显示期间包。具体地说,当该链路控制器100接收到来自主机侧数据传输控制装置10的数据设置在数据域的显示期间包时,将含有包中设置的同步信号码的包头和包中设置的数据,输出到接口电路110(RGB接口电路310)。另一方面,当链路控制器100接收到来自主机侧数据传输控制装置10的无数据设置在数据域的非显示期间包时,链路控制器100只将含有包中设置的同步信号码的包头,输出到接口电路110,而不输出数据。

这样,在非显示期间VNDP中,无数据设置在数据域的包可以通过串行总线从主机侧传输到目标侧。而且,由于这种无数据设置在数据域的包的位数(字节数)少,所以能够提高非显示期间VNDP中的通过串行总线的数据传输效率。因此,如图8所示,即使在非显示期间,采用传输含有同步信号码的包的方式,也可尽量减少使数据传输效率降低的情况。

8.处理的具体描述

通过图9的流程图,详细地描述本实施例的处理过程。首先,系统装置5和主机侧数据传输控制装置10之间接口由图1的CNF端子[2:0]确定(步骤S1)。其次,系统装置5访问主机侧的内部寄存器250,并设置目标侧接口电路110的接口信号的信号类型(步骤S2)。而且,通过串行总线,系统装置5将主机侧的内部寄存器250的信息中的目标侧所需的信息(接口信息和定时信息)传输至目标侧的内部寄存器350(步骤S3)。

接着,系统装置5访问主机侧的内部寄存器250,设置作为数据发送目的地的端口号码(步骤S4)。而且,系统装置5写入数据至主机侧的内部寄存器250(步骤S5)。于是,主机侧的链路控制器90产生含有其数据的包(步骤S6),通过串行总线将包从主机侧发送至目标侧(步骤S7)。

接着,目标侧的链路控制器100分析接收到的包(步骤S8)。目标侧的接口电路110产生按照在目标侧的内部寄存器350上设置的接口信息(定时信息)的接口信号(数据信号、接口控制信号),并输出接口信号到由端口号码选定的端口上(步骤S9)。

如上所述,在本实施例中,用于规定由目标侧接口电路110输出的接口信号的信号类型的接口信息(狭义上是指用于特定接口信号的信号电平变化的定时的定时信息),由系统装置5设置在主机侧的内部寄存器250上。例如,主机侧的链路控制器90产生含有在主机侧的内部寄存器250上设置的接口信息(定时信息)的包,并且通过差动信号的串行总线将生成包发送至目标侧数据传输控制装置30。具体地说,当系统装置5命令内部寄存器250所包含的寄存传输开始寄存器开始传输时,链路控制器90产生含有接口信息(定时信息)的包并且发送(命令传输)生成的包。然后,含有接口信息(定时信息)的包发送后,主机侧链路控制器90产生数据设置在数据域的包,并且将生成的包发送至目标侧传输控制装置30。这样,能有效地产生利用接口信息(定时信息)的接口信号。

9.根据差动信号的串行传输方法

下面参考图10,描述本实施例的串行传输方法以及收发器20和40。

在图10中,DTO+和DTO-表示从主机侧(数据传输控制装置10)输出到目标侧(数据传输控制装置30)的数据(OUT数据)。CLK+和CLK-表示主机侧提供给目标侧的时钟信号。主机侧与时钟信号CLK+/-的边缘(例如,上升沿。也可以是下降沿)同步输出数据DTO+/-。因此,目标侧可利用时钟信号CLK+/-采集和摄取数据DTO+/-。而且,在图10中,目标侧根据主机侧提供的时钟信号CLK+/-进行操作。也就是说,时钟信号CLK+/-成为目标侧的系统时钟信号。因此,PLL(Phase Locked Loop)12(广义上是指时钟信号生成电路)设置在主机侧,而不设置目标侧。

DTI+和DTI-表示从目标侧输出到主机侧的数据(IN数据)。STB+和STB-表示从目标侧提供到主机侧的选通脉冲(广义上是指时钟信号)。目标侧根据主机侧提供的时钟信号CLK+/-产生STB+/-,并且输出产生的STB+/-。而且,目标侧与STB+/-的边缘(例如是上升沿。也可以是下降沿)同步输出数据DTI+/-。因此,利用STB+/-,主机侧可采集和摄取数据DTI+/-。

将DTO+/-、CLK+/-、DTI+/-和STB+/-中的每一个通过发送电路(驱动电路)电流驱动与这些中的每一个相对应的差动信号线(Differential Signal Line)来发送。而且,为了实现高速传输,可以设置两对或者更多对的DTO+/-和DTI+/-各差动信号线。

主机侧收发器20包括:OUT传输(广义上是指数据传输)、时钟传输发送电路22和24、IN传输(广义上是指数据传输)、以及选通脉冲传输(广义是指时钟信号传输)的接收电路26和28。目标侧收发器40包括:OUT传输和时钟传输接收电路42和44、以及IN传输和选通脉冲传输发送电路46和48。而且,其结构也可以不包括这些电路模块。

OUT传输和时钟传输的发送电路22和24,通过电流驱动DTO+/-和CLK+/-的差动信号线分别发送DTO+/-和CLK+/-。OUT传输和时钟传输的接收电路42和44,提供根据流经DTO+/-和CLK+/-差动信号线的电流进行电流·电压的变换,并将上述不同的电流·电压变换得到的差动电压信号(第一和第二电压信号)进行比较处理(差动放大处理),从而接收数据DTO+/-和时钟信号CLK+/-。

通过电流驱动DTI+/-和STB+/-的差动信号线,IN传输和时钟传输的发送电路46和48分别发送DTI+/-和STB+/-。IN传输和选通脉冲传输的接收电路26和28,通过根据DTI+/-和STB+/-的差动信号线上流动的电流情况进行电流/电压的变换,并将上述不同的电流·电压变换得到的差动电压信号(第一和第二电压信号)进行比较处理(差动放大处理),从而接收DTI+/-和STB+/-。

除图10所示的电路模块以外,发送器20和40可包括:并行/串行变换电路、串行/并行变换电路、代码(例如8位/10位代码)的编码电路、代码的解码电路、代码的加法电路和错误信号产生电路,分频电路等。而且,也可以使这些电路的一部分包含在链路控制器90和100中。

10.链路控制器和接口电路的构成例

图11和12表示主机侧链路控制器90、接口电路92、目标侧链路控制器100、接口电路110的构成例。而且,本实施例中的链路控制器和接口电路不限于图11和12所示配置。图11和12所示的电路模块的某些组成部分可省略,或者电路模块之间的连接状态可改变,或者可增加不同于图11和12所示电路模块的其他电路模块。

图11表示主机侧链路控制器90和接口电路92的构成例。主机侧链路控制器90包括:事务控制器200、包产生&分析电路202。而且可以省略其中的一部分。

事务控制器200进行数据传输的事务处理层所涉及的处理。具体地说,事务处理控制器200控制诸如请求包、连续包、应答包等的包传输,并控制由多个包结构的事务。

包产生&分析电路202负责由事务处理控制器200指示传输的包的生成,以及分析从目标侧接收到的包。具体地说,该包产生&分析电路202从接口电路92接收包头上的信息和数据信息,并且将包头和数据结合组成包。包产生&分析电路202把从目标侧接收到的包分成包头和数据,并分析接收到的包。

包产生&分析电路202包括:RGB弹性缓冲器204、包缓冲器206和多路复用器208(多路输出选择器)。从接口电路92接收到的RGB接口信号的信息输出到作为FIFO发挥功能的RGB弹性缓冲器204,并通过多路复用器208传输到发送器20。从接口电路92接收到的包信息(包头信息、数据信息)被输入到作为FIFO发挥功能的包缓冲器206,并通过多路复用器208传输到发送器20。从发送起20接收到的包信息通过多路复用器208和包缓冲器206传输到接口电路92。

接口电路92包括:RGB接口电路210、MPU接口电路220、串行接口电路230、多路复用器(多路输出选择器)232,写&读FIFO240、以及传输控制器242和244。这些电路模块中某些可省略。这里,该RGB接口电路210、MPU接口电路220和串行接口电路230是用于分别与系统装置5之间进行RGB、MPU和串行接口处理的电路。

通过端子CNF[2:0]选择RGB接口时,RGB接口电路210即可工作。从系统装置5接收到的RGB接口信号如水平同步信号HSYNC、垂直同步信号VSYNC、时钟信号CLK和RGB数据信号D[17:0]等通过多路复用器232输出到RGB接口电路210。而且,RGB数据被暂时存储在作为FIFO发挥功能的弹性缓冲器212。信号检测器214执行水平同步信号或者垂直同步信号的边缘检测处理或者进行边缘检测信号和RGB数据信号的采集处理。

通过端子CNF[2:0]选择MPU接口时,MPU接口电路220即可工作。而且,从系统装置5的MPU接口信号如读信号RD、写信号WR、地址0信号A0、和数据信号D[17:0]等通过多路复用器232输入到MPU接口电路220。在进行读操作时,来自MPU接口电路220的读数据信号作为数据信号D[17:0]通过多路复用器232输出到系统总线。

通过端子CNF[2:0]选择串行接口时,串行接口电路230即可工作。从系统装置5接收到的串行接口信号如芯片选择信号SCS、读/写信号SR/W、地址0信号SA0、数据信号SIO和时钟信号SCK等输入到串行接口电路230。在进行读操作时,来自串行接口电路230的读数据信号作为SIO输出到系统总线。

通过MPU接口电路220或者串行接口电路230,系统装置5访问内部寄存器250,并且在该内部寄存器250上设置各种信息。通过传输控制器242和244,存储于写&读FIFO 240和内部寄存器250的信息传输到链路控制器90。例如,通过传输控制器244,存储于主机侧内部寄存器250的接口信息(定时信息)传输到链路控制器90,并发送到目标侧。从链路控制器90接收到的信息,通过传输控制器242和244,写入写&读FIFO 240和内部寄存器250。

图12表示目标侧链路控制器100和接口电路110。该链路控制器100的构成例。链路控制器100包括事务处理控制器300和包产生&分析电路302。这些电路的某些可省略。

该事务处理控制器300执行数据传输的事务层所涉及的处理。该包产生&分析电路302执行由该事务处理控制器300指示传输的包的产生处理,以及分析从主机侧接收到的包的处理。具体地说,该包产生&分析电路302从接口电路110接收包头信息和数据信息,并通过将包头和数据结合组成包。另外,将从主机侧接收的包分为包头和数据,并分析接收到的包。

包产生&分析电路302包括:RGB弹性缓冲器304、接收包缓冲器306、发送包缓冲器307和多路复用器308(多路选择输出器)。通过多路复用器308从收发器40接收到的包的信息中的RGB接口信号的信息输入到作为FIFO发挥功能的RGB弹性缓冲器304,并传输到接口电路110(RGB接口电路310)。通过多路复用器308从收发器40接收到的包的信息输入到作为FIFO发挥功能的包缓冲器306,并传输到接口电路110。从接口电路110接收到的包的信息输入到包缓冲器307,并通过多路复用器308传输到收发器40。

接口电路110包括:RGB接口电路310、MPU接口电路320、串行接口电路330、内部寄存器接口电路340、以及多路复用器342和344(多路选择输出器)。这些中的某些可省略。

RGB接口电路310、MPU接口电路320和串行接口电路330是用于分别在连接到接口总线的装置LCD1、LCD2和GD之间进行RGB、MPU和串行接口处理的电路。内部寄存器接口电路340是用于将从主机侧传输来的信息(接口信息和定时信息)写入到内部寄存器350的电路。

从链路控制器100接收到的RGB接口信号上的信息(RGB数据、同步信号码)输入到RGB接口电路310。而且,RGB数据暂时存储于其功能相当于一个先进先出(FIFO)的弹性缓冲器312。RGB接口信号如垂直同步信号、水平同步信号、就绪信号、时钟信号和数据信号由信号发生器314产生,并通过多路复用器342作为信号FPFRAME、FPLINE、FPDRDY、FPSHIFT、和FPDAT[17:0]输出。

从链路控制器100接收到的MPU接口信号的信息(MPU数据)输入到MPU接口电路320。MPU接口信号如写(读)信号、数据信号和地址0信号等由信号发生器322产生,并通过多路复用器342作为信号FPFRAME(FPLINE)、FPDAT[17:0]和FPA0输出。芯片选择信号FPCS等由CS发生器324产生。通过多路复用器342和MPU接口电路320,来自与接口总线相连接的装置的读数据信号被传输到链路控制器100。

从链路控制器100接收到的串行接口信号的信息(串行数据)输入到串行接口总线330。串行接口信号如地址0信号、读/写信号、数据信号和时钟信号等由信号发生器332产生,并通过多路复用器344和342作为信号FPA0、FPR/W、FPSIO和FPSCK输出。I2C接口电路334产生I2C的接口信号,并输出。从主机侧通过的SERIAL总线信号,通过多路复用器344和342作为信号FPA0、FPR/W、FPSIO和FPSCK输出到接口总线。

通过内部寄存器接口电路340,来自链路控制器100的目标侧的寄存器的信息(接口信息和定时信息)传输并写入内部寄存器350。

11.主机侧和目标侧RGB接口电路的构成例

下面,参照图13A,说明图11所示的主机侧的RGB接口电路210(信号检测器214)的配置实例。如图13A所示,RGB接口电路210包括边缘检测器400和410、以及采集电路420。

边缘检测器400检测来自系统装置5的水平同步信号HSYNC的边缘,并输出边缘检测信号HDET。边缘检测器410检测到来自系统装置5的垂直同步信号VSYNC边缘,并输出边缘检测信号VDET。这种情况下,根据内部寄存器250的设置决定检测上升沿还是下降沿。

根据时钟信号CLK,采集电路420执行边缘检测信号HDET和VDET、以及数据信号D[17:0]的采集处理。这里,CLK是从系统装置5传输来的时钟信号,是用于采集RGB数据的各像素数据的像素时钟信号。这样,在本实施例中,由于采集是基于频率不那么高的像素时钟信号CLK进行的,所以主机侧数据传输控制装置10的功耗可降低。

通过执行采集边缘检测信号HDET和VDET处理过程,采集电路420决定设置在包中的水平同步信号码(见图7)。当检测到如垂直同步信号的边缘检测信号VDET时,同步信号码设置为“1”(VS=1,HS=0)。当检测到水平同步信号的边缘检测信号HDET时,同步信号码设置为“2”(VS=0,HS=1)。当检测到垂直同步信号的边缘检测信号VDET以及水平同步信号的边缘检测信号HDET两个时,同步信号码设置为“3”(VS=1,HS=1)。这样同步信号码可设置在传输到目标侧的包的同步信号码域上。

采集电路420包括VDP/VNDP检测计数器422,该VDP/VNDP检测计数器422根据边缘检测信号HDET和VDET执行计数过程。而且,根据该计数器422的计数结果,采集电路420执行显示期间VDP和非显示期间VNDP的判断(辨别)处理。

例如,把显示期间VDP从非显示期间VNDP区别开的信息设置在内部寄存器250。具体地说,显示期间VDP的起始点信息、显示期间VDP的长度信息、水平扫描期间的长度信息等,设置在内部寄存器250。以图2为例,显示期间VDP的起始点信息设置为“3”,显示期间VDP的长度信息设置为“6”,以及水平扫描期间的长度信息设置为“11”。而且,当检测到垂直同步信号VSYNC,并边缘检测信号VDET激活时,计数器422清零,并且记录边缘检测信号HDET的发生次数。当计数器422记录到边缘信号HDET的发生次数为“3”(显示期间VDP的起始点信息)时,采集电路420判断非显示期间VNDP已经变换为显示期间VDP。当边缘检测信号HDET的发生次数为“9”时,即成为“3”(显示期间VDP起始点信息)和“6”(显示期间VDP长度信息)之和时,采集电路420判断显示期间VDP已经变换为非显示期间VNDP。

链路控制器90从采集电路420接收VDP/VNDP的判断信息。当判断该期间是非显示期间VNDP时,如图8所示,链路控制器90产生非显示期间包,并且输出产生的包到目标侧,该非显示期间包中同步信号码设置在同步信息码域中以及无数据设置在数据域中。当判断该期间是显示期间VDP,链路控制器90产生显示期间包,并且输出产生的包到目标侧,该显示期间包中同步信号码设置在同步信息码域中以及数据设置在数据域中。这样可提高主机侧与目标侧之间串行传输的效率。

参照图13B,描述图12所示的目标侧的RGB接口电路310(信号检测器314)的配置实例。如图13B所示,该RGB接口电路310包括定时发生器430和440。定时发生器430包括像素计数器432,定时发生器440包括像素计数器442和水平(行)计数器444。

该定时发生器430从链路控制器110接收RGB数据上的信息,从内部寄存器350接收定时信息(HDPS、HDP等)。根据像素计数器432的计数值,如图3B所示,定时发生器430产生并输出与作为像素时钟信号的FPSHIFT同步的数据信号FPDAT[17:0]。

定时发生器440从链路控制器100接收含有同步信号码的包头信息,从内部寄存器350接收定时信息(VT、VPW、VDPS、VDP、HT和HPW等)。而且,根据像素计数器442的计数值和水平(行)计数器444的计数值,所确定的(时限),定时发生器440产生和输出如图4(A)和图4(B)所示的定时的垂直同步信号FPFRAME以及水平同步信号FPLINE。

如上所述,在本实施例中,由于RGB接口信号的定时按照内部寄存器350的定时信息进行微调,所以可降低功耗,提高数据传输效率。

12.电子设备

图14表示本实施例的电子设备的构成的例子。该电子设备包括本实施例中说明的数据传输控制装置502、512、514、520、530。另外,包括基带设备500(广义上说为通信装置)、应用设备510(广义上说为处理器)、照相机540(广义上说为摄像装置)、或LCD 550(广义上说为显示装置)。换言之,图14的电子设备包括:目标侧数据传输控制装置520、530,通过串行总线连接于目标侧数据传输控制装置520、530的主机侧数据传输控制装置514,通过接口总线连接于目标侧数据传输控制装置520、530的一个或多个装置540、550。另外,也可省略这些中的部分。利用该构成可实现具有照相功能与LCD(Liquid Crystal Display)显示功能的手机等。但是、本实施例的电子设备不局限于手机,也可适用于数码相机、PDA、电子笔记本、电子词典、或携带型信息终端等各种电子设备。

如图14所示,在设于基带设备500上的主机侧数据传输控制装置502与设于应用设备510(图形设备)上的目标侧数据传输控制装置512之间,进行本实施例说明的串行传输。另外,在设于应用设备510上的主机侧数据传输控制装置514与包括有照相机接口电路522的数据传输控制装置520、包括有LCD接口电路532的数据传输控制装置530之间,也进行本实施例中说明的串行传输。

根据图14的构成,与先前电子设备相比可降低EMI噪音。另外,通过实现数据传输控制装置的小型化、省电化,可以降低电子设备的耗电量。另外,当电子设备为手机时,通过手机的连接部分(铰链部分)的信号线可以为串行信号线,由此可使组装更加容易。

另外,本发明不限于上述实施例,还可以进行各种变形。例如,在说明书或附图中的记载中作为广义、同义用语(一个或多个装置、第1~第N接口电路、接口信息等)引用的用语(LCD1、LCD2、GD,RGB、MPU、串行接口电路,定时信息等),在说明书或附图中的其他记载中,也可置换为广义、同义用语。

另外,数据传输控制装置、电子设备的构成及动作也不局限于本实施例说明的构成及限定,还可以进行各种变形。例如,在本实施例中对接口电路包括RGB接口电路、MPU接口电路、串行接口电路的情况进行了说明。但是,接口电路也可不包括RGB接口电路与串行接口电路。另外,目标侧数据传输控制装置的部分或全部可组装到连接于接口总线的装置(LCD1、LCD2等)上。另外,主机侧数据传输控制装置部分或全部也可以组装到系统装置上。

符号说明

5 系统装置 10 主机侧数据传输控制装置

20 收发器 30 目标侧数据传输控制装置

40 收发器 90 链路控制器

92 接口电路 100 链路控制器

110 接口电路 250 内部寄存器

310 RGB接口电路 320 MPU接口电路

330 串行接口电路 350 内部寄存器

Claims (9)

1.一种用于控制数据传输的数据传输控制装置,通过串行总线与主机侧数据传输控制装置连接,通过接口总线与一个或多个装置连接,其特征在于包括:

链路控制器,用于分析通过串行总线从主机侧数据传输控制装置接收到的包;以及

接口电路,用于产生接口信号,并将产生的接口信号输出到接口总线;

从所述主机侧数据传输控制装置通过串行总线传输的包包括同步信号码域,所述同步信号码域用于设置同步信号码;

所述链路控制器对所述同步信号码进行分析,所述同步信号码设定在从主机侧数据传输控制装置传输的包的所述同步信号码域中;

所述接口电路基于所述链路控制器对所述同步信号码的分析结果产生包括在接口信号中的同步信号,且输出到所述一个或多个装置中。

2.根据权利要求1所述的数据传输控制装置,其特征在于:

通过接口总线连接的所述一个或多个装置是显示面板;

所述链路控制器,在所述显示面板的显示期间从主机侧数据传输控制装置接收数据域中设置有数据的显示期间包;在所述显示面板的非显示期间从主机侧数据传输控制装置接收数据域中未设置数据的非显示期间包。

3.根据权利要求1或2所述的数据传输控制装置,其特征在于:

通过接口总线连接的所述一个或多个装置是显示面板;

所述链路控制器,当从主机侧数据传输控制装置接收到数据域中设置有数据的所述显示面板的显示周期包时,向所述接口电路输出含有设置在包中的所述同步信号码的包头和设置在包中的数据;当从主机侧数据传输控制装置接收到数据域中未设置数据的所述显示面板的非显示周期包时,向所述接口电路输出含有设置在包中的所述同步信号码的包头。

4.一种用于控制数据传输的数据传输控制装置,通过系统总线与系统装置连接,通过串行总线与目标侧数据传输控制装置连接,其特征在于包括:

接口电路,用于执行所述用于控制数据传输的数据传输控制装置和系统装置之间的接口处理,所述系统装置是外部装置;以及

链路控制器,用于产生通过串行总线传送给目标侧数据传输控制装置的包;

所述接口电路从所述系统装置接收同步信号,

所述链路控制器,将与从所述系统装置接收的同步信号相应的同步信号码设置在包的同步信号码域,并将设置有所述同步信号码的包发送到目标侧数据传输控制装置。

5.根据权利要求4所述的数据传输控制装置,其特征在于:

所述目标侧数据传输控制装置通过接口总线与显示面板连接;

所述链路控制器,在所述显示面板的显示期间产生在所述同步信号码域设置同步信号码、数据域中设置有数据的显示期间包;在所述显示面板的非显示期间产生在同步信号码域设置同步信号码、数据域中未设置数据的非显示期间包。

6.根据权利要求4或5所述的数据传输控制装置,其特征在于,

所述接口电路包括:

第一边缘检测器,用于检测来自所述系统装置的垂直同步信号的边缘,并输出第一边缘检测信号;

第二边缘检测器,用于检测来自所述系统装置的水平同步信号的边缘,并输出第二边缘检测信号;以及

采集电路,基于给定的时钟信号对所述第一边缘检测信号和第二边缘检测信号进行采集处理,确定设置在包中的所述同步信号码。

7.根据权利要求6所述的数据传输控制装置,其特征在于,所述采集电路包括计数器,所述计数器基于所述第一边缘检测信号和第二边缘检测信号进行计数处理,所述采集电路基于所述计数器的计数结果判断显示期间和非显示期间。

8.一种电子设备,其特征在于包括:

目标侧数据传输控制装置;

主机侧数据传输控制装置,通过串行总线与所述目标侧数据传输控制装置连接;以及

一个或者多个装置,通过接口总线与所述目标侧数据传输控制装置连接,

其中,所述目标侧数据传输控制装置包括:

链路控制器,用于分析通过串行总线从所述主机侧数据传输控制装置接收到的包;以及

接口电路,用于产生接口信号,并将产生的接口信号输出到接口总线;

从所述主机侧数据传输控制装置通过串行总线传输的包包括同步信号码域,所述同步信号码域用于设置同步信号码;

所述链路控制器对所述同步信号码进行分析,所述同步信号码设定在从主机侧数据传输控制装置传输的包的所述同步信号码域中;

所述接口电路基于所述链路控制器对所述同步信号码的分析结果产生同步信号且输出到所述一个或多个装置中,所述同步信号被包括在接口信号中。

9.一种电子设备,其特征在于包括:

主机侧数据传输控制装置,通过系统总线与系统装置连接,通过串行总线与目标侧数据传输控制装置连接;

目标侧数据传输装置,通过串行总线与所述主机侧数据传输控制装置连接;以及

一个或者多个装置,通过接口总线与所述目标侧数据传输控制装置连接,

其中,所述主机侧数据传输控制装置包括:

接口电路,用于进行所述主机侧数据传输控制装置和系统装置的接口处理,所述系统装置是所述主机侧数据传输控制装置的外部装置;

链路控制器,用于产生通过串行总线发送到所述目标侧数据传输控制装置的包;

所述接口电路从所述系统装置接收同步信号,

所述链路控制器,将与从所述系统装置接收的同步信号相应的同步信号码设置在包的同步信号码域,并将设置有所述同步信号码的包发送到目标侧数据传输控制装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004066064A JP3786121B2 (ja) | 2004-03-09 | 2004-03-09 | データ転送制御装置及び電子機器 |

| JP2004066064 | 2004-03-09 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1667964A CN1667964A (zh) | 2005-09-14 |

| CN100380819C true CN100380819C (zh) | 2008-04-09 |

Family

ID=34918299

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2005100535341A Expired - Fee Related CN100380819C (zh) | 2004-03-09 | 2005-03-08 | 数据传输控制装置及电子设备 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US7908419B2 (zh) |

| JP (1) | JP3786121B2 (zh) |

| CN (1) | CN100380819C (zh) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3835459B2 (ja) * | 2004-03-09 | 2006-10-18 | セイコーエプソン株式会社 | データ転送制御装置及び電子機器 |

| JP2006119619A (ja) * | 2004-09-22 | 2006-05-11 | Pioneer Electronic Corp | 表示装置の駆動回路、表示装置及び表示装置の駆動制御方法 |

| JP4661810B2 (ja) * | 2007-03-16 | 2011-03-30 | セイコーエプソン株式会社 | データ転送制御装置及び電子機器 |

| US7856520B2 (en) * | 2008-01-04 | 2010-12-21 | Silicon Image, Inc. | Control bus for connection of electronic devices |

| WO2012016867A1 (de) * | 2010-08-03 | 2012-02-09 | Continental Teves Ag & Co. Ohg | Kommunikationsverfahren mit echo |

| CN103530215B (zh) * | 2013-09-30 | 2015-12-02 | 杭州华为数字技术有限公司 | 一种内部集成电路主机的自检方法、装置及主机 |

| JP6488844B2 (ja) * | 2015-04-14 | 2019-03-27 | 富士ゼロックス株式会社 | 制御装置及び画像形成装置 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1258153A (zh) * | 1998-12-23 | 2000-06-28 | 朗迅科技公司 | 经过高压接口的同步数据传送协议 |

| CN1067477C (zh) * | 1996-04-16 | 2001-06-20 | 联华电子股份有限公司 | 以串行编码方式进行芯片组间信号传输的装置 |

| CN1363892A (zh) * | 2001-01-02 | 2002-08-14 | 阿尔卡塔尔公司 | 串联连接中的数据同步方法 |

| US20030006981A1 (en) * | 2001-07-03 | 2003-01-09 | Pioneer Corporation And Shizuoka Pioneer Corporation | Display position control apparatus |

| US6609167B1 (en) * | 1999-03-17 | 2003-08-19 | Adaptec, Inc. | Host and device serial communication protocols and communication packet formats |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1047428C (zh) | 1991-06-03 | 1999-12-15 | 北京矿冶研究总院 | 一种适用于倾斜缓倾斜中厚矿体的采矿及回填方法 |

| JPH1153832A (ja) | 1997-08-01 | 1999-02-26 | Canon Inc | 伝送装置、受信装置及びデータ処理装置 |

| JP2000059420A (ja) | 1998-04-24 | 2000-02-25 | Sony Corp | 情報処理装置 |

| JP4058888B2 (ja) | 1999-11-29 | 2008-03-12 | セイコーエプソン株式会社 | Ram内蔵ドライバ並びにそれを用いた表示ユニットおよび電子機器 |

| JP4639420B2 (ja) | 2000-03-08 | 2011-02-23 | ソニー株式会社 | 信号伝送装置および信号伝送方法 |

| US6903780B2 (en) * | 2001-06-08 | 2005-06-07 | Texas Instruments Incorporated | Method of expanding high-speed serial video data providing compatibility with a class of DVI receivers |

| JP4351828B2 (ja) | 2002-03-29 | 2009-10-28 | アイコム株式会社 | 音声通信システム、音声通信方法、送信システム及び受信システム |

| KR100479391B1 (ko) * | 2002-09-16 | 2005-03-28 | 엘지전자 주식회사 | 직렬 데이터의 포맷구조 및 그 직렬 데이터 변환장치 |

| JP4030055B2 (ja) * | 2002-11-26 | 2008-01-09 | インターナショナル・ビジネス・マシーンズ・コーポレーション | フォーマット変換回路 |

| US20050226338A1 (en) * | 2004-04-05 | 2005-10-13 | Honeywell International, Inc. | Camera theft detection system |

-

2004

- 2004-03-09 JP JP2004066064A patent/JP3786121B2/ja not_active Expired - Lifetime

-

2005

- 2005-02-22 US US11/062,954 patent/US7908419B2/en not_active Expired - Fee Related

- 2005-03-08 CN CNB2005100535341A patent/CN100380819C/zh not_active Expired - Fee Related

-

2007

- 2007-11-02 US US11/982,703 patent/US7620762B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1067477C (zh) * | 1996-04-16 | 2001-06-20 | 联华电子股份有限公司 | 以串行编码方式进行芯片组间信号传输的装置 |

| CN1258153A (zh) * | 1998-12-23 | 2000-06-28 | 朗迅科技公司 | 经过高压接口的同步数据传送协议 |

| US6609167B1 (en) * | 1999-03-17 | 2003-08-19 | Adaptec, Inc. | Host and device serial communication protocols and communication packet formats |

| CN1363892A (zh) * | 2001-01-02 | 2002-08-14 | 阿尔卡塔尔公司 | 串联连接中的数据同步方法 |

| US20030006981A1 (en) * | 2001-07-03 | 2003-01-09 | Pioneer Corporation And Shizuoka Pioneer Corporation | Display position control apparatus |

Also Published As

| Publication number | Publication date |

|---|---|

| US7620762B2 (en) | 2009-11-17 |

| US7908419B2 (en) | 2011-03-15 |

| JP3786121B2 (ja) | 2006-06-14 |

| US20050201538A1 (en) | 2005-09-15 |

| JP2005258579A (ja) | 2005-09-22 |

| US20080263241A1 (en) | 2008-10-23 |

| CN1667964A (zh) | 2005-09-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100373780C (zh) | 数据传输控制装置及电子设备 | |

| CN100363913C (zh) | 数据传输控制装置及电子设备 | |

| CN100442263C (zh) | 数据传输控制装置及电子设备 | |

| CN100380819C (zh) | 数据传输控制装置及电子设备 | |

| CN100386718C (zh) | 数据传输控制装置及电子设备 | |

| CN105051706B (zh) | 用于具有pcie协议栈的低功率phy的操作的设备、方法和系统 | |

| CN100449519C (zh) | 数据传输控制装置及电子设备 | |

| US7630375B2 (en) | Data transfer control device and electronic instrument having reduced power consumption | |

| JP2008310349A (ja) | データ転送制御装置及び電子機器 | |

| CN108614795A (zh) | 一种usb数据传输的数字实现方法 | |

| CN103399839A (zh) | 媒介外围接口、电子装置及通信方法 | |

| CN101719353A (zh) | 一种Display Port液晶显示器EDID烧录方法 | |

| CN101998135A (zh) | 移动电视信号采集及播放系统、控制方法 | |

| US8161216B2 (en) | Interface transmission device and method | |

| CN107608927A (zh) | 一种支持全功能的lpc总线主机端口的设计方法 | |

| CN100462952C (zh) | 接口可配置的通用串行总线控制器 | |

| JP4661810B2 (ja) | データ転送制御装置及び電子機器 | |

| CN205910687U (zh) | 一种适用于mdb/icp总线的简化通信电路 | |

| CN203746068U (zh) | 支持批量读取校验的i2c多路复用器 | |

| Maćkowski | The influence of electromagnetic disturbances on data transmission in USB standard | |

| CN100543826C (zh) | 显示器中的数据处理电路及用于显示器的专用集成电路 | |

| Kikani | Bidirectional control transfer with microcontroller | |

| CN102717612A (zh) | 针刻印机的高速通信接入装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20080409 Termination date: 20210308 |

|

| CF01 | Termination of patent right due to non-payment of annual fee |