WO2019012369A1 - 撮像装置、及び電子機器 - Google Patents

撮像装置、及び電子機器 Download PDFInfo

- Publication number

- WO2019012369A1 WO2019012369A1 PCT/IB2018/054888 IB2018054888W WO2019012369A1 WO 2019012369 A1 WO2019012369 A1 WO 2019012369A1 IB 2018054888 W IB2018054888 W IB 2018054888W WO 2019012369 A1 WO2019012369 A1 WO 2019012369A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- transistor

- signal line

- signal

- electrically connected

- circuit

- Prior art date

Links

- 238000003384 imaging method Methods 0.000 title claims abstract description 157

- 238000006243 chemical reaction Methods 0.000 claims abstract description 58

- 238000013528 artificial neural network Methods 0.000 claims abstract description 40

- 230000006870 function Effects 0.000 claims description 109

- 238000000034 method Methods 0.000 claims description 30

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 claims description 19

- 229910052711 selenium Inorganic materials 0.000 claims description 19

- 239000011669 selenium Substances 0.000 claims description 19

- 238000011176 pooling Methods 0.000 claims description 12

- 230000008569 process Effects 0.000 claims description 12

- 239000003990 capacitor Substances 0.000 claims description 11

- 230000015572 biosynthetic process Effects 0.000 claims description 10

- 229910052782 aluminium Inorganic materials 0.000 claims description 8

- 210000002569 neuron Anatomy 0.000 claims description 8

- 150000001875 compounds Chemical class 0.000 claims description 4

- 229910052738 indium Inorganic materials 0.000 claims description 4

- 229910044991 metal oxide Inorganic materials 0.000 claims description 4

- 150000004706 metal oxides Chemical class 0.000 claims description 4

- 229910052733 gallium Inorganic materials 0.000 claims description 3

- 229910052718 tin Inorganic materials 0.000 claims description 3

- 229910052719 titanium Inorganic materials 0.000 claims description 3

- 229910052725 zinc Inorganic materials 0.000 claims description 3

- 229910052684 Cerium Inorganic materials 0.000 claims description 2

- 229910052779 Neodymium Inorganic materials 0.000 claims description 2

- 229910052746 lanthanum Inorganic materials 0.000 claims description 2

- 229910052727 yttrium Inorganic materials 0.000 claims description 2

- 229910052726 zirconium Inorganic materials 0.000 claims description 2

- 239000004065 semiconductor Substances 0.000 description 43

- 238000012545 processing Methods 0.000 description 18

- 239000010408 film Substances 0.000 description 17

- 239000000758 substrate Substances 0.000 description 16

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 14

- 229910052710 silicon Inorganic materials 0.000 description 14

- 239000010703 silicon Substances 0.000 description 14

- 238000010586 diagram Methods 0.000 description 13

- 229910052751 metal Inorganic materials 0.000 description 13

- 239000002184 metal Substances 0.000 description 13

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 12

- 239000000463 material Substances 0.000 description 12

- 239000004973 liquid crystal related substance Substances 0.000 description 10

- 230000008859 change Effects 0.000 description 9

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 8

- 229910052739 hydrogen Inorganic materials 0.000 description 8

- 239000001257 hydrogen Substances 0.000 description 8

- 239000012535 impurity Substances 0.000 description 8

- 230000003287 optical effect Effects 0.000 description 8

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 7

- 230000000694 effects Effects 0.000 description 7

- 238000004364 calculation method Methods 0.000 description 6

- 229910021389 graphene Inorganic materials 0.000 description 6

- 238000004519 manufacturing process Methods 0.000 description 5

- 239000002096 quantum dot Substances 0.000 description 5

- 230000005855 radiation Effects 0.000 description 5

- 239000011787 zinc oxide Substances 0.000 description 5

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 238000013473 artificial intelligence Methods 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- 239000013078 crystal Substances 0.000 description 4

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 4

- 229910001195 gallium oxide Inorganic materials 0.000 description 4

- 229910002804 graphite Inorganic materials 0.000 description 4

- 239000010439 graphite Substances 0.000 description 4

- 239000012212 insulator Substances 0.000 description 4

- 239000010409 thin film Substances 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 239000000853 adhesive Substances 0.000 description 3

- 230000001070 adhesive effect Effects 0.000 description 3

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 3

- 239000006059 cover glass Substances 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 229910000449 hafnium oxide Inorganic materials 0.000 description 3

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 3

- 238000007689 inspection Methods 0.000 description 3

- 230000001151 other effect Effects 0.000 description 3

- 229910052760 oxygen Inorganic materials 0.000 description 3

- 239000001301 oxygen Substances 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 229910052688 Gadolinium Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 238000004458 analytical method Methods 0.000 description 2

- 229910052795 boron group element Inorganic materials 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 230000001419 dependent effect Effects 0.000 description 2

- 239000002274 desiccant Substances 0.000 description 2

- 238000001514 detection method Methods 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 239000012528 membrane Substances 0.000 description 2

- 238000002156 mixing Methods 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 2

- 229910052696 pnictogen Inorganic materials 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 229910001233 yttria-stabilized zirconia Inorganic materials 0.000 description 2

- 239000011701 zinc Substances 0.000 description 2

- 229910016036 BaF 2 Inorganic materials 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 229910004261 CaF 2 Inorganic materials 0.000 description 1

- 229910020156 CeF Inorganic materials 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910052777 Praseodymium Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 229910052771 Terbium Inorganic materials 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 230000003667 anti-reflective effect Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- XQPRBTXUXXVTKB-UHFFFAOYSA-M caesium iodide Inorganic materials [I-].[Cs+] XQPRBTXUXXVTKB-UHFFFAOYSA-M 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 229910052800 carbon group element Inorganic materials 0.000 description 1

- 239000002041 carbon nanotube Substances 0.000 description 1

- 229910021393 carbon nanotube Inorganic materials 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000018044 dehydration Effects 0.000 description 1

- 238000006297 dehydration reaction Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000012530 fluid Substances 0.000 description 1

- -1 for example Substances 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000003331 infrared imaging Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000005305 interferometry Methods 0.000 description 1

- 230000031700 light absorption Effects 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 238000007726 management method Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000005424 photoluminescence Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- FVAUCKIRQBBSSJ-UHFFFAOYSA-M sodium iodide Inorganic materials [Na+].[I-] FVAUCKIRQBBSSJ-UHFFFAOYSA-M 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 238000009736 wetting Methods 0.000 description 1

- 210000000707 wrist Anatomy 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/71—Charge-coupled device [CCD] sensors; Charge-transfer registers specially adapted for CCD sensors

- H04N25/75—Circuitry for providing, modifying or processing image signals from the pixel array

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06G—ANALOGUE COMPUTERS

- G06G7/00—Devices in which the computing operation is performed by varying electric or magnetic quantities

- G06G7/48—Analogue computers for specific processes, systems or devices, e.g. simulators

- G06G7/60—Analogue computers for specific processes, systems or devices, e.g. simulators for living beings, e.g. their nervous systems ; for problems in the medical field

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/04—Architecture, e.g. interconnection topology

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/06—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons

- G06N3/063—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons using electronic means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06N—COMPUTING ARRANGEMENTS BASED ON SPECIFIC COMPUTATIONAL MODELS

- G06N3/00—Computing arrangements based on biological models

- G06N3/02—Neural networks

- G06N3/06—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons

- G06N3/063—Physical realisation, i.e. hardware implementation of neural networks, neurons or parts of neurons using electronic means

- G06N3/065—Analogue means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14609—Pixel-elements with integrated switching, control, storage or amplification elements

- H01L27/14612—Pixel-elements with integrated switching, control, storage or amplification elements involving a transistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14636—Interconnect structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

- H01L27/14645—Colour imagers

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/67—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to fixed-pattern noise, e.g. non-uniformity of response

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

- H04N25/771—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components comprising storage means other than floating diffusion

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/79—Arrangements of circuitry being divided between different or multiple substrates, chips or circuit boards, e.g. stacked image sensors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14621—Colour filter arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1462—Coatings

- H01L27/14623—Optical shielding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14625—Optical elements or arrangements associated with the device

- H01L27/14627—Microlenses

Definitions

- One embodiment of the present invention relates to an imaging device and an electronic device.

- one embodiment of the present invention is not limited to the above technical field.

- the technical field of one embodiment of the invention disclosed in the present specification and the like relates to an object, a method, or a method of manufacturing.

- one embodiment of the present invention relates to a semiconductor device, a display device, a light-emitting device, a power storage device, a memory device, a driving method thereof, or a manufacturing method thereof.

- a semiconductor device refers to an element, a circuit, a device, or the like that can function by utilizing semiconductor characteristics.

- a semiconductor element such as a transistor or a diode is a semiconductor device.

- a circuit including a semiconductor element is a semiconductor device.

- a device including a circuit including a semiconductor element is a semiconductor device.

- IoT Internet of things

- AI Artificial Intelligence

- the amount of data of image data increases with the increase in resolution and gradation of a display device, an efficient management method is required. Further, the increase in the amount of data increases the amount of calculation for processing image data, so the power consumption and the calculation processing time also increase.

- Patent Document 1 discloses a technique for adding an arithmetic function to an imaging device.

- an imaging apparatus provided with a solid-state imaging device such as a CMOS image sensor, high-quality images can be easily taken by technological development. In the next generation, it is required that the imaging apparatus be equipped with more intelligent functions.

- advanced image processing In order to recognize an object from image data, advanced image processing is required.

- advanced image processing various analysis processes for analyzing an image, such as filtering process and comparison operation process, are used.

- analysis processing for image processing the amount of computation increases according to the number of pixels to be processed, and the processing time increases according to the amount of computation. For example, in an in-vehicle image system or the like, there is a problem that an increase in processing time affects safety. In addition, in the image system, there is a problem that the power consumption increases due to the increase in the amount of calculation.

- an object of one embodiment of the present invention is to provide an imaging device with a novel configuration.

- an object of one embodiment of the present invention is to provide an imaging device having a pooling layer of a neural network.

- an object of one embodiment of the present invention is to provide an imaging device with a novel configuration which can reduce the amount of calculation and shorten the processing time.

- an object of one embodiment of the present invention is to provide an imaging device with a novel structure which can reduce power consumption.

- One embodiment of the present invention is an imaging device having a neural network interface, wherein the imaging device includes a pixel area (10), a first circuit (11), a second circuit (12), and a third.

- the pixel region includes a plurality of pixels (P), and the pixel includes a first transistor (25), a circuit (13), a fourth circuit (14), and a first signal line Wx.

- the fourth circuit has a neural network interface.

- the pixel is electrically connected to the third circuit through the first signal line Wx, the third circuit is electrically connected to the fourth circuit, and the first circuit is a scan signal to the pixel

- the second circuit has a function of applying a weight potential to the pixel selected by the scanning signal.

- the pixel has a function of obtaining a first signal by photoelectric conversion from light, and the pixel has a function of multiplying a first signal by a first transistor and a weight potential by a first transistor.

- the transistor of has a function of generating a multiplication term of the first signal, the weight potential, a first offset term (C4), and a second offset term (C6).

- the third circuit has a function of subtracting the first offset term

- the fourth circuit has a function of subtracting the second offset term.

- the fourth circuit has a function of determining a multiplication term, and the fourth circuit is an imaging device characterized by outputting a determination result through a neural network interface.

- the second circuit further has a function of applying an offset potential to the pixel selected by the scanning signal, and the pixel generates the second signal by adding the offset potential to the first signal.

- the pixel has a function of generating a third signal by adding a weight potential to the offset potential, and the pixel has a fourth function of adding an offset potential and a weight potential to the first signal.

- Has a function of generating a signal of The first transistor has a function of multiplying the second signal by an arbitrary magnification to generate a fifth signal, and the first transistor multiplies the third signal by an arbitrary magnification and the sixth signal.

- the first transistor has a function of multiplying the fourth signal by an arbitrary factor to generate a seventh signal.

- the third circuit has a function of storing a second signal, and the third circuit has a function of generating an eighth signal by computing the seventh signal and the fifth signal. ing.

- the fourth circuit has a function of storing an eighth signal, and the fourth circuit has a function of generating a ninth signal by calculating the eighth signal and the sixth signal.

- the multiplication term of the first signal and the weight potential is output to the ninth signal, the fourth circuit has a function of determining the ninth signal, and the fourth circuit is a neural network.

- an imaging device is characterized in that the determination result is output via an interface.

- the imaging device further includes an analog-to-digital converter (15), a signal line Pio, and a wiring VRS, and the pixel analog-digital converts the first data via the signal line Pio. It has a function of outputting to a circuit, and has a function of inputting a first potential applied to the wiring VRS to the pixel through the signal line Pio, and supplies the wiring VRS to the pixel through the signal line Pio.

- the imaging device is characterized in that it functions as a neuron of a neural network when a first potential to be generated is input.

- the imaging device further includes the wiring VPD, the wiring VDM, the signal line G1, the signal line G2, the signal line G3, the signal line Tx, the signal line Res, the signal line S1, and the signal line S2, Are the photoelectric conversion element (50), the first transistor (21), the second transistor (22), the third transistor (23), the fourth transistor (24), the fifth transistor (25), the fifth The sixth transistor (26), the seventh transistor (27), the first capacitive element (C1), the second capacitive element (C2), and the third capacitive element (C3) are included.

- the first circuit (11) is electrically connected to the pixel through the signal line G1, the first circuit is electrically connected to the pixel through the signal line G2, and the first circuit is a signal

- the second circuit (12) is electrically connected to the pixel through the signal line S1, and the second circuit is electrically connected to the pixel through the signal line S2. It is electrically connected.

- One of the electrodes of the photoelectric conversion element is electrically connected to the wiring VPD

- the other of the electrodes of the photoelectric conversion element is electrically connected to one of the source or the drain of the first transistor

- the gate of the first transistor Is electrically connected to the signal line Tx

- the other of the source or the drain of the first transistor is one of the source or the drain of the second transistor, the gate of the third transistor, and the first capacitive element.

- the other of the source or the drain of the second transistor is electrically connected to the wiring VRS

- the gate of the second transistor is electrically connected to the signal line Res.

- One of the source and the drain of the third transistor is electrically connected to the wiring VDM, and the other of the source and the drain of the third transistor is a fourth transistor.

- One of the source or the drain and one of the electrodes of the second capacitor element are electrically connected, and the other of the source or the drain of the fourth transistor is electrically connected to the wiring Pio, and the gate of the fourth transistor Is electrically connected to the signal line G3, and the other electrode of the second capacitive element is the gate of the fifth transistor, one of the source or drain of the sixth transistor, and the electrode of the third capacitive element

- One of the source or the drain of the fifth transistor is electrically connected to the first signal line Wx, and the other one of the source or the drain of the sixth transistor is the signal line S1.

- the gate of the sixth transistor is electrically connected to the signal line G1, and the other electrode of the third capacitive element is connected to one of the source and the drain of the seventh transistor.

- the other of the source and the drain of the seventh transistor is electrically connected to the signal line S2, and the gate of the seventh transistor is formed by being electrically connected to the signal line G2.

- the imaging device further includes the signal line Csw, the signal line Cswb, the signal line Eabs, the signal line Osp, the signal line Ewx, the signal line Mac, and the wiring VIV

- the third circuit is a current mirror

- a current mirror circuit includes an eighth transistor (31), a ninth transistor (32), a tenth transistor (33), and an eleventh transistor (34).

- a twelfth transistor (35) and the memory circuit includes a thirteenth transistor (36), a fourteenth transistor (37), a fifteenth transistor (38), and a fourth capacitive element (C4).

- the output circuit includes a sixteenth transistor (39) and a resistor element R1.

- the wiring VDM is electrically connected to one of the source or drain of the eighth transistor (31) and one of the source or drain of the ninth transistor (32), and the gate of the eighth transistor (31) is The eighth transistor is electrically connected to the gate of the ninth transistor (32), one of the source or drain of the tenth transistor (33), and one of the source or drain of the eleventh transistor (34).

- the other of the source or the drain of (31) is electrically connected to the other of the source or the drain of the tenth transistor (33) and one of the source or the drain of the twelfth transistor (35).

- the gate of (33) is electrically connected to the signal line Cswb, and the gate of the eleventh transistor (34) is connected to the signal line Csw.

- the gate of the twelfth transistor (35) is electrically connected to the signal line Eabs, and the other of the source or the drain of the twelfth transistor (35) is connected to the first signal line Wx,

- the other of the source or drain of the ninth (32) transistor is electrically connected to one of the source or drain of the sixteenth transistor (36), and the other of the source or drain of the eleventh transistor (34);

- the gate of the fourteenth transistor (37) is electrically connected to one of the source or drain of the thirteenth transistor (36) and one of the fourteenth transistor (37), and the signal line Osp.

- the other of the source or drain of the fourteenth transistor (37) is one of the source or drain of the fifteenth transistor (38) and the fourth capacitor

- the gate of the fifteenth transistor (38) is electrically connected to one of the electrodes of the element (C4) and the gate of the thirteenth transistor (36), and is electrically connected to the signal line Res.

- the other of the source and the drain of the transistor (39) is electrically connected to one of the electrodes of the resistance element R1 and the signal line Mac, and the gate of the sixteenth transistor (39) is electrically connected to the signal line Ewx

- the other of the electrodes of the resistance element R1 is electrically connected to the wiring VIV.

- the imaging device further includes the signal line Sh, the signal line CL, the signal line Out, the wiring VCDS, and the wiring JD

- the fourth circuit includes the CDS circuit and the determination circuit.

- the CDS circuit includes a fifth capacitance element (C5), a sixth capacitance element (C6), an operational amplifier OP1, and a seventeenth transistor (41), and the determination circuit includes a seventh capacitance element (C7). , An operational amplifier OP2, and an eighteenth transistor (41).

- the signal line Mac is electrically connected to one of the electrodes of the fifth capacitive element (C5), and the first input terminal of the operational amplifier OP1 is the other of the electrodes of the fifth capacitive element (C5), and the sixth

- the gate of the seventeenth (41) transistor is electrically connected to the signal line CL.

- the gate of the seventeenth (41) transistor is electrically connected to one of the electrodes of the capacitor element (C6) and one of the source or drain of the seventeenth transistor (41).

- the second input terminal of the operational amplifier OP1 is electrically connected to the wiring VCDS, and the output terminal of the operational amplifier OP1 is the other of the electrodes of the sixth capacitive element (C6) and the seventeenth transistor (41)

- the gate of the eighteenth transistor is electrically connected to the signal line Sh, and the eighteenth transistor is electrically connected to the other of the source or the drain of the transistor and the one of the source or the drain of the eighteenth transistor (42).

- the other of the source and the drain of the inverter is electrically connected to the first input terminal of the operational amplifier OP2 and one of the electrodes of the seventh capacitive element (C7), and the second input terminal of the operational amplifier OP2 is connected to the wiring JD It is preferable that the imaging device is electrically connected to the output terminal of the operational amplifier OP2 and the signal line Out, and the signal line Out is connected to the neural network.

- the imaging device further includes a second signal line Wx, a signal line Bsel1, and a switch Bsw.

- the switch Bsw has a function of electrically connecting the first signal line Wx and the second signal line Wx by a signal applied to the wiring Bsel

- the third circuit includes the first signal line Wx.

- a plurality of fifth signals, a plurality of sixth signals, and a plurality of seventh signals are provided from the plurality of connected pixels and the plurality of pixels connected to the second signal line Wx.

- the third circuit has a function of adding the fifth signal, the sixth signal, and the seventh signal supplied from the respective pixels and then subtracting the first offset term.

- the imaging apparatus preferably has a function of selecting a selection range of a plurality of pixels according to a signal supplied to the switch Bsw, and the imaging apparatus is preferably an imaging apparatus characterized in that pooling processing according to the selection range of the pixels is performed.

- the photoelectric conversion element is preferably an imaging device including selenium or a compound containing selenium.

- an imaging device is preferable in which the thirteenth transistor (36) has the same size as the channel length and the channel width of the fifth transistor (25).

- the imaging device is characterized in that the second voltage applied to the wiring VIV is smaller than the third voltage applied to the wiring VDM.

- an imaging device is preferable in which the metal oxide is In, Zn, and M (M is Al, Ti, Ga, Sn, Y, Zr, La, Ce, Nd, or Hf).

- An electronic device including the imaging device according to any one of the above and a display device is preferable.

- an aspect of the present invention can provide an imaging device with a novel configuration.

- one aspect of the present invention can provide an imaging device having a pooling layer of a neural network.

- one embodiment of the present invention can provide an imaging device with a novel configuration which can reduce the amount of calculation and shorten the processing time.

- one embodiment of the present invention can provide an imaging device with a novel configuration which can reduce power consumption.

- the effects of one embodiment of the present invention are not limited to the effects listed above.

- the above listed effects do not disturb the existence of other effects.

- the other effects are the effects not mentioned in this item described in the following description.

- the effects not mentioned in this item can be derived by the person skilled in the art from the description such as the specification or the drawings, and can be appropriately extracted from these descriptions.

- one embodiment of the present invention has at least one of the effects and / or other effects listed above. Therefore, one aspect of the present invention may not have the effects listed above in some cases.

- FIG. 2 is a block diagram illustrating an imaging device.

- FIG. 2 is a circuit diagram illustrating an imaging device.

- FIG. 2 is a circuit diagram illustrating an imaging device.

- 7 is a timing chart illustrating the operation of the imaging device.

- FIG. 3 is a diagram illustrating a configuration of a pixel of an imaging device.

- FIG. 3 is a diagram illustrating a configuration of a pixel of an imaging device.

- FIG. 3 is a diagram illustrating a configuration of a pixel of an imaging device.

- FIG. 3 is a diagram illustrating a configuration of a pixel of an imaging device.

- FIG. 3 is a diagram illustrating a configuration of a pixel of an imaging device.

- FIG. 3 is a diagram illustrating a configuration of a pixel of an imaging device.

- FIG. 3 is a diagram illustrating a configuration of a pixel of an imaging device.

- BRIEF DESCRIPTION OF THE DRAWINGS The package which accommodated the imaging device, and the perspective view of a module.

- FIG. 8 is a block diagram illustrating an electronic device.

- FIG. 2 shows an example of the configuration of an electronic device.

- FIG. 2 shows an example of the configuration of an electronic device.

- Embodiment 1 In this embodiment mode, an imaging device which reduces an offset component generated when performing multiplication by a transistor will be described with reference to FIGS.

- the imaging device 100 is connected to the neural network 17 and the processor 18.

- the imaging device 100 can output data to the neural network 17 via a neural network interface, and can further output imaging data to the processor 18.

- the processor 18 can control the imaging device 100 and a neural network.

- the imaging device 100 includes a pixel area 10, a circuit 11, a circuit 12, circuits 13 (1) to 13 (m / 2), circuits 14 (1) to 14 (m / 2), and an analog digital conversion circuit 15 (1).

- an analog-to-digital converter 15 (m) To the analog-to-digital converter 15 (m), and the switch module 16 (1) to the switch module (m / 2).

- the circuit 13, the circuit 14, the analog-to-digital converter circuit 15, and the switch module 16 will be described.

- m and n are positive integers of 1 or more.

- the imaging device 100 includes the signal line Pio (1) to the signal line Pio (m), the first signal line Wx to the signal line Wx (m / 2), the signal line Out, the signal line IOsel, the wiring VRS, and a plurality of A switch Bsw, a plurality of switches Bsw2 and a plurality of signal lines Bsel1 are provided. Furthermore, although not shown in FIG. 1, the signal lines G1 (1) to G1 (n), the signal lines G2 (1) to G2 (n), the signal lines G3 (1) to G3 ( n) signal lines S1 (1) to S1 (m) and signal lines S2 (1) to S2 (m).

- the pixel area 10 includes pixels P (1, 1) to P (m, n).

- the pixel area 10 can group the pixels P into any selection range.

- the selection range can be determined by the switch Bsw, the switch Bsw2, the signal line Bsel1, and the signal line Bsel2. Therefore, it is preferable to arrange the switch Bsw, the switch Bsw2, the signal line Bsel1, and the signal line Bsel2 according to the selection range.

- the pixel P or the pixel P (i, j) in the i-th column and the j-th row of the pixel area is described.

- i is a positive integer less than or equal to m

- j is a positive integer less than or equal to n.

- the range AG1, the range AG2, or the range AG3 indicates a selectable range having different numbers of pixels.

- the selectable range is not limited to the above, and it is preferable that pixels in different ranges can be selected.

- the selectable range is the selection range of the pooling process in the neural network.

- the neural network can reduce the amount of operation and make it easier to obtain features by the pooling process with different selection ranges. Therefore, the imaging apparatus 100 can reduce the operation amount of the neural network, and reduce the power consumption and the processing time by outputting the imaging data subjected to the pooling process to the neural network.

- the circuit 11 is electrically connected to the pixel extending in the column direction through the signal line G1, and the circuit 11 extends in the column direction through the signal line G2.

- the circuit 11 is electrically connected to the existing pixel, and the circuit 11 is electrically connected to the pixel extending in the column direction through the signal line G3.

- Circuit 12 is electrically connected to the pixels extending in the row direction through signal line S1, and circuit 12 is electrically connected to the pixels extending in the row direction through signal line S2.

- the pixel P (1,1) to the pixel P (2, n) are electrically connected to the circuit 13 (1) through the first signal line Wx, and the circuit 13 (1) is , And the circuit 14 (1).

- the output of the circuit 14 (1) is electrically connected to the neural network via the signal line Out.

- the circuit 11 has a function of providing a scan signal to the pixel P (i, j) through the signal line G1 (j) to the signal line G3 (j), and the circuit 12 selects the pixel P selected by the scan signal

- the offset potential W and the weight potential w (i, j) can be given to i, j).

- the pixel P (i, j) can obtain the first signal by photoelectric conversion from light. Furthermore, the pixel P (i, j) can generate a second signal by adding an offset potential to the first signal. In addition, the pixel P (i, j) can generate a third signal by adding a weight potential to the offset potential. In addition, the pixel P (i, j) can generate a fourth signal by adding the offset potential and the weight potential to the first signal.

- the pixel P (i, j) can multiply the second signal by an arbitrary magnification to generate a fifth signal. Also, the pixel P (i, j) can generate the sixth signal by multiplying the third signal by an arbitrary magnification. In addition, the pixel P (i, j) can generate the seventh signal by multiplying the fourth signal by an arbitrary magnification.

- the circuit 13 can store the second signal. Furthermore, the circuit 13 can generate an eighth signal by calculating the seventh signal and the fifth signal.

- the circuit 14 can store an eighth signal. Furthermore, the circuit 14 can generate a ninth signal by calculating the eighth signal and the sixth signal. The multiplication term of the first signal and the weight potential is output as the ninth signal. Therefore, the circuit 14 can output the determination result of the ninth signal to the neural network. That is, the circuit 14 has the function of a neural network interface.

- the pixel P (1, 1) is electrically connected to the switch module 16 (1) via the signal line Pio (1).

- the switch module (1) can connect the signal line Pio (1) to either the analog-to-digital converter 15 (1) or the wiring VRS by a signal supplied to the signal line IOsel.

- the pixel P (1, 1) functions as an imaging device by providing the first data to the analog-to-digital converter 15 (1) through the signal line Pio.

- the pixel P (1, 1) functions as a neuron of a neural network.

- the imaging device 100 further includes a signal line Tx, a signal line Res, a signal line Csw, a signal line Cswb, a signal line Eabs, a signal line Osp, a signal line Ewx, a signal line Mac, a signal line Sh, a signal line CL, and a signal line Out. And a wiring VPD, a wiring VDM, a wiring VRS, a wiring VIV, a wiring VCDS, a wiring JD, and a wiring GND.

- the pixel P (i, j) includes a photoelectric conversion element 50, a transistor 21, a transistor 22, a transistor 23, a transistor 24, a transistor 25, a transistor 26, a transistor 27, a capacitive element C1, a capacitive element C2, a capacitive element C3, a node FN1, It has nodes FN2 and FN3.

- One of the electrodes of the photoelectric conversion element 50 is electrically connected to the wiring VPD, the other of the electrodes of the photoelectric conversion element 50 is electrically connected to one of the source or drain of the transistor 21, and the gate of the transistor 21 is a signal It is electrically connected to the line Tx.

- the other of the source and the drain of the transistor 21 is electrically connected to one of the source or the drain of the transistor 22, the gate of the transistor 23, and one of the electrodes of the capacitor C1, and the other of the source or the drain of the transistor 22 is

- the gate of the transistor 22 is electrically connected to the wiring VRS, and the gate of the transistor 22 is electrically connected to the signal line Res.

- One of the source or drain of the transistor 23 is electrically connected to the wiring VDM, and the other of the source or drain of the transistor 23 is electrically connected to one of the source or drain of the transistor 24 and one of the electrodes of the capacitive element C2. It is connected.

- the other of the source and the drain of the transistor 24 is electrically connected to the wiring Pio (i), and the gate of the transistor 24 is electrically connected to the signal line G3.

- the other electrode of the capacitive element C2 is electrically connected to the gate of the transistor 25, one of the source or drain of the transistor 26, and one of the electrodes of the capacitive element C3.

- One of the source and the drain of the transistor 25 is electrically connected to the signal line Wx.

- the other of the source and the drain of the transistor 25 is electrically connected to the wiring GND.

- the other of the source and the drain of the transistor 26 is electrically connected to the signal line S1 (i), and the gate of the transistor 26 is electrically connected to the signal line G1 (j).

- the other electrode of capacitive element C3 is electrically connected to one of the source or drain of transistor 27, and the other one of the source or drain of transistor 27 is electrically connected to signal line S2 (i).

- the gate is electrically connected to the signal line G2 (j).

- the node FN1 is formed by connecting the other of the source and the drain of the transistor 21, one of the source and the drain of the transistor 22, the gate of the transistor 23, and one of the electrodes of the capacitive element C1.

- the node FN2 is formed by connecting the other of the source and the drain of the transistor 23, one of the source and the drain of the transistor 24, and one of the electrodes of the capacitor C2.

- the node FN3 is formed by connecting the other electrode of the capacitive element C2, the gate of the transistor 25, one of the source and the drain of the transistor 26, and one of the electrodes of the capacitive element C3.

- the circuit 13 includes a current mirror circuit, a memory circuit, and an output circuit.

- the current mirror circuit includes a transistor 31, a transistor 32, a transistor 33, a transistor 34, and a transistor 35.

- the memory circuit includes a transistor 36, a transistor 37, a transistor 38, and a capacitor C4.

- the output circuit includes a transistor 39 and a resistance element R1.

- the wiring VDM is electrically connected to one of the source or drain of the transistor 31 and one of the source or drain of the transistor 32.

- the gate of the transistor 31 is the gate of the transistor 32 and one of the source or drain of the transistor 33.

- the source or drain of the transistor 34 is electrically connected.

- the other of the source or the drain of the transistor 31 is electrically connected to the other of the source or the drain of the transistor 33 and one of the source or the drain of the transistor 35.

- the gate of the transistor 33 is electrically connected to the signal line Cswb

- the gate of the transistor 34 is electrically connected to the signal line Csw

- the gate of the transistor 35 is electrically connected to the signal line Eabs.

- the other of the source and the drain of the transistor 35 is electrically connected to the signal line Wx and one of the source or the drain of the transistor 39.

- the other of the source or the drain of the transistor 32 is electrically connected to the other of the source or the drain of the transistor 34, one of the source or the drain of the transistor 36, and one of the transistors 37.

- the other of the source and the drain of the transistor 36 is electrically connected to the wiring GND.

- the gate of transistor 37 is electrically connected to signal line Osp, and the other of the source or drain of transistor 37 is one of the source or drain of transistor 38, one of the electrodes of capacitive element C4, and the gate of transistor 36.

- the gate of the transistor 38 is electrically connected to the signal line Res.

- the other of the source and the drain of the transistor 38 is electrically connected to the other of the electrodes of the capacitor C4 and the wiring GND.

- the other of the source and the drain of the transistor 39 is electrically connected to one of the electrodes of the resistive element R1 and the signal line Mac, the gate of the transistor 39 is electrically connected to the signal line Ewx, and the electrode of the resistive element R1 The other is electrically connected to the wiring VIV.

- the circuit 14 includes a CDS circuit and a determination circuit.

- the CDS circuit includes a capacitive element C5, a capacitive element C6, an operational amplifier OP1, and a transistor 41.

- the determination circuit includes a capacitive element C6, an operational amplifier OP2, and a transistor.

- the signal line Mac is electrically connected to one of the electrodes of the capacitive element C5.

- the first input terminal of the operational amplifier OP1 is electrically connected to the other of the electrodes of the capacitive element C5, one of the electrodes of the capacitive element C6, and one of the source or drain of the transistor 41.

- the gate of the transistor 41 is electrically connected to the signal line CL.

- the second input terminal of the operational amplifier OP1 is electrically connected to the wiring VCDS, and the output terminal of the operational amplifier OP1 is the other of the electrode of the capacitive element C6, the other of the source or drain of the transistor 41, and the source of the transistor 42 or the source It is electrically connected to one of the drains.

- the gate of the transistor 42 is electrically connected to the signal line Sh.

- the other of the source and the drain of the transistor 42 is electrically connected to the first input terminal of the operational amplifier OP2 and one of the electrodes of the capacitive element C7, and the second input terminal of the operational amplifier OP2 is electrically connected to the wiring JD. It is connected.

- the output terminal of the operational amplifier OP1 is electrically connected to the signal line Out, and the signal line Out is connected to the neural network.

- the pixel P (i, j) preferably has two functions.

- the first function has a function as an imaging device.

- the second function functions as a neuron and has a function of multiplying imaging data by a weighting factor.

- the weighting factor is preferably given by voltage as a weighting potential.

- the imaging data vi (i, j) is output to the signal line Pio (i) through the transistor 24.

- the imaging data vi (i, j) is supplied to the analog-to-digital converter 15 (i) via the switch module 16 (i / 2), and the analog-to-digital converter (i) i, j) can be output to processor 18;

- a potential as a power supply of the photoelectric conversion element 50 is applied to the wiring VPD, and a reset potential for resetting the node FN1 is applied to the wiring VRS through the transistor 22.

- the transistor 21 is turned on by a signal supplied to the signal line Tx, and the photoelectric conversion element 50 can supply a photocurrent generated by photoelectric conversion to the capacitive element C1.

- the photocurrent applied to the capacitive element C1 is voltage-converted by the capacitive element C1 to update the node FN1.

- a voltage lower than the potential of the node FN1 by the threshold voltage Vth23 of the transistor 23 is applied to the node FN2 as imaging data vi (i, j).

- the imaging data vi (i, j) is output to the signal line Pio (i) through the transistor 24, and is further applied to the analog-to-digital converter 15 (i) through the signal line Pio (i).

- the imaging data vi (i, j) corresponds to a first signal.

- the pixel P (i, j) can have the multiplication function of the product-sum operation function of a neuron.

- the pixel P (i, j) can perform multiplication using a transistor by controlling the node FN3 with the capacitor C2, the capacitor C3, and the transistors 25 to 27. That is, the pixel P (i, j) can obtain a multiplication result as a change in the potential of the node FN3 as a change in the drain current of the transistor 25.

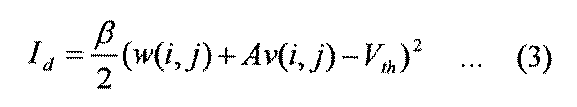

- the drain current Id of the transistor 25 can be expressed by equation (1).

- variable ⁇ can be expressed by equation (2).

- the variable ⁇ is a variable that the transistor 25 has.

- the weighting potential w (i, j) is applied to the node FN3 from the signal line S1 (i) through the transistor 26.

- the reset potential applied to the wiring VRS is supplied to the node FN2 through the transistor 22, and it is preferable that the imaging data vi (i, j) be obtained when the reset potential is supplied to the node FN1.

- imaging data vi (i, j) generated by the photoelectric conversion element 50 is supplied to the node FN2. Accordingly, the potential Vgs of the transistor 25 is such that the imaging data vi (i, j) is added to the weight potential w (i, j) stored in the node FN3 via the capacitive element C2. Therefore, the drain current Id of the transistor 25 is expressed by Equation (3).

- the threshold value Vth of Expression (3) indicates the threshold value of the transistor 25.

- the potential of the node FN3 is converted by a capacitance ratio A of the capacitive element C2, the capacitive element C3, and the gate capacitance of the transistor 25.

- the capacity ratio A will be described as 1.

- Formula (4) can be obtained by expanding and arranging Formula (3.1). Expression (4) can be organized into a multiplication term of imaging data using a transistor 25 and a weight potential, and an offset term A1 (Expression (4.1)) other than the multiplication term.

- the offset term A1 is preferably reduced by the circuit. Therefore, in the equation (5), in order to reduce the offset term A1, the offset term A2 shown in the equation (5.1) depending on the imaging data vi (i, j) from the equation (3.1) It is preferable to subtract the offset term A3 shown in the dependent equation (5.2).

- Formula (5.3) can be obtained by expanding Formula (5).

- Formula (6) can be obtained by arranging each term. Therefore, by subtracting the offset term A2 and the offset term A3 from Expression 3.1, the offset term A1 can be reduced to a size that can be represented only by the threshold value Vth of the transistor 25.

- the weight potential w (i, j) can be reworded as a weighting factor.

- the weighting factors can be set from positive values to negative values. However, even if the weighting factor is a negative value, it is preferable that the weighting potential w (i, j) is a positive potential. Therefore, even if the weighting factor is a negative value, it is preferable to add the offset potential W to the weighting potential w (i, j) so that the weighting potential w (i, j) is a positive potential. Therefore, the equation (5.4) adds the offset potential W to each term of the equation (5).

- Formula (7) can be obtained by expanding and arranging Formula (5.4). Therefore, the offset component of the offset term A1 can be reduced to the offset potential W and the threshold value Vth of the transistor 25.

- the circuits 13 and 14 are used to subtract the offset components. It is preferable to do.

- the circuit 13 subtracts the offset term A2 depending on the imaging data vi (i, j) represented by the equation (5.1), and the circuit 14 reduces the weight potential w (i, j) represented by the equation (5.2).

- An offset term A3 which depends on j) can be subtracted.

- the offset potential W is applied to the node FN3 from the signal line S1 (i) through the transistor 26.

- the offset potential W is applied to the other of the electrodes of the capacitive element C3 from the signal line S2 (i) through the transistor 27. Therefore, the same offset potential W is given to any electrode of the capacitive element C3.

- the reset potential applied to the wiring VRS via the transistor 24 is applied to the node FN2. Further, it is preferable that the node FN1 be supplied with a reset potential through the transistor 22 by a signal supplied to the signal line Res.

- the potential applied to the wiring GND is applied to the capacitive element C4 through the transistor 38 by the signal applied to the signal line Res.

- the reset potential may be the same as the potential applied to the wiring VRS, or may be any of the reference potentials of the imaging device 100. Note that the potential applied to the wiring GND may be the same as the reference potential of the imaging device 100.

- the operational amplifier OP1 forms a voltage follower. Therefore, the potential applied to the wiring VCDS connected to the second input terminal of the operational amplifier OP1 is output to the output terminal of the operational amplifier OP1.

- the node Cdsin connected to the first input terminal of the operational amplifier OP1 is supplied with the potential supplied to the wiring VCDS through the transistor 41. That is, the capacitive element C6 is reset by the potential applied to the wiring VCDS.

- the transistor 42 is turned on by the signal supplied to the signal line Sh, and the first input terminal of the operational amplifier OP2 is supplied with the potential supplied to the wiring VCDS output to the output terminal of the operational amplifier OP1.

- the capacitive element C7 is reset by the potential applied to the wiring VCDS.

- Vgs of the transistor 25 is a voltage obtained by adding the imaging data vi (i, j) output to the node FN2 via the capacitive element C2 to the offset potential W stored in the node FN3. That is, the second signal is generated by adding the offset potential W to the imaging data vi (i, j).

- the result of multiplication of the transistor 25 in accordance with the second signal applied to the gate of the transistor 25 is applied to the signal line Wx as a drain current. At this time, the signal applied to the signal line Wx can be used as a fifth signal.

- the transistors 33, 35, and 37 are turned on by signals supplied to the signal line Eabs, the signal line Cswb, and the signal line Osp.

- the transistors 33 and 35 are turned on, the transistors 31, 32 and 33 form a circuit of a current mirror.

- the fifth signal flowing to the transistor 31 is copied to the transistor 32, and is applied to the capacitive element C4 via the transistor 37.

- the transistor 36 is preferably a transistor having the same channel length and channel width as the transistor 25.

- Node FN 4 can store a second signal of the same size as node FN 3 as transistor 36 flows a current of the same size as the current flowing through transistor 25.

- the transistors 33 and 37 are turned off. Furthermore, the weight potential w (i, j) is given to the other of the electrodes of the capacitive element C3 through the transistor 27.

- the node FN3 generates a fourth signal obtained by adding the weight potential w (i, j) to the second signal.

- the result of multiplication of the transistor 25 in accordance with the signal applied to the gate of the transistor 25 is applied to the signal line Wx as the drain current. At this time, the signal applied to the signal line Wx can be used as a seventh signal.

- the signals supplied to the signal line Eabs, the signal line Csw, and the signal line Ewx turn on the transistors 34, 35, and 39.

- the transistors 34 and 35 With the transistors 34 and 35 turned on, the transistors 31, 32 and 34 form a circuit of a current mirror.

- the fifth signal flowing to the transistor 32 is copied to the transistor 31, and the fifth signal can be subtracted from the seventh signal flowing to the signal line Wx. Therefore, in the signal line Wx, the offset term A2 depending on the imaging data vi (i, j) is subtracted from the seventh signal.

- the resistance element R1 is connected to the signal line Wx via the transistor 39.

- the eighth signal is generated by converting the current obtained by subtracting the fifth signal from the seventh signal into a voltage by the resistor element R1. It is preferable that the potential applied to the wiring VIV be smaller than the power supply voltage of the current mirror circuit applied to the wiring VDM. As an example, when an intermediate potential between the wiring VDM and the reference potential GND of the circuit is applied to the wiring VIV, it is preferable for the weighting factor to calculate either a positive value or a negative value.

- the eighth signal is applied to the signal line Mac.

- the eighth signal applied to the wiring Mac is applied to the node Cdsin through the capacitive element C5 included in the circuit 14. Thereafter, the transistor 41 is turned off by the signal supplied to the signal line CL.

- the node Cdsin can store the eighth signal because it becomes a floating node. Furthermore, the transistor 35 is turned off by the signal applied to the signal line Eabs.

- the reset potential is applied to the node FN2 through the transistor 24.

- a third signal obtained by adding the weight potential w (i, j) to the offset potential W is generated.

- the transistor 25 applies the result multiplied by the signal applied to the gate to the signal line Wx as a drain current.

- the signal line Mac is provided with a sixth signal generated by converting the potential of the signal line Wx into a voltage by the resistor element R1.

- the sixth signal is applied to node Cdsin via capacitive element C5.

- the node Cdsout connected to the output terminal of the operational amplifier OP1 is supplied with a ninth signal generated by subtracting the sixth signal from the eighth signal. Therefore, an offset term A3 dependent on the weight potential w (i, j) is subtracted from the eighth signal from the eighth signal. Therefore, the ninth signal is a multiplication term of the imaging data vi (i, j) and the weight potential w (i, j) as shown by the equation (7), and the offset component is It is possible to reduce the offset term depending on the threshold value Vth.

- the ninth signal is applied via the transistor 42 to the first input terminal of the operational amplifier OP2.

- the timing of applying the ninth signal to the operational amplifier OP2 can be controlled by the signal applied to the signal line Sh.

- the determination voltage is applied to the second input terminal of the operational amplifier OP2 from the wiring JD.

- the determination result is given to the signal line Out from the output terminal of the operational amplifier OP2.

- a transistor with small off current is preferable to use as each of the transistor 21, the transistor 22, the transistor 24, the transistor 26, and the transistor 27. Deterioration of imaging data stored in the nodes FN1 and FN2 can be suppressed by using transistors with small off current as the transistors 21, 22 and 24. In addition, deterioration of the second signal, the third signal, and the fourth signal stored in the node FN3 can be suppressed by using a transistor with small off current as the transistor 26 and the transistor 27. A transistor with a small off current is described in detail in Embodiment 2.

- FIG. 3 shows an example in which a plurality of pixels P (i, j) to pixels P (i + 1, j + 1) are connected to the circuit 13 through the signal line Wx.

- the number of pixels P connected to the signal line Wx is not limited.

- a plurality of pixels P included in a range AG selected by the pooling process can be connected to the circuit 13 as shown in FIG.

- the pixel P has a function of multiplying the imaging data vi (i, j), the weight potential w (i, j), and the offset potential W, and the circuit 13 and the circuit 14 are generated when multiplying by the pixel P And the function of subtracting the offset term.

- the signal line Wx has a function of adding the outputs of the plurality of pixels P by connecting the plurality of pixels P via the signal line Wx. Therefore, the plurality of pixels P, the circuit 13 and the circuit 14 can have the function of the product-sum operation that the neuron of the neural network has. Therefore, the product-sum operation calculated by the plurality of pixels P, the circuit 13 and the circuit 14 can be expressed by equation (8).

- reset potential (* 1) is applied to nodes FN1, FN2, and FN4, respectively.

- the nodes Cdsin and Cdsout are each reset by the potential applied to the wiring VCDS.

- a signal of “H” is given to the signal line G1 (j) and the signal line G2 (j) to set the signal line S1 (i to the other of the electrodes of the node FN3 and the capacitive element C3 connected to the node FN3.

- the signal line S2 (i) can apply an offset potential W.

- the node FN1 can be updated with the imaging data data (i, j) (* 2) output from the photoelectric conversion element 50 through the transistor 21 by applying the signal of “H” to the signal line Tx.

- the imaging data vi (i, j) (* 3) which is lower than the imaging data data (i, j) by the threshold voltage Vth23 of the transistor 23, is supplied to the node FN2.

- the imaging data vi (i, j) means the first data.

- the node FN3 stores a second signal to which the imaging data vi (i, j) and the offset potential are added.

- the current mirror circuit of FIG. 13 is activated by giving the signal of “L” to the signal line Cswb and the signal line Eabs, and further, the signal of “H” is given to the signal line Osp. Can be copied and stored in the node FN4.

- the offset potential W and the weight potential w (i) are applied to the other of the electrodes of the capacitive element C3 connected to the node FN3 via the signal line S2 (i).

- J) can be applied to give a third signal (* 5). Therefore, the fourth signal (* 6) to which the imaging data vi (i, j), the offset potential and the weight potential w (i, j) are added is stored in the node FN3.

- the fifth signal generated by the transistor 36 can be subtracted from the seventh signal generated by the transistor 25 by applying a signal of “L” to the signal line Csw. Furthermore, at T5, an eighth signal is generated by the resistance element R1 by giving a signal of “H” to the signal line Ewx, and an eighth signal (* 7) to be supplied to the node Cdsin of the circuit 14 is provided. it can.

- the current mirror circuit of the circuit 13 is stopped by supplying a signal of "H” to the signal line Csw and the signal line Eabs.

- the eighth signal (* 7) can be stored in the node Cdsin by giving the signal line “L” to the signal line CL.

- a signal of "H” is applied to the signal line G3 (j) to update the node FN2 with the reset potential. Therefore, the node FN3 is updated to the third signal (* 5), and the ninth signal (* 8) is generated at the node Cdsin of the circuit 14.

- the ninth signal (* 8) is determined by the determination voltage applied to the wiring JD by providing the signal line “H” to the signal line Sh, and the operational amplifier OP2 determines the determination result Result (*) to the signal line Out. 9) can be given.

- the timing chart shown in FIG. 4 shows an example in which the pixel P (i, j) in FIG. 2, the circuit 13 and the circuit 14 are used, as shown in FIG. It is good also as composition used.

- the imaging apparatus 100 perform the pooling process by one imaging using the global shutter method.

- the imaging apparatus 100 can reduce power consumption and processing time by providing a neural network interface that outputs data after the pooling process.

- the imaging device 100 can reduce the offset term generated by the multiplication operation of the imaging data vi (i, j) by the pixel P and the weight potential w (i, j).

- FIG. 5 shows an imaging device 100 having pixels different from those in FIG. In FIG. 5, points different from FIG. 2 will be described.