WO2016185636A1 - 電流共振型dc-dcコンバータ - Google Patents

電流共振型dc-dcコンバータ Download PDFInfo

- Publication number

- WO2016185636A1 WO2016185636A1 PCT/JP2015/085541 JP2015085541W WO2016185636A1 WO 2016185636 A1 WO2016185636 A1 WO 2016185636A1 JP 2015085541 W JP2015085541 W JP 2015085541W WO 2016185636 A1 WO2016185636 A1 WO 2016185636A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- transistor

- circuit

- fet

- current

- output

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/22—Conversion of dc power input into dc power output with intermediate conversion into ac

- H02M3/24—Conversion of dc power input into dc power output with intermediate conversion into ac by static converters

- H02M3/28—Conversion of dc power input into dc power output with intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate ac

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/22—Conversion of dc power input into dc power output with intermediate conversion into ac

- H02M3/24—Conversion of dc power input into dc power output with intermediate conversion into ac by static converters

- H02M3/28—Conversion of dc power input into dc power output with intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate ac

- H02M3/325—Conversion of dc power input into dc power output with intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate ac using devices of a triode or a transistor type requiring continuous application of a control signal

- H02M3/335—Conversion of dc power input into dc power output with intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode to produce the intermediate ac using devices of a triode or a transistor type requiring continuous application of a control signal using semiconductor devices only

Definitions

- the embodiment relates to a current resonance type DC-DC converter.

- a current resonance type DC (Direct Current) -DC converter typically supplies a stable output voltage to a load by controlling a driving frequency of a switching circuit.

- a current resonance type DC-DC converter has a problem that the allowable range of the input voltage is narrow. Therefore, practically, for example, a constant voltage DC-DC converter of PWM (Pulse Width Modulation) control has been provided in front of the current resonance type DC-DC converter in order to prevent the input voltage from deviating from the allowable range. .

- PWM Pulse Width Modulation

- the embodiment aims to expand the allowable range of the input voltage of the current resonance type DC-DC converter.

- the embodiment includes a switching circuit, a resonance circuit, and a drive circuit.

- the switching circuit includes a first transistor, a second transistor connected in series to the first transistor, a third transistor, and a fourth transistor connected in series to the third transistor, The second transistor, the second transistor, the third transistor, and the fourth transistor are arranged in parallel.

- the resonant circuit includes a first input terminal commonly connected to the first transistor and the second transistor, and a second input terminal commonly connected to the third transistor and the fourth transistor.

- the drive circuit turns on / off the first transistor at a drive frequency based on the output voltage or output current of the resonance circuit, and turns on the second transistor alternately with the first transistor

- the third transistor is switched to the opposite state of the first transistor at substantially the same timing as the ON / OFF timing of the first transistor, and the fourth transistor is turned ON / OFF alternately with the third transistor.

- the first transistor is turned on / off, the second transistor is turned on / off alternately with the first transistor, and the third transistor is turned on. Timing shifted by the phase shift amount based on the output voltage or output current of the resonance circuit from the ON / OFF timing of the transistor 1 Switching the state of the first transistor and the reverse, turning ON / OFF the fourth transistor alternating with the third transistor.

- FIG. 1 is a circuit diagram illustrating a current resonance type DC-DC converter according to a first embodiment;

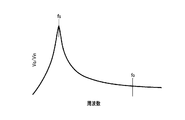

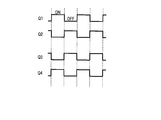

- 3 is a graph illustrating frequency characteristics of a gain of an LCR resonance circuit included in the current resonance type DC-DC converter of FIG. 3 is a timing chart illustrating a control signal supplied to the gate terminal of each FET when the FET drive circuit of FIG. 1 operates in the first control mode.

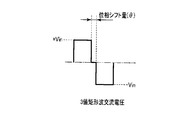

- 3 is a graph illustrating a waveform of a voltage input to the LCR resonance circuit when the FET drive circuit of FIG. 1 operates in the first control mode.

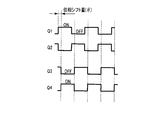

- 6 is a timing chart illustrating a control signal supplied to the gate terminal of each FET when the FET drive circuit of FIG. 1 operates in the second control mode.

- FIG. 2 illustrates a basic circuit of a current resonance type DC-DC converter.

- the basic circuit of FIG. 2 corresponds to a half-bridge type DC-DC converter. Therefore, the basic circuit of FIG. 2 is different from the full-bridge type DC-DC converter shown in FIG. .

- the DC-DC converter shown in FIG. 2 includes a switching circuit and a field effect transistor (FET) driving circuit 200.

- FET field effect transistor

- the switching circuit includes a first input terminal, a second input terminal, an output terminal, a first control terminal, and a second control terminal.

- the first input terminal of the switching circuit is connected to a voltage source (not shown), and an input voltage (V in ) is applied.

- the second input terminal of the switching circuit is grounded (connected to GND).

- the output terminal of the switching circuit is connected to the input terminal of the LCR resonant circuit.

- the first control terminal and the second control terminal of the switching circuit are output to the first output terminal and the second output terminal of the FET drive circuit 200, respectively.

- the switching circuit generates a rectangular wave based on the input voltage (V in ), and supplies this rectangular wave to the input terminal of the LCR resonant circuit.

- the frequency and phase of the rectangular wave are controlled by a first control signal and a second control signal received via the first control terminal and the second control terminal.

- the switching circuit includes an FET Q1 and an FET Q2.

- the gate terminal of FET Q1 is connected to the first control terminal of the switching circuit.

- the drain terminal of the FET Q1 is connected to the first input terminal of the switching circuit.

- the source terminal of the FET Q1 is connected to the drain terminal of the FET Q2 and the output terminal of the switching circuit. That is, FET Q2 is connected in series to FET Q1.

- the gate terminal of FET Q2 is connected to the second control terminal of the switching circuit.

- the drain terminal of the FET Q2 is connected to the source terminal of the FET Q1 and the output terminal of the switching circuit.

- the source terminal of the FET Q2 is connected to the second input terminal of the switching circuit.

- FET Q1 and FET Q2 receive the first control signal and the second control signal from the FET drive circuit 200, and are turned ON / OFF alternately according to the levels of the first control signal and the second control signal.

- both the first control signal and the second control signal correspond to pulse signals having a frequency equal to f and a duty ratio equal to about 50%.

- the FET Q2 is in a state opposite to that of the FET Q1 at substantially the same timing as the ON / OFF timing of the FET Q1, according to the level of the second control signal substantially corresponding to the inverted signal of the first control signal. Switch to

- the FET drive circuit 200 includes a control terminal, a first output terminal, and a second output terminal.

- the control terminal of the FET drive circuit 200 is connected to the first output terminal of the LCR resonance circuit.

- the first output terminal of the FET drive circuit 200 is connected to the first control terminal of the switching circuit.

- the second output terminal of the FET drive circuit 200 is connected to the second control terminal of the switching circuit.

- FET drive circuit 200 detects the output voltage or output current of the LCR resonance circuit via the control terminal.

- the FET drive circuit 200 generates a first control signal and a second control signal for driving the FET Q1 and the FET Q2, respectively, based on the output voltage or output current of the LCR resonance circuit.

- the FET drive circuit 200 outputs the first control signal and the second control signal to the FET Q1 and the FET Q2 via the first output terminal and the second output terminal.

- the FET drive circuit 200 turns on / off the FET Q1 at a drive frequency (f) based on the output voltage or output current of the LCR resonant circuit. Then, the switching circuit applies a rectangular wave AC voltage to the primary inductor of the transformer T1 included in the LCR resonance circuit.

- the rectangular wave AC voltage has a peak voltage equal to ⁇ V in / 2 and a frequency equal to f.

- the fundamental wave component (V 0 ) of this rectangular wave AC voltage can be expressed by the following mathematical formula (1).

- the LCR resonant circuit includes an input terminal, a first output terminal, and a second output terminal.

- the LCR resonant circuit generates an output voltage by stepping up or down a rectangular wave AC voltage supplied from a switching circuit via an input terminal.

- the LCR resonant circuit applies an output voltage to a load connected between the first output terminal and the second output terminal.

- the LCR resonant circuit includes a resonant capacitor C1, a resonant capacitor C2, a transformer T1, a rectifier circuit D, a smoothing capacitor C3, and a load.

- the resonance characteristics of this LCR resonance circuit are determined by the combined capacitance (C1 + C2) of the resonance capacitor C1 and the resonance capacitor C2, the leakage inductance (L s ) and the excitation inductance (L p ) of the transformer T1, and the resistance value (RL) of the load. Determined.

- the rectifier circuit D and the smoothing capacitor C3 are connected to the secondary side of the transformer T1, and generate a DC output voltage by rectifying and smoothing the AC input voltage from the transformer T1.

- the gain (that is, output voltage / input voltage) of the LCR resonant circuit varies depending on the frequency.

- F s shown in FIG. 3 represents the frequency substantially maximize the gain, can be derived by the following equation (2).

- f o represents a frequency at which the gain is substantially equal to 1 (0 dB) on the higher frequency side than f s , and can be derived by the following formula (3).

- the drive frequency (f) is by controlling the range from f s to f o, it is possible to adjust the output voltage or the output current of the LCR resonant circuit. For example, even if the input voltage (V in ) fluctuates to some extent, the FET drive circuit 200 can stabilize the output voltage or output current of the LCR resonance circuit.

- FET driving circuit 200 when the output voltage of the LCR resonant circuit is lower than the target value closer driving frequency (f) to f s (i.e., reduce) by, the output voltage Can be increased.

- FET driving circuit 200 when the output voltage of the LCR resonant circuit is higher than the target value closer driving frequency (f) to f o (i.e., increase) by, be reduced the output voltage it can.

- the frequency characteristic of FIG. 3 since the gain is hardly changed at the high-band than f o, the output voltage as the FET drive circuit 200 is higher than the drive frequency (f) f o is hardly lowered. Therefore, since the current resonance type DC-DC converter of FIG. 2 has difficulty in generating a target output voltage when the input voltage (V in ) increases to some extent, a mechanism (for example, a constant voltage) is stabilized. Voltage DC-DC converter).

- the current resonance type DC-DC converter according to the first embodiment expands the allowable range of the input voltage by using both the first control mode and the second control mode described later (particularly, the allowable upper limit). ).

- a current resonance type DC-DC converter according to this embodiment is illustrated in FIG.

- the current resonance type DC-DC converter of FIG. 1 includes a switching circuit, an FET drive circuit 100, and an LCR resonance circuit.

- the switching circuit includes a first input terminal, a second input terminal, a first output terminal, a second output terminal, a first control terminal, a second control terminal, a third control terminal, and a fourth control terminal. Provide terminals.

- the first input terminal of the switching circuit is connected to a voltage source (not shown), and an input voltage (V in ) is applied.

- the second input terminal of the switching circuit is grounded (connected to GND).

- the first output terminal and the second output terminal of the switching circuit are connected to the second input terminal and the first input terminal of the LCR resonance circuit, respectively.

- the first control terminal, the second control terminal, the third control terminal, and the fourth control terminal of the switching circuit are the first output terminal, the second output terminal, and the third output terminal of the FET drive circuit 100, respectively. And a fourth output terminal.

- the switching circuit generates two rectangular waves based on the input voltage (V in ), and supplies the two rectangular waves to the first input terminal and the second input terminal of the LCR resonance circuit, respectively.

- the frequency and phase of the rectangular wave are the first control signal, the second control signal, the second control signal, the second control signal, the second control signal, the second control signal, the second control signal, the second control signal, 3 and the fourth control signal.

- the switching circuit includes FET Q1, FET Q2, FET Q3, and FET Q4.

- the FET Q1, FET Q2, FET Q3, and FET Q4 may be replaced with other types of transistors.

- the gate terminal of FET Q1 is connected to the first control terminal of the switching circuit.

- the drain terminal of the FET Q1 is connected to the first input terminal of the switching circuit.

- the source terminal of the FET Q1 is connected to the drain terminal of the FET Q2 and the first output terminal of the switching circuit. That is, FET Q2 is connected in series to FET Q1.

- the gate terminal of FET Q2 is connected to the second control terminal of the switching circuit.

- the drain terminal of the FET Q2 is connected to the source terminal of the FET Q1 and the first output terminal of the switching circuit.

- the source terminal of the FET Q2 is connected to the second input terminal of the switching circuit.

- the FET Q1 and the FET Q2 receive the first control signal and the second control from the FET drive circuit 100 regardless of whether the FET drive circuit 100 is operating in the first control mode or the second control mode.

- the signal is received and turned ON / OFF alternately according to the levels of the first control signal and the second control signal.

- both the first control signal and the second control signal correspond to pulse signals having a frequency equal to f and a duty ratio equal to about 50%.

- the FET Q2 is in a state opposite to that of the FET Q1 at substantially the same timing as the ON / OFF timing of the FET Q1, according to the level of the second control signal substantially corresponding to the inverted signal of the first control signal. Switch to

- the gate terminal of FET Q3 is connected to the third control terminal of the switching circuit.

- the drain terminal of the FET Q3 is connected to the first input terminal of the switching circuit. That is, in the example of FIG. 1, the FET Q3 is connected in parallel to the FET Q1.

- the source terminal of the FET Q3 is connected to the drain terminal of the FET Q4 and the second output terminal of the switching circuit. That is, FET Q4 is connected in series to FET Q3.

- the gate terminal of FET Q4 is connected to the fourth control terminal of the switching circuit.

- the drain terminal of the FET Q4 is connected to the source terminal of the FET Q3 and the second output terminal of the switching circuit.

- the source terminal of the FET Q4 is connected to the second input terminal of the switching circuit. That is, in the example of FIG. 1, the FET Q4 is connected in parallel to the FET Q2.

- FET Q3 and FET Q4 are arranged in parallel with FET Q1 and FET Q2, regardless of whether the FET drive circuit 100 is operating in the first control mode or the second control mode described later.

- the third control signal and the fourth control signal are received from the FET drive circuit 100, and are turned ON / OFF alternately according to the levels of the third control signal and the fourth control signal.

- both the third control signal and the fourth control signal correspond to pulse signals having a frequency equal to f and a duty ratio equal to about 50%.

- the FET Q4 is in a state opposite to that of the FET Q3 at substantially the same timing as the ON / OFF timing of the FET Q3, according to the level of the fourth control signal substantially corresponding to the inverted signal of the third control signal. Switch to

- the LCR resonance circuit includes a first input terminal, a second input terminal, a first output terminal, and a second output terminal.

- the first input terminal and the second input terminal of the LCR resonant circuit are connected to the second output terminal and the first output terminal of the switching circuit, respectively.

- the first output terminal and the second output terminal of the LCR resonant circuit can be connected to the first terminal and the second terminal of the load, respectively.

- the first output terminal or the second output terminal of the LCR resonant circuit is also connected to the control terminal of the FET drive circuit 100 for measuring the output voltage or output current of the LCR resonant circuit.

- the LCR resonance circuit generates an output voltage by stepping up or down a rectangular wave AC voltage supplied from the switching circuit via the first input terminal and the second input terminal.

- the LCR resonant circuit applies an output voltage to a load connected between the first output terminal and the second output terminal.

- the LCR resonant circuit includes a resonant capacitor Cr , a transformer T1, a rectifier circuit D1, a smoothing capacitor Co, and a load.

- the resonance characteristics of this LCR resonance circuit are determined by the capacitance of the resonance capacitor Cr, the leakage inductance (L s ) and excitation inductance of the transformer T1, and the load resistance (RL).

- the gain of the LCR resonant circuit changes depending on the frequency as in the frequency characteristic illustrated in FIG.

- the rectification circuit D1 and the smoothing capacitor C o is connected to the secondary side of the transformer T1, and generates a DC output voltage (V o) by rectifying and smoothing the AC input voltage from the transformer T1.

- the FET drive circuit 100 includes a control terminal, a first output terminal, a second output terminal, a third output terminal, and a fourth output terminal.

- the control terminal of the FET drive circuit 100 is connected to the first output terminal of the LCR resonance circuit.

- the first output terminal of the FET drive circuit 100 is connected to the first control terminal of the switching circuit.

- the second output terminal of the FET drive circuit 100 is connected to the second control terminal of the switching circuit.

- the third output terminal of the FET drive circuit 100 is connected to the third control terminal of the switching circuit.

- the fourth output terminal of the FET drive circuit 100 is connected to the fourth control terminal of the switching circuit.

- the FET drive circuit 100 detects the output voltage or output current of the LCR resonant circuit via the control terminal.

- the FET drive circuit 100 outputs the first control signal, the second control signal, the third control signal, and the fourth control signal for driving the FET Q1, FET Q2, FET Q3, and FET Q4 to LCR resonance. Generated based on the output voltage or output current of the circuit.

- the FET drive circuit 100 includes a first control signal, a second control signal, and a third control signal via the first output terminal, the second output terminal, the third output terminal, and the fourth output terminal.

- the fourth control signal is output to the switching circuit.

- the FET drive circuit 100 can operate in the first control mode or the second control mode.

- the FET drive circuit 100 turns on / off the FET Q1 at a drive frequency (f) based on the output voltage or output current of the LCR resonant circuit, and the FET Q3 is substantially the ON / OFF timing of the FET Q1.

- the state is switched to the opposite state of FET Q1.

- the FET drive circuit 100 generates a first control signal, a second control signal, a third control signal, and a fourth control signal as illustrated in FIG. Then, the switching circuit applies the rectangular wave AC voltage illustrated in FIG. 5 to the LCR resonance circuit.

- This rectangular wave AC voltage has a peak voltage equal to ⁇ V in and a frequency equal to f. Furthermore, the fundamental wave component (V 1 ) of this rectangular wave AC voltage can be expressed by the following mathematical formula (4).

- the FET drive circuit 100 can adjust the output voltage or output current of the LCR resonance circuit by controlling the drive frequency (f).

- the FET drive circuit 100 turns on / off the FET Q1 at the drive frequency (f), and changes the FET Q3 to the output voltage or output current of the LCR resonance circuit from the ON / OFF timing of the FET Q1.

- the state is switched to the reverse state of the FET Q1.

- the FET drive circuit 100 generates a first control signal, a second control signal, a third control signal, and a fourth control signal as illustrated in FIG. Then, the switching circuit applies the ternary rectangular wave AC voltage illustrated in FIG. 7 to the LCR resonance circuit.

- the ternary rectangular wave AC voltage has a peak voltage equal to ⁇ V in , an intermediate voltage equal to 0 [V], and a frequency equal to f. Furthermore, the fundamental wave component (V 2 ) of the ternary rectangular wave AC voltage can be expressed by the following mathematical formula (5).

- FET driving circuit 100 can adjust the input voltage of the LCR resonant circuit by controlling the amount of phase shift (theta). Therefore, the FET drive circuit 100 can adjust the output voltage or output current of the LCR resonance circuit by controlling the phase shift amount ( ⁇ ) without controlling the drive frequency (f). Note that the FET drive circuit 100 may use the control of the phase shift amount ( ⁇ ) and the control of the drive frequency (f) in the second control mode.

- the output voltage of the LCR resonance circuit can be made lower than that in the first control mode.

- the FET drive circuit 100 can limit V 2 to a range of 0 or more and V 1 or less regardless of the magnitude of the input voltage (V in ) of the switching circuit. Therefore, the FET drive circuit 100 can raise the allowable upper limit of the input voltage (V in ) of the switching circuit by using the second control mode as compared with the case of always operating in the first control mode. is there.

- the FET drive circuit 100 may switch between the first control mode and the second control mode as described below.

- the FET drive circuit 100 may provide an upper limit value (hereinafter referred to as a first threshold value) of the drive frequency (f) that can be set in the first control mode. That is, the FET drive circuit 100 switches to the second control mode when the drive frequency (f) based on the output voltage or output current of the LCR resonant circuit becomes equal to or higher than the first threshold during operation in the first control mode. Also good.

- the driving frequency (f) based on the output voltage or output current may be derived through calculation, for example, a table (LUT (Look Up Table) or the like) created in advance based on the frequency characteristics of the gain of the LCR circuit. May be searched.

- the FET drive circuit 100 may provide a lower limit value (hereinafter referred to as a second threshold value) of the phase shift amount ( ⁇ ) that can be set in the second control mode. That is, the FET drive circuit 100 switches to the first control mode when the phase shift amount ( ⁇ ) based on the output voltage or output current of the LCR resonance circuit becomes equal to or less than the second threshold during operation in the second control mode. May be.

- the phase shift amount ( ⁇ ) based on the output voltage or output current may be derived through calculation, or may be searched from a table (LUT or the like) created in advance.

- the first threshold value and the second threshold value may be fixed, or may be dynamically controlled by the FET drive circuit 100 (or a threshold setting circuit not shown).

- the first threshold value may change to a larger value as the input voltage (V in ) of the switching circuit is higher.

- the second threshold value may change dynamically as the input voltage (V in ) increases. According to such dynamic control, it is possible to improve the power conversion efficiency and improve the responsiveness to a sudden change in the input voltage (V in ) of the switching circuit.

- the first threshold value may change to a smaller value as the output current of the LCR resonant circuit increases.

- the second threshold value may change dynamically as the output current increases. Such dynamic control can improve the responsiveness to a sudden change in the output current of the LCR resonant circuit.

- the first threshold value is larger as the loss obtained by subtracting the output power in the current resonance type DC-DC converter from the input power in the current resonance type DC-DC converter in FIG. 1 (in other words, the efficiency is lower). It may change dynamically to a larger value.

- the second threshold value may change dynamically as the loss increases. According to such dynamic control, power conversion efficiency can be improved.

- the current resonance type DC-DC converter according to the first embodiment includes the first control mode for adjusting the output voltage or the output current by controlling the driving frequency of the switching circuit, and the switching.

- the second control mode for adjusting the output voltage or the output current by controlling the phase difference between the two rectangular waves generated by the two transistor pairs included in the circuit is used in combination. Therefore, according to this current resonance type DC-DC converter, even when a high level voltage that is not allowed in the first control mode is input, the target output voltage is obtained using the second control mode. Can be generated. That is, since the current resonance type DC-DC converter has a wide input voltage allowable range, a mechanism for stabilizing the input voltage (for example, a constant voltage DC-DC converter) can be omitted (or simplified). . Therefore, according to the current resonance type DC-DC converter, it is possible to avoid (or suppress) an increase in cost and size and a decrease in power conversion efficiency associated with the mechanism.

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Dc-Dc Converters (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015-101166 | 2015-05-18 | ||

| JP2015101166A JP6141908B2 (ja) | 2015-05-18 | 2015-05-18 | 電流共振型dc−dcコンバータ |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| WO2016185636A1 true WO2016185636A1 (ja) | 2016-11-24 |

Family

ID=57319716

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| PCT/JP2015/085541 WO2016185636A1 (ja) | 2015-05-18 | 2015-12-18 | 電流共振型dc-dcコンバータ |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP6141908B2 (zh) |

| WO (1) | WO2016185636A1 (zh) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7541298B2 (ja) * | 2021-01-13 | 2024-08-28 | 富士電機株式会社 | 電力変換装置、電力変換装置の制御装置、および、電力変換制御方法 |

| CN116802981A (zh) * | 2021-02-08 | 2023-09-22 | 松下控股株式会社 | 电力转换系统和控制方法 |

| WO2023127464A1 (ja) * | 2021-12-27 | 2023-07-06 | パナソニックホールディングス株式会社 | 電力変換システム |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002262569A (ja) * | 1989-07-13 | 2002-09-13 | General Electric Co <Ge> | 共振インバータ |

| JP2014003764A (ja) * | 2012-06-15 | 2014-01-09 | Panasonic Corp | 電力変換装置 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9379617B2 (en) * | 2012-02-03 | 2016-06-28 | Fuji Electric Co., Ltd. | Resonant DC-DC converter control device |

| JP2014039383A (ja) * | 2012-08-14 | 2014-02-27 | Hitachi Automotive Systems Ltd | 電源装置および車載用電源装置 |

-

2015

- 2015-05-18 JP JP2015101166A patent/JP6141908B2/ja active Active

- 2015-12-18 WO PCT/JP2015/085541 patent/WO2016185636A1/ja active Application Filing

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002262569A (ja) * | 1989-07-13 | 2002-09-13 | General Electric Co <Ge> | 共振インバータ |

| JP2014003764A (ja) * | 2012-06-15 | 2014-01-09 | Panasonic Corp | 電力変換装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP6141908B2 (ja) | 2017-06-07 |

| JP2016220347A (ja) | 2016-12-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6970366B2 (en) | Phase-shifted resonant converter having reduced output ripple | |

| US10622907B2 (en) | DC-DC converter | |

| US11018592B2 (en) | Flyback converter controller, flyback converter and methods of operation | |

| JP3257505B2 (ja) | 圧電トランスインバータ | |

| US9787204B2 (en) | Switching power supply device | |

| JP5434371B2 (ja) | 共振型スイッチング電源装置 | |

| AU2016277074B2 (en) | Dual bridge DC/DC power converter | |

| US20150349627A1 (en) | Llc resonant power converter | |

| US10396671B2 (en) | Power supplies having power switches controllable with a varying frequency, duty cycle and/or phase to regulate outputs | |

| CN111726005A (zh) | 相移全桥转换器、操作相移全桥转换器的方法和ac/dc转换器 | |

| JP6141908B2 (ja) | 電流共振型dc−dcコンバータ | |

| JP7325059B2 (ja) | 力率改善回路 | |

| US10075055B2 (en) | Zero-voltage-switching scheme for phase shift converters | |

| US11804781B2 (en) | Electronic circuit and method | |

| TW201824725A (zh) | 諧振控制裝置及其諧振控制方法 | |

| JP6186392B2 (ja) | 電流共振型dc−dcコンバータ | |

| JP4635584B2 (ja) | スイッチング電源装置 | |

| US20140125397A1 (en) | Level converter for controlling switch | |

| WO2023161669A1 (ja) | 電力変換方法及び電力変換装置 | |

| WO2023042392A1 (ja) | スイッチング制御装置、スイッチング電源装置および電力供給システム | |

| WO2023042393A1 (ja) | スイッチング制御装置、スイッチング電源装置および電力供給システム | |

| JP6417543B2 (ja) | スイッチング電源装置 | |

| JP5652921B2 (ja) | Fetスイッチング駆動回路及びその動作方法 | |

| JP2022098323A (ja) | Dc-dcコンバータ | |

| JP2002171755A (ja) | 直流−直流変換装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| 121 | Ep: the epo has been informed by wipo that ep was designated in this application |

Ref document number: 15892634 Country of ref document: EP Kind code of ref document: A1 |

|

| NENP | Non-entry into the national phase |

Ref country code: DE |

|

| 122 | Ep: pct application non-entry in european phase |

Ref document number: 15892634 Country of ref document: EP Kind code of ref document: A1 |