KR910002764B1 - 비결정 반도체의 제법 및 장치 - Google Patents

비결정 반도체의 제법 및 장치 Download PDFInfo

- Publication number

- KR910002764B1 KR910002764B1 KR8201088A KR820001088A KR910002764B1 KR 910002764 B1 KR910002764 B1 KR 910002764B1 KR 8201088 A KR8201088 A KR 8201088A KR 820001088 A KR820001088 A KR 820001088A KR 910002764 B1 KR910002764 B1 KR 910002764B1

- Authority

- KR

- South Korea

- Prior art keywords

- amorphous silicon

- temperature

- gas

- range

- semiconductor

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims description 50

- 238000000034 method Methods 0.000 title claims description 35

- 239000007789 gas Substances 0.000 claims description 33

- 239000000758 substrate Substances 0.000 claims description 23

- 238000000354 decomposition reaction Methods 0.000 claims description 17

- 229920000548 poly(silane) polymer Polymers 0.000 claims description 17

- 239000002019 doping agent Substances 0.000 claims description 14

- 238000000151 deposition Methods 0.000 claims description 11

- 230000008021 deposition Effects 0.000 claims description 10

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical group [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 claims description 8

- 238000004519 manufacturing process Methods 0.000 claims description 8

- 239000011261 inert gas Substances 0.000 claims description 6

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical group [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 claims description 5

- 229910052786 argon Inorganic materials 0.000 claims description 4

- 230000006911 nucleation Effects 0.000 claims description 4

- 238000010899 nucleation Methods 0.000 claims description 4

- 239000002245 particle Substances 0.000 claims description 4

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 claims description 3

- LICVGLCXGGVLPA-UHFFFAOYSA-N disilanyl(disilanylsilyl)silane Chemical compound [SiH3][SiH2][SiH2][SiH2][SiH2][SiH3] LICVGLCXGGVLPA-UHFFFAOYSA-N 0.000 claims description 3

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 claims description 2

- 229910052796 boron Inorganic materials 0.000 claims description 2

- 239000001307 helium Substances 0.000 claims description 2

- 229910052734 helium Inorganic materials 0.000 claims description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 claims description 2

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 claims 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 claims 1

- NBIIXXVUZAFLBC-UHFFFAOYSA-L Phosphate ion(2-) Chemical compound OP([O-])([O-])=O NBIIXXVUZAFLBC-UHFFFAOYSA-L 0.000 claims 1

- OFZCMPKIAFHGRP-UHFFFAOYSA-N [GeH3][GeH2][GeH2][GeH2][GeH2][GeH3] Chemical compound [GeH3][GeH2][GeH2][GeH2][GeH2][GeH3] OFZCMPKIAFHGRP-UHFFFAOYSA-N 0.000 claims 1

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 claims 1

- 229910052731 fluorine Inorganic materials 0.000 claims 1

- 239000011737 fluorine Substances 0.000 claims 1

- 229910000073 phosphorus hydride Inorganic materials 0.000 claims 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 43

- 239000000463 material Substances 0.000 description 31

- 239000010410 layer Substances 0.000 description 22

- 239000010408 film Substances 0.000 description 20

- 239000000203 mixture Substances 0.000 description 13

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 11

- 238000006243 chemical reaction Methods 0.000 description 9

- 238000001556 precipitation Methods 0.000 description 7

- 230000008569 process Effects 0.000 description 6

- 239000000047 product Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 230000007246 mechanism Effects 0.000 description 5

- 238000002360 preparation method Methods 0.000 description 5

- 239000000376 reactant Substances 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- -1 lithium aluminum hydride Chemical compound 0.000 description 4

- 239000002244 precipitate Substances 0.000 description 4

- 230000005855 radiation Effects 0.000 description 4

- 238000007738 vacuum evaporation Methods 0.000 description 4

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 3

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 239000000919 ceramic Substances 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 229910000077 silane Inorganic materials 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 229910001220 stainless steel Inorganic materials 0.000 description 3

- 239000010935 stainless steel Substances 0.000 description 3

- 230000003068 static effect Effects 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- 206010034972 Photosensitivity reaction Diseases 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- 230000004888 barrier function Effects 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 238000010276 construction Methods 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000001704 evaporation Methods 0.000 description 2

- 230000008020 evaporation Effects 0.000 description 2

- 239000008246 gaseous mixture Substances 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 150000004678 hydrides Chemical class 0.000 description 2

- 239000000543 intermediate Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 230000000737 periodic effect Effects 0.000 description 2

- 235000011007 phosphoric acid Nutrition 0.000 description 2

- 230000036211 photosensitivity Effects 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 150000004756 silanes Chemical group 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 238000001179 sorption measurement Methods 0.000 description 2

- 230000003595 spectral effect Effects 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- 238000004804 winding Methods 0.000 description 2

- 229910001339 C alloy Inorganic materials 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 241000208152 Geranium Species 0.000 description 1

- 206010034960 Photophobia Diseases 0.000 description 1

- BUGBHKTXTAQXES-UHFFFAOYSA-N Selenium Chemical compound [Se] BUGBHKTXTAQXES-UHFFFAOYSA-N 0.000 description 1

- 229910000831 Steel Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 208000027418 Wounds and injury Diseases 0.000 description 1

- PZKRHHZKOQZHIO-UHFFFAOYSA-N [B].[B].[Mg] Chemical compound [B].[B].[Mg] PZKRHHZKOQZHIO-UHFFFAOYSA-N 0.000 description 1

- HMDDXIMCDZRSNE-UHFFFAOYSA-N [C].[Si] Chemical compound [C].[Si] HMDDXIMCDZRSNE-UHFFFAOYSA-N 0.000 description 1

- BSYQEPMUPCBSBK-UHFFFAOYSA-N [F].[SiH4] Chemical class [F].[SiH4] BSYQEPMUPCBSBK-UHFFFAOYSA-N 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- HSFWRNGVRCDJHI-UHFFFAOYSA-N alpha-acetylene Natural products C#C HSFWRNGVRCDJHI-UHFFFAOYSA-N 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 230000003667 anti-reflective effect Effects 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- LUXIMSHPDKSEDK-UHFFFAOYSA-N bis(disilanyl)silane Chemical compound [SiH3][SiH2][SiH2][SiH2][SiH3] LUXIMSHPDKSEDK-UHFFFAOYSA-N 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000009388 chemical precipitation Methods 0.000 description 1

- 239000007795 chemical reaction product Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 238000005336 cracking Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 230000007812 deficiency Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000004821 distillation Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 125000002534 ethynyl group Chemical group [H]C#C* 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000004817 gas chromatography Methods 0.000 description 1

- QUZPNFFHZPRKJD-UHFFFAOYSA-N germane Chemical compound [GeH4] QUZPNFFHZPRKJD-UHFFFAOYSA-N 0.000 description 1

- 150000004820 halides Chemical class 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 229910000040 hydrogen fluoride Inorganic materials 0.000 description 1

- GPRLSGONYQIRFK-UHFFFAOYSA-N hydron Chemical compound [H+] GPRLSGONYQIRFK-UHFFFAOYSA-N 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 208000013469 light sensitivity Diseases 0.000 description 1

- 239000012280 lithium aluminium hydride Substances 0.000 description 1

- GVALZJMUIHGIMD-UHFFFAOYSA-H magnesium phosphate Chemical compound [Mg+2].[Mg+2].[Mg+2].[O-]P([O-])([O-])=O.[O-]P([O-])([O-])=O GVALZJMUIHGIMD-UHFFFAOYSA-H 0.000 description 1

- 239000004137 magnesium phosphate Substances 0.000 description 1

- 229960002261 magnesium phosphate Drugs 0.000 description 1

- 229910000157 magnesium phosphate Inorganic materials 0.000 description 1

- 235000010994 magnesium phosphates Nutrition 0.000 description 1

- YTHCQFKNFVSQBC-UHFFFAOYSA-N magnesium silicide Chemical compound [Mg]=[Si]=[Mg] YTHCQFKNFVSQBC-UHFFFAOYSA-N 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- QSHDDOUJBYECFT-UHFFFAOYSA-N mercury Chemical compound [Hg] QSHDDOUJBYECFT-UHFFFAOYSA-N 0.000 description 1

- 229910052753 mercury Inorganic materials 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 239000010955 niobium Substances 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 208000017983 photosensitivity disease Diseases 0.000 description 1

- 231100000434 photosensitization Toxicity 0.000 description 1

- 238000005086 pumping Methods 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 229910052711 selenium Inorganic materials 0.000 description 1

- 239000011669 selenium Substances 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910052990 silicon hydride Inorganic materials 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 229910021483 silicon-carbon alloy Inorganic materials 0.000 description 1

- 239000010959 steel Substances 0.000 description 1

- 239000004575 stone Substances 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 229920002994 synthetic fiber Polymers 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 229910052714 tellurium Inorganic materials 0.000 description 1

- PORWMNRCUJJQNO-UHFFFAOYSA-N tellurium atom Chemical compound [Te] PORWMNRCUJJQNO-UHFFFAOYSA-N 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

- LXEXBJXDGVGRAR-UHFFFAOYSA-N trichloro(trichlorosilyl)silane Chemical compound Cl[Si](Cl)(Cl)[Si](Cl)(Cl)Cl LXEXBJXDGVGRAR-UHFFFAOYSA-N 0.000 description 1

- VEDJZFSRVVQBIL-UHFFFAOYSA-N trisilane Chemical compound [SiH3][SiH2][SiH3] VEDJZFSRVVQBIL-UHFFFAOYSA-N 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

-

- C—CHEMISTRY; METALLURGY

- C01—INORGANIC CHEMISTRY

- C01B—NON-METALLIC ELEMENTS; COMPOUNDS THEREOF; METALLOIDS OR COMPOUNDS THEREOF NOT COVERED BY SUBCLASS C01C

- C01B33/00—Silicon; Compounds thereof

- C01B33/02—Silicon

- C01B33/021—Preparation

- C01B33/027—Preparation by decomposition or reduction of gaseous or vaporised silicon compounds other than silica or silica-containing material

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/24—Deposition of silicon only

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02422—Non-crystalline insulating materials, e.g. glass, polymers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02367—Substrates

- H01L21/0237—Materials

- H01L21/02425—Conductive materials, e.g. metallic silicides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02436—Intermediate layers between substrates and deposited layers

- H01L21/02439—Materials

- H01L21/02441—Group 14 semiconducting materials

- H01L21/0245—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/0257—Doping during depositing

- H01L21/02573—Conductivity type

- H01L21/02576—N-type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/0257—Doping during depositing

- H01L21/02573—Conductivity type

- H01L21/02579—P-type

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/0262—Reduction or decomposition of gaseous compounds, e.g. CVD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/18—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof

- H01L31/20—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof such devices or parts thereof comprising amorphous semiconductor materials

- H01L31/202—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof such devices or parts thereof comprising amorphous semiconductor materials including only elements of Group IV of the Periodic System

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Abstract

내용 없음.

Description

제1a도는 본 발명에 의한 비결정 반도체준비 방법의 플로우챠트.

제1b도는 비결정 실리콘 준비방법을 나타내는 제1a도 플로우챠트에 적합한 도.

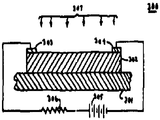

제2a도는 적합한 반도체 제조의 도시 배열의 구성도.

제2b도는 본 발명의 비결정 반도체 준비 반응챔버(Chamber)의 구성도.

제2c도는 본원 발명에 의하여 생산된 필름과 다른 기술로 생산된 필름간에 차이를 나타내는 파장에 대한 상대 양자 효율그라프.

제3도는 본 발명에 의하여 준비되는 광검출기와 부속회로의 구성도.

제4도는 본 발명에 의한 이질의 PN 접합 반도체의 구성도.

제5도는 본 발명에 의하여 준비된 쇼트키 장벽 광기전 장치의 단면도.

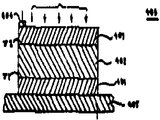

제6도는 본 발명에 의하여 준비된 P-I-N 광기전 장치의 단면도.

제7도는 본 발명에 의하여 준비된 P-N 광기전 장치의 단면도.

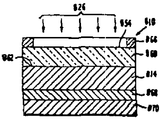

제8도는 본 발명에 의하여 준비된 또 다른 이질의 P-N 접합 광기전 장치의 단면도.

* 도면의 주요부분의 대한 부호의 설명

401 : n타입 반도체 402 : 진성재료

614 : 몸체 710 : 반도체장치

본 발명은 비결정 반도체의 제법 특히 반도체 장치에서의 사용에 관한 것이다.

비결정 반도체는 여러 장치에서 폭 넓게 유용되고 있다.

예로서, 기억장치, 전계효과와 얇은 필름, 디스플레이와 발광 장치등에 사용되고 있다.

비결정 반도체는 특히 방사때 전압을 공급하거나 전기적으로 에너지를 줄 때 방사하는 광기전 장치에 유용하다.

불행히도 광기전 장치는 현재 종래의 전기에너지 원과는 비교가 되지 않는다.

이것은 일차적으로 적당한 반도체 재료의 제조단가가 그 이유이다.

처음으로 고가이며 비교적 두꺼운 단일 결정재가 얻어졌다.

더욱 최근에는, 가스상에서 글로우 방진함으로써 감광에 적합한 비결정재를 만들어 왔다.

글로우 방전으로 준비된 수소화 실리콘의 형태로된 비결정재가 특히 적합한 것으로 알려져 왔다.

미국특허 4064521; 4142195; 4163677; 4196438; 4200473과 4162505에서 나타나 있다.

비결정 실리콘의 글로우 방전 제품은 단일결정재의 제품보다 가격이 낮지만, 가격의 관점은 이 기술의 일반적인 적용에 한계를 계속 나타내고 있다.

염가 재료를 제공하기 위한 시도는 모노실란(monosilane, SiH4)의 증착분해 (Pyrolytic decomposition)에 의하여 비결정 실리콘의 제조를 포함하고 있다.

다른 기술들을 스퍼티링(Sprttering)과 진공 증발을 포함하는 모노실란을 채용하고 있다.

불행히도, 보통 화학증기분체(Chemical Vapor Deposition, C. V. D.)라고 알려진 모노실란의 증착분해로 제조되는 비결정 실리콘은 제한된 광기전성 또는 광전도성을 보이고 있다.

이러한 것은 재료가 수소화되어 재료의 불량밀도 라고 알려져 온 것을 보정한때 일지라도 계속 되어온 것이다.

이와 유사하게 모노실란의 스퍼터링과 진공 증발로 준비된 비결정 실리콘은 글로우 방전재료로 된 것보다 덜한 광감응을 나타내고 있다.

여러가지의 플루오르씰란(fluorosilane)으로부터 비결정 실리콘을 만드는 여러가지 시도가 예를 들어 미국특허 2120451과 4125643에서와 기술된 바와 같이 시도되어 왔다.

여기에 다시, 합성적인 재료의 광 감응성이 글로우 방전에 의하여 제조되는 수소화 비결정 실리콘과 합하여진 것과 유사하게 된 반면 그 제법의 비용은 역시 상당한 것이다.

비결정 실리콘을 준비하는 또 다른 방법은 압력 10-4토르(Torr) 이하에서 유지되는데 필요한 초진공 반응기에서 비교적 고온(1400°내지 1600°)에서 실란의 분해를 하는 것이다.

잔여 가스 기류는 미국특허 4237150과 4237151호에서 설명된 바와 같이 저온에서 유지되는 기질(Substrate)로 향한다.

이 기술은 귀찮고, 고온 진공을 요하며 비교적 낮은 광전도성(10-7(Ω-㎝)-1혹은 이하)의 필름으로 된다.

따라서 본 발명의 목적은 적합한 광 감음성을 가진 효율좋고 염가의 반도체 재료를 얻고자 하는 것이다.

본 발명의 다른 목적은 적합한 광기전 및 광 검출장치를 얻고자 하는 것이다.

본 발명의 또 하나의 목적은 단일 결정재료 보다 염가이며 덜 복잡하며 적합한 광 감지성이 있는 반도체 재료의 제품을 제공하는 것이다.

본 발명의 또 하나의 다른 목적은 글로우 방전, 스퍼터링 그리고 진공 증발기술에 의한 것보다 염가하여 덜 복잡한 비결정 실리콘 재료를 얻고자 하는 것이다.

전술한 바와 같은 목적을 달성하기 위하여 본 발명은 약 500°이하의 온도에서 하나 혹은 그 이상의 가스상 종합반도체의 증착 분해에 의하여 적당한 광 감지성을 갖는 비결정 반도체를 준비하는 방법을 제공한다.

본 기술은 저조한 광전도성과 열등한 광 기전성을 갖게 되는 실란 및 플루오르 실란을 증착 분해하는 선행 기술과는 상이하다.

본 발명은 배치 프로쎄씽(batch processing)에 반대되는 연속 프로쎄씽으로 이바지 하게되고 가격과 글로우 방전, 스퍼터링 그리고 진공 증발에 의한 단일결정과 비결정 실리콘의 제품에 따르는 복잡한 장치를 제거하여 준다.

본 발명의 한면에 의하면, 분해는 약 300℃ 내지 약 500℃의 범위내의 온도에서 일어나고 약 350℃에서 450℃의 범위가 바람직하다.

본 발명의 다른 면에 의하면, 분해는 약 1기압 보다 작고 수운 1미크론 이상인 폴리실란의 부분 압력에서 일어나며, 약 1토르 이상이 바람직하다.

압력은 증착 분해하는 동안 입자의 가스상 핵형성을 제한하기 위하여 약 1토르에서 약 100토르의 범위내가 바람직하다.

본 발명의 또 한면에 의하면 폴리쎄미 콘덕턴스(polysemiconductance)는 디쎄미 콘덕턴스(disemiconductance)에서 헥사써미콘덕턴스(hexasemiconductance)까지와의 범위의 종류에서 선택되며 식 ScnH2n+2로 나타나는데 여기에서 "Sc"는 실리콘이나 게르마늄 같은 반도체를 나타내고 n은 2에서 6까지의 범위이다.

폴리쎄미 콘덕턴스는 마그네슘 규화물(Mg2Si)와 같은 쎄미 콘덕타이드(Semiconductide)와 인산(H3PO4, 오르토인산), 진황산(H2SO4), 불화수소(HF) 및 염산(HCl)과 같은 용액상 산과의 반응에서 바람직하게 얻어진다.

고순도의 디실란을 얻고자 한다면, 트랩(trap)된 디실란은 증류를 트랩하기 위한 이중 트랩과 저온 부분 분리법 또는 가스 크로마토그라피 등과 같은 다른 방법에 의하여 더욱 순화될 수 있다.

폴리세미 콘덕턴스는 디실리콘 헥사 클로라이드 같은 반도체 할로겐화물과 리듐 알루미늄 수소화물 같은 수소화물의 환원에 의하여 얻어질 수도 있다.

본 발명의 또 다른면에 의하면, 기체상은 하나 혹은 2이상의 도판트(dopant) 가스를 포함할 수 있다.

도판트 가스는 도우프된 재료에 바람직한 도전률 타입에 따라 선택된다.

도핑(doping)에 적합한 가스는 도전률 타입이 n인지 p인지에 따라 인화수소(phosphine)와 디보란(diborane)을 포함한다.

본 발명의 또 다른 면에 의하면, 가스상은 불활성 가스 캐리어를 포함하고 있다.

적당한 불활성 가스 캐리어는, 아르곤, 헬륨, 그리고 하이드로겐이다.

가스상 재료는 가열된 기질에서 유리하게 분해되며 분해 온도는 기질의 온도이다.

본 발명의 또 다른 면에 의하면, 비결정 반도체 기구는 하나 혹은 2이상의 가스상 폴리세미 콘덕턴스 증착분해를 거쳐 몸체를 형성하거나 몸체에 접착함으로서 준비된다.

몸체는 원하는 도전을 타입에 따라 도판트를 포함할 수 있는 하나 또는 2이상의 분리된 층에서의 기질에서 바람직하게 형성된다.

공유영역을 형성하는 금속과 반사 방지층과 같은 부가층이 포함될 수도 있다.

이하 도면에 따라 본 발명을 상세히 설명하면 다음과 같다.

제1a도는 본 발명의 일반적인 실시인 플로우챠트 100A를 설명하는 것이고, 제1b도는 본 발명에 의하여 주어지는 특성을 지닌 비결정 실리콘의 특정한 준비를 위한 플로우 챠트 100B를 나타낸다.

본 발명 실시를 위한 세미 콘덕턴스는 주기율표의 IV족으로부터 선택되며 따라서 게르마늄 혹은 주석을 포함할 수 있으며, 그리고 주기율표의 VI족으로부터 일때는 셀렌과 텔루륨을 포함할 수 있다.

다음에 기술하는 바와 같이, 특히 적합한 반도체는 실리콘이다.

한번 폴리세미 콘덕턴스가 준비되고, 공정 블록 102A에 표시된 반응 챔버내로 도입된다.

챔버내에 있는 동안 폴리세미 콘덕턴스는 공정 블록 103A에서 표시되는 바와 같이 증착분해 된다.

증착 분해는 원하는 기질의 표면에서 재료를 비결정 반도체로 변환시킨다는 고려하에 가스재료에 적합한 온도에서 열의 효과를 동반한다.

선행 기술과 비교한다면, 증착 분해로 제조된 폴리세미 콘덕턴스는 모노세미 콘덕턴스(monosemiconductance)로부터의 비결정 반도체의 제품에서 흔히 나타나는 수소 결점 특성이 나타나지 않는다.

결과적으로 최종 제품을 수소 이온 이식이나 헤비도핑을 할 필요가 없는 것이다.

특히, 본 발명은 제1b도의 플로우챠트 100B에 의하여 비결정 실리콘의 제조에 적합한 것이다.

이 공정에서 폴리세미 콘덕탄은 공정블록 101B에 따라 폴리실란의 형태를 취한다.

한번 제조되면 폴리실란은 공정 블록 102B에 따라 반응챔버에 도입된다.

챔버에 있는 동안 폴리실란은 공정블록 103B에 의하는 바와 같이 가열된다.

이로 인하여 비결정 실리콘으로 분해된다. 제료는 모노실란을 분해하는데 필요한 온도보다 대체로 낮은 온도에서 균일하고 조정 가능한 상태하에서 준비된다.

또한, 폴리실란의 분해로 생성된 비결정 실리콘 제품은 수소 결핍을 보충하기 위한 후속 처리가 필요없는 것이다.

제1a도의 플로우챠트에 따라 준비된 반도체의 경우와 같이 제1b도에 의하여 제조되는 비결정 실리콘은 여러종류의 반도체 장치에서 널리 유용하다.

보통의 경우에, 본 발명에 따라 생성된 비결정 반도체는 여러종류의 반도체 장치에서 다른 방법으로 생산된 반도체들에 대치될 수 있다.

이것은 광기전, 광 전도 그리고 전류 정류장치에서 사실이다.

폴리 실란의 경우에 유용한 것들에는 디실린, 트리실란, 테트라실란, 펜타실란, 그리고 헥사실란이 포함된다.

그족의 이성체 역시 적합하다. 유용한 멤버의 종류에 대한 제한은 단지 원하는 반응에 수반되는 폴리실란의 안정성에 의하여 지배된다.

폴리실란의 오더는 증가하면서 모든 안정성에는 환원이 있으나 보통 이것은 적당한 조작 조건에 의하여 보충된다.

증착 분해된 폴리실란은 폴리실란의 혼합물의 형태를 취하거나 단일 폴리실란 단독으로 제공될 수 있다.

또한 적어도 하나의 폴리실란의 존재 하는한 가스 혼합물은 모노실란을 포함할 수 도 있다.

이것은 가스상 부분 압력을 줄이는 효과가 있고 따라서 조작 조건은 그에 따라 조정된다.

가스 혼합물은 또한 도판트와 비활성 가스 캐리어를 포함할 수 있다.

적당한 조작 압력은 약 1기압이나, 약 1토르의 압력까지 낮게 내려가는 저압에서 행하여 질수도 있다.

바람직한 압력은 입자의 가스상 핵생성을 제한하기 위하여 약 1토르에서 약 100토르의 범위내이다.

적당한 온도는 약 300℃에서 약 500℃의 범위내이다.

특히 적당한 약 350℃에서 약 450℃의 범위이다.

가스상 혼합물이 전술한 온도의 어느점에서 가열된 기질위를 지날 때 또는 온도가 전술한 범위의 어느 하나의 적어도 일부분에서 변할때에 고품질의 비결정 실리콘이 기질상에서 얻어진다.

특별히 양질의 필름은 모노실란이 가스상 혼합물로부터 적어도 부분적으로 제거될 때 생성된다.

예를 들어 헥사실란 이하 같은 매우 상위 순의 실란은 실온에서 무시할 만큼의 증기압을 갖고 있기 때문에 표준 온도와 압력에서 원하는 비결정 실리콘 필름의 제품에 거의 효율이 없다.

그러나, 위순의 실란이 가열되어 예를 들어 수은 1㎜ 이상의 증기압을 내게되면 역시 양질의 비결정 실리콘 필름을 제공할 수 있다.

본 발명에 의한 비결정 반도체를 준비하기 위한 도시 배치는 제2도에 표시되어 있다.

배열은 2개로 구분되어 있는데, 적합한 세미 콘덕탄의 제조를 나타내는 210과 세미콘덕탄을 원하는 비결정 반도체로 변환하는 것을 나타내는 250이다.

배열 200은 특히 증착 분해에 의한 비결정 실리콘의 제조에 응용되나 다른 비결정 반도체의 제조를 위하여 적절한 수정이 가해질 수도 있다는 것이 이해될 것이다.

도시한 변환부 250에서, 선택된 폴리실란을 포함하는 반응물은 덮개 261의 형체내의 반응 챔버 260에 도입된다.

반응 챔버 260은 도시한 바와 같이 비결정 실리콘이 침전되는 기질 262를 내포하고 있다. 챔버 261은 기질 262를 오염시키지 않는 물질로 되어있다.

적합한 재료로는 석형, 유리, 스테인레스 스틸이다.

제2도의 반응챔버 261에는 입구 263과 출구 264가 있다.

입구 263은 공급기 252와 255로부터 하나 또는 2이상의 도판트 가스에 의하여 보충되는 가스 혼합물을 진입시키는 조정 밸브 251을 통하여 선택된 폴리실란 또는 모노실란-폴리실란 혼합물을 유입하게 한다.

입구 263 하부에는 기질 262의 홀더 266의 지지구 265가 위치하고 있다.

도시된 기질 홀더 266은 쎄라믹 코어가 감기고 저항소자 266을 둘러싼 쎄라믹 바인더로된 카드리지 가열기이다.

후자는 홀더를 따라 지지하도록 뻗어 있는 적합한 권선에 의하여 에너지를 받고 있다.

스테인레스 스틸 케이스는 화살 G로 나타나는 유입 가스 흐름으로부터 세라믹 코어를 절연한다.

압력계 270은 내부 압력을 나타내기 위하여 챔버 261에 장착된다.

기질 262의 온도는 히터 266r의 권선에 포함된(도시 안됨) 게이지에 의하여 모니터된다.

기질 262는 대표적으로 유리이다.

원하는 비결정 실리콘 침전물을 만들기 위하여 가스 혼합물 G는 기질위를 지나서 진공펌프(도시 안됨)의 효과로 인하여 출구 264쪽으로 끌려나간다.

기질 262은 약 350℃에서 약 500℃의 범위내의 온도에서 반응하여 가스흐름의 적어도 일부는 증착 분해된다.

분해 조성물은 절선 B로 나타난다.

배기 E로 나타나는 가스 혼합물의 균형은 출구 264를 통해 나간다.

상술한 바와 같은 동적 시스템의 택일로서 정적 침전 시스템이 역시 사용될 수도 있다.

정적 침전에서 쎄미콘덕턴은 밸브를 통해 빈 반응기내에 도입된다.

그리고 배기와 입구 밸브는 닫히고 일정 부피의 가스 혼합물은 챔버내에 충진된다.

코일의 가열효과로 인하여 충진된 가스는 반응기의 벽과 기질에서 분해한다.

원하는 비결정 실리콘의 침전물이 기질상에 남는다.

정적 시스템은 가스 중간물의 부피와 펌핑에 결제적인 잇점이 있다.

챔버 261내의 압력은 약 1토르에서 대기압의 범위내이다.

진공이 감소되면서 침전율도 따라서 감소된다.

임계 압력은 입구에서 실란 혼합물의 부분 압력이다.

부분 압력이 너무 높으면 즉 약 100토르 이상이면 가스상은 입자의 핵생성이 일어나고 비결정 및 결정 실리콘의 혼합물이 생기는 샤워(shower)를 초래하게 된다.

침전된 비결정 실리콘의 성질은 아르곤과 같은 반응물에 부수되는 불활성 완충 가스의 양에 따라 조정될 수 있다.

아르곤의 양은 반응물의 부분 압력에 영향을 미치지 않으므로 성질의 원하는 수정에 따라 어떤 적당한 레벨에서도 도입될 수 있다. 또한 침전된 비결정 실리콘의 전기적 성질은 공급기 252와 255로부터의 도판트가스의 성질에 따라 조정된다.

p타입 도핑에서는 도판트 가스 252는 B2H6, B10H14같은 불화수소가 될수 있는데 n타입 도핑에서는 도판트 가스 255는 PH3또는 P2H4같은 수소화인 것이다.

선택적으로 바람직한 도판트 수소화물은 반응물에서 붕화 마그네슘 및/또는 인산마그네슘을 포함함으로서 가스 혼합물에서 형성될 수 있다.

여러종의 어느 다른 도판트도 널리 사용될 수 있다고 설명된다.

어떤 경우에는 공급기 252와 253에서와 같이 2 또는 그 이상의 별개의 공급기에서 같은 도판트 가스가 선택적으로 적용되는 것이 바람직하다.

가스혼합물 G의 주요부는, 챔버 261이 파손되는 경우 반응물의 자연적인 산화를 막기 위하여 불활성 가스로 되는 것이 바람직하다.

제2도의 기질 262가 경제적인 이유로 유리로 선택된다면, 금속 기질, 특히 스틸도 사용될 수 있다.

비결정 게라늄을 침전시키기 위하여, 디게트만(Ge2H6)이 사용될 수 있고 150℃에서 220℃의 범위의 온도에서 침전이 행하여 진다.

디게르만 대신 모노게르만(GeH4)가 사용될 수도 있으나 침전률은 디게르만 보다 다소 늦다.

트리게르만(Ge3H8) 같은 다른 상위 게르만도 사용될 수 있다.

본 발명의 실시예는 표 1에 요약된 다음의 예를 들면서 설명된다.

[표 1]

[장치의 상세한 설명]

본 발명에 의한 비결정 반도체는 여러종류의 반도체 장치를 형성하는데 쓰일 수 있다.

본 발명에 의하여 제조되는 비결정 실리콘 필름은 보통 글로우 방전과 초진공 침전 필름과는 다르다는 것이 중요하다.

본 발명에 의한 필름은 이온 손상을 입지않는다.

본 발명 필름과 종래 기술에 의한 필름 특성 차이의 예로서, 제2c도에서 본 발명에 의한 필름과 대표적인 글로우 방전 필름의 스펙트럼 응답을 비교한다.

제2c도의 곡선에서 상대 기전 양자효과는 여기 방사의 파장에 대하여 그래프를 그린 것이다.

제2c도로부터 글로우 방전 필름과 접촉함으로서 본 발명에 의하여 제조된 비결정 실리콘 필름은 높은 상대 양자 효율을 가진 스펙트럼 응답을 갖고 있음이 명백하다.

또한, 초진공 침전 필름과의 비교로서, 본 발명 필름은 더 높은 광전도성 얻는데 미국특허 4237150과 4237151의 초진공 필름 침전 필름이 10-9-10-7ohms-㎝-1의 범위인데 반하여 즉, 10-6-10-4ohms/㎝(ohms-㎝-1)이다.

제3도의 광 검출기 300이 그러한 하나의 장치이다.

비결정 실리콘 침전물 302와 같이 유리기질 301은 알루미늄 접촉면 303과 304와 같이 주어지고 밧데리 305를 통해 로드 306에 회로안에 연결되어 있다.

비결정 실리콘 302에 빛 307이 갑자기 비쳐지는 순간 밧데리 305의 전압에 의하여 작용하는 1쌍의 전자홀이 생기고, 다수의 홀-전자쌍이 생김에 따라 로드 306에서 볼트가 상승된다.

본 발명에 의하여 제조된 비결정 실리콘을 사용케 하는 다른 장치는 제4도의 헤테로 접합 반도체장치 400이다.

이 장치는 p타입 재료 403과 반대의 진성(i타입)재료 402 사이에 그리고 반대로 진성 재료 402와 n-타입 반도체 재료 401 사이에 다른 접합점 J1과 J2를 가지고 있다. p와 n타입 재료 403과 401의 밴드갭은 진성 재료 402와는 다르다.

진송재료 402와 n타입 재료 403은 화학적 증발 침전에 의하여 형성된다. n타입 재료인 경우 포시핀 같은 토판트가 포함된다.

p타입재 403 역시 붕소 같은 적당한 도판트로 화학 침전에 의하여 만들어 진다.

또한 p타입 재료 가스 흐름은 실리콘 카본 합금(a-(Si, C) : H)을 생산하기 위하여 메탄 또는 아세틸렌을 포함한다.

합성장치 400은 그리드 접점 404에 의하여 조정되고 기질 405에 바람직하게 침전되는 P-I-N 반도체이다.

장치 400은 비결정 실리콘 카본 합금층 401로 인하여 진성층 402로 빛이 많이 들어 가도록된 다른 유사한 장치에 비하여 잇점이 있는데 그것은 진성측 402보다 높은 밴드갭을 가지고 있다.

보통, 바람직한 반도체 장치는 다른 기술로 되는 반도체층을 본 발명에 의하여 준비되는 반도체층을 대체함으로서 생산될 수 있다.

예를 들어 미국특허 4064521호에 설명된 여러가지 장치는 선행 기술의 글로우 방전 비결정 실리콘을 증착 분해된 폴리세미 콘덕탄을 대체 함으로서 본 발명에 의하여 채택될 수 있다.

SinH2n+2(n=2-6)으로부터 되는 CVD 비결정 실리콘의 집적 상태의 평균밀도는 1016/㎤에서 1017/㎤ 범위에서 되는 장치로 믿어지거나 추론되고, 다른 방법 즉 스퍼터 하거나 증발시키는 비결정 실리콘에 의하여 제조되는 비결정 실리콘의 밀도보다 아주 낮다.

집적 상태의 평균 밀도는 1019/㎤이거나 혹은 크다.

이로 결점 상태의 낮은 밀도는 공핍폭이 길어지고 재결합을 낮게하여 양질의 장치를 얻게 된다.

첫번째 도핑된 층에서 전극 628의 표면 비저항이 약 10ohms/CMS 혹은 그 이상의 순이라면 몸체 614에서 발생하는 전류의 수집을 위한 첫번째 도핑층 613에서 제5도에서와 같은 그리드 접점을 역시 갖게되는 오히려 낳고, 전극 628의 반대쪽에 두 번째 도핑층 615의 표면에 전기접점 627이 있다.

전기접점 627은 알루니늄, 크로뮴, 탄타륨, 안티모니, 니오븀 혹은 스테인레스 스틸 같은 전기 전도성을 갖는 재료로 되어 있다.

제5도에서 설명한 바와 같이, SinH2n+2(n은 2-6)의 화학적 증기 분배로 얻어지는 비결정 실리콘 필름의 흡착 계수는 가시범위에서의 단일 결정 실리콘의 흡착 계수보다 크다.

이런 이유로 얇은 층의 비결정 실리콘 만이 충분한 태양 방사 흡착에 필요하다.

특히 비결정 실리콘의 진성 부위는 두께가 약 1미크론 또는 그 이하이며 제 1, 2의 도핑층 613과 614는 두께가 각각 몇백 옹그스트롬이다.

제7도는 보면, 반도체 장치 710은 광기전장치이고, 더욱 상세하게는 P-N 접합 태양 전지이다.

광기전 장치 710은 택일된 도핑 가스와 함께 본 발명에 의한 폴리실란 화학적 증기 분해 방법에 의해 제조되는 비결정 실리콘의 범위 711을 포함한다.

범위 711은 중간적인 P-N 접합 756과 함께 반대 전도성의 제2의 도핑층 754와 접촉하는 전도성 타입의 제1의 도핑층 752를 구성한다.

이러한 목적으로, 제1도의 도핑층 752는 p-타입 전도성이고 제2의 도핑층은 n-타입 전도성이다.

제 1, 2의 도핑층 752,754는 광기전 장치 710의 몸체 714이다.

범위 711은 제2의 도핑층 754의 표면에서 제3의 도핑층 758을 포함하지만 제2의 도핑층 754보다 높은 도핑 집중력이 있다.

그래서 제3의 도핑층 758은 n-타입 전도성이다.

제3의 도핑층 758은 몸체 714에서 저항 접촉을 하도록 도와준다.

제5, 6, 7도에서 설명된 개구가 태양 전지로 기술되었지만, 이러한 기구로서 고주파 광검지 즉 방사 에너지에 응답하는 장치로 유용될 수 있는 장치라는 것이 예기된다.

제8도에서, 본 발명의 반도체 장치로서 다른 기구가 810으로 나타나 있다.

반도체 장치 810은 본 발명의 8번째 기구를 설명하기 위한 헤테로 접합 광기전 장치로서 나타나 있다.

광기전 장치 810은 증착 분해에 의하여 합성되는 비결정 실리콘의 몸체 814를 포함한다.

비결정 실리콘의 몸체 814는 본 발명의 제4의 몸체 402와 같은 특성이 있다.

광기전 장치 810의 구성은 전술한 기구의 구성과 유사하다.

반도체 860은 비결정 실리콘의 몸체 814의 분해를 위한 변환장치(제 4, 5도에서 전술함)에서 지지구로서의 역할을 한다.

선택적 구성 방법으로서 몸체 814는 디실란의 증착으로서 형성될 수 있으며, 반도체 범위 860은 몸체 814에 스퍼터될 수 있다.

다음 제1의 전극 866, 중간층 868 그리고 제2전극 870은 기술계에서 잘 알려진 마스킹과 증발기술로서 형성된다.

본 발명의 다른 기구가 광기전 장치로서 기술되는 동안 반도체 기술에서의 그러한 기술에는 그러한 장치가 정류기로서 역할을 할 수 있음이 명백하다.

장치 430이 정류기로서 작동된다면 태양 방사에 세미 트랜스 페어런트 하거나 트랜스 페어런트한 재료로 된 반도체 범위 860 필요없게 된다.

또한, 태양 방사가 그위에 충돌할 수 있는 표면 864도 필요없게 된다.

본 발명의 여러 양상이 도면과 명세서에 의하여 설명되면서, 나타나고 설명된 것들을 위한 동등한 구성물의 치환이 다음의 청구범위에서 설명되는 본 발명의 사상이나 범위로부터 이탈되지 않고 만들어 질뿐 아니라 전술한 상세한 설명은 여러가지 설명만을 위한 그리고 그러한 변화를 위한 것임이 이해될 것이다.

Claims (16)

- 500℃ 이하의 온도에서 하나 혹은 그 이상의 가스상 폴리세미 콘덕탄(Polysemiconductanes)을 증착분해하는 것을 특징으로 하는 비결정 반도체(Amorphous Semiconducter)를 제조하는 방법.

- 제1항에 있어서, 증착 분해가 약 300℃에서 약 500℃까지의 범위의 온도에서 일어나는 비결정 반도체를 제조하는 방법.

- 제2항에 있어서, 상기 온도는 약 350℃에서 약 450℃까지의 범위내인 비결정 반도체를 제조하는 방법.

- 제1항에 있어서, 약 수은 1미크론 보다 크고 약 1기압 보다 작은 분압에서 증착 분해가 일어나는 비결정 반도체를 제조하는 방법.

- 제4항에 있어서, 상기 압력이 약 1토르부터의 범위내에 있는 비결정 반도체를 제조하는 방법.

- 제5항에 있어서, 상기 압력이 약 1토르에서 약 100토르까지의 범위내이면서, 그러므로써 입자의 가스상 핵 생성을 방지하는 비결정 반도체를 제조하는 방법.

- 제1항에 있어서, 상기 폴리세미 콘덕탄은 식 SinH2n+2(n은 2-6)로되는 디실란부터 헥사실란을 포함하는 급에서 선택되는 비결정 반도체를 제조하는 방법.

- 제1항에 있어서, 상기 가스상의 하나 또는 그 이상의 도판트(Dopant) 가스를 포함하는 비결정 반도체를 제조하는 방법.

- 제8항에 있어서, 상기 도판트 가스는 가스를 지닌 인과 불소를 포함하는 클라스로부터 선택되는 비결정 반도체를 제조하는 방법.

- 제9항에 있어서, 가스를 포함하는 상기 인은 포스핀(인화수소 pH3)이고 가스를 포함하는 붕소가 디보란(B2H6)인 비결정 반도체를 제조하는 방법.

- 제1항에 있어서, 상기 가스상의 불활성 가스 캐리어를 포함하는 비결정 반도체를 제조하는 방법.

- 제11항에 있어서, 상기 불활성 가스 캐리어가 아르곤이나 헬륨인 비결정 반도체를 제조하는 방법.

- 제1항에 있어서, 상기 폴리실란의 하나 또는 그 이상이 가열된 기질위에 분해되는 비결정 반도체를 제조하는 방법.

- 제13항에 있어서, 분해가 기질의 온도에서 일어나는 비결정 반도체를 제조하는 방법.

- 제1항에 있어서, 상기 폴리세미 콘덕탄은 식 GenH2n+2(n은 2-6)로 표시되는 디게르만으로부터 헥사게르만까지와의 범위내의 급에서 선택되는 비결정 반도체를 제조하는 방법.

- 제15항에 있어서, 상기 분해의 온도가 150℃와 220℃사이인 비결정 반도체를 제조하는 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US24270781A | 1981-03-11 | 1981-03-11 | |

| JP242707 | 1981-03-11 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR910002764B1 true KR910002764B1 (ko) | 1991-05-04 |

Family

ID=22915870

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR8201088A KR910002764B1 (ko) | 1981-03-11 | 1982-03-11 | 비결정 반도체의 제법 및 장치 |

Country Status (11)

| Country | Link |

|---|---|

| EP (1) | EP0075007A4 (ko) |

| JP (1) | JPS58500360A (ko) |

| KR (1) | KR910002764B1 (ko) |

| CA (1) | CA1187622A (ko) |

| ES (1) | ES510893A0 (ko) |

| HU (1) | HU187713B (ko) |

| IN (1) | IN156594B (ko) |

| IT (1) | IT1150674B (ko) |

| NO (1) | NO823744L (ko) |

| OA (1) | OA07249A (ko) |

| WO (1) | WO1982003069A1 (ko) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA1245109A (en) * | 1983-10-31 | 1988-11-22 | Hsien-Kun Chu | Method of forming amorphous polymeric halosilane films and products produced therefrom |

| FR2555206B1 (fr) * | 1983-11-22 | 1986-05-09 | Thomson Csf | Procede de depot de silicium amorphe par decomposition thermique a basse temperature et dispositif de mise en oeuvre du procede |

| DE3441044A1 (de) * | 1984-11-09 | 1986-05-22 | Messerschmitt-Bölkow-Blohm GmbH, 8012 Ottobrunn | Verfahren zur herstellung von duennschicht-halbleiterelementen, insbesondere solarzellen |

| US4637895A (en) * | 1985-04-01 | 1987-01-20 | Energy Conversion Devices, Inc. | Gas mixtures for the vapor deposition of semiconductor material |

| US4696834A (en) * | 1986-02-28 | 1987-09-29 | Dow Corning Corporation | Silicon-containing coatings and a method for their preparation |

| US4762808A (en) * | 1987-06-22 | 1988-08-09 | Dow Corning Corporation | Method of forming semiconducting amorphous silicon films from the thermal decomposition of fluorohydridodisilanes |

| US4923719A (en) * | 1988-08-22 | 1990-05-08 | Allied-Signal Inc. | Method of coating silicon carbide fibers |

| US5424097A (en) * | 1993-09-30 | 1995-06-13 | Specialty Coating Systems, Inc. | Continuous vapor deposition apparatus |

| EP1021389A1 (en) * | 1995-10-18 | 2000-07-26 | Specialty Coating Systems, Inc. | Processes for the preparation of octafluoro- 2,2]paracyclophane |

| ATE230445T1 (de) * | 1995-10-27 | 2003-01-15 | Specialty Coating Systems Inc | Verfahren und vorrichtung zur ablagerung von parylen af4 auf halbleiterwafern |

| US5806319A (en) * | 1997-03-13 | 1998-09-15 | Wary; John | Method and apparatus for cryogenically cooling a deposition chamber |

| US5841005A (en) * | 1997-03-14 | 1998-11-24 | Dolbier, Jr.; William R. | Parylene AF4 synthesis |

| US6051276A (en) * | 1997-03-14 | 2000-04-18 | Alpha Metals, Inc. | Internally heated pyrolysis zone |

| WO2007044429A2 (en) | 2005-10-05 | 2007-04-19 | Nanogram Corporation | Linear and cross-linked high molecular weight polysilanes, polygermanes, and copolymers thereof, compositions containing the same, and methods of making and using such compounds and compositions |

| US7799376B2 (en) * | 2007-07-27 | 2010-09-21 | Dalsa Semiconductor Inc. | Method of controlling film stress in MEMS devices |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| USB524765I5 (ko) * | 1966-02-03 | 1900-01-01 | ||

| US3490961A (en) * | 1966-12-21 | 1970-01-20 | Sprague Electric Co | Method of producing silicon body |

| US4064521A (en) * | 1975-07-28 | 1977-12-20 | Rca Corporation | Semiconductor device having a body of amorphous silicon |

| US4237150A (en) * | 1979-04-18 | 1980-12-02 | The United States Of America As Represented By The United States Department Of Energy | Method of producing hydrogenated amorphous silicon film |

| US4237151A (en) * | 1979-06-26 | 1980-12-02 | The United States Of America As Represented By The United States Department Of Energy | Thermal decomposition of silane to form hydrogenated amorphous Si film |

| JPS5767938A (en) * | 1980-10-16 | 1982-04-24 | Canon Inc | Production of photoconductive member |

-

1982

- 1982-03-10 WO PCT/US1982/000299 patent/WO1982003069A1/en not_active Application Discontinuation

- 1982-03-10 CA CA000398016A patent/CA1187622A/en not_active Expired

- 1982-03-10 ES ES510893A patent/ES510893A0/es active Granted

- 1982-03-10 EP EP19820901328 patent/EP0075007A4/en not_active Withdrawn

- 1982-03-10 JP JP57501373A patent/JPS58500360A/ja active Pending

- 1982-03-10 HU HU821672A patent/HU187713B/hu unknown

- 1982-03-11 IT IT20100/82A patent/IT1150674B/it active

- 1982-03-11 KR KR8201088A patent/KR910002764B1/ko active

- 1982-03-15 IN IN291/CAL/82A patent/IN156594B/en unknown

- 1982-11-10 NO NO823744A patent/NO823744L/no unknown

- 1982-11-11 OA OA57842A patent/OA07249A/xx unknown

Also Published As

| Publication number | Publication date |

|---|---|

| IT1150674B (it) | 1986-12-17 |

| EP0075007A1 (en) | 1983-03-30 |

| IT8220100A0 (it) | 1982-03-11 |

| EP0075007A4 (en) | 1984-06-05 |

| ES8402462A1 (es) | 1984-02-01 |

| IN156594B (ko) | 1985-09-14 |

| HU187713B (en) | 1986-02-28 |

| CA1187622A (en) | 1985-05-21 |

| ES510893A0 (es) | 1984-02-01 |

| JPS58500360A (ja) | 1983-03-10 |

| OA07249A (fr) | 1984-08-31 |

| WO1982003069A1 (en) | 1982-09-16 |

| NO823744L (no) | 1982-11-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4459163A (en) | Amorphous semiconductor method | |

| US4379943A (en) | Current enhanced photovoltaic device | |

| JP2951146B2 (ja) | 光起電力デバイス | |

| US4910153A (en) | Deposition feedstock and dopant materials useful in the fabrication of hydrogenated amorphous silicon alloys for photovoltaic devices and other semiconductor devices | |

| JP2539916B2 (ja) | 光起電力素子 | |

| US4196438A (en) | Article and device having an amorphous silicon containing a halogen and method of fabrication | |

| US4598164A (en) | Solar cell made from amorphous superlattice material | |

| KR910002764B1 (ko) | 비결정 반도체의 제법 및 장치 | |

| US5024706A (en) | Pin heterojunction photovoltaic elements with polycrystal AlP(H,F) semiconductor film | |

| US5006180A (en) | Pin heterojunction photovoltaic elements with polycrystal GaP (H,F) semiconductor film | |

| GB2124826A (en) | Amorphous semiconductor materials | |

| US5007971A (en) | Pin heterojunction photovoltaic elements with polycrystal BP(H,F) semiconductor film | |

| US6124545A (en) | Thin film solar cell | |

| AU637852B2 (en) | Deposition feedstock and dopant materials useful in the fabrication of hydrogenated amorphous silicon alloys for photovoltaic devices and other semiconductor devices | |

| US5002618A (en) | Pin heterojunction photovoltaic elements with polycrystal BAs(H,F) semiconductor film | |

| US4690830A (en) | Activation by dehydrogenation or dehalogenation of deposition feedstock and dopant materials useful in the fabrication of hydrogenated amorphous silicon alloys for photovoltaic devices and other semiconductor devices | |

| CA1245330A (en) | Back reflector system and devices utilizing same | |

| US5002617A (en) | Pin heterojunction photovoltaic elements with polycrystal AlAs(H,F) semiconductor film | |

| US4396793A (en) | Compensated amorphous silicon solar cell | |

| US4478654A (en) | Amorphous silicon carbide method | |

| US5278015A (en) | Amorphous silicon film, its production and photo semiconductor device utilizing such a film | |

| CA1213375A (en) | Semiconductor device having a body of amorphous silicon | |

| US5152833A (en) | Amorphous silicon film, its production and photo semiconductor device utilizing such a film | |

| AU8339082A (en) | Amorphous semiconductor method and devices | |

| US5258207A (en) | Amorphous silicon film, its production and photo semiconductor device utilizing such a film |