KR900005818B1 - 반도체 스위칭회로 - Google Patents

반도체 스위칭회로 Download PDFInfo

- Publication number

- KR900005818B1 KR900005818B1 KR1019870008570A KR870008570A KR900005818B1 KR 900005818 B1 KR900005818 B1 KR 900005818B1 KR 1019870008570 A KR1019870008570 A KR 1019870008570A KR 870008570 A KR870008570 A KR 870008570A KR 900005818 B1 KR900005818 B1 KR 900005818B1

- Authority

- KR

- South Korea

- Prior art keywords

- fet

- output

- gate

- source

- resistor

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/56—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices

- H03K17/687—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/78—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used using opto-electronic devices, i.e. light-emitting and photoelectric devices electrically- or optically-coupled

- H03K17/785—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used using opto-electronic devices, i.e. light-emitting and photoelectric devices electrically- or optically-coupled controlling field-effect transistor switches

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/04—Modifications for accelerating switching

- H03K17/041—Modifications for accelerating switching without feedback from the output circuit to the control circuit

- H03K17/0412—Modifications for accelerating switching without feedback from the output circuit to the control circuit by measures taken in the control circuit

- H03K17/04123—Modifications for accelerating switching without feedback from the output circuit to the control circuit by measures taken in the control circuit in field-effect transistor switches

Landscapes

- Electronic Switches (AREA)

Abstract

내용 없음.

Description

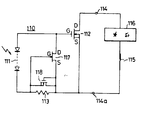

제1도는 제너다이오드가 정전압 전도소자로서 사용되는 본 발명에 따른 반도체 스위칭히로의 일실시예의 회로도.

제2도는 출력 MOSFET를 OFF상태로부터 ON상태로 시프팅하는 입력전류 즉, 감도와 저항간의 관계.

제3도는 정전압 전도소자의 부재시의 반도체 스위칭회로의 응답속도와 입력전류간의 관계도.

제4도는 인핸스먼트형 FET가 정전압전도소자로서 사용되는 본 발명에 따른 반도체 스위칭회로의 다른 실시예의 회로도.

본 발명은 반도체 스위칭회로, 특히 입력신호를 광신호(light signal)로 변환하는 광방사 다이오드(light emitting diode)와 같은 광방사 소자에 광학적으로 접속된 광기전성(photovoltaic)다이오드 어레이에 광신호를 전기신호로 변환하여, 이변환된 전기신호가 FET, 바람직하게는 금속-산화물-반도체 피일드효과 트랜지스터(이후 간단히 "MOSFET"로 칭함)와 같은 출력수단을 구동하는데 사용되는 반도체 스위칭회로에 관한 것이다.

상기 언급한 종류의 반도체 스위칭회로에 대하여, 광기전성 다이오드 어레이가, 광방사 다이오드에 광학적으로 접속되고, 저항과 병렬로 전기 접속되며, 저항이 어레이에 저항 임피이던스를 제공하며 MOSFET의 게이트 및 소오스전극과 직렬로 접속되는 회로가 달레엠. 브라운등에 의한 미국특허번호 제4,227,098호로 제안되었다.

전류가 이경우 광방사 다이오드측의 입력단자로 흐를때 광기전성 출력이 광기전성 다이오드 어레이의 양끝단자에서 발생되며, 이 출력전압은 MOSFET의 게이트 및 소오스에 인가되어, MOSFET의 전류통가 전극에 접속된 출력단자간의 결과적인 MOSFET의 임피이던스는 현저히 다른값으로 변화된다. 즉 인핸스먼트형 MOSFET의 경우에 출력단자의 상태는 오프상태에서 온상태로 시프트된다.

이때 다이오드 어레이에 병렬로 접속된 저항은 MOSFET의 게이트 및 소오스에 누적된 정전전하를 방전하는 역할을 하며, 이저항이 존재하지 않는다고 가정하면 출력단의 상태는 광방사다이오드로의 입력전류가 방해될때 조차도 오프상태로 환원될 수 없다.

상기 미국특허에서는, 출력단자를 온상태로 하기 위하여 요구되는 최소입력전류를 감소시키기 위하여 저항값을 크게 하는 것이 필요한 반면, 저항값은 출력단자의 상태를 입력전류의 중지후에 오프상태를 하기 위해 필요한 시간을 단축시키기 위하여 작아야 하므로, 이 두 이율배반적인 기능을 동시에 만족시키기는 어려우며, 입력신호가 최소전류범위에 있을때 MOSFET의 게이트 및 소오스의 전류가 입력전류에 비례하여 변하여서 MOSFET의 전류통과전극에 접속된 출력단자의 MOSFET의 임피이던스가 어떤값을 취하여 단자의 상태가 온 및 오프상태를 조정하여 큰전력손실을 유발하고 소자에 피해를 가하는 문제점이 있었다.

더욱이 에드워드 티.로드리구에즈에 의한 미국특허번호 제4,390,790호에, 광방사다이오드에 광학적 접속된 광기전정 다이오드 어레이가 정상 ON형 접합 FET가 접속된 게이트 및 소오스에 대한 MOSFET와 직렬로 접속되며, 부가광기전성 다이오드 어레이가 저항을 통하여 이 접합 FET의 게이트 및 소오스에 접속된 반도체 스위칭회로가 기술되어 있다.

로드리구에즈에 따르면, MOSFET의 중간상태는 정상 ON형 접합 FET를 구동하기 위한 부가 다이오드 어레이의 설비에 의해 방지될 수 있지만, 접합 FET와 부가 다이오드 어레이를 조합한 회로배열은 또다른 문제를 발생시키며, 다이오드어레이에 대한 필요한 칩크기는 크게되고 광전도율은 악화되어 광감도 및 스위칭동작을 저하시킨다.

월리암 제이.자누트카에 의한 미국특허번호 제4,492,883호에서는 다른 P-채널형 FET가 MOSFET의 게이트와 소오스 사이에 접속되어 있고, 제너다이오드가 다른 FET의 게이트와 소오스사이, 즉 MOSFET의 게이트와 P-채널 FET의 게이트사이에 삽입되어 있고, 저항이 P-채널 FET의 게이트와 드레인 사이에 삽입되어 있는 MOSFET용 터닝-OFF회로가 기술되었다.

이러한 회로배열로서, MOSFET의 스위칭동작이 방지될 수 있다.

그러나 사용된 저항으로 인한 게이트 구동의 누설(leak)의 사용때문에, 고속터닝 ON동작에는 고전압 및 고전류 구동전원을 이용하는 것이 필요하며, 광기전성 다이오드 어레이에 접속함에 있어서, 회로에 불잇점을 제공할 수 있다.

더욱이, 본건에 있어서의 동일 양수인에게 양도된 시게오 아키야마에 의한 미국특허출원번호 26,994(혹은, 대응 서독출원 P37 08 812.2, 영국출원번호 8705701 혹은 한국출원번호 87-2703)에 있어서, MOSFET가 광방사 다이오드에 광학적 접속된 광기전성 다이오드 어레이에 직결 접속되어 있고, 임피이던스 소자가 광기전성 다이오드 어레이에 직렬 접속되어 있으며, 정상 ON형 구동트랜지스터는 광기전성 다이오드 어레이와 임피이던스 소자 사이의 접합점으로 제어전극에서 접속된 MOSFET에 접속되어 광기전성 다이오드 어레이의 광기전성 출력으로 인한 임피이던스 소자 양단에 발생된 전압에 의하여 고임피이던스 상태로 바이어스 되는 반도체 스위칭회로가 제안되었다.

이경우에 있어서, 온 및 오프상태간의 중간상태가 출력단자에 걸쳐 온상태를 되게 하기 위한 최소 필요입력 전류범위내에서, 출력단자 양단에 발생하는 것을 금지시킴이 가능하므로 동작속도가 전술한 세 미국특허의 기지의 반도체 스위칭회로의 온 및 오프속도에 비교할때 큰 범위로 가속화될 수 있다.

아키야마의 반도체 스위칭회로의 경우에 있어서, 기지의 회로에 나타난 여러 문제점들이 효과적으로 제거될 수 있지만 여전히 입력감도를 향상시켜야 하고 더 나은 고속도 스위칭동작을 이룩하기 위한 응답시간을 단축시켜야할 필요가 있는데, 이는 고임피이던스 상태로의 정상 ON형 구동 트랜지스터의 바이어싱에 공헌하며 큰 값을 갖는 저항과 같은 임피이던스 소자가 필요 최소전류를 전달할 수 있으며 즉 출력단자 양단의 상태를 온상태가 되게 하기 위한 일전류(working current)가 더 작게 되지만 오프상태에 도달하는 출력단자 상태를 갖는 필요응답시간은 비교적 연장되기 때문이며 반면, 더 작게 세트된 값은 반대현상을 유발하며 회로는 이러한 조건에 있어서 전술한 특허의 경우보다 훨씬 더 향상된 것을 보여준다.

본 발명의 목적은 감도에 있어 현저히 향상되고 동작속도가 빠른, 부가하여 출력단자의 상태가 거의 동작 전류인 입력전류의 범위내에서 온과 오프의 중간상태로 있게 되는것을 방지함에 의하여 순간적인 미소트리거링의 방지와 같은 아키야마의 회로에서 이루어진 효과도 갖는 반도체 스위칭회로를 제공하는 것이다.

본 발명에 의하면, 상기 목적은 광신호에 응답하여 광기전성 출력을 발생하기 위한 입력전류의 존재시에 광신호를 발생하는 광방사 소자에 광학적 접속된 다이오드 어레이, 광기전성 다이오드 어레이에 직렬 접속된 저항, 출력 FET의 게이트와 소오스 양단의 광기전성 출력의 인가에 따라 제1임피이던스 상태에서 제2임피이던스 상태로 되게 하기 위하여 광기전성 다이오드 어레이에 접속된 출력 FET, 및 다이오드 어레이에서의 관기전성 출력의 발생에 따른 저항 양단의 전압에 의하여 오프상태로 바이어스 될 수 있으며 드레인 및 소오스가 출력 FET의 게이트 및 소오스에 접속되고 게이트 및 소오스가 저항에 접속된 디프레션 모드 구동 FET로 구성되고, 디프레션 모드 출력 FET의 드레스-호올드 전압보다 높은 전압의 인가하에서 전도성 있으며, 이 전도에 의한 전류로서 출력 FET의 드레인과 소오스간에 방전이 일어나는 동안에 게이트와 소오스간에는 충전되는 정전압 전도 소자가 구동 FET의 게이트와 소오스 양단에 접속된 저항에 병렬 접속되는 것을 특징으로 하는 반도체 스위칭 회로가 제공되었다.

본 발명에 따른 상기 반도체 스위칭회로에서, 감도는 구동 FET의 게이트와 소오스간에 접속된 저항의 값을 세팅하여 향상될 수 있으며, 구동 FET는 작은 입력전류로서도 오프상태가 될 수 있고, 결과적으로 출력 FET의 게이트전위는 출력 FET를 오프상태로부터 온상태로 시프트하기 위하여 작은 광전류로서 높일 수 있다.

한편 출력 FET의 오프상태로부터 온상태로의 과도기동안에, 출력 FET의 드레인과 게이트간에 누적된 전하는 방전되며, 이에 따라 정전압 전도소자는 저항과 정전압 전도소자의 평행회로의 양단에서 발생된 전압에 의하여 전도성있게 되어서, 소자는 출력 FET의 드레인과 게이트간의 용량에 의존하는 방전전류를 고레벨로 유지하기 위하여 바이패스될 것이며, 출력 FET의 오프상태로부터 온상태로의 고속시프트는 보장될 수 있다.

본 발명의 기타목적 및 잇점이 첨부도면에 도시된 발명의 실시예를 참고로 하여 상세히 기술되는 후술하는 설명으로부터 명확해질 것이다.

본 발명이 첨부도면에 도시된 실시예를 참고로하여 서술될 것이지만, 본 발명이 이 실시예만 국한되는 것이 아니고 첨부한 특허청구범위의 취지내에서 다양한 설계수정이 가능함이 이해되어져야 할 것이다.

제1도에는 본 발명의 반도체 스위칭회로의 일실시예를 도시한 것이다.

회로(10)는 입력신호에 응하여 광신호를 발생하는 광 방사 다이오드와 같은 광방사 소자에 광학적 접속된 다이오드 어레이(11)를 포함하며, 다이오드 어레이(11)는 광방사 소자로부터의 광신호의 수신에 따라 광기전성 출력을 발생한다.

다이오드 어레이(11)는 출력 FET, 바람직하게는 MOSFET(12)의 게이트와 소오스 사이에 접속되며, 비교적 큰 저항값을 갖는 저항(13)도 어레이와 직렬로 접속된다.

출력 MOSFET(12)는 바람직하게는 N채널형 인핸스먼트 모드이며, 게이트 및 소오스간에 걸친 다이오드어레이(11)로부터의 광기전성 출력의 인가에 따라 제1임피이던스 상태로부터 제2 임피이던스 상태로 변화하게 하는 기능을 하며, 한편 출력 MOSFET(12)는 출력 MOSFET(12)의 임피이던스 상태에 따라 부하(16)를 제어하기 위하여 소오스측에 대해 드레인측이 포지티브 전위가 되도록 드레인 및 소오스가 한쌍의 출력단자(14, 15)를 통하여 전원(15)및 부하(16)에 접속된다.

한편 출력 MOSFET(12)의 게이트와 소오스에 걸처 디프레션 모드의 구동 FET(17)의 드레인 및 소오스가 접속되어 있으며, 한편 이 구동 FET(17)의 게이트와 소오스는 다이오드 어레이(11)에 직렬 접속된 저항(13)에 접속되었다.

구동 FET(17)로서, 바람직하게는 접합형 FET(JFET)가 광신호에 응한 다이오드 어레이(11)의 광기전성 출력의 발생에 따라서 저항(13)에 걸린 전압에 의하여 오프상태로 바이어스 되도록 사용된다.

본 발명에서 정전압 전도소자로서 유일하게 사용되는 제너다이오드(18)는 저항(13)아 병렬 접속되며, 이 제너다이오드(18)는 디프레션 모드 구동 FET(17)의 드레스호울드 전압보다 높은 항복전압을 갖도록 세트된다.

더욱이, 제너다이오드(18)는 구동 FET(17)의 드레스 호울드 전압보다 높은 전압이 인가될때 전도가 되도록 회로(10)에 삽입되어 있으며, 그러한 전도에 따른 제너전류가 출력 MOSFET(12)의 게이트와 소오스간에 충전을 하도록 극성을 갖는다.

본 실시예의 동작은 다음에 서술될 것이다.

먼저 본 발명의 이해를 돕기 위하여 제너라이오드(18)가 없는 상태에서의 동작에 관하여 설명하면, 광기전성 다이오드 어레이(11)에서 광신호를 수신하면, 다이오드 어레이(11)양단에 광기전성 전압이 발생되며, 광전류가 회로(10)를 통해 흐른다.

이 전류는 정산 ON구동 FET(17)를 통하여 비교적 큰 저항을 갖는 저항(13)으로 흐르며, 저항(13)에 걸린 전압이 구동 FET(17)의 드레스호울드 전압을 초과할때, 후자는 오프상태가 되며, 광전류는 출력 MOSFET(12)의 게이트 및 소오스를 통하여 흐르며, 출력 MOSFET(12)는 오프상태로부터 온상태로 시프트 된다.

이러한 순간적인 시프트 기간중에 MOSFET(12)의 드레인 전위는 소오스 전압 레벨로부터 제로레벨로 강하하여서 MOSFET(12)의 드레인과 게이트간의 전위차도 역시 크게 변하여서, 광기전성 다이오드 어레이(11)를 통하여 드레인과 소오스간에 누적된 전하를 방전하는 것이 필요하다.

이 방전에 요구되는 시간은 전회로(10)의 동작시간, 즉 응답시간의 대부분을 차지하는 것이다.

본예의 경우, 최소 필요입력전류, 혹은 다른말로써 MOSFET(12)의 출력단자(14, 14a)간의 상태를 온으로 하기 위한 일정류는 제2도에서 명백해지듯이 점차 감소되며, 구동 FET의 게이트와 소오스간에 접속된 저항(13)의 값은 증가된다.

즉, 제2도에서 그래프(k, l, m)는 구동 FET(17)의 게이트-소오스전압이 각각 -0.3V, -0.5V 및 -0.9V에 세트된 경우를 나타내며, 일전류(Ion)는 저항(13)의 저항이 증가됨에 따라 감소되어서 일전류는 -0.3V의 게이트-소오스 전압에서 1.0MΩ의 저항, -0.5V에서 1.7M 및 -0.9V에서 3.0MΩ에 대해 약 2mA일 수 있다.

저항(13)의 값이 다이오드 어레이(11)에 대한 광량 즉, 다이오드 어레이(11)에 광학적 접속된 광방사소자에 대한 입력전류(If)를 증가시키기 위하여 단지 더 증가될때 조차도, 한편 전회로(17)의 동작시간, 즉 응답시간(Ton)은 제3도에서 명백해지듯이 실질적인 변화가 없다.

즉, 제3도에서, 그래프(n, o, p)는 저항(13)의 저항이 0.3MΩ, 1MΩ 및 3MΩ에 세트된 경우에 해당하며, 저항(13)이 예를들면 3MΩ이상으로 만들어진 경우에 응답시간(Ton)은 600μse 이하가 될수 없다.

입력전류(If)가 500mA이상 되는 경우조차도 MOSFET(12)의 드레인과 소오스간에 누적된 전하의 방전에 따른 광전류는 저항(13)에 의해 현저히 제한된다.

본 발명의 실시예에서, 제너다이오드(18)는 저항(13)과 병렬로 접속되어 있으며, 큰값의 저항(13)이 사용될때 조차도, 저항(13) 및 제너다이오드(18)의 병렬회로 양단에 인가된 전압은 언급되어온 바와같이 MOSFET(12)가 오프상태에서 온상태로 되는 과도기에서의 출력 MOSFET(12)의 게이트와 드레인간의 전하의 방전에 따라 제너다이오드(18)의 항복전압을 초과하는 원인이 되며, 제너다이오드(18)는 이에 의하여 바이패스 기능을 수행하기 위하여 전도성있게 되며, 방전전류는 주로 제너다이오드(18)를 통해 흐르게 된다.

MOSFET(12)의 게이트와 드레인간에 누적된 전하의 방전 시간은 충분히 단축될 수 있으며, 그러한 특성은 제3도에서 선형그래프(q)에 의해 나타나며, 출력 MOSFET(12)의 온상태로의 고속동작은 저항(13)값이 크고 일전류가 작게 세트될때 조차도 보장될 수 있다.

출력 MOSFET(12)가 완전히 온상태로 시프트되는 경우에, MOSFET(12)의 드레인과 소오스간의 전하의 방전이 종료되며, 게이트 및 소오스간의 전하가 그 양단간의 전압을 상승하도록 수행되며, 저항(13)과 제너다이오드(18)의 병렬회로에 걸린 전압은 강하되어, 저항(13)의 전압강하는 작게되어 제너다이오드(18)의 항복전압 이하가 되며, 다음에 제너다이오드(18)는 비전도상태로 된다.

이후에, 작은 전류가 구동 FET(18)의 드레인과 소오스를 통해 흐르며 저항(13)의 존재로 인하여 구동 FET(17)는 고임피이던스 상태에서 유지될 수 있다.

한편 광기전성 다이오드 어레이(11)에 광학적 접속된 광방사 소자에 대한 입력전류가 소멸하고 따라서 어레이(11)가 더 이상 광신호를 수신하지 않을때, 다이오드 어레이(11)에서의 광기전성 출력의 발생은 중단되고 구동 FET(17)의 게이트와 소오스에 걸린 전압은 강하된다.

이에 의하여 구동 FET(17)는 온상태가 되고, 출력 MOSFET(12)의 게이트와 소오스간에 누적된 전하는 구동 FET(17)를 통하여 신속히 방전되어서, 출력 MOSFET(12)는 오프상태가 되어서 출력단자(14, 14a)도 역시 오프상태가 된다.

구동 FET(17)는 게이트와 소오스간에 누적된 전하가 저항(13)을 통하여 방전되는 동안, 구동 FET의 전극에 걸리는 용량은 출력 MOSFET(12)의 전극에 걸린 용량보다 훨씬 작으며, 이 전하방전에 요구되는 시간이 짧으므로 이 방전은 출력 MOSFET(12)의 고속동작에 실질적인 영향을 주기에는 효과적이지 못하다.

제4도는 참고로 하면, 제1도의 실시예의 동일회로 구성소자가 제1도의 동일부재 번호에 100을 더하여 나타난 본 발명에 따른 반도체 스위칭회로의 다른 실시예가 도시되어 있다.

본 실시예는 용도에서만 제1도와 상이하며, 정전압 전도 소자가 저항(113)과 병렬로 접속되어 있으며, 인핸스먼트 모드 FET(118)는 게이트와 소오스에 걸쳐 달락회로 되어 있다.

이 인핸스먼트 모드 FET(117)는 구동 FET(117)보다 높은 드레스호울드 전압이 제공되어 있으며. 저항(113) 및 구동 FET(117)의 게이트 및 소오스에 평행 접촉되어 있으며 출력 MOSFET(112)의 게이트와 소오스의 전하는 전도에 따른 드레인 전류와 더불어 이루어지도록 극성을 갖는다.

저항(113)과 인핸스먼트 모드 FET(118)의 병렬회로의 양단에 인가된 전압이 FET(118)의 드레인과 소오스간의 소정 드레스호울드 전압 이상으로 상승할때, FET의 드레인과 소오스간에는 전도상태가 되지만, 게이트와 드레인간의 단락회로 때문에, 인핸스먼트 모드 FET(118)가 제1도의 실시예에서의 제너다이오드(18)와 동일 기능을 수행할 수 있다.

이 실시예의 경우, 인핸스먼트 모드 FET(118)는 MOSFET(112) 및 구동 FET(117)와 유사한 구조를 갖고 있어서, 반도체 스위칭회로(110)가 단일칩으로의 라미네이션에 의하여 형성될때 특허 유리하며, 대량생산에 있어서 향상을 기할 수 있다.

제4도의 실시예의 반도체 스위칭회로(117)에서 기타 배열 및 동작은 제1도의 실시예의 것과 본질적으로 동일하다.

본 발명에서, 다양한 설계수정이 첨부된 청구범위의 취지내에서 가해질 수 있다.

예를들면, MOSFET는 출력 FET로서 사용된 것으로 기술된 반면에 스태틱 인덕션형 트랜지스터(SIT)등이 역시 이용될 수 있다.

디프레션 모드 구동 FET(17 혹은 117)로서 사용된 것으로 도시된 접합형 FET(JFET)대신에 디프레션 모드 MOSFET 혹은 스태틱 인덕션형 트랜지스터(SIT)가 역시 사용될 수 있다.

더욱이, 인핸스먼트 모드 N-채널형은 출력 MOSFET(12 혹은 112)로서 사용된 것으로 서술되었지만 P-체널형 흑은 디프레션 모드중 하나를 사용하는 것도 가능할 것이다.

서술된 것과 같은 배열을 갖는 본 발명의 반도체 스위치 회로에 따르면, 작은 입력전류로서 출력 FET의 온 및 오프동작이 이루어질 수 있고, 회로는 감도에 있어 효과적으로 향상될 수 있으며, 출력 FET의 게이트와 드레인에 걸리는 전하는 출력 FET가 온상태로 되는 과도기에 신속히 방전될 수 있으며, 이에 의하여 고속동작이 보장되어서 상기와 같은 종류의 반도체 스위칭회로의 상호 이율배반적인 기능이 동시에 얻어질 수 있다.

Claims (4)

- 상기 광신호에 응답하는 광기전성 출력을 발생하기 위한 입력전류의 존재시에 광신호를 발생하는 광방사소자에 광학적 접속된 다이오드 어레이, 상기 광기전성 다이오드 어레이와 직렬로 접속된 저항, 게이트 및 소오스에 대한 상기 광기전성 출력의 인가에 따라 제1 임피이던스 상태로부터 제2 임피이던스 상태로 되도록 상기광기전성 다이오드 어레이에 접속된 출력 FET, 드레인 및 소오스가 상기 출력 FET의 게이트 및 소오스에 접속되고 게이트 및 소오스가 상기 저항의 양단에 접속되고 광기전성 다이오드 어레이에서의 상기 광기전성 출력의 발생에 따라 저항 양단에 걸린 전압에 의하여 오프상태로 바이어스 될 수 있는 디프레션 모드의 구동 FET, 및 상기 디프레선 모드 구동 FET의 드레스호울드 전압보다 높은 전압의 인가에 따라 전도성 있게 되도록 상기 저항에 병렬로 접속되고 상기 전도에 따른 전도전류로서 게이트와 소오스간의 충전 및 출력 FET의 드레인과 게이트간의 방전에 기여하는 정전압 전도 소자로 구성되는 것을 특징으로 하는 반도체 스위칭회로.

- 제1항에 있어서, 상기 정전압 전도소자는 상기 구동 FET의 상기 드레스호울드 전압보다 높은 항복전압을 갖는 제너다이오드인 것을 특징으로 하는 반도체 스위칭회로.

- 제1항에 있어서, 상기 정전압 전도소자는 상기 구동 FET보다 높은 드레스 호울드 전압을 가지며 게이트와 드레인간이 단락회로인 인핸스먼트 모드 FET인 것을 특징으로 하는 반도체 스위칭회로.

- 제1항에 있어서, 상기 출력 FET는 MOSFET인 것을 특징으로 반도체 스위칭회로.

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP188272 | 1986-08-11 | ||

| JP18827286 | 1986-08-11 | ||

| JP61-188272 | 1986-08-11 | ||

| JP255023 | 1986-10-27 | ||

| JP61-255023 | 1986-10-27 | ||

| JP61255023A JPS63153916A (ja) | 1986-08-11 | 1986-10-27 | 半導体スイツチ回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR880003483A KR880003483A (ko) | 1988-05-17 |

| KR900005818B1 true KR900005818B1 (ko) | 1990-08-11 |

Family

ID=16220761

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019870008570A KR900005818B1 (ko) | 1986-08-11 | 1987-08-05 | 반도체 스위칭회로 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JPS63153916A (ko) |

| KR (1) | KR900005818B1 (ko) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2757438B2 (ja) * | 1989-03-17 | 1998-05-25 | 松下電工株式会社 | 光結合型リレー回路 |

| JPH0812993B2 (ja) * | 1990-10-26 | 1996-02-07 | 松下電工株式会社 | 半導体リレー回路 |

| JPH0812992B2 (ja) * | 1990-10-26 | 1996-02-07 | 松下電工株式会社 | 半導体リレー回路 |

| JPH03238918A (ja) * | 1990-02-15 | 1991-10-24 | Matsushita Electric Works Ltd | 半導体リレー回路 |

| US5138177A (en) * | 1991-03-26 | 1992-08-11 | At&T Bell Laboratories | Solid-state relay |

| JP2009147022A (ja) * | 2007-12-12 | 2009-07-02 | Toshiba Corp | 光半導体リレー |

| JP7357562B2 (ja) * | 2020-02-04 | 2023-10-06 | 日清紡マイクロデバイス株式会社 | 高周波スイッチ回路 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5629458B2 (ko) * | 1973-07-02 | 1981-07-08 | ||

| JPS5368066A (en) * | 1976-11-30 | 1978-06-17 | Hitachi Ltd | Semiconductor switch |

| JPS553259A (en) * | 1978-06-21 | 1980-01-11 | Fujitsu Ltd | Switching circuit |

| JPS5529972U (ko) * | 1978-08-16 | 1980-02-27 | ||

| US4492883A (en) * | 1982-06-21 | 1985-01-08 | Eaton Corporation | Unpowered fast gate turn-off FET |

| JPS61165210A (ja) * | 1985-01-17 | 1986-07-25 | Ishikawajima Harima Heavy Ind Co Ltd | 圧延機 |

| JPH0478210A (ja) * | 1990-07-18 | 1992-03-12 | Miharu Tsushin Kk | ノッチフィルター又はバンドエルミネートフィルターの周波数自動制御方法 |

-

1986

- 1986-10-27 JP JP61255023A patent/JPS63153916A/ja active Granted

-

1987

- 1987-08-05 KR KR1019870008570A patent/KR900005818B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| KR880003483A (ko) | 1988-05-17 |

| JPS63153916A (ja) | 1988-06-27 |

| JPH0481894B2 (ko) | 1992-12-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4801822A (en) | Semiconductor switching circuit | |

| US5057694A (en) | Optoelectronic relay circuit having charging path formed by a switching transistor and a rectifying diode | |

| US4039862A (en) | Level shift circuit | |

| US5004936A (en) | Non-loading output driver circuit | |

| US4695744A (en) | Level shift circuit including source follower output | |

| EP0168552A2 (en) | MOS transistor ciruit with breakdown protection | |

| KR920006014B1 (ko) | 입력버퍼 및 임계전압 증가방법 | |

| US5013926A (en) | Photocoupler apparatus capable of shortening switching time of output contact | |

| KR900004108A (ko) | 파워 mos 트랜지스터가 구비된 모놀리딕 쌍방향 스위치 | |

| US4811191A (en) | CMOS rectifier circuit | |

| KR950000320B1 (ko) | 반도체 릴레이회로 | |

| KR900005818B1 (ko) | 반도체 스위칭회로 | |

| US5278422A (en) | Normally open solid state relay with minimized response time of relay action upon being turned off | |

| US4296340A (en) | Initializing circuit for MOS integrated circuits | |

| US4677325A (en) | High voltage MOSFET switch | |

| EP0593588B1 (en) | Circuit protection arrangement | |

| US4612448A (en) | Electronic switch | |

| KR0132780B1 (ko) | 집적 논리 회로 | |

| US4837458A (en) | Flip-flop circuit | |

| US5847593A (en) | Voltage discharge circuit for a photovoltaic power source | |

| JP3258050B2 (ja) | 誘導性負荷用mosfetを備えた回路装置 | |

| US5095220A (en) | Circuit configuration for potential triggering of a field effect transistor | |

| JP3470488B2 (ja) | 半導体リレー回路 | |

| KR900001812B1 (ko) | 단락방지 버퍼회로 | |

| US4359654A (en) | Alternating polarity power supply control apparatus |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20060810 Year of fee payment: 17 |

|

| EXPY | Expiration of term |