KR900005313B1 - 세라믹기판표면을 요철화 하는 방법과 동 기판을 사용하여 인쇄회로기판을 제조하는 방법 - Google Patents

세라믹기판표면을 요철화 하는 방법과 동 기판을 사용하여 인쇄회로기판을 제조하는 방법 Download PDFInfo

- Publication number

- KR900005313B1 KR900005313B1 KR1019870012550A KR870012550A KR900005313B1 KR 900005313 B1 KR900005313 B1 KR 900005313B1 KR 1019870012550 A KR1019870012550 A KR 1019870012550A KR 870012550 A KR870012550 A KR 870012550A KR 900005313 B1 KR900005313 B1 KR 900005313B1

- Authority

- KR

- South Korea

- Prior art keywords

- bath

- substrate

- conductive layer

- ceramic substrate

- phosphoric acid

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/38—Improvement of the adhesion between the insulating substrate and the metal

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B41/00—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone

- C04B41/009—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone characterised by the material treated

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B41/00—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone

- C04B41/53—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone involving the removal of at least part of the materials of the treated article, e.g. etching, drying of hardened concrete

- C04B41/5338—Etching

- C04B41/5353—Wet etching, e.g. with etchants dissolved in organic solvents

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B41/00—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone

- C04B41/80—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone of only ceramics

- C04B41/91—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone of only ceramics involving the removal of part of the materials of the treated articles, e.g. etching

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C18/00—Chemical coating by decomposition of either liquid compounds or solutions of the coating forming compounds, without leaving reaction products of surface material in the coating; Contact plating

- C23C18/16—Chemical coating by decomposition of either liquid compounds or solutions of the coating forming compounds, without leaving reaction products of surface material in the coating; Contact plating by reduction or substitution, e.g. electroless plating

- C23C18/18—Pretreatment of the material to be coated

- C23C18/1851—Pretreatment of the material to be coated of surfaces of non-metallic or semiconducting in organic material

- C23C18/1862—Pretreatment of the material to be coated of surfaces of non-metallic or semiconducting in organic material by radiant energy

- C23C18/1865—Heat

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C18/00—Chemical coating by decomposition of either liquid compounds or solutions of the coating forming compounds, without leaving reaction products of surface material in the coating; Contact plating

- C23C18/16—Chemical coating by decomposition of either liquid compounds or solutions of the coating forming compounds, without leaving reaction products of surface material in the coating; Contact plating by reduction or substitution, e.g. electroless plating

- C23C18/18—Pretreatment of the material to be coated

- C23C18/1851—Pretreatment of the material to be coated of surfaces of non-metallic or semiconducting in organic material

- C23C18/1872—Pretreatment of the material to be coated of surfaces of non-metallic or semiconducting in organic material by chemical pretreatment

- C23C18/1886—Multistep pretreatment

- C23C18/1893—Multistep pretreatment with use of organic or inorganic compounds other than metals, first

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/38—Improvement of the adhesion between the insulating substrate and the metal

- H05K3/381—Improvement of the adhesion between the insulating substrate and the metal by special treatment of the substrate

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2111/00—Mortars, concrete or artificial stone or mixtures to prepare them, characterised by specific function, property or use

- C04B2111/00474—Uses not provided for elsewhere in C04B2111/00

- C04B2111/00844—Uses not provided for elsewhere in C04B2111/00 for electronic applications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/0306—Inorganic insulating substrates, e.g. ceramic, glass

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/11—Treatments characterised by their effect, e.g. heating, cooling, roughening

- H05K2203/1105—Heating or thermal processing not related to soldering, firing, curing or laminating, e.g. for shaping the substrate or during finish plating

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

- H05K3/18—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern using precipitation techniques to apply the conductive material

- H05K3/181—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern using precipitation techniques to apply the conductive material by electroless plating

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Ceramic Engineering (AREA)

- Organic Chemistry (AREA)

- Materials Engineering (AREA)

- Structural Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Inorganic Chemistry (AREA)

- Manufacturing Of Printed Wiring (AREA)

- Application Of Or Painting With Fluid Materials (AREA)

Abstract

내용 없음.

Description

제1도는 본 발명에 따라서 세라믹 인쇄회로기판을 제조하는 방법의 전체공정에 대한 블록 다이아그램.

제2도는 본 발명에 따라서 세라믹기판표면을 요철화(roughening)하는데 사용될 수 있는 한 기판처리공정을 설명하기 위한 블록 다이아그램.

제3도는 본 발명에 따라서 세라믹기판 표면을 요철화하는 방법에 있어서 인산욕 처리공정을 설명하기 위한 블록다이아그램.

제4도는 제3도의 처리공정을 실행하기 위한 시스템을 설명하기 위한 약 다이아그램.

제5도는 인산욕을 처리하는 온도와 기판표면의 조도에 대한 세 상이한 알루미나 기판간의 관계를 도시하는 그래프.

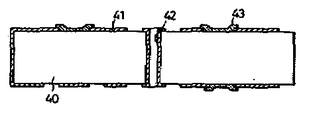

제6도는 도전층의 박리 강도를 설명하기 위한 약도.

제7도는 본 발명법과 종래법을 대비하여 기판표면의 조도와 인산으로 처리하는 시간과의 관계를 도시하는 그래프.

제8도는 본 발명에 따라 획득한 인쇄회로기판 표면의 단면도.

본 발명은 세라믹 기판표면을 요철화하는 방법과 이 요철화된 세라믹기판을 사용하여 인쇄회로기판을 제조하는 방법에 관한 것이다.

이 특징이 있는 방법에 따라 제조된 세라믹인쇄 회로기판은 전자부품으로서 사용되는 것이 통상적이다.

통상적인 세라믹 인쇄회로기판 또는 특별하게는 드로우호울을 가지고 있는 양면 인쇄회로기판을 제조하는 방법으로는 스크린 인쇄법에 의해 회로패턴을 형성하기 위해 세라믹기판의 양면상에 도전 페이스트를 도포하여 건조하고, 저항 페이스트(resistor paste)를 스크린 인쇄법으로써 세라믹기판의 양면상에 도포하여 건조하며, 그리고 전체 기판을 특정 분위기에서 소결하는 방법을 들 수 있다. 도전 페이스트로서, 상당히 고가인 Au, Ag-pd 합금등과 같은 귀금속으로 된 페이스트를 사용하는 것이 필수적이지만, 이 페이스트에 함유되어 있는 글래스 프리트로 인하여 솔더의 접착능이 악화된다.

전기도금 또는 스퍼터링, 증착등과 같은 기상공정을 통하여 얻을 수 있는 전도층은 불순물이 없으므로 순금속과 동등한 수준의 면적저항(sheet-resistance)을 갖는다고 알려졌으며 대량생산성 때문에 아직 가격은 낮다. 그러나 전기도금 또는 기상공정을 통해서 획득한 전도층은 기판과 전도층간의 물리적으로 얻을 수 있는 접착력이 일반적으로 불충분하다는 문제점이 수반된다. 기판표면을 요철화하고 그것을 메탈라이제이션시켜서 전도체의 접착력을 향상시키는 방법이 제안되었고, 이러한 처리를 이용했을때 고착효과(anchor effect)는 획득 되었다.

세라믹 기판을 용융알칼리 금속화합물로써 그 표면을 요철화한후 전도층을 도금법으로써 요철화된 표면상에 형성시키는 방법이 예컨대 마이클 에이.디루카(Michael A. Deluca et al)등의 미국특허번호 4,574,094호 및 4,604,299호에 개시되어 있다. 이와같은 방법으로써, 용융알칼리 금속화합물이 세라믹기판의 결정입을 부식시켜서 세라믹 표면이 균일하고 미세하게 요철화되지만, 표면 요철화를 기판의 깊이 방향으로 충분하게 달성할 수 있다는 것이 필요하다.

반면에 에스.지.스택넥커, 주니어(S.G. Slalnecker, Jr.)의 미국특허번호 3,296,012호와 일본특허공개공보 60-46976호에는, 세라믹 기판표면을 인산등과 같은 산으로써 요철화시켜서 거기에 전도층을 접착시키는 것이 고시되어있고, 여기에서 산으로 부식된 결정입계는 결정입이 떨어져 나가게하므로 요철화된 세라믹기판 표면이 얻어진다. 특히 인산을 사용하여 세라믹기판 표면은 고도의 효율적으로 그리고 균일하게 요철화될 수 있고, 충분하게 강력한 접착력이 현저하게 개량된 고착효과에 의해 달성될 수 있다. 그러나 이 방법은 다음과 같은 문제점을 수반한다. 세라믹 기판을 가열된 인산욕중에 침지시켜서 그 표면을 요철화할 때, 가열된 상태하에서 시간이 결과함에 따라 탈수 축합현상이 인산욕중에서 발생하므로, 이 욕의 점도는 높아지게 된다. 기판처리가 세라믹기판 표면에 대하여 반복될 때, 이 세라믹과 인산간의 반응생성물은 세라믹기판 표면상에 석출하게 되므로, 균일하고 미세하게 요철화된 표면이 더 이상 기대되지 않고 오히려 처리욕이 제품의 사용연한을 단축시킨다는 결점이 야기된다.

본 발명자들 즉 엔.야마구찌 등의 일본특허공개공보 번호 61-140195에는 인산에 의해 세라믹 기판표면을 요철화하는 방법이 개시되어 있다. 이 방법은 인산의 탈수축합현상으로 인하여 증대된 점도를 취급하기 위한 유효 수단을 제시하는데 있어서 아직 성공적이지 못하여 상기한 결점이 미해결된 채로 남아있다.

요철화된 세라믹기판 표면에 무전해도금에 의해 형성된 전도층이 제공되어 열처리될 때, 블리스터와 같은 변형이 세라믹기판과 전도층간에 발생하게 되어 생산수율이 악화되고, 이 블리스터가 발생하는 경향은 저항체(resistor)가 전도층의 회로 패턴상에서 소성(fired)됨에 따라 제공된 때 현저하게 된다.

본 발명의 제일 목적은 인산으로써 세라믹기판 표면을 고도의 효율적으로 또한 균일하게 요철화하는 방법을 제공하여, 현저한 고착효과에 의한 전도층의 강력한 접착력을 얻고, 표면이 요철화를 순조롭게 수행하기 위해 세라믹 기판과 인산과의 반응 생성물의 석출을 효과적으로 억제하고, 처리욕의 유효 사용수명을 연장시키는 것이다.

본 발명에 따라서, 표면이 요철화된 세라믹 기판상의 전도층의 회로패턴에 대해서 저항체를 소성하여 형성할 때 블리스터와 같은 변형이 발생을 얻게함으로써 양호한 세라믹인쇄기판을 제조할 수 있는 방법이 또한 제공된다.

본 발명에 따라, 상기한 목적은 세라믹기판 표면을 세라믹 인쇄회로기판을 제공하기 위해 그 표면상에 전도층을 형성하기전에 가열된 인산처리욕 또는 요철화 처리를 하는 욕(이하 "요철욕"이라함, roughening bath)에 기판을 침지시켜서 세라믹기판 표면을 요철화하는 방법을 제공함으로써 실현될 수 있고, 여기에서 인산욕의 일부분은 순차적으로 욕으로부터 방출되어 재생처리를 받는다.

또한, 블리스터발생이 효과적으로 억제된 양호한 세라믹 인쇄회로기판은 가열된 인산처리욕에 침지시킴으로써 요철화된 세라믹기판 표면상에 전도층을 형성할 때, 전도층에 간극(interstices)을 제공하고 순차적인 열처리를 불활성 기체 분위기에서 수행하는 방법에 의해 실현될 수 있다.

본 발명이 기타 목적과 이점은 본 발명의 실시예와 관련하여 상술된 본 발명의 설명으로부터 명백하게 될 것이다.

본 발명은 상이한 실시예와 관련하여 지금부터 설명될 것이지만, 본 발명은 개시된 실시예에 한정되는 것은 아니고, 오히려 본 발명의 범위내에서 가능한 모든 수정, 변경 및 상당 하는 장치가 포함된다.

본 발명에 따르는 세라믹 인쇄회로기판의 제조단계를 보여주는 제1도에 의하면, 최적의 세라믹기판을 먼저 준비하고, 표면을 탈지한 후, 세라믹기판을 가열된 인산욕이나 표면을 요철화하기 위한 요철욕에 침지하고, 침지중에 정상상태로 인산욕을 유지하기 위해 욕을 일부꺼내어 순차적으로 재생처리를 한다. 기판의 요철면위에 무전해 도금용 촉매를 제공하고, 무전해 도금을 하여 그 표면상에 회로패턴을 구성하는 전도층을 형성한다. 전도층을 형성할 때 간극을 제공하여 다공질로 만든다. 저항페이스트를 회로패턴의 전도층위에 가하고 불활성 기체 분위기내에서 소성시키면 세라믹 인쇄회로기판이 제조된다. 이 제조방법에 따르면, 전도층이 다공질로되어 특히 인쇄회로기판에서 저항체를 구성하는 저항페이스트를 소성하기 위해 열처리를 할 때 전도층 내에 생기는 어떤 기체도 외부로 방출될 수 있고 그럼으로써 생성된 기체에 기인하는 블리스터와 같은 변형의 어떤 생성도 막을 수 있다. 또한, 필요하다면 열처리가 저항체의 소성전에 수행되기도 한다.

다음, 세라믹 인쇄회로기판의 제조방법을 다음에 부분적으로 상술하기로 한다.

본 발명의 이해를 촉진하기 위해 세라믹기판 표면을 요철화하는 기술의 일정한 기본물질을 제2도와 관련하여 설명하기로 한다. 먼저 소결세라믹기판을 준비한다. 세라믹 재료로는, 알루미나, 포스테라이트, 스테아타이트, 지르콘, 뮬라이트, 코트디에라이트, 지르코니아, 티타니아 등과 같은 산화물로부터 선택된 재료를 사용하는 것이 바람직하나, 탄화물이나 질화물로부터 선택된 재료도 사용되며, 특히 알루미나 기판이 가장 적당하다. 알루미나 기판으로서는 Al2O3가 92 내지 99.5wt%, SiO2, MgO와 CaO가 총량의 0.5 내지 8wt%, 그리고 CaO가 0 내지 1wt%인 것이 또한 바람직하다. 표면요철화의 관점에서는, 사용될 기판은 표면입도가 1 내지 5㎛인 것이 또한 바람직하다. 그 다음에 세라믹 기판을 탈지한다. 탈지를 위해서는 알칼린세제, 아세톤, 톨루엔 또는 그 유사한 것을 사용하며 세라믹 기판표면이 유지나 먼지는 표면의 습윤화과정에서 제거한다. 탈지후, 기판을 세척하고 건조시켜서 처리시약을 실질적으로 완전히 제거한다. 이 경우, 세척은 수조에 기판을 침지하여 초음파 세척기로 수행하는 것이 바람직하고 건조는 건조기안에서 시행한다. 그 다음 기판을 인산처리욕에 침지하여 기판표면을 요철화한다. 이 표면요철화로써, 기판표면 위에 나중에 형성되는 전도층에 강력한 접착력을 제공하는 고착효과를 얻을 수 있다. 인산처리욕을 위해서는 기판표면에 산 잔류물이 남아있을 때라도 전도층의 접착력을 낮추지않고 화학적으로 도금된 금속에 아무런 영향도 주지않는 정인산, 피로인산과 메타인산으로 구성되는 군에서 적어도 하나를 선택하여 사용하는 것이 가장 적당하다. 처리욕은 250 내지 360℃ 범위의 온도로 유지되는 것이 바람직하다. 왜냐하면 250℃ 이하와 360℃ 이상에서는 인산의 분해와 축합의 급격한 증가로 인해 부식능력이 낮아지기 때문이다. 세라믹 기판표면의 요철정도는 인산욕에서의 침지시간에 따라 변화하지만 침지시간은 1 내지 30분, 가장 적당하게는 3내지 10분의 범위로 설정하는 것이 바람직하다. 특별히, 인산욕은 알루미늄농도를 1wt% 이하로 유지한다.

이경우, 알루미늄농도는 예를들어 형광 X-선 분석방법으로 측정하여 욕에 함유된 알루미늄의 감소된 농도로 나타낸다. 더우기 인산욕은 사량체 인산과의 사분자 중합으로 인한 사인산 이상의 다가인산의 농도가 5몰% 이하가 되도록 조절하는 것이 바람직하다.

또한, 온도를 전술한 범위로 유지하면서 알루미나 세라믹 기판의 표면을 요철화하기 위해 계속사용되는 인산욕은 점차 하얗게 혼탁된다. 이것은 알루미늄과 인산과의 반응생성물이 인산함량과 기판의 알루미나 함량과 반응하여 생성되고, 이 생성된 알루미늄인산염의 경정이 분리되어 요철화능력을 악화시키기 때문에, 혼탁이 발생하는 것을 방지하기 위해 인산욕을 조절하는 것이 또한 바람직하다.

한편, 360℃이하에서도 기판표면을 요철화하기 위해서 인산욕을 계속 가열하여 사용하면 욕에서 축합이 일어나 점차로 부식능력이 낮아지는 것으로 알려져 있다.

본 발명의 현저한 특징에 따르면, 인산욕을 정상상태로 유지하고 지속적으로 세라믹 기판표면을 균일하고 미세하게 요철화하기 위해 인산욕을 재생시키도록 인산욕을 순차적으로 처리하는 방법이 제공된다.

제3도와 4도와 관련하여 본 특징에 대해 보다 상세히 설명하면, 사용중인 인산처리욕을 예컨대 고점도용 화합펌프(12)에 의해서 요철욕(11)탱크의 하부에서 일부꺼내고, 이때 꺼낸 일부욕을 냉각기(13)에서 냉각시켜 예를들어, 250 내지 360℃로 유지되던 욕의 온도를 실온내지 100℃, 바람직하게는 70 내지 100℃ 범위의 온도로 내린다. 이렇게 냉각된 욕을 가수분해욕(14)으로 도입하여 교반기를 작동시키고 물을 첨가함으로써 바람직하게 가수분해한다. 이 가수분해욕(14)에 도입된 인산욕에서는 사인산보다 높은 오더의 축합된 인산이 정인산, 초성인산, 또는 3가 인산으로 분해 및 재생된다. 여기서, 물을 인산욕에 욕 1리터당 0.2 내지 0.4리터의 비율로 첨가하는 것이 바람직하다. 왜냐하면 물을 이 비율보다 적게 첨가하면 교반이 부드럽게 되지 않아서 필요한 가수분해시간이 연장되는 반면 이 비율을 초과하여 물을 첨가하면 다음공정에서 고온탈수가 일어나 시간을 낭비하게 된다.

가수분해된 인산욕을 인산과 세라믹기판간의 어떤 반응생성물도 여과해내는 여과기가 있는 예를들어, 화학펌프(15)를 통해 가수분해욕(14)으로 부터 꺼내서 인산함침욕(16)으로 도입하고, 여기에서 이와같이 가수분해되고 여과된 인산욕에 인산이 공급되므로 욕중의 인산양이 일정하도록 유지된다. 이 함침욕(16)에서 함유물이 적절하게 교반되도록 이 함침욕에도 교반기를 설치하는 것이 바람직하다. 이렇게 인산이 공급된 욕을 예를들어 화학펌프(17)에 의해서 고온탈수욕(18)으로 도입하여 탈수시킨다. 이경우 인산욕은 탈수욕(18)에서 160내지 240℃까지 가열되므로 수증기에 의한 거품효과를 활용하면서 탈수가 진행된다.

요철욕(11)으로 복귀되기전에, 필요하다면, 이렇게 인산이 공급되고 탈수된 인산욕, 즉 재생된 인산욕은 예열을 받게된다. 결국에는, 재생욕은 익류관(19)을 통해 고온탈수욕(18)에서 예열욕(20)까지 도입되고, 여기에서 재생욕은 가열되어 실질적으로 요철욕(11)의 온도와 같아지며, 그후 재생욕은 익류관(21)을 통해 요철욕(11)으로 복귀된다. 재생욕이 요철욕(11)으로 복귀되는 양은 요철욕(11)이 기저에서 욕을 꺼내는 양과 실질적으로 같도록 설정하고, 전체 재생시스템도 그렇게 고안한다.

처리인산욕의 전술한 순차적 재생순화과정이 세라믹 기판표면을 요철화하는 공정에 합동된 것은 정상적인 활성상태로 처리욕을 유지하는데 효과적이므로, 세라믹 기판에 대한 표면의 요철화가 일정하게 균일하고 양호하게 수행될 수 있다는 사실은 인정되어야 한다. 최적으로 요철화된 기판표면에 대하여, 세척과 건조작용을 수행하여 요철욕을 제거하고, 그후에 전도층을 무전해 도금이나 화학적도금, 스퍼터링, 진공증착 또는 그 유사한 공정으로써 형성한다. 전도층이 두꺼운 피막으로서 제공되는 것이 필요할때는, 전해도금을 중첩하여 시행하는 것이 바람직하다.

[실시예 1]

알루미나 함량이 96wt%인 알루미나 기판(조성은 Al2O3: 96wt%, CaO : 0.5wt%, MgO : 1.5wt%, SiO2: 2wt% : 평균표면입도는 3 내지 4㎛)을 제4도에 도시된 기판표면 요철화 시스템에 따라 표면요철화용 요철욕에 침지하였다. 요철욕(11)은 330℃까지 가열하였고, 가수분해욕(14)은 80℃로, 고온탈수욕(18)은 230℃로, 예열욕은 280℃로 유지하였고, 요철욕(11)에서 꺼내는 양, 즉, 재생욕의 복귀량은 20g/min로 설정하였다. 더우기, 알루미나 기판을 인산욕에 5분동안 침지하여 순차적으로 기판표면을 요철화하였다. 욕의 알루미늄농도는 0.4wt%로 유지하고 사인산 이상의 인산농도는 2몰%로 유지하였다.

이렇게 처리된 알루미나 기판의 감량(lost weight)과 표면조도를 측정하면, 감량은 변동량(fluctuation)이 ±0.05×10-3g/㎠인 평균 1.85×10-3g/㎠인 한편, 표면조도는 변동량이 ±1.0㎛이하인 평균 4.0㎛이었다. 구리전도층을 표면이 요철화된 알루미나 기판위에 공지의 무전해도금을 통해서 형성하고, 35㎛, 의 두꺼운 필름상 구리전도층을 형성하기 위해 구리 전해도금을 앞서 형성된 층위에 중첩하여 시행하였다.

또한, 요철욕(11)의 온도를 적절히 변화시키고, 알루미나 기판의 표면조도를 측정한 결과는 제5도의 곡선예1로 도시된 것과 같았다. 제6도에서 도시된 것처럼 알루미나 기판(30)에 대하여 수직방향으로 구리전도층(31)을 인상할 때의 박리강도를 측정한 결과 한정변동량이 ±5%이하인 평균 1.4㎏/㎝이었다.

다음으로 알루미나 기판들을 각각 5분동안 순차적으로 요철화하는 인산욕에 침지하고 모든 기판에 대해 얻어진 표면조도를 측정하여, 이런 기판들에 대한 각각의 결과를 욕의 사용중에 모든 기판의 침지시간의 경과에 따라서 제7도의 곡선 "예11"로서 플로트하였다. 종래의 배치공정을 통해 유사하게 거칠어진 알루미나 기판에 대한 측정결과를 도시하는 다른 곡선 "종래품"과 비교할 때 명백해지는 것처럼 양호한 표면조도가 장시간동안의 순차적인 욕의 사용중에 균일하게 이루어졌음을 알 수 있다.

[실시예 2]

알루미나 기판표면(조성은 Al2O3: 96wt%, CaO : 0.5wt%, MgO : 2wt%, SiO2: 1.5wt% : 평균표면입도는 2 내지 3㎛)의 요철화를 실시예 1에서와 같은 시스템을 통해 다음과 같이 시행했다. 즉, 인산욕(알루미늄농도는 0.7wt%로 사인산 이상의 인산농도는 1몰%로 유지함)은 300℃로 가열하고, 가수분해욕은 70℃로, 고온탈수욕은 240℃로, 그리고 예열욕은 260℃로 가열하고, 재생량은 10g/min으로 하고, 그리고 알루미나 함량이 96wt%인 알루미나 기판을 인산욕에서 6분동안 침지하였다. 동일한 측정을 한결과, 평균 감량은 변동량이 ±0.05×10-3g/㎠인 1.75×10-3g/㎠인 한편, 평균표면조도는 변동량이 ±1.0㎛이하인 3.5㎛이었다. 35㎛두께의 구리전도층을 실시예 1에서와 같은 방법으로 형성하고 이 층에 대한 박리강도를 측정한 결과는 한정 변동량이 ±5%이하인 평균 1.2㎏/㎝의 평균치를 보였다.

[실시예 3]

알루미나 함량이 92wt%인 알루미나 기판(조성은 Al2O3: 92wt%, CaO : 1wt%, MgO : 2wt%, SiO2: 5wt% : 평균 표면입도는 4 내지 5㎛)을 예열욕(20)의 생략을 제외하고는 실시예 1과 동일한 시스템을 통해서 표면요철화를 시행하였다. 즉, 요철욕(알루미늄 농도는 1.0wt%로 사인산 이상의 인산농도는 0몰%로 유지함)은 260℃까지 가열하고, 가수분해욕은 70℃로, 고온탈수욕은 230℃까지 가열하고, 재생량은 10g/min 그리고 침지시간은 4분으로 하였다. 실시예 1에서와 동일한 측정을 한 결과 평균감량은 오차가 ±0.1×10-3g/㎠인 2.35×10-3g/㎠이고 평균표면조도는 변동량이 ±1.0㎛인 5.0㎛이었다. 35㎛두께의 구리전도층을 실시예 1에서와 같은 방법으로 형성하고 박리강도를 측정한 결과는 한정 변동량이 ±5%이하인 평균 1.5㎏/㎝이었다. 인산욕의 온도를 적절히 변화시켜 생긴 표면조도의 변화를 알루미나 기판에 대해 측정한 결과를 제5도의 곡선 "예3"으로서 나타냈다.

[실시예 4]

표면입도가 4 내지 5㎛인 포스테라이트 기판을 인산욕 (사인산 이상의 인산농도는 실질적으로 제로임)의 온도를 270℃로 유지하는 것을 제외하고는 실시예 3에서와 동일한 조건하에서, 즉 예열욕(20)을 생략한 채 실시예 1과 동일한 시스템을 통해 표면을 요철화하였다. 실시예 1에서와 동일한 측정을 한 결과, 평균 감량은 변동량이 ±0.1×10-3g/㎠인 3.8×10-3g/㎠이었고 평균 표면조도는 변동량이 ±1.0㎛이하인 8㎛이었다.

[실시예 5]

알루미나 함량이 99.5wt%인 알루미나 기판(조성은 Al2O3: 99.5wt%, CaO : 0wt%, MgO : 0.3wt%, SiO2: 0.2wt% : 평균 표면입도는 1 내지 2㎛)을 실시예 1에서와 동일한 조건하에 동일한 시스템을 통해 표면을 요철화하여 동일한 측정을 한 결과, 평균 감량은 변동량이 ±0.05×10-3g/㎠인 1.3×10-3g/㎠인 한편 평균표면조도는 변동량이 ±0.5㎛ 이하인 2.5㎛이었다. 35㎛두께의 구리전도층을 실시예 1에서와 동일한 방법으로 형성하고 박리강도를 측정한 결과, 한정 변동량이 ±5%이하인 평균 1.2㎏/㎝이었다. 인산욕(알루미늄 농도는 0.4wt%로, 사인산 이상의 인산농도는 2몰%로 보유하고 있음)을 적절하게 온도를 변화시켜 얻어지는 표면조도를 측정하여 제5도의 곡선 "예5"로 표시되는 것과 같은 결과를 얻었다.

[비교실시예 1]

실시예 1에서와 같은 알루미나 함량이 96wt%인 알루미나 기판(조성은 Al2O3: 96wt%, CaO : 0.5wt%, MgO : 1.5wt%, SiO2: 2.0wt% : 평균 표면입도는 3 내지 4㎛)을 종래의 배치공정으로 요철욕으로써 표면을 요철화하고 330℃로 가열하여, 실시예 1에서와 동일한 측정을 한 결과를 실시예 제7도의 곡선 "종래품"으로서 나타냈다. 제7도는 처리시작시간으로부터 한시간이 경과할때까지 표면조도의 현저한 차이를 보여주고 있다. 35㎛두께의 구리전도층을 실시예 1에서와 같은 방법으로 형성하고, 박리강도를 측정한 결과를 측정 변동량이 최대 40%일 정도로 크며, 균일한 접착력을 얻을 수 없음을 보여주었다.

본 발명의 또 다른 현저한 특징에 따르면, 표면이 거칠어진 세라믹 기판에 대하여 전도층을 형성한 후 열처리시에 세라믹기판과 전도층 사이에 생기는 블리스터로 인해 수반되는 불량품을 방지하는 방법이 제공된다. 결국, 본 발명에 따르면, 세라믹 기판으로된 인쇄회로기판은 전도층은 형성한 후 열처리시에 내부에서 생성되는 기체가 통과해 빠져나갈 수 있는 충분한 간극을 갖출 수 있도록 제조된다. 이 제조방법은 이래에서 상세히 언급하기로 한다.

세라믹 기판표면을 요철화하고 요철화된 표면을 세척하고 건조하기위해 제2도와 관련하여 기술된 것과 동일한 공정들을 수행하였다. 나아가, 요철화된 표면을 세척하고 건조시킨 후에 세라믹 기판을 활성화 처리하였으므로 다음 공정으로서 무전해 도금을 수행할 때 표면은 촉매로서 작용할 것이다. 이경우 촉매는 SnCl2와 PdCl2를 쓰는 투-팩형의 감광활성화(sensitizing activation)공정이나 싱글-팩형 촉매촉진공정의 방법으로 준비하는 것이 바람직하지만, 다른 어떤 활성화공정도 촉매가 다음공정에서 무전해도금의 피막을 석출시킬 수 있는한 사용할 수 있다.

다음으로, 무전해도금을 활성처리된 세라믹 기판의 전체 표면에 대하여 형성하였다. 이 무전해도금 세라믹 기판에 대하여, 회로를 형성한 후, 저항 페이스트를 도포하고 결과적으로 저항을 이루는 저항체를 불활성 기체 분위기내에서 특히 바람직하게는 N2내에서 실시예 3. 이 소성중에, 도금층이 성장하는 동안 도금층으로 유입된 수분이나 도금욕의 성분일부에서 증발현상이 일어난다. 그러나, 널리 공지된 무전해 도금에서는 도금욕은 전기적 특성과 기계적특성을 향상시키는 첨가제를 함유하고 있고, 도금된 피막의 결정은 조밀하고 세라믹 기판 표면에 대하여 층구조를 나타내므로, 피막내부에서의 압력상승을 완화할 수 없다. 즉, 피막내에서의 증발에 의해 생성되는 기체성분은 외부로 방출될 수 없으므로 블리스터는 세라믹 기판과 전도층의 피막사이에서 발생하는 것 같다. 이 블리스터발생을 방지하기 위해서 본 발명에서는 무전해도금된 전도층자체에 증발에 의한 기체성분을 신속히 방출하는 기능을 부여하였다. 즉, 본 발명에 따라, 무전해도금 피막을 입상, 구상 및 주상조직중 적어도 하나의 조직으로 만들어 이 도금 피막을 다공성 조직으로 하여 기체가 통과될 수 있도록 하였다. 즉, 전도층을 두께방향으로 간극들이 있는 상태로 만들었다. 피막의 기공도의 상한은 다음 공정에서 회로 패턴을 형성하는데 사용하는 절연도료를 도포하거나 제거할 때 절연도료가 결정조직을 통해서 통과하지 않는 정도이어야 한다. 왜냐하면 이 도금피막을 통해서 침투되어 존재하는 절연도료는 기체발생원이 될 수 있을 뿐만 아니라, 회로 패턴의 형성이나 다른 전기적 특성에 나쁜 영향을 미치게 하기 때문이다.

다음으로 전해도금을 이와같이 형성되어 간극이 있는 피막을 가지고 있는 세라믹기판에 대해 수행하여 소정두께의 전도층을 얻는다. 소정두께의 전도층을 무전해도금을 통해 얻는 것이 가능할 때에는 물론 전해도금을 하는 추가공정은 생략될 수 있다. 어쨌든, 전해적으로 형성된 전도층은 일반적으로 고밀도이어서 열처리시 생성되는 기체성분이 이 층을 통해 통과할 수 없으므로 요구된 최소한으로 제한하는 것이 바람직하다. 이에 반하여 회로패턴이 현저히 복잡하기보다는 오히려 보다 간단할 때에는, 무전해 도금법보다 짧은 분해시간을 요하는 전해도금법을 전도층을 신속히 형성시키는데 사용하는 것이 유리하다. 왜냐하면 전도층을 첨가제를 사용하지 않고 보다 높은 전류밀도로써 다공질로 만들 수 있기 때문이다.

무전해도금법과 필요하다면 추가로 전해도금법으로 기판표면 전체에 다공질 전도층이 형성되어 있는 세라믹 기판에 대해 수행된 서브트랙티브 공정에 의한 인쇄회로 패턴의 부식형성에 대해 언급하기로 한다. 부식에 필요한 절연도료로서는 액체형, 건조필름형과 페이스트형의 절연도료중 어느것 하나를 필요한 라인폭에 따라 사용해야 한다. 부식후 기판을 세척하고, 절연도료를 제거하고, 다시 기판을 세척하고 건조시킨다.

세라믹 기판상에 인쇄회로 패턴을 형성하는 전도층의 기공도가 부적당할 때는 이 층을 열처리한다. 이 목적을 위해서는, 기판을 점차 온도가 상승되는 열원에 노출시키는데, 비교적 낮은 온도상승률인 200℃/h 이하가 바람직하다. 그리고 열처리를 불활성 기체 분위기에서 500 내지 1,083℃의 범위에서 수행하여 전도층으로 부터 기체 발생원을 방출한다. 전도층의 기공도가 불충분하더라도, 종래의 생성물에서처럼 심하게 조밀하지 않으므로, 기체 발생원을 이 층내에 블리스터를 형성하지 않고서도 제거할 수 있다.

위의 처리단계를 통해서, 소정의 회로패턴을 가지는 인쇄회로기판을 얻을 수 있다. 이러한 기공도를 갖춘 전도층은 전기적특성을 결코 악화시키지 않는다. 왜냐하면 구리피막은 전술한 열처리나 절연도료의 소성중에 재결정화되어 충분히 조밀해지기 때문이다. 나아가, 인쇄회로패턴을 형성시킬 때에 서브트랙티브 공정과는 다른 애디티브공정이나 세미-애디티브공정을 사용할 수도 있다.

[실시예 6]

알루미나 함량이 95wt%인 알루미나 기판들(조성은 Al2O3: 96wt%, CaO : 0.2wt%, MgO : 2wt%, SiO2: 1.8wt% : 평균 표면입도는 2 내지 3㎛)을 300 내지 360℃로 가열한 요철욕에, 2 내지 5분동안 침지하여 그 표면을 요철화하여, 5㎛와 10㎛의 각각 상이한 두개의 표면조도를 얻었다. 이것을 고온 세척하고, 초음파 세척기에서 추가로 세척한 다음, 촉매

Pd를 SnCl2와 PdCl2를 쓰는 투-팩형 감광활성화 공정으로써 기판표면에 공급하였다. 그 다음에 기본조성이 Cu, EDTA, NaOH와 HCHO이고 첨가제를 함유하지 않은 도금욕을 써서 기판에 대해 고속무전해 도금을 하였다. 이경우, Cu농도를 2.5g/lit로 일정하게 하면서 도금욕을 60℃로 유지하는 한편 HCHO와 NaOH 농도의 설정치를 변동시켜서 부하율을 1d㎡/lit로 일정하게 하면서 4개의 상이한 도금욕을 제조하여 도금을 수행해서 15㎛ 두께의 전도층을 얻었다. 이 도금중에 Cu, HCHO와 NaOH의 농도는 자동농도제어기로써 설정치로 유지하였다.

이렇게 도금한 알루미나 기판들을 충분히 온수 세척하고 다시 물로 세척한 다음 80 내지 100℃에서 10 내지 60분 동안 건조시켰다. 이렇게 해서 도금된 전도층이 있는 알루미나 기판위에 회로패턴을 감광액체 절연도료를 이용하는 인화법(photographic printing)으로써 형성하였다. 이경우, 기체 발생원을 제거하기 위한 열처리를 수행하지 않았다.

이렇게 제조한 인쇄회로 알루미나 기판을 질소분위기이고, 1,000℃의 머플로에 직접 장입하여 열처리를 10분동안 하였다. 블리스터 발생상태를 관찰하고 그 결과를 실시예 61에 나타냈다.

본실시예에서 얻은 구리전도층은 일반적으로 입자상 결정구조를 보이며, 전도층내로 침투된 절연도료는 관찰되지 않았다. 본 경우에서, 블리스터가 발생하지 않는 시료들은 석출률을 가속시키기 위해 pH와 HCHO 농도가 각각 12.5와 1.5g/lic로 비교적 높게 설정된 것이고, 보다 높은 표면조도를 나타내는 것이 보다 유리하다는 사실을 알 수 있었다.

시료에 대해 블리스터를 발생하지 않는 조건하에서 제조된 인쇄회로기판에 대하여 저항체를 질소 분위기 내에서 소성되는 형의 저항 페이스트로 스크린 공정(screen process)을 통해서 실제로 형성시키고 850 내지 900℃에서 소성시켜서 우수한 혼성회로 기판을 얻었다. 이 기판은 전도부 또는 전도부의 중첩부 및 사용한 저항 페이스트에서 블리스터가 발생하지 않았다. 더우기 850 내지 900℃에서의 열처리에 의해 구리피막은 재결정화되어 더 조밀해지고, 전도율은 열처리하기전의 인쇄회로기판과 대비하면 약 20%가 개선되었다.

[실시예 7]

알루미나 함량이 96wt%인 알루미나 기판들(조성은 Al2O3: 96wt%, CaO : 1wt%, MgO : 2wt%, SiO2: 1wt% : 평균 표면입도는 4 내지 5㎛)을 탈지하고, 포화수산화 나트륨 용액에 침지하고, 수산화 나트륨을 알루미나 기판표면에 도포하였다. 80 내지 100℃로 유지되는 건조기안에서 수분을 증발시키고, 건조된 기판을 400 내지 450℃로 유지되는 전기로내에서 10 내지 20분동안 열처리를 하며, 표면조도가 5㎛, 10㎛, 그리고 15㎛인 세개의 상이한 알루미나 기판을 얻었다. 이들 알루미나 기판들을 고온세척하고 초음파 세척기로 충분히 순차적으로 세척하여, 이렇게 세척한 기판들을 10% 염산용액으로 중화하였다.

다음, SnCl2와 PdCl2를 사용하는 투-팩형 감광활성화 공정으로써 기판표면에 촉매 Pd를 제공하고 고속무전해 도금을 수행하였다. 도금은 4개의 상이한 도금욕으로 수행되었다. 이 도금욕들은 급하였다. 이 도금욕들은 Cu, EDTA, NaOH와 HCHO의 기본조성이 실시예 6에서와 동일하고 다른 첨가제가 없는욕, 기본조성에 2, 2'-디피리딜 첨가제가 첨가된욕, 기본 조성에 시안화 나트륨 첨가제가 첨가된욕, 기본조성에 8-아세톡시-퀴놀린 첨가제가 첨가된 욕 등이었다. 도금피막을 성장시키기 위해서 욕을 만든후, 촉매가 제공된 알루미나 기판들을 도금욕에 침지하는 한편, 석출반응에 의해 기본조성의 농도가 자연히 감소되는 동안, 부하율은 0.5 내지 3㎡/lit로 온도는 50 내지 70℃로 설정하여 피막두께가 15㎛가 되도록 제조하였다. 피막두께는 도금욕이 초기농도로 회복된 후 기판을 이욕에 침지하는 조작을 반복함으로써 보다 증대되는데, 각 침지 시간은 2 내지 3시간으로 설정하였다. 기판을 침지하는 동안 욕을 적당히 교반하였다.

도금이 완료된 알루미나 기판들을 충분히 고온 세척하고 다시 물로 세척한 다음, 80 내지 100℃에서 10 내지 60분 동안 건조시켰다. 이들 도금된 전도층이 있는 알루미나 기판들에 대하여 감광약체 절연도료를 이용하여 회로패턴을 형성하였다. 여기에서 기체 발생원을 제거하기 위한 열처리는 수행하지 않았다.

실시예 6 통해 제조한 알루미나 인쇄회로판을 1,000℃로 유지되는 질소분위기의 머플로에 직접 장입하여 열처리를 10분동안 하였다. 이 열처리후, 이들 인쇄회로기판의 블리스터 발생상태를 관찰하여 그 결과를 표 2에 나타내었다.

본실시예 7을 통해 얻은 구리 전도층들은 블리스터의 발생을 수반하지 않으면서 모두 구형조직으로 나타났다. 절연도료가 전도층에 침투하는 것을 표면조도가 15㎛인 알루미나 기판위에 전도층이 도금된 경우에 볼 수 있었다.

절연도료가 전도층에 침투하지 않도록 하는 조건하에서 제조한 알루미나 인쇄회로기판들에 대해서 질소분위기에서 소성하는 형의 저항 페이스트의 필요한 패턴을 스크린 공정인쇄법으로 인쇄하고 850 내지 900℃의 범위에서 소성하여 우수한 혼성회로기판을 얻었다. 이 기판의 전도층, 전도층의 중첩부 및 절연도료에서 블리스터가 발생하지 않았다. 또한 이 기판은 전도층에 대한 기공도의 규정이 블리스터방지에 매우 기여한다는 사실을 보여준다.

[실시예 8]

실시예 6과 동일한 방법으로써 화학적으로 표면이 요철화되고 알루미나 함량이 96wt%인 알루미나 기판들(조성은 Al2O3: 96wt%, CaO : 0.1wt%, MgO : 2.1wt%, SiO2: 1.8wt% : 평균 표면입도는 2 내지 3㎛)에 싱글 팩형의 촉매촉진 공정에 의해 촉매 Pd를 제공하고, 고속무전해도금을 이들 기판들에 대해 수행하였는데, 이때 Cu, EDTA, HCHO 및 NaOH의 기본조성의 도금욕과 시안화물의 첨가제를 사용하였다. 도금하는 동안, Cu, HCHO와 NaOH의 초기농도는 설정치로 일정하게 유지하는 한편, 욕온은 50 내지 55℃로 유지하였다. 부하율은 1d㎡/lit로 설정하면서 15㎛ 두께의 전도층을 도금하였다.

이렇게 도금된 기판들을 온수로 충분히 세척한 다음 물로 세척하고, 80 내지 100℃에서 10 내지 60분 동안 건조시켰다. 회로패턴을 도금된 전도층이 있는 알루미나 기판위에 감광액체 절연도료를 사용하여 형성하였다. 기판들을 질소분위기내에서 50 내지 100℃/h의 속도로 온도를 올리고 500 내지 600℃에서 10 내지 60분 동안 유지하는 온도 조건하에서 열처리를 함으로써 기체 발생원을 방출하였다.

위의 공정을 통해 얻은 알루미나 인쇄회로 기판을 곧바로 1,000℃로 유지되는 질소분위기의 머플로에 장입하고 열처리를 10분동안한후, 인쇄회로 기판을 블리스터 발생상태의 관점에서 조사하였다. 이 조사의 결과를 표 3에 나타내었다.

본 실시예에서 얻은 구리전도층은 모두 주상의 결정 조직이었고 블리스터 발생이나 절연도료의 침투도 없었다. 질소분위기에서 소성하는 형의 저항 페이스트를 상기 공정을 통해 얻은 알루미나 인쇄회로기판상에 스크린 공정인쇄법으로 인쇄하고 850 내지 900℃의 온도에서 소성할 때 우수한 혼성회로기판을 얻을 수 있었으며, 이 기판은 전도부 또는 전도부와 저항 페이스트간의 중첩부에서 블리스터가 발생하지 않았다. 전도부에 대한 기공도의 규정조건은 블리스터 방지에 매우 기여하였다.

[비교실시예 2]

실시예 6실시예 6같은 두 상이한 방법을 통해서 화학적으로 표면을 요철화하고 알루미나함량이 96wt%인 알루미나 기판들(조성이 Al2O3: 96wt%, CaO : 1wt%, MgO : 2wt%, SiO2: 1wt% : 평균표면입도는 4 내지 5㎛)들에 투-팩형의 감광활성공정에 의해 촉매 Pd를 제공하고, 두 상이한 도금욕으로써 고속 무전해구리도금을 시행했다. 이 도금욕은 Cu, EDTA, NaOH 및 HCHO의 기본조성과 첨가제 2,2'-디피리딜로 구성된 도금욕과 상기 기본조성에 첨가제 8-아세톡시-퀴놀린으로 구성된 도금욕이었다. 부하율은 1d㎡/lit로 설정하였고 욕은 50 내지 70℃이었으며 도금피막층의 두께는 15㎛로 제조하였다. 도금하는 동안에 Cu, HCHO 및 NaOH의 각각의 농도는 자동농도제어기에 의해 초기 설정치로 일정하게 유지하였다.

이렇게 처리된 알루미나 기판을 온수로 충분히 세척한 후 다시 물로 세척하여 80 내지 100℃의 온도에서 10 내지 60분 동안 건조시켰다. 회로패턴을 감광성 절연도료로 인화법에 의해 도금전도층이 있는 알루미나기판상에 형성시켰다. 이때 기체발생원을 제거하기 위한 어떤 열처리도 시행하지 않았다.

상기 공정을 통해서 제조한 이들 알루미나 인쇄회로 기판을 1000℃로 유지되는 N2분위기의 머플로에 직접 장입하여 10분 동안 열처리하였다. 그다음 이들 기판에 대해 블리스터 발생여부를 관찰하여 그 결과를 표 4에 나타냈다.

이 비교실시예 2에서 얻어진 구리전도층은 모두 층상 결정조직을 나타냈으며, 전도층 내부에서 발생한 기체가 원활하게 방출되지 않아서 다수의 블리스터가 발생한 것을 보여주었다. 이 비교실시예의 기판에 대해서 실시예 8에서와 같이 동일한 열처리를 하였으나 온도상승률은 큰 범위까지 낮추었을 때도 기체는 블리스터 발생부로부터 방출될 수 없었다.

[표 I]

[표 II]

[표 III]

[표 IV]

본 발명의 또다른 특징에 따르면, 본 발명을 세라믹의 양면인쇄회로 기판에 적용할 때, 세라믹 기판의 야면 뿐만 아니라 드로우-호울의 원주벽을 동시에 요철화할 수 있으므로, 높은 접착력이 있는 드로우-호울을 양면인쇄회로 기판에 효율적으로 제공할 수 있다. 제8도와 관련하여 본 특징을 보다 상세히 언급하면, 제1도와 관련하여 설명된 것과 같은 다양한 형의 세라믹 기판을 기판의 양표면상에 회로간의 접속을 위한 드로우-호울이 있는 양면인쇄회로 기판으로서 제조하려할때는, 세라믹판으로 제조하기 위한 원판을 소결하기 전에 세라믹 원판을 펀칭하는 공정, 이미 소결된 세라믹 기판에 레이저 또는 드릴작업에 의해 소정위치에서 구멍을 뚫는 공정을 통해서 이 기판에 드로우 호울을 마련한다.

그다음 펀칭 또는 천공에 의한 호울이 있는 세라믹 기판을 제2도 또는 제3도에 관련하여 기술한 것처럼 요철욕에 침지하여 세라믹 기판의 표면 뿐만 아니라 드로우-호울의 원주벽을 요철화한다. 이 호울이 있는 기판을 도금하여 그 표면상에 전도층을 형성한다.

이때 전도층은 앞서의 실시예처럼 다공질이 되도록 하는 것이 바람직하다. 전도층을 형성할때에, 기판에 예컨대 감광활성 공정에 의해 촉매를 제공한후 절연도료를 소정 회로패턴에 대해 반대패턴으로 기판에 도포하고 이 기판을 무전해도금욕에 침지하여 도금을 시행한다.

도금에 있어서 소정두께의 전도층이 생성될때까지 전술한 태양과 같은 Cu, EDTA, NaOH 및 HCHO의 기본조성의 도금욕으로서 고속무전해도금을 시행하거나 또는 필요하다면 무전해도금을 통해서 미리 형성된 전도층에 전해도금을 부가적으로 시행하는 것이 가능하다.

외부의 양표면과 천공된 호울의 내주벽이 요철화된 세라믹 가판의 모든 요철면상에 도금된 전도층이 제공되고 드로우-호울(42)은 세라믹 기판(40)의 외부표면상에서 전도층(41)의 형성과 동시에 형성된다.

저항페이스트를 스크린인쇄법 등에 의해 전도층(41)의 회로패턴에 소정 패턴으로 도포한다. 도포된 페이스트를 건조 및 소성하여 저항체(43)를 형성한다. 저항페이스트로는 Sn, LaB6계 또는 Ta계 질화물 또는 SrRuO4의 저항재료와 Si, Ca, Al 등의 산화물을 함유하는 글래스 또는 유기 비이클과의 페이스트상 혼합물을 용도에 따라 선택하는 것이 적절하다. 건조 및 소성조건에 있어서, 저항페이스트를 50 내지 200℃의 온도에서 건조하고 예컨대 500 내지 1,083℃, 가장 적합하게는 600 내지 950℃의 온도에서 가열하는 것이 바람직하며, 이 온도는 저항페이스트의 글래스프리트가 세라믹 기판에서 융해되는 온도이다.

도포된 페이스트를 소성할때 전도층이 산화되는 것을 방지하기 위해 불활성기체 분위기에서 시행하는 것이 바람직하다. 저항체(43)의 저항치를 제어하는 것이 필요할때는 트리밍을 레이저 또는 샌드블라스팅방법에 의해 시행한다. 저항페이스트의 인쇄, 건조 및 소성을 반복하여 수행할때, 소정두께의 저항체를 형성시키는 것이 가능하므로, 저항치의 범위는 필요에 따라 폭넓게 선택할 수 있다.

[실시예 9]

알루미나 함량이 96wt%인 알루미나 기판(조성은 Al2O3: 96wt%, CaO : 0.5wt%, MgO : 1.5wt%, SiO2: 2wt% : 평균 표면입도는 3 내지 4㎛)을 레이저로 구멍을 뚫어 200 내지 400㎛ø의 드로우-호울을 마련했다.

기판을 330℃로 가열된 85wt%의 정인산의 표면요철욕에 5분간 침지하여 기판의 외부 표면 뿐만 아니라 천공된 호울의 내주벽을 요철화하였다. 이 요철화된 기판을 감광 및 활성욕(sensitizing and activation baths)에 순차적으로 침지하여 기판표면상에 팔라디움의 매개물을 핵생성시켰다.

도금절연도료(plating resist)를 인쇄패턴에 대해 반대 패턴으로 기판의 양표면상에 도포하고 실시예 7과 동일한 무전해도금을 시행하여 두께 10㎛의 구리 전도층을 얻었다.

이렇게해서 얻은 알루미나 기판의 양면상의 회로 기판의소정위치에 SrRuO4계의 저항페이스트를 스크린 인쇄법으로 도포하였다. 저항 페이스트가 도포된 알루미나 기판을 900℃로 유지되는 질소분위기에서 소성하여 저항체를 기판상에 형성시켰다. 저항체를 레이저 트림머로 최종적으로 트리밍하였으므로 저항체는 소정 저항치를 갖게되고, 알루미나 양면인쇄회로 기판을 얻었다.

이렇게 해서 얻은 인쇄회로 기판에서 시행한 박리시험(기판으로부터 전도층을 박리하는데 필요한 부하를 측정하는 시험, 예컨대 1.5㎟의 전도층표면에 수직적으로 납땜한 0.8㎜ø의 연구리선으로 박리한다)은 기판에 대한 접착력이 구리전도층과 저항체 모두에서 2.0 내지 3.0㎏/㎟일 정도로 높고, 드로우-호울의 신뢰성이 종래품의 경우보다 아주 높다는 사실을 입증한다.

[실시예 10]

순차적으로 소결된 상태에 있는 알루미나 함량이 96wt%인 알루미나 원판(조성은 Al2O3: 96wt%, CaO : 1wt%, MgO : 2wt%, SiO2: 1wt% : 평균 표면입도는 4 내지 5㎛)을 펀칭하여 호울을 마련하고 소결했다. 드로우-호울로서 이용될 200 내지 400㎛ 호울이 있는 소결된 알루미나 기판을 얻었다.

이 알루미나 기판을 실시예 9와 동일한 방식으로 표면을 요철화하고, 팔라디움핵생성을 시키고, 무전해도금욕에 침지하여 10㎛ 두께의 전도층을 형성했다. 실시예 9와 동일한 공정을 통해서 기판을 처리하여 알루미나의 양면인쇄회로 기판을 얻었다. 실시예 9의 것과 동일하게 양호한 결과를 얻었다.

[실시예 11]

지르코니아 기판을 사용한 것외에는 실시예 9와 동일한 공정을 통해서 지르코니아의 양면인쇄회로 기판을 얻었다. 이 실시예의 것과 동일하게 양호한 결과를 얻었다.

[실시예 12]

소결된 질화알루미늄기판을 사용하여 요철욕을 300℃로 가열한 것외에는 실시예 9와 동일한 공정을 통해서 질화알루미늄의 양면인쇄회로 기판을 얻었다. 이 실시예의 것과 동일하게 양호한 결과를 얻었다.

[실시예 13]

소결된 질화알루미늄기판을 사용하여 요철욕을 300℃로 가열한 것외에는 실시예 10와 동일한 공정을 통해서 질화알루미늄의 양면인쇄회로 기판을 얻었다. 이 실시예의 것과 동일게 양호한 결과를 얻었다.

[실시예 14]

실시예 9와 동일한 조성이고 알루미나 함량이 96wt%인 알루미나 기판을 330℃로 가열된 85wt%의 정인산의 요철욕에 5분간 침지하여 이 기판을 균일하게 요철화하였다. 이렇게 요철화된 기판을 충분히 세척 및 건조하고 감광 및 활성욕에 침지시킴으로써 파라디움매개물의 핵생성을 기판표면상에서 시행했다.

도금 절연도료를 회로패턴에 대해 반대패턴으로 알루미나 기판표면에 도포하고 10㎛ 두께의 전도층을 도포된 절연도료를 제거하면서 실시예 7과 동일한 무전해도금공정을 통해서 기판표면상에 형성시켰다.

알루미나 기판상에 이렇게 해서 얻은 회로패턴의 소정위치에 SrRuO4의 저항페이스트를 스크린인쇄법에 의해 도포하고, 900℃의 질소분위기에서 도포된 페이스트를 소성함으로써 저항체를 얻었다. 최종적으로 레이저트림머에 의해 트리밍하여 소정 저항치를 달성하여 알루미나 인쇄회로 기판을 얻었다.

Claims (33)

- 세라믹 기판표면을 요철화하는 방법에 있어서, 세라믹인쇄회로 기판을 준비하기 위하여 상기 세라믹 기판표면에 전도층을 형성하기 전에 세라믹 기판을 가열된 인산욕에 침지하는 공정과 욕을 순차적으로 재생하기 위하여 상기 인산욕의 일부를 순차적으로 꺼내는 공정으로 구성되는 것을 특징으로 하는 세라믹 기판 표면을 요철화하는 방법.

- 제1항에 있어서, 상기 인산욕을 250 내지 360℃ 범위의 온도로 유지하는 것을 특징으로 하는 방법.

- 제1항에 있어서, 상기 인산욕을 하얗게 혼탁해지지 않는 상태로 유지하는 것을 특징으로 하는 방법.

- 제1항에 있어서, 상기 세라믹 기판의 상기 침지공정은 3 내지 10분동안 시행하는 것을 특징으로 하는 방법.

- 제1항에 있어서, 상기 인산욕을 그것의 알루미늄 농도가 1wt% 이하로 유지되도록 하는 것을 특징으로 하는 방법.

- 제1항에 있어서, 상기 인산욕을 그것의 사인산이상의 인산농도가 5몰% 이하로 유지되도록 하는 것을 특징으로 하는 방법.

- 제1항에 있어서, 상기 재생공정은 고온 탈수공정을 포함하는 것을 특징으로 하는 방법.

- 제7항에 있어서, 상기 고온탈수공정을 실질적으로 160 내지 240℃ 범위의 온도에서 시행하는 것을 특징으로 하는 방법.

- 제7항에 있어서, 상기 재생공정은 가수분해 공정을 포함하는 것을 특징으로 하는 방법.

- 제9항에 있어서, 상기 가수분해공정을 실질적으로 실온 내지 100℃ 범위의 온욕으로 시행하는 것을 특징으로 하는 방법.

- 제1항에 있어서, 상기 재생공정은 상기 인산욕을 부분적으로 꺼내는 양과 재생욕이 상기 침지를 위한 욕으로 복귀되는 양이 실질적으로 동일하도록 유지함으로써 시행되는 것을 특징으로 하는 방법.

- 제1항에 있어서, 상기 재생공정은 부분적인 욕의꺼냄, 가수분해, 인산공급, 고온탈수 및 재생된 욕의 복귀등의 공정들로 순차적으로 수행되는 재순환 사이클로 시행되는 것을 특징으로 하는 방법.

- 제12항에 있어서, 상기 재순환 사이클은 상기 가수분해 공정전에 꺼낸 일부욕을 냉각시키는 공정을 포함하는 것을 특징으로 하는 방법.

- 제1항에 있어서, 상기 세라믹 기판은 입도가 1 내지 5㎛인 알루미나 기판인 것을 특징으로 하는 방법.

- 제1항에 있어서, 상기 세라믹 기판은 그것의 조성이 Al2O3는 92 내지 99.5wt%이고, CaO, MgO 및 SiO2의 합은 총량의 0.5 내지 8wt%이며, 그중 CaO는 0 내지 1WT%인 알루미나 기판인 것을 특징으로 하는 방법.

- 세라믹 인쇄회로 기판을 제조하는 방법에 있어서, 상기 세라믹인쇄회로 기판을 준비하기 위하여 세라믹 기판 상에 전도층을 형성하기 전에 상기 기판의 표면을 요철화하기 위해 상기 세라믹 기판을 표면요철화용 욕에 침지하는 공정과, 상기 요철화된 기판 표면상에 무전해도금법으로 상기 전도층을 형성하는 한편 이 층의 두께방향으로 소통되는 간극을 이 층에 제공하는 공정으로 구성되는 것을 특징으로 하는 세라믹인쇄회로 기판을 제조하는 방법.

- 제16항에 있어서, 상기 표면 요철화용욕은 인산으로 이루어지는 것을 특징으로 하는 방법.

- 제16항에 있어서, 상기 전도층이 있는 상기 세라믹 기판을 열처리하는 것을 특징으로 하는 방법.

- 제18항에 있어서, 상기 열처리는 실질적으로 500 내지 1,083℃ 범위에서 시행되는 것을 특징으로 하는 방법.

- 제16항에 있어서, 상기 전도층은 결정립이, 입상, 구상 및 주상의 결정조직중 적어도 하나를 갖도록 형성되는 것을 특징으로 하는 방법.

- 제17항에 있어서, 상기 표면 요철화용 욕은 실질적으로 250 내지 360℃ 범위로 가열되는 것을 특징으로 하는 방법.

- 제16항에 있어서, 상기 표면이 요철화된 세라믹 기판을 촉매로서 작용하도록 하기 위해 활성화처리하는 것을 특징으로 하는 방법.

- 제22항에 있어서, 상기 활성화처리는 투-팩형의 감광활성화 공정으로써 시행되는 것을 특징으로 하는 방법.

- 제22항에 있어서, 상기 활성화처리는 싱글-팩형의 촉매촉진공정으로써 시행되는 것을 특징으로 하는 방법.

- 제20항에 있어서, 상기 무전해도금은 기본조성이 Cu, EDTA, NaOH 및 HCHO인 도금욕으로 시행되는 것을 특징으로 하는 방법.

- 세라믹 양면인쇄회로 기판을 제조하는 방법에 있어서, 세라믹 인쇄회로 기판을 준비하기 위해 세라믹 기판상에 전도층을 형성하기 전에 상기 기판의 표면을 요철화하기 위해 상기 세라믹 기판을가열된 인산욕에 침지하는 공정과, 상기 요철화된 기판상에 무전해도금법을 시행하여 회로패턴을 형성하는 한편 상기 전도층에 이 층의 두께방향으로 소통되는 간극을 제공하는 공정과, 상기 회로패턴에 대하여 소정 저항체를 형성하는 공정으로 구성되는 것을 특징으로 하는 세라믹 양면인쇄회로 기판을 제조하는 방법.

- 제26항에 있어서, 상기 표면 요철화에 앞서, 드로우-호울로서 사용되는 호울을 상기 세라믹 기판에 형성하는 공정을 더 포함하는 것을 특징으로 하는 방법.

- 제26항에 있어서, 상기 저항체를 형성하는 상기 공정은 저항페이스트를 도포하고, 건조하고, 소성하는 공정들을 포함하는 것을 특징으로 하는 방법.

- 제28항에 있어서, 상기 저항페이스트의 소성은 불활성기체 분위기내에서 시행되는 것을 특징으로 하는 방법.

- 제29항에 있어서, 상기 저항페이스트의 소성은 질소분위기내에서 시행되는 것을 특징으로 하는 방법.

- 제30항에 있어서, 상기 저항페이스트의 소성은 페이스트내에 함유된 글래스프리트가 상기 기판표면으로 용융되는 온도에서 시행되는 것을 특징으로 하는 방법.

- 제26항에 있어서, 상기 저항페이스트의 소성은 실질적으로 500 내지 1,083℃ 범위에서 시행되는 것을 특징으로 하는 방법.

- 제26항에 있어서, 상기 전도층의 상기 회로패턴에 따라 형성된 상기 저항체는 소정 저항치로 트리밍되는 것을 특징으로 하는 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP61-266265 | 1986-11-08 | ||

| JP26626586A JPH0653253B2 (ja) | 1986-11-08 | 1986-11-08 | セラミツク基板の粗化法 |

| JP86-266265 | 1986-11-08 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR880006961A KR880006961A (ko) | 1988-07-25 |

| KR900005313B1 true KR900005313B1 (ko) | 1990-07-27 |

Family

ID=17428572

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019870012550A KR900005313B1 (ko) | 1986-11-08 | 1987-11-07 | 세라믹기판표면을 요철화 하는 방법과 동 기판을 사용하여 인쇄회로기판을 제조하는 방법 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US4865877A (ko) |

| JP (1) | JPH0653253B2 (ko) |

| KR (1) | KR900005313B1 (ko) |

| DE (1) | DE3737757A1 (ko) |

| GB (1) | GB2197622B (ko) |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE3833441A1 (de) * | 1988-10-01 | 1990-04-05 | Hoechst Ag | Verfahren zum metallisieren von aluminiumoxid-substraten |

| EP0455229B1 (en) * | 1990-05-02 | 1997-10-15 | Mitsubishi Materials Corporation | Ceramic substrate used for an electric or electronic circuit |

| US5622769A (en) * | 1993-02-12 | 1997-04-22 | Kabushiki Kaisha Toshiba | Ceramic circuit board having a thermal conductivity substrate |

| JPH06334301A (ja) * | 1993-05-19 | 1994-12-02 | Murata Mfg Co Ltd | スル−ホ−ル配線基板の加工方法 |

| JP3369665B2 (ja) * | 1993-08-27 | 2003-01-20 | 日本特殊陶業株式会社 | 半導体パッケージ用のセラミック製リッド基板およびセラミック製リッド |

| US6524645B1 (en) * | 1994-10-18 | 2003-02-25 | Agere Systems Inc. | Process for the electroless deposition of metal on a substrate |

| JP3246245B2 (ja) * | 1994-12-30 | 2002-01-15 | 株式会社村田製作所 | 抵抗体 |

| JPH09275091A (ja) * | 1996-04-03 | 1997-10-21 | Mitsubishi Electric Corp | 半導体窒化膜エッチング装置 |

| DE10147897C1 (de) * | 2001-09-28 | 2003-01-23 | Epcos Ag | Verfahren zum galvanischen Aufbringen von Kontaktschichten auf keramische Bauelemente |

| DE10221498A1 (de) * | 2002-05-14 | 2003-12-04 | Basf Ag | Kondensatoren hoher Energiedichte |

| US7682578B2 (en) | 2005-11-07 | 2010-03-23 | Geo2 Technologies, Inc. | Device for catalytically reducing exhaust |

| US7682577B2 (en) | 2005-11-07 | 2010-03-23 | Geo2 Technologies, Inc. | Catalytic exhaust device for simplified installation or replacement |

| US7722828B2 (en) | 2005-12-30 | 2010-05-25 | Geo2 Technologies, Inc. | Catalytic fibrous exhaust system and method for catalyzing an exhaust gas |

| TW201118940A (en) * | 2009-11-20 | 2011-06-01 | Holy Stone Entpr Co Ltd | Ceramic substrate manufacturing method |

| TW201118059A (en) * | 2009-11-20 | 2011-06-01 | Holy Stone Entpr Co Ltd | Manufacturing process for high precision ceramic substrate |

| US9090046B2 (en) * | 2012-04-16 | 2015-07-28 | Applied Materials, Inc. | Ceramic coated article and process for applying ceramic coating |

| DE102014212490A1 (de) * | 2014-06-27 | 2016-01-14 | Mahle International Gmbh | Peltierelement und Verfahren zur Herstellung |

| US20160005514A1 (en) * | 2014-07-07 | 2016-01-07 | Epistar Corporation | Method for forming electronic element |

| JP6867102B2 (ja) | 2014-10-22 | 2021-04-28 | Jx金属株式会社 | 銅放熱材、キャリア付銅箔、コネクタ、端子、積層体、シールド材、プリント配線板、金属加工部材、電子機器、及び、プリント配線板の製造方法 |

| US10529646B2 (en) | 2015-04-24 | 2020-01-07 | Amosense Co., Ltd. | Methods of manufacturing a ceramic substrate and ceramic substrates |

| KR102518645B1 (ko) * | 2015-05-06 | 2023-04-12 | 주식회사 아모센스 | 세라믹 기판 제조 방법 |

| KR102518646B1 (ko) * | 2015-05-11 | 2023-04-12 | 주식회사 아모센스 | 세라믹 기판 제조 방법 및 이 제조방법으로 제조된 세라믹 기판 |

| WO2021030122A1 (en) * | 2019-08-13 | 2021-02-18 | Corning Incorporated | Textured glass articles and methods of making the same |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3296012A (en) * | 1965-04-30 | 1967-01-03 | Corning Glass Works | Electroless copper plating on ceramic material |

| US4016525A (en) * | 1974-11-29 | 1977-04-05 | Sprague Electric Company | Glass containing resistor having a sub-micron metal film termination |

| JPS55117299A (en) * | 1979-03-05 | 1980-09-09 | Hitachi Ltd | Method of fabricating printed circuit board by noovoltage copper plating |

| US4316920A (en) * | 1980-07-03 | 1982-02-23 | Bell Telephone Laboratories, Incorporated | Thick film resistor circuits |

| JPS5770281A (en) * | 1980-10-20 | 1982-04-30 | Nisshin Steel Co Ltd | Zinc phosphate treatment of zinc hot dipping steel plate |

| JPS57149814A (en) * | 1981-03-09 | 1982-09-16 | Yoshio Aoyama | Recovering method for phosphoric acid |

| EP0109015A1 (en) * | 1982-11-15 | 1984-05-23 | Shipley Company Inc. | Electroless copper plating |

| US4574094A (en) * | 1983-06-09 | 1986-03-04 | Kollmorgen Technologies Corporation | Metallization of ceramics |

| US4604299A (en) * | 1983-06-09 | 1986-08-05 | Kollmorgen Technologies Corporation | Metallization of ceramics |

| US4563217A (en) * | 1983-07-25 | 1986-01-07 | Hitachi, Ltd. | Electroless copper plating solution |

| US4448804A (en) * | 1983-10-11 | 1984-05-15 | International Business Machines Corporation | Method for selective electroless plating of copper onto a non-conductive substrate surface |

| US4666744A (en) * | 1984-05-10 | 1987-05-19 | Kollmorgen Technologies Corporation | Process for avoiding blister formation in electroless metallization of ceramic substrates |

| JPS61140195A (ja) * | 1984-12-12 | 1986-06-27 | 松下電工株式会社 | セラミツク配線基板の製法 |

| NL8500474A (nl) * | 1985-02-20 | 1986-09-16 | Philips Nv | Werkwijze voor het continu regenereren van een stroomloos metalliseringsbad en inrichting voor toepassing van de werkwijze. |

| US4604229A (en) * | 1985-03-20 | 1986-08-05 | Ferrofluidics Corporation | Electrically conductive ferrofluid compositions and method of preparing and using same |

| US4696851A (en) * | 1985-03-25 | 1987-09-29 | Olin Corporation | Hybrid and multi-layer circuitry |

| US4684512A (en) * | 1986-08-25 | 1987-08-04 | Stauffer Chemical Company | Phosphate recovery from wet phosphoric acid purification process |

| JPH0646976A (ja) * | 1992-07-31 | 1994-02-22 | Sanyo Electric Co Ltd | 電気掃除機 |

-

1986

- 1986-11-08 JP JP26626586A patent/JPH0653253B2/ja not_active Expired - Lifetime

-

1987

- 1987-10-27 GB GB8725089A patent/GB2197622B/en not_active Expired - Lifetime

- 1987-10-27 US US07/113,125 patent/US4865877A/en not_active Expired - Lifetime

- 1987-11-06 DE DE19873737757 patent/DE3737757A1/de active Granted

- 1987-11-07 KR KR1019870012550A patent/KR900005313B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| US4865877A (en) | 1989-09-12 |

| DE3737757A1 (de) | 1988-05-19 |

| JPS63119878A (ja) | 1988-05-24 |

| GB2197622B (en) | 1990-10-17 |

| KR880006961A (ko) | 1988-07-25 |

| JPH0653253B2 (ja) | 1994-07-20 |

| GB2197622A (en) | 1988-05-25 |

| GB8725089D0 (en) | 1987-12-02 |

| DE3737757C2 (ko) | 1990-06-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR900005313B1 (ko) | 세라믹기판표면을 요철화 하는 방법과 동 기판을 사용하여 인쇄회로기판을 제조하는 방법 | |

| US5235139A (en) | Method for fabricating printed circuits | |

| US4913784A (en) | Process for metallizing a ceramic substrate | |

| EP0240268B1 (en) | Process for metallizing glass surface | |

| JPH05251849A (ja) | 銅メタライズドセラミック基板の製造方法 | |

| JPH09184076A (ja) | 窒化アルミニウムメタライズ基板の製造方法 | |

| US5419829A (en) | Electroplating process | |

| US4842899A (en) | Process for forming metallic film on inorganic material | |

| JPH07243085A (ja) | 金属被覆ポリイミド基板の製造方法 | |

| JPS61151081A (ja) | セラミツク配線基板の製法 | |

| US4888208A (en) | Ceramic substrate for printed circuits and production thereof | |

| JPH0337319B2 (ko) | ||

| DE3744747C2 (en) | Ceramic substrates with chemically roughened surfaces | |

| JPH01164786A (ja) | 導体層付セラミック基板とその製法 | |

| EP0252941A1 (en) | Fabrication of electrical conductor by augmentation replacement process | |

| JPH0533556B2 (ko) | ||

| JPH0891969A (ja) | セラミック基材へのNiメタライズ法 | |

| JP3152090B2 (ja) | セラミック配線板の製造方法 | |

| JP3152089B2 (ja) | セラミック配線板の製法 | |

| JPH0434625B2 (ko) | ||

| JPS61159792A (ja) | セラミツク配線基板の製法 | |

| EP0185967A2 (en) | Process for avoiding blister formation in electroless metallization of ceramic substrates | |

| JPS6311675A (ja) | アルミナ基板への無電解めつき方法 | |

| EP0254201A1 (en) | Method of metallizing ceramic substrates | |

| JP3203771B2 (ja) | 銅メタライズドセラミック基板の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20030723 Year of fee payment: 14 |

|

| LAPS | Lapse due to unpaid annual fee |