KR20190093576A - 전도성 특징부를 에칭하는 방법 및 관련 디바이스와 시스템 - Google Patents

전도성 특징부를 에칭하는 방법 및 관련 디바이스와 시스템 Download PDFInfo

- Publication number

- KR20190093576A KR20190093576A KR1020197016384A KR20197016384A KR20190093576A KR 20190093576 A KR20190093576 A KR 20190093576A KR 1020197016384 A KR1020197016384 A KR 1020197016384A KR 20197016384 A KR20197016384 A KR 20197016384A KR 20190093576 A KR20190093576 A KR 20190093576A

- Authority

- KR

- South Korea

- Prior art keywords

- layer

- etch

- substrate

- conductive

- corrosion resistant

- Prior art date

Links

- 238000000034 method Methods 0.000 title claims abstract description 147

- 238000005530 etching Methods 0.000 title claims description 98

- 239000000463 material Substances 0.000 claims abstract description 209

- 239000000758 substrate Substances 0.000 claims abstract description 199

- 238000005260 corrosion Methods 0.000 claims abstract description 123

- 230000007797 corrosion Effects 0.000 claims abstract description 121

- 230000008569 process Effects 0.000 claims abstract description 102

- 238000000151 deposition Methods 0.000 claims abstract description 50

- 239000004020 conductor Substances 0.000 claims abstract description 46

- 238000004519 manufacturing process Methods 0.000 claims abstract description 23

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 87

- 229910052802 copper Inorganic materials 0.000 claims description 84

- 239000010949 copper Substances 0.000 claims description 84

- 239000007788 liquid Substances 0.000 claims description 56

- 238000000576 coating method Methods 0.000 claims description 49

- 239000011248 coating agent Substances 0.000 claims description 42

- 238000007641 inkjet printing Methods 0.000 claims description 23

- 229910052751 metal Inorganic materials 0.000 claims description 22

- 239000002184 metal Substances 0.000 claims description 22

- 229920000642 polymer Polymers 0.000 claims description 21

- 230000008021 deposition Effects 0.000 claims description 18

- 238000012545 processing Methods 0.000 claims description 15

- 238000003475 lamination Methods 0.000 claims description 10

- 238000004528 spin coating Methods 0.000 claims description 9

- 239000011368 organic material Substances 0.000 claims description 8

- 238000001039 wet etching Methods 0.000 claims description 8

- 238000007764 slot die coating Methods 0.000 claims description 5

- 239000002262 Schiff base Substances 0.000 claims description 2

- 150000004753 Schiff bases Chemical class 0.000 claims description 2

- 150000001413 amino acids Chemical class 0.000 claims description 2

- 230000001678 irradiating effect Effects 0.000 claims 2

- 239000010410 layer Substances 0.000 description 467

- 238000000059 patterning Methods 0.000 description 103

- 239000000203 mixture Substances 0.000 description 97

- 239000000976 ink Substances 0.000 description 85

- DNIAPMSPPWPWGF-UHFFFAOYSA-N Propylene glycol Chemical compound CC(O)CO DNIAPMSPPWPWGF-UHFFFAOYSA-N 0.000 description 54

- 238000006243 chemical reaction Methods 0.000 description 53

- 239000000243 solution Substances 0.000 description 45

- 239000007864 aqueous solution Substances 0.000 description 28

- BDERNNFJNOPAEC-UHFFFAOYSA-N propan-1-ol Chemical compound CCCO BDERNNFJNOPAEC-UHFFFAOYSA-N 0.000 description 26

- 230000000670 limiting effect Effects 0.000 description 22

- 238000001035 drying Methods 0.000 description 19

- 238000007639 printing Methods 0.000 description 19

- 229920002873 Polyethylenimine Polymers 0.000 description 16

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 16

- 230000003287 optical effect Effects 0.000 description 15

- 239000000126 substance Substances 0.000 description 14

- 230000015572 biosynthetic process Effects 0.000 description 13

- 230000002829 reductive effect Effects 0.000 description 12

- 150000003839 salts Chemical group 0.000 description 12

- 230000004913 activation Effects 0.000 description 11

- 238000009792 diffusion process Methods 0.000 description 11

- 239000004094 surface-active agent Substances 0.000 description 11

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 10

- 229920006318 anionic polymer Polymers 0.000 description 9

- -1 copper salt Chemical class 0.000 description 9

- 239000013078 crystal Substances 0.000 description 9

- 238000005507 spraying Methods 0.000 description 9

- 238000012546 transfer Methods 0.000 description 9

- 125000000129 anionic group Chemical group 0.000 description 8

- 125000002091 cationic group Chemical group 0.000 description 8

- 239000000839 emulsion Substances 0.000 description 8

- 150000001412 amines Chemical class 0.000 description 7

- CBTVGIZVANVGBH-UHFFFAOYSA-N aminomethyl propanol Chemical compound CC(C)(N)CO CBTVGIZVANVGBH-UHFFFAOYSA-N 0.000 description 7

- 150000001768 cations Chemical group 0.000 description 7

- 239000002245 particle Substances 0.000 description 7

- 229920005792 styrene-acrylic resin Polymers 0.000 description 7

- HEMHJVSKTPXQMS-UHFFFAOYSA-M Sodium hydroxide Chemical compound [OH-].[Na+] HEMHJVSKTPXQMS-UHFFFAOYSA-M 0.000 description 6

- 150000001450 anions Chemical group 0.000 description 6

- KRKNYBCHXYNGOX-UHFFFAOYSA-N citric acid Chemical compound OC(=O)CC(O)(C(O)=O)CC(O)=O KRKNYBCHXYNGOX-UHFFFAOYSA-N 0.000 description 6

- 239000011347 resin Substances 0.000 description 6

- 229920005989 resin Polymers 0.000 description 6

- 238000007650 screen-printing Methods 0.000 description 6

- 239000002253 acid Substances 0.000 description 5

- 239000003795 chemical substances by application Substances 0.000 description 5

- 238000011161 development Methods 0.000 description 5

- 230000003993 interaction Effects 0.000 description 5

- 230000007246 mechanism Effects 0.000 description 5

- 230000002265 prevention Effects 0.000 description 5

- 239000000376 reactant Substances 0.000 description 5

- 239000007787 solid Substances 0.000 description 5

- 239000002699 waste material Substances 0.000 description 5

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 4

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 4

- 229920005692 JONCRYL® Polymers 0.000 description 4

- 230000009471 action Effects 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 238000004140 cleaning Methods 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 239000012777 electrically insulating material Substances 0.000 description 4

- 150000003071 polychlorinated biphenyls Chemical class 0.000 description 4

- 230000009467 reduction Effects 0.000 description 4

- 239000011701 zinc Substances 0.000 description 4

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 3

- 229920000178 Acrylic resin Polymers 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 3

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 3

- 229910019142 PO4 Inorganic materials 0.000 description 3

- 230000002378 acidificating effect Effects 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 239000002585 base Substances 0.000 description 3

- 229910052791 calcium Inorganic materials 0.000 description 3

- 239000011575 calcium Substances 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 230000000052 comparative effect Effects 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- ORTQZVOHEJQUHG-UHFFFAOYSA-L copper(II) chloride Chemical compound Cl[Cu]Cl ORTQZVOHEJQUHG-UHFFFAOYSA-L 0.000 description 3

- 238000003618 dip coating Methods 0.000 description 3

- 239000006185 dispersion Substances 0.000 description 3

- 238000004090 dissolution Methods 0.000 description 3

- 239000012530 fluid Substances 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 238000007646 gravure printing Methods 0.000 description 3

- IXCSERBJSXMMFS-UHFFFAOYSA-N hcl hcl Chemical compound Cl.Cl IXCSERBJSXMMFS-UHFFFAOYSA-N 0.000 description 3

- 229920000140 heteropolymer Polymers 0.000 description 3

- 229910010272 inorganic material Inorganic materials 0.000 description 3

- 229910052749 magnesium Inorganic materials 0.000 description 3

- 239000011777 magnesium Substances 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 238000001000 micrograph Methods 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 238000005240 physical vapour deposition Methods 0.000 description 3

- 230000004044 response Effects 0.000 description 3

- 159000000000 sodium salts Chemical group 0.000 description 3

- 150000003457 sulfones Chemical class 0.000 description 3

- 239000000080 wetting agent Substances 0.000 description 3

- 229910052725 zinc Inorganic materials 0.000 description 3

- 239000004593 Epoxy Substances 0.000 description 2

- 229910021578 Iron(III) chloride Inorganic materials 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- 239000000654 additive Substances 0.000 description 2

- 230000000996 additive effect Effects 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- QGZKDVFQNNGYKY-UHFFFAOYSA-O ammonium group Chemical group [NH4+] QGZKDVFQNNGYKY-UHFFFAOYSA-O 0.000 description 2

- ROOXNKNUYICQNP-UHFFFAOYSA-N ammonium persulfate Chemical compound [NH4+].[NH4+].[O-]S(=O)(=O)OOS([O-])(=O)=O ROOXNKNUYICQNP-UHFFFAOYSA-N 0.000 description 2

- 150000001767 cationic compounds Chemical class 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 239000011889 copper foil Substances 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 239000004744 fabric Substances 0.000 description 2

- 238000009472 formulation Methods 0.000 description 2

- 239000003365 glass fiber Substances 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 150000002466 imines Chemical class 0.000 description 2

- 238000007654 immersion Methods 0.000 description 2

- 230000003100 immobilizing effect Effects 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 230000002401 inhibitory effect Effects 0.000 description 2

- 229910001411 inorganic cation Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- RBTARNINKXHZNM-UHFFFAOYSA-K iron trichloride Chemical compound Cl[Fe](Cl)Cl RBTARNINKXHZNM-UHFFFAOYSA-K 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 229910001092 metal group alloy Inorganic materials 0.000 description 2

- 230000005012 migration Effects 0.000 description 2

- 238000013508 migration Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 150000002894 organic compounds Chemical class 0.000 description 2

- JRKICGRDRMAZLK-UHFFFAOYSA-L peroxydisulfate Chemical compound [O-]S(=O)(=O)OOS([O-])(=O)=O JRKICGRDRMAZLK-UHFFFAOYSA-L 0.000 description 2

- 239000010452 phosphate Substances 0.000 description 2

- 235000021317 phosphate Nutrition 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 239000002096 quantum dot Substances 0.000 description 2

- 239000011734 sodium Substances 0.000 description 2

- 239000007921 spray Substances 0.000 description 2

- 230000001960 triggered effect Effects 0.000 description 2

- 238000005406 washing Methods 0.000 description 2

- 238000009736 wetting Methods 0.000 description 2

- GDTSJMKGXGJFGQ-UHFFFAOYSA-N 3,7-dioxido-2,4,6,8,9-pentaoxa-1,3,5,7-tetraborabicyclo[3.3.1]nonane Chemical compound O1B([O-])OB2OB([O-])OB1O2 GDTSJMKGXGJFGQ-UHFFFAOYSA-N 0.000 description 1

- FLCAEMBIQVZWIF-UHFFFAOYSA-N 6-(dimethylamino)-2-methylhex-2-enamide Chemical compound CN(C)CCCC=C(C)C(N)=O FLCAEMBIQVZWIF-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-M Acrylate Chemical compound [O-]C(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-M 0.000 description 1

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- 229910001020 Au alloy Inorganic materials 0.000 description 1

- 229910021591 Copper(I) chloride Inorganic materials 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- WHNWPMSKXPGLAX-UHFFFAOYSA-N N-Vinyl-2-pyrrolidone Chemical compound C=CN1CCCC1=O WHNWPMSKXPGLAX-UHFFFAOYSA-N 0.000 description 1

- NIPNSKYNPDTRPC-UHFFFAOYSA-N N-[2-oxo-2-(2,4,6,7-tetrahydrotriazolo[4,5-c]pyridin-5-yl)ethyl]-2-[[3-(trifluoromethoxy)phenyl]methylamino]pyrimidine-5-carboxamide Chemical compound O=C(CNC(=O)C=1C=NC(=NC=1)NCC1=CC(=CC=C1)OC(F)(F)F)N1CC2=C(CC1)NN=N2 NIPNSKYNPDTRPC-UHFFFAOYSA-N 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 239000003929 acidic solution Substances 0.000 description 1

- 150000001252 acrylic acid derivatives Chemical group 0.000 description 1

- 229910001870 ammonium persulfate Inorganic materials 0.000 description 1

- 150000003863 ammonium salts Chemical class 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- VSGNNIFQASZAOI-UHFFFAOYSA-L calcium acetate Chemical compound [Ca+2].CC([O-])=O.CC([O-])=O VSGNNIFQASZAOI-UHFFFAOYSA-L 0.000 description 1

- 239000001639 calcium acetate Substances 0.000 description 1

- 229960005147 calcium acetate Drugs 0.000 description 1

- 235000011092 calcium acetate Nutrition 0.000 description 1

- 238000003486 chemical etching Methods 0.000 description 1

- 239000007795 chemical reaction product Substances 0.000 description 1

- ZCDOYSPFYFSLEW-UHFFFAOYSA-N chromate(2-) Chemical compound [O-][Cr]([O-])(=O)=O ZCDOYSPFYFSLEW-UHFFFAOYSA-N 0.000 description 1

- JZULKTSSLJNBQJ-UHFFFAOYSA-N chromium;sulfuric acid Chemical compound [Cr].OS(O)(=O)=O JZULKTSSLJNBQJ-UHFFFAOYSA-N 0.000 description 1

- 238000004581 coalescence Methods 0.000 description 1

- 239000008199 coating composition Substances 0.000 description 1

- 239000011247 coating layer Substances 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 238000004624 confocal microscopy Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 150000001879 copper Chemical class 0.000 description 1

- OXBLHERUFWYNTN-UHFFFAOYSA-M copper(I) chloride Chemical compound [Cu]Cl OXBLHERUFWYNTN-UHFFFAOYSA-M 0.000 description 1

- 239000012792 core layer Substances 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- IQDGSYLLQPDQDV-UHFFFAOYSA-N dimethylazanium;chloride Chemical compound Cl.CNC IQDGSYLLQPDQDV-UHFFFAOYSA-N 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- PGQAXGHQYGXVDC-UHFFFAOYSA-N dodecyl(dimethyl)azanium;chloride Chemical compound Cl.CCCCCCCCCCCCN(C)C PGQAXGHQYGXVDC-UHFFFAOYSA-N 0.000 description 1

- 238000000572 ellipsometry Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 230000008014 freezing Effects 0.000 description 1

- 238000007710 freezing Methods 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

- 239000003112 inhibitor Substances 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 229960004592 isopropanol Drugs 0.000 description 1

- 238000011068 loading method Methods 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- MYWUZJCMWCOHBA-VIFPVBQESA-N methamphetamine Chemical compound CN[C@@H](C)CC1=CC=CC=C1 MYWUZJCMWCOHBA-VIFPVBQESA-N 0.000 description 1

- 238000000386 microscopy Methods 0.000 description 1

- 150000007522 mineralic acids Chemical class 0.000 description 1

- 230000000116 mitigating effect Effects 0.000 description 1

- MEFBJEMVZONFCJ-UHFFFAOYSA-N molybdate Chemical compound [O-][Mo]([O-])(=O)=O MEFBJEMVZONFCJ-UHFFFAOYSA-N 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910052755 nonmetal Inorganic materials 0.000 description 1

- 150000002843 nonmetals Chemical class 0.000 description 1

- 238000000879 optical micrograph Methods 0.000 description 1

- 150000007524 organic acids Chemical class 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- NBIIXXVUZAFLBC-UHFFFAOYSA-K phosphate Chemical compound [O-]P([O-])([O-])=O NBIIXXVUZAFLBC-UHFFFAOYSA-K 0.000 description 1

- 150000003013 phosphoric acid derivatives Chemical group 0.000 description 1

- 229920000768 polyamine Polymers 0.000 description 1

- 229920000447 polyanionic polymer Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 238000001314 profilometry Methods 0.000 description 1

- HXHCOXPZCUFAJI-UHFFFAOYSA-N prop-2-enoic acid;styrene Chemical group OC(=O)C=C.C=CC1=CC=CC=C1 HXHCOXPZCUFAJI-UHFFFAOYSA-N 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 230000035484 reaction time Effects 0.000 description 1

- 230000009257 reactivity Effects 0.000 description 1

- 238000004064 recycling Methods 0.000 description 1

- 238000004626 scanning electron microscopy Methods 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- UKLNMMHNWFDKNT-UHFFFAOYSA-M sodium chlorite Chemical compound [Na+].[O-]Cl=O UKLNMMHNWFDKNT-UHFFFAOYSA-M 0.000 description 1

- 229960002218 sodium chlorite Drugs 0.000 description 1

- SUKJFIGYRHOWBL-UHFFFAOYSA-N sodium hypochlorite Chemical compound [Na+].Cl[O-] SUKJFIGYRHOWBL-UHFFFAOYSA-N 0.000 description 1

- 238000007711 solidification Methods 0.000 description 1

- 230000008023 solidification Effects 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001256 stainless steel alloy Inorganic materials 0.000 description 1

- 229920001909 styrene-acrylic polymer Polymers 0.000 description 1

- LSNNMFCWUKXFEE-UHFFFAOYSA-L sulfite Chemical compound [O-]S([O-])=O LSNNMFCWUKXFEE-UHFFFAOYSA-L 0.000 description 1

- BDHFUVZGWQCTTF-UHFFFAOYSA-M sulfonate Chemical compound [O-]S(=O)=O BDHFUVZGWQCTTF-UHFFFAOYSA-M 0.000 description 1

- 150000003871 sulfonates Chemical group 0.000 description 1

- 150000003512 tertiary amines Chemical group 0.000 description 1

- 238000013519 translation Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/02—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding

- H05K3/06—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding the conductive material being removed chemically or electrolytically, e.g. by photo-etch process

- H05K3/061—Etching masks

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/02—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding

- H05K3/06—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding the conductive material being removed chemically or electrolytically, e.g. by photo-etch process

- H05K3/068—Apparatus for etching printed circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/28—Applying non-metallic protective coatings

- H05K3/282—Applying non-metallic protective coatings for inhibiting the corrosion of the circuit, e.g. for preserving the solderability

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/01—Tools for processing; Objects used during processing

- H05K2203/0104—Tools for processing; Objects used during processing for patterning or coating

- H05K2203/013—Inkjet printing, e.g. for printing insulating material or resist

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/03—Metal processing

- H05K2203/0392—Pretreatment of metal, e.g. before finish plating, etching

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/11—Treatments characterised by their effect, e.g. heating, cooling, roughening

- H05K2203/1163—Chemical reaction, e.g. heating solder by exothermic reaction

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/11—Treatments characterised by their effect, e.g. heating, cooling, roughening

- H05K2203/1184—Underetching, e.g. etching of substrate under conductors or etching of conductor under dielectrics; Means for allowing or controlling underetching

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing Of Printed Circuit Boards (AREA)

Abstract

하나 이상의 전기 전도성 특징부로 패터닝된 디바이스를 만드는 방법은 기판의 전기 절연성 표면 위에 전도성 물질 층을 증착하는 단계, 전도성 물질 층 위에 내부식성 물질 층을 증착하는 단계, 및 내부식성 물질 층 위에 에칭 방지 물질 층을 증착하는 단계를 포함한다. 에칭 방지 물질 층은 내부식성 물질 층 위에 증착될 수 있고, 내부식성 물질 층은 2-성분 에칭 마스크를 전도성 물질 층의 덮인 부분 및 전도성 물질 층의 노출된 부분을 도출하는 패턴으로 형성하고, 덮인 부분이 디바이스의 하나 이상의 전도성 특징부에 대응하는 위치에 위치한다. 습식 에칭 공정이 수행되어 전도성 물질 층의 노출된 부분을 전기 절연성 기판에서 제거되고, 2-성분 에칭 마스크가 제거되어 나머지 전도성 물질을 노출시킬 수 있다. 시스템 및 디바이스가 패터닝된 특징부를 갖는 디바이스와 관련된다.

Description

도입

다양한 전자 디바이스 및 전자 부품의 제조는 기판 상에 패터닝된 층을 제조할 것을 필요로 한다. 예를 들어, 마이크로칩, 인쇄 회로 기판, 태양 전지, 전자 디스플레이(가령, 액정 디스플레이, 유기 발광 다이오드 디스플레이, 및 퀀텀 닷 전자발광 디스플레이), 및 그 밖의 다른 다양한 전기 또는 광학 디바이스 및 부품이 기판에 의해 지지되는 복수의 겹치는 상이한 물질의 패터닝된 층으로 구성될 수 있다. 기판 상에 이러한 패터닝된 층을 하나 제조하는 것은 비-패터닝 물질 층을 기판 상으로 도포하고, 이 층 상에 에칭 방지 마스크를 제조하며, 에칭 공정을 수행하여 상기 에칭 방지 마스크에 의해 덮이지 않은 층의 일부분을 제거하고, 기판 상에 패터닝된 층을 형성함으로써 수행될 수 있다.

인쇄 회로 기판(PCB) 또는 그 밖의 다른 전자 부품의 제조에 대해 사용될 수 있는 하나의 예시에서, 전기 전도성 금속 층이 기판의 전기 절연 표면에 도포되고(또는 동등하게, 전기 전도성 층이 기판의 전기 절연성 표면 상에 형성), 에칭 방지 마스크가 전도성 층에 도포(또는 전도성 층 상에 형성)되고, 에칭 공정이 수행되어, 에칭 저항 마스크에 의해 덮이지 않는 전도성 층의 일부분을 제거하고, 따라서 기판의 전기 절연 표면 상에 패터닝된 전도성 층을 형성할 수 있다. 이렇게 형성된 패터닝된 전도성 층은 기판의 전기 절연 표면 상에 하나 이상의 전도성 특징부, 가령, 전도성 물질의 선형, 원형, 사각형 및 그 밖의 다른 형태를 포함할 수 있다. 특정 경우, 이러한 패터닝된 전도성 층을 형성하는 데 사용되는 에칭 프로세스가 습식 에칭 프로세스일 수 있으며, 이로 인해 액상 에칭 물질이 전도성 층과 상호 작용하여 기판의 전기 절연 표면으로부터 전도성 층을 제거할 수 있다. 이러한 습식 에칭 공정은 예를 들어 습식 "화학적" 에칭 공정일 수 있다.

습식 에칭의 빈번한 특성이 전도성 층을 에칭하는 대표적 예시에서 에칭 마스크 아래에서 전도성 층 물질의 제거 현상을 일컫는 "언더커팅(undercutting)"이다. 이러한 언더커팅은 에칭 마스크의 대응하는 폭에 대해 전기 전류의 흐름에 수직인 방향으로 특징부 폭을 감소시킴으로써 전도성 층의 전도율을 감소시킬 수 있다. 따라서 전도율이 희망 레벨 밑으로 떨어질 수 있다. 이러한 언더커팅으로 인한 전도율 감소는 비교적 작은 특징부 폭, 가령, 약 60 ㎛ 미만의 특징부 폭의 경우 특히 두드러질 수 있다. 이 언더커팅 현상은 또한 기울어진 전도성 특징부 또는 비-평탄형 "측벽"에 전이될 수 있다. 본 명세서에서 사용될 때, "측벽(side-wall)"은 특징부의 측방 표면, 가령, 에칭 마스크에 인접한 특징부의 상부로부터 기판에 인접한 특징부의 하부까지 뻗어 있는 특징부의 측부 상의 벽을 지칭한다. 일부 경우, 이러한 언더커팅과 연관된 특징부가 기울어진, 즉, 비-평면 측벽을 가질 수 있음으로써, 특징부의 상부에 가까운(에칭 마스크에 가까운) 폭이 특징부의 하부에 가까운(기판에 가까운) 폭보다 작다. 가령, 원하는 전도율을 획득하기 위해 또는 원하는 전기 주파수 응답을 얻기 위해 특징부의 상부에서의 특정 최소 특징부 폭이 바람직할 수 있으며, 이러한 언더커팅은 최소 특징부 폭 또는 최소 특징부 간 공백(feature-to-feature spacing) 중 적어도 하나에 하한을 부가함으로써, 기판 상에 제공될 수 있는 특징부의 밀도를 제한할 수 있다.

언더커팅은 PCB의 제조 시 전도성 금속 라인의 패터닝이 아닌 다른 적용예에서 바람직하지 않을 수 있다. 예를 들어, 앞서 PCB에 대해 앞서 기재된 바와 같이 유사한 고려사항이 또한 예를 들어, 마이크로칩, 전자 디스플레이, 또는 태양 전지의 제조 시 전기 전류 및/또는 전기 신호를 운반하기 위한 목적으로 금속 라인을 이용하는 그 밖의 다른 응용예에도 적용될 수 있다. 또 다른 예시에서, 그 밖의 다른 고려사항이 실질적으로 수직인 측벽이 바람직한 전자 또는 광학 디바이스 또는 부품의 제조 시 패터닝된 층, 비금속, 예를 들어, 광학 코팅 또는 절연 층을 이용하는 응용예에도 적용될 수 있다.

전자 및/또는 광학 디바이스 또는 전자 및/또는 광학 부품을 제조하기 위한 목적으로 기판 상에 패터닝된 층을 형성할 때 습식 에칭 공정을 이용해 형성된 특징부의 언더커팅을 완화(가령, 감소 또는 제거)하는 개선된 기법이 필요하다.

종래의 공정에서, 기판에 패턴별 광 노출 및 후속 공정 시 에칭 마스크로 변환되는 감광성 물질(종종, UV 광 민감성 물질)의 블랭킷 코팅(blanket coating)을 도포함으로써 앞서 기재된 에칭 마스크가 형성된다. 이러한 후속 공정은 일반적으로 기판 상에 에치 마스크 패턴을 형성하기 위한 (가령, 현상 단계 동안의) 감광성 물질의 제거를 포함한다. 많은 사례에서, 비제한적 예를 들면, PCB의 금속 층을 패터닝하기 위해 에칭 마스크를 이용할 때, 에칭 마스크는 기판 표면의 50% 미만을 덮고 제거된 감광성 물질이 폐기물로서 폐기된다. 많은 사례에서, 감광성 물질의 제거는 기판을 액체(가령, 현상제)로 세정하는 것을 필요로 하며 이러한 세정을 수행하기 위해 사용되는 액체가 폐기물로서 폐기된다. 많은 사례에서, 비제한적 예를 들면, 에칭 마스크를 이용해 PCB의 금속 층을 패터닝할 때, 감광성 물질이 캐리어 시트(carrier sheet) 상에 준비되고 그 후 적층화(lamination)를 통해 상기 캐리어 시트로부터 기판 상으로 전사되며, 이러한 전사 후 캐리어 시트는 폐기물로 폐기된다. 전자 및/또는 광학 디바이스 및/또는 부품을 제조할 때, 폐기물을 감소시키는 것이 바람직하다. 이러한 폐기물을 감소시키기 위한 한 가지 접근법이 기판에 원하는 패턴의 액상 마스크 잉크를 전달하고 그 후 (가령, 건조 및/또는 베이킹을 통해) 액상 코팅을 처리하여 완성된 에칭 마스크를 형성하기 위해 비-타격 인쇄(가령, 잉크젯 인쇄)를 이용해 원하는 패턴으로 에칭 마스크를 기판에 직접 도포하는 것이다. 그러나 이러한 비-타격 인쇄 방법에 의해 전달되는 잉크는 일반적으로 광학 및/또는 전기 부품 및/또는 디바이스의 제조에서 사용되는 기판의 표면 상에 잘 흡수되지 않고, 이러한 잉크는 이러한 표면 상에서 통제되지 않는 방식으로 확산 및/또는 이동될 수 있음으로써, 예컨대, 클러스터링(clustering), 유합(coalescence), 및 망점 퍼짐(dot gain) 현상을 초래할 수 있다. 따라서, 이러한 비-타격 인쇄 공정으로부터 도출된 에칭 마스크는 감소된 분해능, 세부사항의 부재, 패터닝된 선 폭 불일치, 선 에지 평활도 불량, 분리될 특징부들 간 결합, 및 연속이어야 할 특징부 내 단절을 보일 수 있다.

앞서 기재된 바와 같이 에칭 마스크를 준비하기 위해 비-타격 인쇄가 사용되는 이러한 경우, 기판의 표면 상의 이러한 제어되지 않는 증착된 액상 마스크 잉크의 확산 및/또는 이동을 완화(가령, 감소 또는 제거)할 필요가 있다.

본 발명의 하나의 양태에서, 하나 이상의 전기 전도성 특징부로 패터닝된 디바이스를 만드는 방법은 기판의 전기 절연성 표면 위에 전도성 물질 층을 증착하는 단계, 전도성 물질 층 위에 내부식성 물질 층을 증착하는 단계, 및 내부식성 물질 층 위에 에칭 방지 물질 층을 증착하는 단계를 포함한다. 내부식성 물질 층 위에 에칭 방지 물질 층을 증착하는 단계를 포함하며, 상기 에칭 방지 물질 층 및 내부식성 물질 층은 2-성분 에칭 마스크(bi-component etch mask)를 전도성 물질 층의 덮인 부분 및 전도성 물질 층의 노출된 부분을 도출하는 패턴으로 형성하고, 덮인 부분이 디바이스의 하나 이상의 전도성 특징부에 대응하는 위치에 위치한다. 습식 에칭 공정이 수행되어 전기 절연성 기판의 노출된 부분을 제거하고, 2-성분 에칭 마스크가 제거되어 전도성 물질 층의 덮인 부분의 나머지 전도성 물질을 노출시키고, 이로써 디바이스의 하나 이상의 전기 전도성 특징부를 형성할 수 있다.

본 발명의 또 다른 양태에서, 전기 전도성 특징부로 패터닝된 디바이스를 만들기 위한 장치가 기판의 전기 절연성 표면 위 전도성 물질 층 위에 내부식성 물질 층을 증착하도록 구성된 제1 증착 모듈, 내부식성 물질 위에 에칭 방지 물질 층을 증착하도록 구성된 제2 증착 모듈, 및 기판의 전도성 물질 층을 에칭하도록 구성된 습식 에칭 모듈을 포함한다.

본 발명의 또 다른 양태에서, 전기 전도성 특징부로 패터닝된 디바이스가 전기 절연성 표면을 갖는 기판 및 전기 절연성 표면 상에 배치된 전도성 특징부를 포함한다. 전도성 특징부는 전기 절연성 표면에 수직인 방향으로 측정된 높이(c), 전기 절연 표면에서 측정된 제1 폭(a), 및 전도성 특징부의 높이(c)를 따라 전기 절연 표면에 대향하는 전도성 특징부의 단부에서 특정된 제2 폭(b)을 포함한다. 제1 폭(a)과 제2 폭(b) 간 차이의 절반을 높이(c)로 나눈 값이 적어도 2이다(즉, [a-b]/c = 2).

본 발명의 또 다른 양태에서, 방법은 제1 반응 성분을 포함하는 제1 액상 조성물을 금속 표면 상으로 도포하여 프라이머 층을 형성하는 단계, 및 프라이머 층에 영향을 미치지 않는 인쇄 공정에 의해 제2 반응 성분을 포함하는 제2 액상 조성물을 이미지별 인쇄(image-wise printing)하여 지정 패턴에 따라 에칭 마스크를 생성하는 단계를 포함한다. 제2 액상 조성물의 액적이 프라이머 층에 접촉할 때, 제2 반응 성분은 제1 반응 성분과의 화학 반응을 겪어서 상기 액적을 부동화할 수 있다.

추가 목적, 특징, 및/또는 그 밖의 다른 이점이 기재에 부분적으로 제공될 것이며, 부분적으로 기재로부터 명백하거나, 본 명세서 및/또는 청구항의 실시에 의해 습득될 수 있다. 이들 목적 및 이점 중 적어도 일부가 첨부된 청구항에 특히 지시되는 요소 및 조합에 의해 구현 및 획득될 수 있다.

상기의 일반적인 설명과 하기의 상세한 설명 모두 예시적이고 설명을 위한 것에 불과하며 청구항을 제한하지 않으며, 오히려 청구항은 균등예를 포함해, 광의의 범위를 가질 것이다.

도 1a-1d는 기판 상의 패터닝된 층을 형성하기 위한 종래의 공정을 겪는 디바이스의 단면도 및 평면도이다.

도 2a-2c는 기판 상의 패터닝된 층을 형성하기 위한 또 다른 종래의 공정을 겪는 디바이스의 단면도 및 평면도이다.

도 3a 및 3c는 기판 상의 패터닝된 층을 형성하기 위한 또 다른 종래의 공정을 겪는 디바이스의 단면도 및 평면도이다.

도 4a-4c는 기판 상의 패터닝된 층을 형성하기 위한 또 다른 종래의 공정을 겪는 디바이스의 단면도 및 평면도이다.

도 5a-5c는 기판 상의 패터닝된 층을 형성하기 위한 또 다른 종래의 공정을 겪는 디바이스의 단면도, 평면도 및 투시도이다.

도 6a-6d는 본 발명의 예시적 실시예에 따라, 기판 상에 패터닝된 층을 형성하기 위한 공정을 겪는 디바이스의 단면 및 평면도이다.

도 7a-7c는 본 발명의 또 다른 예시적 실시예에 따라, 기판 상에 패터닝된 층을 형성하기 위한 공정을 겪는 디바이스의 단면 및 평면도이다.

도 8a-8d는 본 발명의 또 다른 예시적 실시예에 따라, 기판 상에 패터닝된 층을 형성하기 위한 공정을 겪는 디바이스의 단면도이다.

도 9a-9d는 본 발명의 또 다른 예시적 실시예에 따라, 기판 상에 패터닝된 층을 형성하기 위한 공정을 겪는 디바이스의 단면도이다.

도 10은 종래의 공정에 따라 기판 상에 패터닝된 층을 형성하기 위한 공정 동안의 디바이스의 단면도이다.

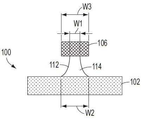

도 11은 본 발명의 예시적 실시예에 따라 기판 상에 패터닝된 층을 형성하기 위한 공정 동안의 디바이스의 단면도이다.

도 12a는 본 발명의 예시적 실시예에 따라 기판 상에 패터닝된 층을 형성하기 위한 공정 동안의 디바이스의 단면도이다.

도 12b는 도 12a의 원(12b) 안의 부분의 확대도이다.

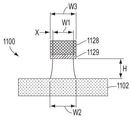

도 13a는 본 발명의 또 다른 예시적 실시예에 따라 기판 상에 패터닝된 층을 형성하기 위한 공정 동안의 디바이스의 단면도이다.

도 13b 및 13c는 B 및 C의 상이한 상태의 특징을 보여주는 도 13a의 원(13B,C) 안의 부분의 확대도이다.

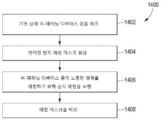

도 14는 본 발명의 예시적 실시예에 따르는 기판 상의 패터닝된 층을 형성하기 위한 작업 흐름을 보여주는 흐름도이다.

도 15는 본 발명의 또 다른 예시적 실시예에 따르는 기판 상의 패터닝된 층을 형성하기 위한 작업 흐름을 보여주는 흐름도이다.

도 16는 본 발명의 또 다른 예시적 실시예에 따르는 기판 상의 패터닝된 층을 형성하기 위한 작업 흐름을 보여주는 흐름도이다.

도 17은 예를 들어, 본 발명의 또 다른 예시적 실시예에 따라 PCB의 제조 시 기판 상에 패터닝된 구리 층을 형성하기 위한 흐름도이다.

도 18은 본 발명의 다양한 예시적 실시예에 따라 디바이스를 형성하기 위한 시스템의 구성요소의 블록도이다.

도 19는 본 발명의 또 다른 예시적 실시예에 따르는 기판 상의 패터닝된 층을 형성하기 위한 작업 흐름을 보여주는 흐름도이다.

도 20은 종래 공정에 따라 형성되는 전도성 특징부의 광학 현미경 사진(photo micrograph)이다.

도 21은 본 발명의 예시적 실시예에 따라 형성되는 전도성 특징부의 광학 현미경 사진이다.

도시의 단순성 및 명료성을 위해, 도면에 도시된 요소들이 반드시 실측 비율로 도시된 것은 아니다. 예를 들어, 명료성을 위해 일부 요소들의 치수가 다른 요소들에 비해 과장될 수 있다. 또한, 경우에 따라, 도면에서 대응하거나 유사한 요소들을 지칭하기 위해 도면 부호가 반복될 수 있다.

도 2a-2c는 기판 상의 패터닝된 층을 형성하기 위한 또 다른 종래의 공정을 겪는 디바이스의 단면도 및 평면도이다.

도 3a 및 3c는 기판 상의 패터닝된 층을 형성하기 위한 또 다른 종래의 공정을 겪는 디바이스의 단면도 및 평면도이다.

도 4a-4c는 기판 상의 패터닝된 층을 형성하기 위한 또 다른 종래의 공정을 겪는 디바이스의 단면도 및 평면도이다.

도 5a-5c는 기판 상의 패터닝된 층을 형성하기 위한 또 다른 종래의 공정을 겪는 디바이스의 단면도, 평면도 및 투시도이다.

도 6a-6d는 본 발명의 예시적 실시예에 따라, 기판 상에 패터닝된 층을 형성하기 위한 공정을 겪는 디바이스의 단면 및 평면도이다.

도 7a-7c는 본 발명의 또 다른 예시적 실시예에 따라, 기판 상에 패터닝된 층을 형성하기 위한 공정을 겪는 디바이스의 단면 및 평면도이다.

도 8a-8d는 본 발명의 또 다른 예시적 실시예에 따라, 기판 상에 패터닝된 층을 형성하기 위한 공정을 겪는 디바이스의 단면도이다.

도 9a-9d는 본 발명의 또 다른 예시적 실시예에 따라, 기판 상에 패터닝된 층을 형성하기 위한 공정을 겪는 디바이스의 단면도이다.

도 10은 종래의 공정에 따라 기판 상에 패터닝된 층을 형성하기 위한 공정 동안의 디바이스의 단면도이다.

도 11은 본 발명의 예시적 실시예에 따라 기판 상에 패터닝된 층을 형성하기 위한 공정 동안의 디바이스의 단면도이다.

도 12a는 본 발명의 예시적 실시예에 따라 기판 상에 패터닝된 층을 형성하기 위한 공정 동안의 디바이스의 단면도이다.

도 12b는 도 12a의 원(12b) 안의 부분의 확대도이다.

도 13a는 본 발명의 또 다른 예시적 실시예에 따라 기판 상에 패터닝된 층을 형성하기 위한 공정 동안의 디바이스의 단면도이다.

도 13b 및 13c는 B 및 C의 상이한 상태의 특징을 보여주는 도 13a의 원(13B,C) 안의 부분의 확대도이다.

도 14는 본 발명의 예시적 실시예에 따르는 기판 상의 패터닝된 층을 형성하기 위한 작업 흐름을 보여주는 흐름도이다.

도 15는 본 발명의 또 다른 예시적 실시예에 따르는 기판 상의 패터닝된 층을 형성하기 위한 작업 흐름을 보여주는 흐름도이다.

도 16는 본 발명의 또 다른 예시적 실시예에 따르는 기판 상의 패터닝된 층을 형성하기 위한 작업 흐름을 보여주는 흐름도이다.

도 17은 예를 들어, 본 발명의 또 다른 예시적 실시예에 따라 PCB의 제조 시 기판 상에 패터닝된 구리 층을 형성하기 위한 흐름도이다.

도 18은 본 발명의 다양한 예시적 실시예에 따라 디바이스를 형성하기 위한 시스템의 구성요소의 블록도이다.

도 19는 본 발명의 또 다른 예시적 실시예에 따르는 기판 상의 패터닝된 층을 형성하기 위한 작업 흐름을 보여주는 흐름도이다.

도 20은 종래 공정에 따라 형성되는 전도성 특징부의 광학 현미경 사진(photo micrograph)이다.

도 21은 본 발명의 예시적 실시예에 따라 형성되는 전도성 특징부의 광학 현미경 사진이다.

도시의 단순성 및 명료성을 위해, 도면에 도시된 요소들이 반드시 실측 비율로 도시된 것은 아니다. 예를 들어, 명료성을 위해 일부 요소들의 치수가 다른 요소들에 비해 과장될 수 있다. 또한, 경우에 따라, 도면에서 대응하거나 유사한 요소들을 지칭하기 위해 도면 부호가 반복될 수 있다.

이하의 상세한 설명에서, 본 발명의 완전한 이해를 제공하기 위해 많은 세부사항이 제공된다. 그러나, 해당 분야의 통상의 기술자라면 이들 특정 세부사항 없이 본 발명이 실시될 수 있음을 이해할 것이다. 한편, 본 발명을 모호하게 하지 않도록 공지된 방법, 절차, 및 구성요소는 상세히 기재되지 않는다.

마이크로칩, 인쇄 회로 기판, 태양 전지, 전자 디스플레이(가령, 액정 디스플레이, 유기 발광 다이오드 디스플레이, 및 퀀텀 닷 전자발광 디스플레이), 및 다양한 그 밖의 다른 전기 또는 광학 디바이스 및 부품이 기판에 의해 지원되는 상이한 물질의 복수의 겹치는 층, 가령, 패터닝된 층으로 구성될 수 있다. 본 발명의 다양한 예시적 실시예가 전기 및/또는 광학 디바이스 및/또는 부품의 제조에 적용되기 위해, 기판 상에 패터닝된 층을 형성하기 위한 방법 및 디바이스를 고려한다. 본 명세서에서 "디바이스 층(device layer)"은 최종 형태, 일부 경우, 패터닝될 수 있는 형태에서, 완성된 광학 및/또는 전자 디바이스 및/또는 부품에서 층을 포함하는 물질의 층을 지칭하며, 여기서, "패터닝된 디바이스 층(patterned device laye)"은 패터닝된 후의 이러한 층을 지칭하고, "비-패터닝 디바이스 층(unpatterned device layer)"은 패터닝되기 전의 이러한 층을 지칭할 것이다. 예를 들어, 다양한 예시적 실시예가, 인쇄 회로 기판(PCB) 또는 그 밖의 다른 전자 부품를 제조하는 일부로서 기판 상에 조립될 수 있는 전도성 라인의 세트를 포함하는 전도성 물질의 패터닝된 디바이스 층을 고려한다. 본 발명의 실시예에 따르면, 기판 상의 비-패터닝 디바이스 층, 비제한적 예를 들면, 기판의 전기적 절연 표면 위에 놓이는 구리 또는 그 밖의 다른 전도성 물질의 전도성 층이 에칭 마스크를 통해 노출된 디바이스 층 물질을 제거하는 데 사용되는 습식 에칭 공정 동안 언더커팅을 감소시키는 효과를 갖는 "언더컷-감소(undercut-reducing)" 물질을 포함하는 "프라이머" 층으로 코팅될 수 있다. 예를 들어, 언더컷-감소 물질이 디바이스 층의 물질에 대해 내부식 속성을 보이는 물질을 포함할 수 있는 내부식성 물질일 수 있다. 이러한 내부식성 물질은 폴리머, 유기 물질, 무기 물질, 시프 염기(Schiff base), 또는 그 밖의 다른 물질, 가령, 그 전체가 본 명세서에 참조로서 포함되는 국제 특허 출원 공개 번호 WO2016/193978 A2 및 WO2016/025949 A1에 개시되어 있는 물질을 포함할 수 있다. 내부식성 물질은 비-패터닝 디바이스 층 위에 블랭킷-형성, 또는 블랭킷-증착, 또는 패턴-형성 또는 패턴-증착될 수 있다. 다양한 실시예에서, 용어 내부식성 물질과 언더컷-감소 물질은 상호 교환 가능하게 사용될 수 있다.

본 발명의 다양한 실시예가 기판 상의 비-패터닝 디바이스 층 위에 언더컷-감소 물질을 포함하는 프라이머 층을 형성하고, 프라이머 층 위에 에칭-방지 물질의 패터닝된 층을 형성함으로써 기판 상에 에칭 마스크를 형성하는 것을 고려한다. 본 발명의 다양한 실시예가 분리 층, 가령, 언더컷-감소 물질을 포함하는 프라이머 층을 형성할 필요 없이, 기판 상에 언더컷-감소 물질과 에칭-저항 물질의 혼합의 패터닝된 층을 형성함으로써, 기판 상의 비-패터닝 디바이스 위에 에칭 마스크를 형성하는 것을 고려한다. 실시예에서, 언더컷-감소 물질을 함유하는 프라이머 층이 기판 상의 비-패터닝 디바이스 층 위에 형성되고, 그 후 프라이머 층 상에 패턴으로 액상 에칭-방지 잉크를 증착하고, 그 후 후속 공정, 가령, 에칭-방지 물질의 고체 패터닝된 층을 형성하기 위한 잉크의 건조 또는 베이킹을 통해, 액상 잉크를 에칭 마스크로 변환함으로써 에칭 마스크가 프라이머 층 위에 형성되는데, 이때, 이러한 액상 에칭-방지 잉크는 프라이머 층과 상호작용하는 물질을 포함할 수 있다. 예를 들어, 액상 에칭-방지 잉크는, 프라이머 층과 접촉 시, 프라이머 표면 상의 잉크의 이동(translation) 또는 확산을 제한하는 화학적 반응을 겪는다. 또 다른 예를 들면, 액상 에칭-방지 잉크는 잉크젯 노즐에 의해 전달되는 액적의 형태로 표면에 도포될 수 있고, 프라이머 표면과 접촉되면, 이러한 액적은 곧 효과적으로 제위치에 부동화(immobilize)되거나 "동결"되어, 프라이머 표면 상의 잉크 액적의 추가 이동 또는 확산이 크게 감소 또는 전체적으로 중단되며, 이는 본 명세서에 참조로서 포함되는 국제 특허 번호 WO2016/193978 A2 및 WO2016/025949 A1에 기재되어 있다. 실시예에서, 가령, 에칭-방지 잉크와 프라이머 층 간 상호작용으로부터 야기된 화학적 반응을 통해 프라이머 표면 상에서의 에칭-방지 잉크의 확산을 제한하는 것이 패터닝될 층 상에 마스크 패턴의 정확한 증착에 기여할 수 있다.

실시예에서, 프라이머 층은 기판 상의 비-패터닝 디바이스 층 위에 형성되고, 액상 에칭-방지 잉크를 프라이머 층 상으로 패턴으로 전달하고, 그 후 후속 처리, 가령, 후속 에칭에 저항성이 있는 고체 패터닝된 층을 형성하기 위한 잉크의 건조 또는 베이킹을 통해 상기 액상 잉크를 에칭 마스크로 변환함으로써, 에칭 마스크는 프라이머 층 위에 형성된다. 실시예에서, 프라이머 층은 제1 반응 성분을 포함하고, 액상 에칭-방지 잉크는 제2 반응 성분을 포함하며, 에칭-방지 잉크가 프라이머 층과 접촉될 때, 제1 및 제2 반응 성분이 반응하여, 잉크를 제위치로 효과적으로 부동화 또는 "동결"시킬 수 있음으로써, 프라리머 표면 상에서의 잉크의 추가 이동 또는 확산이 크게 감소 또는 전체적으로 중단될 수 있다. 실시예에서, 프라이머 층은 제3 반응 성분을 포함하고, 액상 에칭-저항 잉크는 제4 반응 성분을 포함하며, 제3 반응 성분과 제4 반응 성분의 반응은 에칭-방지 잉크에서 비교적 불용성이고 차후 비-패터닝 디바이스 층을 에칭하기 위해 사용되는 에칭 용액에서 불용성인 에칭 마스크 물질을 생산한다(여기서, 비교적 불용성은 제4 반응 성분에 비해 정의된다). 이렇게 형성된 에칭 마스크 물질은 본 명세서에서 2-성분 물질(bi-component material) 또는 2-성분 반응 산물(bi-component reaction product)이라고 지칭된다. 다양한 실시예에서, 질량의 과반수를 에칭 마스크를 구성하는 2-성분 물질을 형성하기 위해 제공하는 반응 성분을 에칭-방지 성분(etch-resist component 또는 etching-resisting component)이라고 지칭하고, 반면에 다른 반응 성분을 고정화 성분(fixating component) 또는 고정화 반응 성분, 또는 고정화 조성물이라고 지칭한다. 실시예에서, 에칭-방지 성분은 복수의 물질을 포함한다. 실시예에서, 고성화 성분은 복수의 물질을 포함한다. 실시예에서, 에칭-방지 잉크가 수성 잉크이며, 2-성분 물질은 물에 비교적 불용성이다. 실시예에서, 에칭 용액은 산성 에칭 용액, 비제한적 예를 들면, 구리 클로라이드와 수소 페록사이드의 혼합물이다. 실시에에서, 제1, 제2, 제3, 또는 제4 성분 중 하나 이상이 복수의 물질을 포함한다. 실시예에서, 제1 성분과 제3 성분이 동일하다. 실시예에서, 제1 성분과 제3 성분이 동일하다. 실시예에서, 2-성분 물질을 생성하는 반응이 프라이머 층 상에 에칭-방지 잉크의 액적을 부동화(immobilize)하는 반응과 동일하다. 실시예에서, 프라이머 층은 언더컷-방지 물질을 포함한다. 실시예에서, 프라이머의 반응 성분(가령, 앞서 기재된 제1 또는 제3 반응 성분)이 언더컷-방지 물질을 포함한다. 실시예에서, 에칭-방지 잉크의 반응 성분(가령, 앞서 기재된 제2 또는 제4 반응 성분)이 언더컷-방지 물질을 포함한다. 실시예에서, 에칭-방지 잉크는 언더컷-방지 물질을 포함한다.

실시예에서, 프라이머 또는 에칭-방지 잉크 중 적어도 하나는 다가 및/또는 폴리-양이온 그룹 및/또는 다가 무기 양이온을 포함할 수 있다. 실시예에서, 프라이머 또는 에칭-방지 잉크 중 적어도 하나는 폴리-음이온 그룹을 포함할 수 있다. 실시예에서, 프라이머 또는 에칭-방지 잉크 중 적어도 하나는 반응 음이온 성분을 포함할 수 있고 수용성일 수 있다. 실시예에서, 이러한 반응 음이온 성분은 7.0를 초과하는 pH의 적어도 하나의 음이온 폴리머를 (기본 형태로) 포함할 수 있다. 실시예에서, 이러한 음이온 폴리머가 용해된 염 형태(비제한적 예를 들면, 소듐 염 형태)의 아크릴 수지 및 스티렌-아크릴 수지, 용해된 염 형태(비제한적 예를 들면, 소듐 염 형태)의 설폰 수지로부터 선택될 수 있다. 실시예에서, 이러한 음이온 폴리머는 암모늄 형태 또는 아민 중성화된 형태일 수 있다. 실시예에서, 이러한 음이온 폴리머는 폴리머 에멀전 또는 분산의 형태를 가질 수 있다. 다양한 실시예에서, 2-성분 물질을 생성하는 반응이 프라이머 층 상의 에칭-방지 잉크의 점도의 큰 증가를 야기하고, 고정 현상(immobilization phenomenon)이 이 점도의 증가로부터 도출된다. 다양한 실시예에서, 에칭-방지 잉크는 2-성분 물질을 형성하는 물질 질량의 대다수를 제공한다. 다양한 실시예에서, 프라이머는 2-성분 물질을 형성하는 물질 질량의 대다수를 제공하고, 이러한 경우, 에칭 방지 잉크가 고정화 성분을 포함할 수 있고 프라이머 층은 에칭 방지 성분을 포함할 수 있다. 다양한 실시예에서, 비-패터닝 디바이스 층 위에 액상 프라이머 잉크의 코팅을 제공하고, 그 후 층을 건조 또는 베이킹하여 층을 처리하여 프라이머 층을 형성함으로써, 프라이머 층이 형성된다. 다양한 실시예에서, 이러한 프라이머 잉크는 수성이다. 다양한 실시예에서, 프라이머 층은 비-패터닝 디바이스 층에 우수한 접착성을 가진다. 다양한 실시예에서, 잉크젯 인쇄, 분사 코팅, 계량된 로드 코팅, 롤 코팅, 딥 코팅, 또는 그 밖의 다른 임의의 적합한 인쇄 또는 코팅 방법에 의해 프라이머 층은 비-패터닝 디바이스 층 위에 도포된다. 다양한 실시예에서, 프라이머 층은 균일(가령, 블랭킷) 코팅이거나 패터닝된 코팅일 수 있다.

실시예에서, 적어도 부분적으로, 비-패터닝 디바이스 층 위에 표면 활성화 용액을 도포함으로써 프라이머 층이 형성된다. 실시예에서, 표면 활성화 용액은 구리 염, 제2철 염, 크롬-황산, 과황산염, 소듐 클로라이트, 및 수소 페록사이드 중 하나 이상을 포함한다. 실시예에서, 비-패터닝 디바이스 층은 금속 층이며 표면 활성화 용액이 금속 층의 표면 상으로 도포된다. 실시예에서, 표면 활성화 용액은 지정 시간 동안 도포될 수 있고, 그 후, 비-제한적 예를 들면, 10초, 20초, 30초, 60초, 또는 더 긴 시간 동안 씻길 수 있다. 실시예에서, 표면을 표면 활성화 용액을 담는 배쓰에 침지시킴으로써 표면 활성화 용액이 도포될 수 있다. 실시예에서, 표면에 표면 활성화 용액을 분사함으로써, 또는 그 밖의 다른 임의의 적합한 방법에 의해 표면 활성화 용액은 도포될 수 있다. 실시예에서, 세정 유체, 비제한적 예를 들면, 알콜 용액, 에탄올, 프로필알콜, 이소-프로필 알콜, 및 아세톤을 이용함으로써, 표면 활성화 용액은 표면으로부터 씻긴다. 실시예에서, 표면이 예를 들어, PCB의 구리 층의 표면이고, 0.5 내지 1.0의 중량 퍼센트 농도의 CuCl2(또는 임의의 2가 구리 염)의 표면 활성화 수용액이 사용되고, 적어도 부분적으로 30초 동안 표면 활성화 용약을 담는 배쓰에 구리 표면을 침지됨으로써 프라이머 층은 형성된다. 실시예에서, 표면이 예를 들어, PCB의 구리 층의 표면이고, 0.5 내지 1.0의 중량 퍼센트 농도의 Na2S2O8(또는 임의의 과산화황산염)의 표면 활성화 수용액이 사용되고, 적어도 부분적으로 30초 동안 표면 활성화 용약을 담는 배쓰에 구리 표면을 침지됨으로써 프라이머 층은 형성된다. 실시예에서, 표면이 예를 들어, PCB의 구리 층의 표면이고, 10의 중량 퍼센트 농도의 H2O2의 표면 활성화 수용액이 사용되고, 적어도 부분적으로 30초 동안 표면 활성화 용약을 담는 배쓰에 구리 표면을 침지됨으로써 프라이머 층은 형성된다. 실시예에서, 표면이 예를 들어, PCB의 구리 층의 표면이고, 20의 중량 퍼센트 농도의 FeCl3의 표면 활성화 수용액이 사용되고, 적어도 부분적으로 10초 동안 표면 활성화 용약을 담는 배쓰에 구리 표면을 침지됨으로써 프라이머 층은 형성된다. 실시예에서, 표면이 예를 들어, PCB의 구리 층의 표면이고, 5의 중량 퍼센트 농도의 HCrO4/H2SO4의 표면 활성화 수용액이 사용되고, 적어도 부분적으로 30초 동안 표면 활성화 용약을 담는 배쓰에 구리 표면을 침지됨으로써 프라이머 층은 형성된다. 실시예에서, 표면이 예를 들어, PCB의 구리 층의 표면이고, 5의 중량 퍼센트 농도의 NaClO2의 표면 활성화 수용액이 사용되고, 적어도 부분적으로 60초 동안 표면 활성화 용약을 담는 배쓰에 구리 표면을 침지됨으로써 프라이머 층은 형성된다.

잉크젯 인쇄기를 이용해 프라이머 층 상으로 에칭-방지 잉크를 인쇄하는 실시예에서, 기판은 거의 "실온", 가령, 20 ℃ 내지 30 ℃이거나, 상승된 온도, 가령, 100 ℃일 수 있다. 실시예에서, 2-성분 에칭 마스크는 적어도 0.01 um의 두께를 가질 수 있다. 실시예에서, 2-성분 에칭 마스크는 적어도 12 um 미만의 두께를 가질 수 있다.

본 발명의 실시예에서, 프라이머 층이 기판 상으로 증착되고 그 후 잉크젯 인쇄를 이용해 에칭 마스크 잉크는 프라이머 층 상으로 증착되고 베이킹되어 에칭 마스크 층을 형성할 수 있다. 프라이머 층과 접촉하자마자, 에칭 마스크의 액적은 프라이머 층과 상호작용하여, 잉크의 액적을 효과적으로 부동화 또는 "동결"시킴으로써, 프라이머 층 내 제1 반응 성분과 에칭 마스크 잉크 내 제2 반응 성분 간 화학적 반응의 결과로서, 추가 확산 및/또는 이동이 크게 감소 또는 제거될 수 있다. 덧붙여, 에칭 마스크 잉크의 하나 이상의 성분이 프라이머 층의 하나 이상의 성분과의 반응을 겪어, 에칭 마스크 잉크에 비교적 불용성이고 상기 에칭 마스크와 함께 사용될 에칭 용액에 비교적 불용성인 2-성분 에칭 마스크 물질을 형성할 수 있다(여기서, 비교적 불용성은 반응하여 2-성분 에칭 마스크 물질을 형성하는 에칭 마스크 잉크 성분에 대해 정의된다). 예를 들어, 에칭 마스크 잉크는 수용성일 수 있고 이러한 반응으로부터 도출된 에칭 마스크 물질은 물에 불용성이고, 에칭 용액은 산성 에칭 용액일 수 있고 이러한 반응으로부터 도출된 에칭 마스크 물질은 산성 에칭 용액에 불용성이다.

실시예에서, 비-패터닝 디바이스 층, 가령, 구리 층을 언더컷-방지 물질, 가령, 내부식성 물질을 코팅하는 것은 에칭 마스크를 이용해 디바이스 층 물질을 습식-에칭되지 않도록 보호할 수 있는 임의의 공정에 적용 가능할 수 있다. 구리가 아닌 그 밖의 다른 금속 층이 실시예에서 사용될 수 있으며, 비제한적 예를 들면, 알루미늄, 스테인리스 강, 금 및 금속 합금일 수 있다. 본 발명의 예시적 실시예는 예를 들어, 적층화, 슬롯 다이 코팅, 또는 스핀 코팅을 통해, 감광성 층을, 차후 포토마스크를 통해 또는 직접 레이저 이미징을 통해, 선택된 파장의 광, 가령, UV 광에 노출시킴으로써 차후에 패터닝되는 비-패터닝 디바이스 층에 도포하기 전에, 프라이머 층의 형태로 언더컷-감소 물질을 도입시키는 것을 포함한다.

화학 에칭 공정 동안 언더컷-감소 물질의 작용이 패터닝 공정으로부터 도출된 디바이스 층 특징부의 언더컷 발생을 완화(가령, 감소, 제거)할 수 있다. 따라서, 화학 에칭 공정이 수행된 후, 언더컷-감소 물질 없이 형성된 디바이스 층에 비교할 때 더 수직이고 덜 경사진 측벽을 갖는 디바이스 층 특징부가 언더컷팅의 감소 또는 제거로 인해 형성될 수 있다. 전기 전류 또는 전기 신호를 운반하는 기능을 갖는 전도성 물질을 포함하는 패터닝된 디바이스에 적용될 때, 본 발명의 다양한 실시예는 이렇게 형성된 전기 회로의 전체 성능을 향상시키고, 개별 전도성 특징부의 전체 전도율을 개선하고, 주파수 응답을 향상시키고, 더 얇은 특징부와 더 얇은 특징부간 공백을 갖는 더 높은 밀도의 패턴의 제조를 가능하게 한다. 유사한 이점이 또한 비-금속 물질의 패터닝된 디바이스 층, 가령, 광학 또는 절연 패터닝된 특징부를 이용하는 구성요소에서 얻어질 수 있다.

종래의 습식-에칭 공정 동안, 액상 에칭제가 에칭 마스크가 덮지 않는 영역 내에 에칭되는 디바이스 층 물질의 두께를 따라(가령, 기판 방향으로) 액상 에칭제가 전진할 때, 액상 에칭제는 또한 에칭 마스크가 덮는 디바이스 층 물질의 부분의 측방 표면(가령, 측벽)으로 측방으로 전지한다. 에칭 깊이가 증가할 때, 측벽의 더 많은 부분이 측방 에칭에 노출될수록, 에칭 마스크에 가장 가까운 측벽의 부분이, 기판에 가장 가까운 측벽의 부분보다 더 긴 시간 동안 액상 에칭제에 노출될 수 있으며, 따라서 증가된 측방 에칭의 대상이 되며, 따라서 최종 패터닝된 디바이스 층 특징부의 측벽에 언더컷 형태를 전달할 수 있다. 다시 말하면, 디바이스 층 물질의 일부분을 제거하기 위해 에칭제가 디바이스 층 물질과 반응하는 시간은 기판으로부터의 거리에 따라 증가한다. 임의의 특정 이론에 구애 받지 않고, 종래의 습식-에칭 공정에서, 침지에 의해 수행되는지 또는 에칭제를 젯 또는 분사함으로써 수행되는지 여부와 무관하게, 에칭제와 기판으로부터 디바이스 층 물질의 부분 간 추가 반응 시간이, 에칭 마스크의 의도가 이들 영역에서의 디바이스 층 물질의 제거를 방지하는 것임에도 불구하고, 에칭 마스크 특징부 바로 아래 그리고 근접한 곳에서 디바이스 층 물질의 영역에서 횡방향으로 내측으로의 디바이스 층 물질의 부식(제거)을 야기한다. 이 현상의 추가 설명 및 도시가 도 4b-5c와 관련하여 이하에서 제공된다.

본 발명에 따르는 다양한 실시예에서 언급된 바와 같이, 습식 에칭 공정 동안 에칭제와 패터닝된 디바이스 층 특징부의 측방 표면, 또는 측벽에 대응하는 디바이스 층 물질의 일부분 간 반응이 완화(가령, 감소, 방지, 억제)되어, 측방 표면 상의 언더컷 형태의 형성이 완화된다.

도 1a-5c 모두, 다양한 종래의 공정에 따라, 기판 상에 패터닝된 디바이스 층, 또는 기판 상에 패터닝된 디바이스 층 특징부를 형성하기 위해 디바이스를 처리하는 다양한 스테이지를 도시한다. 하나의 실시예에서, 디바이스는 제조 중인 PCB이고 디바이스 층 물질은 전기 전도성 물질이다. 그러나, 해당 분야의 통상의 기술자라면, PCB는 비-제한적이며 단지 예시에 불과하고 본 발명의 범위 내에 다양한 적용예, 가령, 앞서 언급된 다양한 전자 및 광학 부품이 포함됨을 알 것이다. 도 1a-1d를 참조하면, 종래의 공정에 따르는 패터닝된 디바이스 층 특징부를 형성하기 위한 공정을 겪는 디바이스(100)의 다양한 모습이 도시된다. 도 1a는 비-패터닝 디바이스 층(104)이 기판(102) 상에 배치된 때의 기판(102)을 포함하는 디바이스(100)의 평면 및 측면도이다.

기판(102)은 복수의 층, 비제한적 예를 들면, 하나 이상의 비-패터닝 또는 패터닝된 디바이스 층을 포함할 수 있다. 예를 들어, 비-패터닝 디바이스 층(104)이 기판(102)의 하나의 면(가령, 도면의 방향에서 "상부") 상에 도시되어 있지만, 이 개시내용은 또한 디바이스(100)의 "양면" 처리를 고려하며, 예를 들어, 기판(102)은 기판(102)의 대향하는 면(가령, "하부")을 포함하도록 위치하는 제2 비-패터닝 디바이스 층을 포함한다. 실시예에서, 이러한 "하부" 면의 비-패터닝 디바이스 층이 "상부" 면의 비-패터닝 디바이스 층(104)과 유사한 패터닝 공정의 대상이 되며, 이러한 "하부" 면의 패터닝은, 전적으로 또는 부분적으로, 비-패터닝 디바이스 층(104)의 "상부" 면 패터닝 전, 후, 또는 동안 발생한다. 실시예에서, 기판(102)은 하나 이상의 실시예에 따라, 비제한적 예를 들면, 비-패터닝 디바이스 층(104)을 처리하는 데 사용되는 방식와 유사한 방식으로 처리되는 하나 이상의 패터닝된 디바이스 층을 포함할 수 있다.

실시예에서, 디바이스(100)는 제조 중인 PCB이고, 비-패터닝 디바이스 층(104)은 전기 전도성 물질을 포함함으로써, 비-패터닝 전기 전도성 디바이스 층을 만들고, 기판(102)은 "상부" 전기 절연성 표면 및 "하부" 전기 절연성 표면을 제공하도록 구성된 전기 절연성 물질의 하나 이상의 층을 포함하며, 비-패터닝 전기 전도성 디바이스 층(104)은 "상부" 전기 절연성 표면에 인접하도록 위치한다. 제2 비-패터닝 전기 전도성 디바이스 층이 기판(102)에 포함되고 "하부" 전기 절연성 표면에 인접하게 위치하며(이러한 "하부" 전기 절연 표면이 기판(102) 내에 있고 도 1에 도시되지 않음), 기판(102)의 "하부" 표면, 즉, 비-패터닝 디바이스 층(104)에 인접한 표면에 대한 기판(102)의 대향하는 면 상의 표면이 제2 비-패터닝 전기 전도성 디바이스 층의 표면이다.

실시예에서, 디바이스(100)는 제조 중인 PCB이며, 기판(102)은 기판(102)과 비-패터닝 디바이스 층(104) 간 계면의 적어도 일부분을 포함하는 영역 상의 전기 절연성 표면을 가진다. 실시예에서, 기판(102)은 전기 절연성 물질의 층, 비제한적 예를 들면, 복합 물질, 가령, 에폭시 수지 도는 그 밖의 다른 물질에 의해 본딩되는 유리 섬유 직물(woven glass)을 포함할 수 있다. 이러한 전기 절연성 물질은, 예를 들어, 약 0.001 인치 내지 약 0.05 인치의 두께를 가질 수 있다. 실시예에서, 기판(102)은 전기 절연성 물질과 전기 전도성 물질의 복수의 교차 층을 포함할 수 있고, 적어도 2개의 전기 절연 층을 더 포함하고, 각각의 층은 에폭시 수지 또는 그 밖의 다른 물질에 의해 본딩되는 유리 섬유 직물을 포함하며, 0.001 인치 내지 0.05 인치의 두께를 가지며, 예를 들어, "핵심" 층 및 하나의 층은 사전-침지된(pre-impregnated) 본딩 시트("PrePreg"라고도 지칭될 수 있음)를 포함하고, 적어도 하나의 패터닝된 전기 전도성 층이 전기 절연 층들 사이에 위치하며, 비-패터닝 디바이스 층(104)과 맞대는 기판(102)의 "상부" 표면이 적어도 2개의 전기 절연성 층들 중 하나의 표면이다. 실시예에서, PrePreg는 FR4 등급 에폭시 적층 시트를 포함한다. 실시예에서, 코어 층은 FR4 등급 에폭시 적층 시트를 포함한다.

비-패터닝 디바이스 층(104)은 전도성 물질, 가령, 금속 또는 금속 합금, 비제한적 예를 들면, 구리, 알루미늄, 은, 금, 또는 해당 분야의 통상의 기술자에게 친숙한 그 밖의 다른 전도성 물질의 층을 포함할 수 있다. 실시예에서, 비-패터닝 디바이스 층(104)은 기판(102) 상으로 적층되는 구리 포일(copper foil)이고, 기판(102)과 비-패터닝 디바이스 층(104) 간 계면이 전기적으로 절연되지만, 그 밖의 다른 전도성 물질이 본 발명의 범위 내에서 고려된다.

도 1b를 참조하면, 공정의 다음 스테이지에서, 에칭 마스크(106)는 비-패터닝 디바이스 층(104)의 노출된 표면(110) 상에 형성된다. 도 1b에 도시된 바와 같이, 공정 후, 에칭 마스크(106)는 원하는 패턴(108), 가령, 패터닝된 디바이스 층 라인이 희망되는 곳에 대응하는 라인으로, 디바이스(100) 상에 형성될 수 있다. 다시 말하면, 에칭 마스크(106)는 디바이스(100) 내에서 패터닝된 디바이스 층 특징부가 희망되는 곳에 대응하는 위치에서 비-패터닝 디바이스 층(104) 위에 증착된 에칭-방지 물질을 포함할 수 있다. 에칭 마스크(106)는 물질, 가령, 폴리머, 옥사이드, 니트라이드, 또는 그 밖의 다른 물질을 포함할 수 있다. 실시예에서, 에칭 마스크 물질은 네거티브 톤 포토-레지스트 물질, 비제한적 예를 들면, 미국, MA 01581, 웨스트보로, 플랜더스 로드 200에 소재하는 Microchem Corp.가 공급하는 SU-8 시리즈의 포토레지스트 중 하나를 이용해 형성되는 폴리머이다. 실시예에서, 에칭 마스크 물질이 포지티브 톤 포토-레지스트 물질, 비제한적 예를 들면, 독일, 베를린 12555, 쾨페니케르 스트라세 325에 소재하는 micro resist technology GmbH.가 공급하는 ma-P 1200 시리즈 포토레지스트를 이용해 형성된 폴리머이다. 에칭 마스크(106)는 방법, 가령, 실크스크린 인쇄, 잉크젯 인쇄, 포토리소그래피, 그레이버 인쇄, 스탬핑, 사진제판술, 또는 그 밖의 다른 방법에 의해, 비-패터닝 디바이스 층(104)의 표면 위에 패터닝될 수 있다. 에칭 마스크(106)가 비-패터닝 디바이스 층(104)의 표면(110)에 적용된 후, 상기 디바이스(100)는 에칭 마스크(106)에 의해 보호되지 않는 영역으로부터 비-패터닝 디바이스 층(104) 내 물질을 제거하는 에칭제, 가령, 화학 에칭제에 노출됨으로써, 도 1c에 도시된 바와 같이, 패터닝된 디바이스 층(114)이 형성된다. 이러한 화학 에칭제는 비-패터닝 디바이스 층(104)의 물질에 대해 부식 효과를 가지는 화학 화합물을 포함할 수 있다. 실시예에서, 비-패터닝 디바이스 층(104)은 전기 전도성 층이고 이러한 화학 에칭제는, 비제한적으로 예를 들면, 암모늄 페르설페이트, 염화제2철, 또는 비-패터닝 디바이스 층(104)의 물질에 부식 영향을 미치는 그 밖의 다른 화학 화합물을 포함할 수 있다. 실시예에서, 비-패터닝 전기 전도성 디바이스 층(104)은 구리를 포함하고, 사용되는 에칭제는 염화 구리(CuCl2)이다. 해당 분야의 통상의 기술자라면 비-패터닝 디바이스 층(104)의 물질의 제거에 적합한 다양한 화학 에칭제에 친숙하다.

도 1c를 계속 참조하면, 비-패터닝 디바이스 층(104)이 에칭제에 노출될 때, 에칭제는 노출된 상부 표면(110)에서 시작하여, 비-패터닝 디바이스 층(104)의 물질을 용해(가령, 부식)한다. 비-패터닝 디바이스 층(104)의 물질이 제거될 때, 에칭제는, 직선이 아니고 수직인 아닌 측벽(112)을 남기면서, 에칭 마스크(106) 아래의 비-패터닝 디바이스 층(104)의 물질의 일부분을 또한 제거할 수 있다. 예를 들어, 도 1c에 도시된 바와 같이, 도 1a-1d에 나타난 공정에 따라 생산된 디바이스(100)에서, 에칭 마스크(106)의 패턴(108)에 따라 생성된 패터닝된 디바이스 층(114)의 특징부의 측벽(112)이 테이퍼형, 가령, 패터닝된 디바이스 층(114)과 에칭 마스크(106) 간 계면의 제1 특징부 폭(W1)으로부터, 기판(102)과 패터닝된 디바이스 층(114) 간 계면의, 제1 특징부 폭(W1)보다 넓은 제2 특징부 폭(W2)으로 테이퍼되는 형태를 보여줄 수 있다. 도 1d는 에칭 마스크(106)가 제거되어, 패터닝된 디바이스 층(114)을 노출시킨 후의 디바이스(100)를 보여준다. 패터닝된 디바이스 층(114)의 특징부의 측벽(112)에 의해 도 1d에 나타난 테이퍼 형태가 "언더컷"인 측벽의 하나의 예시이며, 이하에서 도 4a-4c와 관련하여 더 상세히 기재될 것이다. 언더컷 측벽의 그 밖의 다른 형태 및 배열이 또한 발생할 수 있으며 실질적으로 직선이 아니고 이들이 형성되는 기판의 표면에 실질적으로 수직으로 뻗어 있지 않는 측벽을 포함할 수 있다.

도 2a-2c를 참조하면, 전도성 라인의 패턴(208)을 갖는 에칭 마스크(206)를 형성하는 방법이 도시된다. 기판(202) 및 비-패터닝 층(204)을 갖는 디바이스(200)가 비-패터닝 디바이스 층(204)의 전체 영역 위에서 비-패터닝 에칭-방지 층(216)으로 덮인다(즉, 블랭킷 코팅된다). 그 후 비-패터닝 에칭-방지 층(216)이 패턴의 광(가령, UV 광)에 노출되어, 노출된 영역이 후속 현상 공정(이른바 네거티브-톤 공정)에서 제거되기 덜 쉬워지거나, 노출된 영역이 후속 현상 공정(이른바 포지티브-톤 공정)에서 제거되기 비교적 더 쉬워지도록 할 수 있다. 이러한 패턴-별로 광 노출을 이용하는 것이, 예를 들어, 이른바 포토리소그래피 공정에서와 같이 포토-마스크를 통해 발광함으로써, 또는 에칭-방지 층(216)으로 포커스된 광의 펄스 또는 스캔의 시퀀스를, 가령, 레이저 빔의 형태로, 시간 함수로서 패턴으로, 이른바 직접-쓰기 공정에 의해 전달함으로써, 이뤄질 수 있다. 현상 공정은 패턴별 광 노출에 대응하여 비-패터닝 에칭--방지 층(216) 물질을 제거하여, 도 2c에 도시된 바와 같이, 패턴(208)을 갖는 패터닝된 에칭 마스크(206)을 도출한다. 현상 공정은 디바이스(200)를 비-패터닝 에칭 마스크 층(216) 내 물질을 용해 또는 부식시키는 현상액에 침지시키는 단계를 포함할 수 있으며, 여기서, 비교적 제거에 더 쉬운데, 비제한적 예를 들면, 네거티브 톤 공정의 경우, 현상액은 UV 광에 노출되지 않은 비-패터닝 에칭-방지 층(216) 내 물질을 용해시킬 수 있고, 반면에, 포지티브 톤 공정의 경우, UV 광에 노출된 비-패터닝 에칭-저항 층 내 물질을 용해시킬 수 있다. 에칭 마스크(206)에 의해 보호되지 않는 비-패터닝 디바이스 층(204)의 부분의 제거가, 도 1d와 관련하여 앞서 기재된 바와 같이 진행되어, 패턴(208) 내 특징부를 갖는 패터닝된 디바이스 층을 갖고 언더컷을 보이는 디바이스(200)를 도출한다.

대안으로, 도 2a-2c의 실시예에서와 같이 비-패터닝 에칭-방지 층을 패터닝하는 중간 단계 없이, 에칭 마스크는 원하는 패턴으로 비-패터닝 디바이스 층 상에 직접 증착될 수 있다. 예를 들어, 도 3a 및 3b를 참조하면, 에칭 마스크(306)는 패터닝된 디바이스 층의 특징부가 최종 디바이스 상에서 희망되는 위치에 대응하는 라인의 희망 패턴(308)으로 직접 디바이스(300)의 비-패터닝 디바이스 층(304) 위에 형성될 수 있다. 예를 들어, 잉크젯 인쇄, 적층화, 스크린 인쇄, 그레비어 인쇄, 스탬핑, 또는 그 밖의 다른 방법에 의해, 에칭 마스크(306)는 희망 패턴(308)으로 비-패터닝 디바이스 층(304) 상에 증착될 수 있다. 하나의 실시예에서, 잉크젯 인쇄를 이용해 에칭 마스크(306)가 비-패터닝 디바이스 층(304) 위에 형성되는데, 이때, 복수의 노즐을 갖는 잉크젯 인쇄헤드가 액상 에칭-방지 잉크의 액적을 디바이스(300) 상으로 분사하며, 패턴(308)에 대응하여 액상 에칭 방지 잉크의 코팅을 형성할 수 있으며, 그 후 액상 에칭 방지 잉크의 이러한 코팅이 처리되어, 액상 코팅을 에칭 마스크(306)로 변환할 수 있다. 또 다른 실시예에서, 액상 에칭 방지 잉크의 처리는 디바이스를 건조 및/또는 베이킹하여, 액상 코팅으로부터 고체 에칭 마스크(306)를 형성하는 것을 포함한다. 하나의 실시예에서, 복수의 노즐을 포함하는 하나 이상의 인쇄헤드, 기판을 지지하는 기판 지지부, 복수의 노즐과 기판을 상대적으로 이동시키기 위한 스테이지, 기판과 노즐의 상대적 위치를 제어하기 위한 모션 제어 시스템, 및 기판 상으로 액적을 희망 패턴으로 전달하도록 노즐의 토출을 제어하기 위한 노즐 제어 시스템을 포함하는 잉크젯 인쇄기를 이용해 에칭 마스크(306)는 비-패터닝 디바이스 층(304) 위에 형성된다. 본 명세서에서, 잉크젯 인쇄가 액상 코팅을 증착하는 데 사용되는 임의의 실시예에서, 잉크젯 인쇄 시스템, 가령, 본 명세서에서 기재된 것이 사용될 수 있다.

도 4a-4c는 디바이스(400)로부터 비-패터닝 디바이스 층(404)으로부터 물질을 제거하기 위한 종래의 공정을 도시하며 언더컷을 야기하는 습식-에칭 공정 동안 발생될 것으로 여겨지는 것을 도시한다. 도 4a에서, 비-패터닝 디바이스 층(404)은 패턴(408)에 대응하여 에칭 마스크(406)로 덮인다. 그 후 디바이스(400)는 화학 에칭제(418)에 노출된다. 도 4b의 실시예에서, 에칭제(418)에 침지시킴으로써 노출이 발생한다. 에칭제(418)는 (도 4a로부터) 비-패터닝 디바이스 층(404)으로부터 물질을 제거하여, 부분적으로 패터닝된 디바이스 층(405)을 생성할 수 있다. 예를 들어, 도 4b의 실시예에서, 에칭제(418)는 용기(420)에 담긴 액체, 비제한적 예를 들면, 용액을 포함하고, 에칭 마스크(406)가 구비된 디바이스(400)(도 4b)가 도 4b에 도시된 바와 같이, 에칭제(418)에 침지된다. 비-패터닝 전도성 층(404)의 상부 표면(410)의 노출된 부분(도 4a)이 에칭되고 측벽(412)이 형성되기 시작하면, 측벽(412)이 에칭제(418)에 노출되고 에칭제(418)는 측벽(412)으로부터 물질을 제거하여, 도 4c에 도시된 패터닝된 디바이스 층(414)의 측징부의 테이퍼된 언더컷 형태를 초래한다. 달리 말하자면, 모든 방향으로 전역적으로 동작할 수 있는 에칭제(418)가, 비-패터닝 디바이스 층(404)의 상부 표면(410)이 에칭되자마자, (디바이스 층이 비-패터닝 상태(즉, 404), 부분적으로 패터닝된 상태(즉, 405), 또는 패터닝된 상태(즉, 414)인지에 무관하게) 에칭 마스크(406) 아래에서 횡방향으로 디바이스 층을 포함하는 물질을 공격한다. 에칭제(418)에 의해 제거되는 디바이스 층의 물질량이 디바이스 층의 물질이 에칭제(418)에 노출되는 시간에 따라 달라질 수 있다. 따라서, 에칭제(418)가 부분 패터닝된 디바이스 층(405)의 두께를 통해 (즉, 기판(402)의 평면에 수직인 방향으로) 전진함에 따라, 에칭 마스크(406)에 더 가까운 측벽(412)의 부분이, 기판(402)에 더 가까운 측벽(412)의 부분보다 더 긴 시간 동안 에칭제(418)에 노출되고, 이에 따라 에칭 공정은 도 4c에 도시된 바와 같은 테이퍼된(즉, 언더컷) 형태를 측벽(412)에 부여할 수 있다. 다시 말하면, 디바이스 층으로부터 이러한 물질을 제거하기 위해 에칭제가 디바이스 층 내 물질과 반응하는 시간이 기판으로부터의 거리에 따라 증가한다. 임의의 특정 이론에 구애 받지 않고, 에칭 마스크의 의도가 이들 영역에서 디바이스 층의 물질의 제거를 방지하는 것임에도 불구하고, 에칭제와 기판으로부터 먼 디바이스 층의 부분의 물질 간 추가 반응 시간이 에칭 마스크 바로 아래 그리고 이에 근접한 디바이스 층의 영역에서 횡방향으로 내측으로 디바이스 층으로부터의 물질의 부식(제거)을 야기한다.

지금부터 도 5a-5c를 참조하면, 또 다른 종래의 공정의 실시예가 도시된다. 도 5a-5c의 공정은 도 4a-4c와 관련하여 기재된 것과 유사하며, 도 5a에 도시된 바와 같이, 디바이스(500)의 비-패터닝 디바이스 층(504) 위에 에칭 마스크(506)를 형성하는 것을 포함한다. 에칭제(518) 내에 디바이스(500)를 침지하는 것 대신, 도 4b와 관련하여 앞서 기재된 바와 같이, 에칭제(518)가 도 5b에 도시된 바와 같이, 용기(520) 내에 있을 수 있는 디바이스(500)에 영향을 미치는 제트(522)로 도입된다. 과량의 에칭제(518)는 용기(520)의 배수구(524)로 흐르거나, 가령, 재순환 또는 그 밖의 다른 처리를 위한 그 밖의 다른 방식으로 수집될 수 있다. 에칭제(518)가 전방향으로 동작하기 때문에, 도 5c에 도시된 바와 같이, 테이퍼 또는 언더컷이 패터닝된 디바이스 층(514)의 특징부의 최종 측벽(512) 상에 형성된다.

앞서 언급된 바와 같이, 디바이스 상에 형성되는 패터닝된 디바이스 층의 특징부의 언더컷 측벽이 형성될 수 있는 특징부의 크기 및 형태를 다양하게 제한할 수 있다. 예를 들어, 앞서 언급된 바와 같이, 언더컷이 형성되는 경향이 제작될 수 있는 최소 특징부 폭 또는 최소 특징부간 공백에 제한을 둘 수 있음으로써, 디바이스 상의 특징부 밀도를 제한할 수 있다. 다양한 적용예에서, 디바이스 상의 특징부 밀도를 최대화하는 것이 성능을 개선한다. 다양한 실시예에서, 디바이스 층은 전기 전도성 물질을 포함하고, 디바이스는 PCB이며, 언더컷 경향이 최소 특징부 폭, 최소 특징부간 공백, 및 최대 특징부 밀도를 제한할 수 있다.

도 6a-17은 종래 공정 동안 발생하는 언더컷을 완화(가령, 감소 또는 제거)하기 위한 공정의 다양한 실시예를 보여준다. 예를 들어, 도 6a를 참조하면, 디바이스(600)는 기판(602) 위의 비-패터닝 디바이스 층(604)을 가진다. 화학 기상 증착, 물리 기상 증착, 적층화, 슬롯 다이 코팅, 스핀 코팅, 잉크젯 인쇄, 스크린 인쇄, 노즐 인쇄, 그레비어 인쇄, 로드 코팅, 또는 해당 분야의 통상의 기술자에게 친숙한 그 밖의 다른 임의의 적합한 방법에 의해, 비-패터닝 디바이스 층(604)은 기판에 인가될 수 있다. 내부식성 층(629) 위에 에칭 마스크(628)를 형성하기 전에 비-패터닝 디바이스 층(604)은 내부식성 층(629)으로 코팅된다. 화학 기상 증착, 물리 기상 증착, 적층화, 슬롯 다이 코팅, 스핀 코팅, 잉크젯 인쇄, 스크린 인쇄, 노즐 인쇄, 그레비어 인쇄, 로드 코팅, 또는 해당 분야의 통상의 기술자에게 친숙한 그 밖의 다른 임의의 적합한 방법에 의해, 내부식성 층(629)은 기판에 인가될 수 있다. 일부 실시예에서, 내부식성 층(629)은 "프라이머(primer)" 층을 포함하고, 프라이머 층 상으로, 후속 공정, 비제한적 예를 들면, 건조 또는 베이킹을 통해 에칭 마스크(628)로 변환되는 액상 에칭-방지 잉크를 증착시킴으로써 에칭 마스크(628)가 형성된다. 다양한 실시예에서, 앞서 기재된 바와 같이, 이러한 액상 에칭-방지 잉크가 잉크젯 인쇄를 통해 액적의 형태로 디바이스(600)로 전달될 수 있으며, 이러한 액적이, 프라이머 표면과 접촉할 때 빠르고 효과적으로 제위치에서 부동화 또는 "동결"되어 프라이머 표면 상의 잉크 액적의 추가 이동 또는 확산이 크게 감소 또는 전반적으로 중단될 수 있는 방식으로 내부식성 층(629)과 상호작용할 수 있으며, 이는 앞서 참조로서 포함되는 국제 특허 공개 번호 WO2016/193978 A2 및 WO2016/025949 A1에서 더 언급되어 있다. 이러한 액상 에칭-방지 잉크는 이러한 프라이머 층과의 상호작용을 통해 에칭 방지 마스크를 적어도 부분적으로 형성하는 2-성분 물질을 더 생성할 수 있다.

다양한 실시예에서, 도 6a를 참조하면, 디바이스(600)는 PCB이며, 비-패터닝 디바이스 층(604)는 전기 전도성 물질, 가령, 구리, 알루미늄, 금, 및/또는 그 밖의 다른 금속을 포함하며, 비-패터닝된 전기 전도성 디바이스 층(604)에 인접한 기판(602)의 표면이 전기 절연성이다.

실시예에서, 내부식성 층(629)은 디바이스(600)의 비-패터닝 디바이스 층(604)의 물질을 제거하는 데 사용되는 화학 에칭제의 부식 효과를 지연시키는 능력을 기초로 선택된 물질을 포함할 수 있다. 비제한적 예를 들면, 내부식성 층(629)은, 비제한적으로, 폴리머, 유기 화합물, 가령, 하나 이상의 -이민 기, 하나 이상의 -아민 기, 하나 이상의 -아졸 기, 하나 이상의 -히드라진 기, 하나 이상의 아미노산, 시프 염기, 또는 그 밖의 다른 물질을 포함하는 유기 화합물을 포함할 수 있다. 또 다른 실시예에서, 내부식성 층(629)은 무기 물질, 가령, 크로메이트, 몰리브데이트, 테트라보레이트, 또는 또 다른 무기 화합물을 포함할 수 있다. 일부 실시예에서, 내부식성 층(629)은 반응 성분, 가령, 폴리양이온 및/또는 다가 양이온을 포함하는 하나 이상의 반응 양이온 기를 포함할 수 있다. 양이온 반응 성분이 금속 표면, 가령, 구리 표면에 부착될 수 있다.

일부 실시예에서, 임의의 알려진 도포 방법, 비제한적 예를 들면, 분사, 스핀 코팅, 노즐 인쇄, 로드 코팅, 스크린 인쇄, 스미어링(smearing), 잉크-젯 인쇄 등을 이용해 액상 내부식성 잉크를 비-패터닝 디바이스 층 위에 도포하고, 액상 코팅을 내부식성 층(629)으로 변환하도록 디바이스(600)를 처리함으로써 내부식성 층(629)은 형성될 수 있다. 일부 실시예에서, 내부식성(629)은 프라이머 층으로 지칭될 수 있으며, 액상 내부식성 잉크가 프라이머 잉크로 지칭될 수 있다. 액상 내부식성 잉크는 낮은 또는 높은 분자 중량을 갖는 폴리-이민, 가령, 폴리에틸렌이민, 가령, 선형 폴리에틸렌이민 또는 분지 폴리에틸렌이민을 포함할 수 있는 용액을 포함할 수 있다. 비제한적 예를 들면, 분자 중량은 약 800 내지 약 2,000,000일 수 있다.

일부 실시예에서, 액상 내부식성 잉크 젯 가능한 인쇄헤드를 만들기 위해, 액상 잉크가 추가 에이전트, 가령, 프로필렌 글리콜, n-프로판올 및 습윤제(가령, Evonik Industries가 공급되는TEGO 500)를 포함할 수 있는 수용액일 수 있다.

일부 실시예에서, 내부식성 물질 층(629)의 두께가 약 0.03 ㎛ 내지 약 1.1 ㎛의 범위일 수 있다. 일부 실시예에서, 상기 방법은 고체 코팅을 형성하기 위해 임의의 건조 방법을 이용하여 도포된 잉크를 건조하는 단계를 포함할 수 있다. 일부 실시예에서, 상기 방법은 고체 코팅을 형성하기 위해 임의의 건조 방법을 이용하여 도포된 잉크를 베이킹하는 단계를 포함할 수 있다.

또 다른 비제한적 예시로서, 내부식성 물질 층(629)의 양이온 반응 성분이 다양한 pH 레벨의 폴리아미드, 가령, 폴리에틸렌이민, 폴리-4급 아민, 긴-사슬 4급 아민, 폴리-3급 아민 및 다가 무기 양이온, 가령, 마그네슘 양이온, 아연 양이온, 칼슘 양이온, 구리 양이온, 제2철 양이온, 및 제1철 양이온을 포함할 수 있다. 폴리머 성분이 용해 성분 또는 유제 형태로 제제에 도입될 수 있다.

임의의 적합한 인쇄 또는 코팅 방법, 비제한적 예를 들면, 잉크젯 인쇄, 분사, 측량 로드 코팅, 롤 코팅, 딥 코팅, 스핀 코팅, 스크린 인쇄, 적층화, 스탬핑 등을 이용해 내부식성 물질 층(629)은 비-패터닝 디바이스 층(604)에 도포될 수 있다. 내부식성 층(629)이 비-패터닝 디바이스 층(604) 위에 균일하게 도포되거나, 원하는 패턴으로, 가령, (도 6에 따르는) 패터닝된 디바이스 층(630)의 원하는 패턴을 형성하는 패턴(608)으로 도포될 수 있다.

도 6a-6d의 실시예에서, 내부식성 층(629)은 "프라이머(primer)" 층을 포함하고, 프라이머 층 상으로, 후속 공정, 비제한적 예를 들면, 건조 또는 베이킹을 통해 에칭 마스크(628)로 변환되는 액상 에칭-방지 잉크를 증착시킴으로써 에칭 마스크(628)가 형성된다. 다양한 실시예에서, 이러한 건조하는 것은, 비제한적 예를 들면, 70 ℃ 이상에서 베이킹하는 것을 포함할 수 있다. 다양한 실시예에서, 앞서 기재된 바와 같이, 이러한 액상 에칭-방지 잉크가 잉크젯 인쇄를 통해 액적의 형태로 디바이스(600)로 전달될 수 있으며, 이러한 액적이 프라이머 표면과 접촉할 때 빠르고(가령, 마이크로초 단위로) 효과적으로 제위치에서 부동화 또는 "동결"되어 프라이머 표면 상의 잉크 액적의 추가 이동 또는 확산이 크게 감소 또는 전반적으로 중단될 수 있는 방식으로 프라이머 층과 상호작용할 수 있으며, 이는 앞서 참조로서 포함되는 국제 특허 공개 번호 WO2016/193978 A2 및 WO2016/025949 A1에서 더 언급되어 있다. 이러한 액상 에칭-방지 잉크는 이러한 프라이머 층과의 상호작용을 통해 에칭 마스크를 적어도 부분적으로 형성하는 2-성분 물질을 더 생성할 수 있다.

에칭 마스크(628), 또는 (앞서 기재된 다양한 실시예에 따라) 이러한 에칭 마스크(628)를 만드는 데 사용되는 액상 에칭-방지 잉크가 수용성이고 음이온 기를 포함할 수 있는 폴리머 성분을 포함할 수 있다. 음이온 폴리머가 아크릴 수지 및 스티렌-아크릴 수지의 용해된 염 형태로부터 선택될 수 있다. 음이온 폴리머는 술폰 수지의 용해된 염 형태, 가령, 소듐, 암모늄- 또는 아민- 중성화된 형태로부터 선택될 수 있다. 액상 에칭 방지 잉크를 이용하는 실시예에서, 액상 잉크는 물질의 인쇄 또는 그 밖의 다른 증착 품질을 개선하기 위한 추가 에이전트를 포함할 수 있다.

에칭 마스크(628), 또는 (앞서 기재된 특정 실시예에 따라) 이러한 에칭 마스크(628)를 만드는 데 사용되는 액상 에칭-방지 잉크가 수용성일 수 있고 반응성 음이온 기를 포함할 수 있는 반응 성분을 포함할 수 있다. 음이온 반응 성분의 비제한적 예시는 7.0 pH 이상의 (염기 형태의) 적어도 하나의 음이온 폴리머를 포함할 수 있다. 음이온 폴리머가 아크릴 수지 및 스티렌-아크릴 수지의 용해된 염 형태로부터 선택될 수 있다. 음이온 폴리머는 술폰 수지의 용해된 염 형태, 비제한적 예를 들면, 소듐 염 형태, 암모늄 또는 아민 중성화된 형태뿐 아니라 폴리머 에멀전 또는 분산으로부터 선택될 수 있다. 폴리머 성분이 용해 성분 또는 유제 형태로 제제에 도입될 수 있다.

도 6b를 참조하면, 내부식성 층(629) 및 에칭 마스크(628)가 디바이스(600) 상에 직접 인쇄될 수 있다. 하나의 실시예에서, 내부식성 층(629)은 비-패터닝 디바이스 층(604) 위에 희망 패턴, 가령, 패턴(608)으로 인쇄함으로써 형성되어, (도 6에서와 같은) 대응하는 패터닝된 디바이스 층(630)의 제조를 촉진시킬 수 있다. 내부식성 층(629)은 약 5 nm 내지 약 100 nm, 약 100 nm 이하, 또는 약 1 ㎛ 이하의 두께로 증착될 수 있다. 내부식성 물질 층(629)의 그 밖의 다른 두께가 본 발명의 범위 내에서 고려되고 특정 적용예에 따라 달라질 수 있다. 그 후 에칭 마스크(628)가 내부식성 물질 층(629) 위에 원하는 패턴, 가령, 패턴(608)으로 인쇄함으로써 형성되어, (도 6에서와 같이) 대응하는 패터닝된 디바이스 층(630)의 제조를 촉진시킬 수 있다. 에칭 마스크(628)는, 예를 들어, 약 1 ㎛ 내지 약 5 ㎛, 또는 약 5 ㎛ 이하, 또는 약 15 ㎛ 이하의 두께를 갖도록 증착될 수 있다.

그 후 디바이스(600)는 에칭제, 가령, 도 4b 및 5b와 관련하여 기재된 바와 같이 액상 화학 에칭제(418 또는 518)로 도입된다. 내부식성 물질 층(629)의 존재는, 도 6c 및 6d에 도시된 바와 같이, 패터닝된 디바이스 층(630)의 특징부의 언더컷 크기의 감소에 기여할 수 있다. 예를 들어, 패터닝된 디바이스 층(630)의 특징부가 내부식성 층(629)에 근접한 제1 폭 W1, 및 기판(602)에 근접한 제2 폭 W2을 보여줄 수 있다. 일부 실시예에서, 폭 W1과 폭 W2 간 차이가 테이퍼형 측벽(632)을 나타내는 패터닝된 디바이스 층(630)의 특징부를 도출한다(즉, 패터닝된 디바이스 층(630)의 특징부가 약간의 언더컷을 보일 수 있다). 패터닝된 디바이스 층(630)의 특징부에 의해 나타난 언더컷이 앞서 언급된 패터닝된 디바이스 층(114, 414)(도 1d 및 4d)의 특징부에 의해 나타내어지는 언더컷보다 작을 수 있다. 도 10 및 11과 관련하여 이하에서 더 상세히 언급된 바와 같이, 언더컷의 정도를 정량화하기 위해 다양한 측정치가 사용될 수 있다.

도 7a-7c의 실시예에서, 내부식성 층(729)이 기판(702) 상에 배치된 비-패터닝 디바이스 층(704)의 표면 위에 증착되는 블랭킷이다. 이러한 블랭킷 코팅은 방법, 비제한적 예를 들면, 화학 기상 증착, 물리 기상 증착, 적층화, 잉크젯 인쇄, 분사, 계량 로드 코팅, 롤 코팅, 딥 코팅, 스핀 코팅, 스크린 인쇄, 노즐 인쇄, 또는 그 밖의 다른 방법에 의해 이뤄질 수 있다. 에칭 마스크(728)는 내부식성 층(729) 위에 희망 패턴, 가령, 앞서 다양한 실시예와 관련하여 설명된 바와 같이, 패턴(708)으로 형성될 수 있다. 방법은 앞서 기재된 도 6a-6c의 실시예와 유사하게 진행된다. 예를 들어, 내부식성 층(729) 및 에칭 마스크(728)를 갖는 디바이스(700)는 에칭제, 가령, 도 4b 및 5b와 관련하여 기재된 에칭제(418 또는 518)에 노출된다. 도 7b에 도시된 바와 같이, 디바이스(700)는 용기(720) 내에 위치하고, 에칭제(718)는 에칭 마스크(728)가 배치되는 디바이스(700)의 표면 위에 젯팅된다. 에칭제(718)는 비-패터닝 디바이스 층(704)의 표면으로부터 내부식성 층(729)을 제거하고, 도 7b에 도시된 바와 같이 에칭제(718)에 의해 제거되는 비-패터닝 디바이스 층(704)의 물질을 노출시킴으로써, 종래의 공정에 따라 생성된 패터닝된 디바이스 층(114, 414)과 연관된 측벽(112)과 비교할 때 감소된 언더컷 정도를 보여주는 측벽(732)을 갖는 패터닝된 디바이스 층(730)을 형성할 수 있다. 부분적으로 패터닝된 디바이스 층(705)은, 에칭 마스크를 통해 노출된 영역으로부터 내부식성 층(729)이 제거되고 디바이스 층 자체의 물질 중 일부가 에칭된 후, 에칭이 패터닝된 디바이스 층(730)을 형성하도록 충분히 진행되기 전의 디바이스 층의 중간 상태를 반영한다.

지금부터 도 8a-8d를 참조하여, 도 7a-7c의 실시예의 공정의 일부분의 더 상세한 도시가 나타난다. 도 8a에서, 에칭제(가령, 도 7b의 에칭제(718))의 제트(822)가 기판(802) 상의 비-패터닝 디바이스 층(804) 상에 증착되는 내부식성 층(829) 및 에칭 마스크(828)의 표면에 영향을 미친다. 내부식성 층(829)은 디바이스 층의 물질의 표면에 부착되는 것이 바람직하며, 에칭제(718)에 적어도 부분적으로 용해 가능할 수 있지만, 에칭-방지 물질(828)은 에칭제(718)에서 실질적으로 불용성일 수 있다. 도 8b에 도시된 바와 같이, 에칭제(718)의 제트(822)가 에칭 마스크를 통해 노출된 영역에서 비-패터닝 디바이스 층(804)으로부터 내부식성 층(829)을 제거하기에 충분한 운동 에너지를 포함할 수 있으며, 따라서 도 8c에 도시된 바와 같이, 에칭제(718)는 에칭-방지 물질(828)에 의해 덮이지 않는 비-패터닝 디바이스 층(804)의 물질을 제거하기 시작하고 부분적으로 패터닝된 디바이스 층(805)을 형성할 수 있다. 도 8d는 부분 패터닝된 디바이스 층(805)이 패터닝된 디바이스 층(830)을 형성하는 데 충분히 에칭된 후의 디바이스(800)를 도시한다. 도 8d에서 도시된 바와 같이, 패터닝된 디바이스 층(830)은 도 1a-5c와 관련하여 기재된 종래의 공정에 따라 생성된 측벽보다 언더컷을 덜 보이는 측벽(832)을 가진다. 도 8d에서 패터닝된 디바이스 층(830)이 약간의 언더컷을 가진 것으로 도시되지만, 본 발명은 실질적으로 어떠한 언더컷도 없는 (즉, 실질적으로 직선이고 기판(802)의 표면에 수직으로 뻗어 있는) 패터닝된 디바이스 층(가령, 전도성) 특징부를 고려한다.

이제 도 9a-9c를 참조하면, 디바이스(900) 상의 패터닝된 디바이스 층(930)을 형성하기 위한 공정의 또 다른 실시예가 도시된다. 기판(902) 위에 배치되는 비-패터닝 디바이스 층(904)이 내부식성 층(929) 및 에칭 마스크(928)로 마스킹된다. 디바이스(900)가 에칭제(918)를 갖는 용기(920) 내로 도입되어, 도 9b에서와 같이 디바이스가 에칭제(918) 내에 침지될 수 있다. 도 9c에 도시된 바와 같이, 디바이스(900)의 최종 패터닝된 디바이스 층(930)은 종래의 공정과 연관된 전도성 특징부(114)(도 1d)에 의해 나타내어지는 언더컷보다 작은 언더컷의 정도를 보이는 측벽(932)을 가진다.

이하에서 도 10을 참조하여, 도 1a-5c의 종래의 방법과 관련하여 언급된 디바이스(100)의 확대도가 나타난다. 도 10에서, 패터닝된 디바이스 층(114)의 특징부가 에칭 마스크(106)와 패터닝된 디바이스 층(114)의 계면과 패터닝된 디바이스 층(114)과 기판(102) 간 계면 사이에 뻗어 있는 테이퍼형 측벽을 나타낸다. 패터닝된 디바이스 층 특징부(114)는 패터닝된 디바이스 층(114)과 에칭 마스크(106)의 계면에서의 제1 폭 W1 및 패터닝 디바이스 층(114)과 전기 절연성 기판(102)의 계면에서의 제2 폭 W2를 나타낸다. 도 10은 예시 목적으로 도시되며 프로파일의 변형이 발생될 수 있지만, 일반적으로, 패터닝된 디바이스 층(114)은 에칭-방지 물질과의 계면보다 기판과의 계면에서 더 높은 폭을 가진다. 에칭 마스크(106)는 본 개시내용에서 폭 W2보다 크거나, 작거나, 동일한 것으로 고려되는 폭 W3을 가진다.

지금부터 도 11을 참조하면, 도 6a-9c에서 도시된 디바이스(600, 700, 800, 또는 900)와 유사한 디바이스(1100)의 확대도가 도시된다. 이 실시예에서, 패터닝된 디바이스 층(1130)의 특징부가 패터닝된 디바이스 층(1130)과 내부식성 층(1129) 간 계면에서의 제1 폭 W1, 및 패터닝된 디바이스 층(1130)과 기판(1102) 간 계면에서의 제2 폭 W2를 보인다. 에칭 마스크(1128)는 본 개시내용에서 폭 W2보다 크거나, 작거나, 동일한 것으로 고려되는 폭 W3을 가진다.

언더컷의 정도에 대한 예시적 척도가 에칭 계수 F이며, 이는 패터닝된 디바이스 층의 특징부의 가장 넓은 부분과 가장 좁은 부분의 폭의 차와 패터닝된 디바이스 층의 특징부의 높이의 비이다. 따라서, 에칭 계수 F는 H/X로 정의되며 여기서 H는 라인의 높이(H)이고 X는 (W2-W1)/2, 즉, 바닥 부분 폭(W2)과 상부 폭(W1) 간 차이를 2로 나눈 값과 동일하다. 도 11은 H와 X가 관계를 그래픽으로 나타낸다. 본 발명의 패터닝된 디바이스 층의 특징부에 대한 에칭 계수 F의 예시적 값이 예시 1-3로 이하에서 설명된다. 비-제한적 예를 들면, 본 발명의 다양한 예시적 실시예에 따라 제작된 디바이스와 연관된 디바이스 층의 특징부가 2 초과, 5 초과, 7 초과, 가령, 10 초과, 20 초과 등의 에칭 계수 F를 보여줄 수 있다. 또 다른 예를 들면, 수직 라인에 접근하는(즉, 어떠한 언더컷도 보이지 않는) 측벽을 갖는 전도성 특징부의 에칭 계수 F가 X의 값이 0에 근사함에 따라 무한에 근사할 것이다. 표면 프로파일, 단면, 및 필름 두께를 측정하는 다양한 마이크로스코피(microscopy) 기법, 비제한적 예를 들면, 표면 프로필로메트리(surface profilometry), 스캐닝 전자 마이크로스코피, 엘립소메트리, 및 공초점 마이크로스코피를 이용해 H, W1, 및 W2의 측정치가 수행될 수 있다.

특정 이론에 구애 받지 않고, 본 발명자는 내부식성 물질 층의 일부분이 층으로부터 분리되고 에칭 공정 동안 에칭 마스크 아래의 디바이스 층의 측벽에 부착 및/또는 흡착되어 언더컷을 완화시킬 수 있음을 알았다. 도 12a 및 12b는 이러한 현상을 도시한다.

도 12a는 본 발명의 다양한 실시예에 따라 패터닝 공정에서 중간 처리 단계 동안 디바이스(1200)의 단면도를 도시한다. 도시된 바와 같이, 기판(1202) 상의 부분 패터닝된 디바이스 층(1205)은 에칭 공정을 겪는 중이다. 도 12b는 부분 패터닝된 디바이스 층(1205)의 측벽(1232)과 내부식성 층(1229) 간 계면에서의 도 12a의 부분의 확대도를 도시한다. 도 12b에 도시된 바와 같이, 디바이스(1200)가 에칭제(1218)에 노출될 때, 에칭제(1218)의 작용 때문에, 비제한적 예를 들면, 내부식성 층을 부분적으로 용해시킴으로써, 내부식성 물질을 포함하는 내부식성 층(1229)의 일부분(1246)이 내부식성 층(1229)으로부터 분리되고, 이러한 내부식성 물질이 측벽(1232) 상으로 부착 및/또는 흡착되도록 이동된다. 달리 말하면, 에칭제(1218)의 존재가 에칭 공정 동안 내부식성 물질을 포함하는 내부식성 층(1220)의 일부분(1246)의 내부식성 물질 층(1229)으로부터 부분 패터닝된 디바이스 층(1230)의 측벽(1232)으로의 이동을 촉진시킬 수 있다. 그 후 측벽(1232) 상의 내부식성 물질 부분(1246)의 존재가 측벽(1232) 상의 에칭제(1218)의 부식 작용을 억제할 수 있음으로써, 최종 패터닝된 디바이스 층(1230)에서 보여지는 언더컷의 크기를 감소(가령, 감소 또는 제거)할 수 있다. 다양한 실시예에서, 적어도 2개의 공정이 이들 현상에 기여하는데, 하나의 공정에서 내부식성 물질이 에칭제에 의해 용해되고 또 다른 동시 공정에서, 에칭제에서 용해되는 내부식성 물질이 측벽(1232)에 흡착 및/또는 부착된다. 다양한 실시예에서, 제1 공정 및 제2 공정의 비가 최종 언더컷의 크기를 감소(가령, 감소 또는 제거)하기 위한 에칭 공정 동안 내부식성 물질 부분(1246)이 형성 및 유지되도록 정해진다.

도 12b에 도시된 바와 같이, 측벽(1232)에 흡착되는 내부식성 물질(1246)의 일부분이 일반적으로 테이퍼된 형태를 나타낼 수 있으며, 여기서, 내부식성 물질의 부착 및/또는 흡착된 층(1246)이 내부식성 물질 층(1229) 가까이에서 더 큰 두께를 나타내고 내부식성 물질 층(1229)으로부터 기판 방향으로 층(1246)을 따라 감소하는 두께를 나타낸다.

도 13a, 13b 및 13c는 내부식성 물질의 입자(1348)가 내부식성 층(1329)으로부터 분리되어 디바이스(1300)의 부분 패터닝된 디바이스 층(1305)의 측벽(1332) 상에 부착 및/또는 흡착되는 공정의 추가 예시를 보여준다. 도 13b 및 13c는 내부식성 물질 층(1329)과 부분 패터닝된 디바이스 층 측벽(1332) 간 계면의 확대도를 도시한다. 도 13b에서 도시된 바와 같이, 내부식성 물질의 입자(1348)는 내부식성 물질 층(1306)으로부터 분리된다. 도 13c에서, 분리된 입자(1348)가 부분 패터닝된 디바이스 층(1305)의 측벽(1332) 상에 부착 및/또는 흡착된다. 분리된 입자(1348)는 일반적으로 내부식성 물질 층(1329)으로부터 멀어지는 방향으로 두께가 감소하는 패턴으로 측벽(1332) 상으로 부착 및/또는 흡착될 수 있다. 다양한 경우에서, 분리된 입자(1348)는 실질적으로 고른 패턴, 실질적으로 랜덤 패턴, 또는 그 밖의 다른 일부 패턴으로 측벽(1332)에 흡착 및/또는 부착될 수 있다. 측벽(1332) 상의 입자(1348)의 존재가 에칭제(1318)의 작용을 억제하고 에칭 공정 동안 부분 패터닝된 디바이스 층(1305) 상에서 발생하는 언더컷을 완화(가령, 감소 또는 제거)할 수 있다. 도 12를 참조하여 앞서 기재된 바와 같이 다양한 실시예에서, 적어도 2개의 공정이 이들 현상에 기여하는데, 하나의 공정에서 내부식성 물질이 에칭제에 의해 용해되고 또 다른 동시 공정에서, 에칭제에서 용해되는 내부식성 물질이 측벽(1232)에 흡착 및/또는 부착되고, 다양한 실시예에서, 제1 공정과 제2 공정의 비는, 에칭 공정 동안 관찰되는 언더컷의 크기를 감소(가령, 감소 또는 제거)하도록 내부식성 물질 부분(1346)이 형성되고 유지되도록 정해진다.

도 14는 디바이스, 비제한적 예를 들면, 본 발명에 따르는 전기 또는 광학 부품 또는 디바이스를 형성하기 위한 작업 흐름(1400)의 실시예를 나타내는 흐름도이다. (1402)에서, 비-패터닝 디바이스 층이 기판 상에 준비된다. 예를 들어, 비-패터닝 디바이스 층, 가령, 전도성 필름이 기판의 전기 절연 표면 상으로 적층화, 또는 그 밖의 다른 방식을 증착된다. (1404)에서, 비-패터닝 디바이스 층 상에 내부식성 층을 증착하고 내부식성 물질 위에 에칭 마스크를 증착함으로써, 언더컷 방지 에칭 마스크가 형성된다. 예를 들어, 내부식성 물질을 함유하는 액상 프라이머 잉크가 기판 상으로 코팅되고 그 후 건조되어 내부식성 프라이머 층을 형성하는 블랭킷이고, 액상 에칭 마스크 잉크가 내부식성 프라이머 층 상으로 인쇄되고 그 후 건조되어 에칭 마스크를 형성할 수 있다. 프라이머 층과 에칭 마스크는 함께 언더컷 방지 에칭 마스크를 형성한다. 언더컷 방지 에칭 마스크는 상기 실시예에서 언급된 내부식성 층(가령, 내부식성 층(629, 729, 829, 929, 1129 1229, 또는 1329)) 및 에칭 마스크(가령, 에칭 마스크(628, 728, 828, 또는 928))를 포함할 수 있다. 프라이머 층과 액상 에칭 마스크 잉크는, 앞서 기재된 바와 같이, 상호작용하여 2-성분 물질을 형성할 수 있다. 프라이머 층과 액상 에칭 마스크 잉크는, 앞서 기재된 바와 같이, 상호작용하여, 잉크를 프라이머 표면 상에서 효과적으로 부동화 또는 동결시킬 수 있다. (1406)에서, 습식 에칭이 수행되어 에칭 마스크가 덮지 않는 비-패터닝 디바이스 층의 영역(즉, 비-패터닝 디바이스 층의 노출된 부분)을 제거할 수 있다. 습식 에칭이 비-패터닝 디바이스 층의 노출된 부분을 제거하기에 충분한 지속시간 동안 수행되어, 에칭 마스크가 덮는 특징부에 대응하는 패터닝된 디바이스 층을 남길 수 있다. (1408)에서, 가령, 디바이스를 에칭 마스크를 용해 및 제거하여 상기 디바이스 상의 최종 패터닝된 디바이스 층을 노출시키는 박리 유체(stripping fluid)의 스트림에 침지하거나 상기 디바이스에 상기 박리 유체의 스트림을 분사함으로써, 에칭 마스크는 박리된다. 다양한 실시예에서, 박리 공정은 또한 에칭 마스크 아래의 내부식성 층을 제거한다.

도 15는 앞서 (1404)와 관련하여 기재된 바와 같이, 본 발명에 따르는 기판 상에 언더컷 방지 에칭 마스크를 형성하기 위한 흐름도(1500)의 실시예를 상세히 보여주는 흐름도이다. (1502)에서, 내부식성 층, 가령, 내부식성 층(629, 729, 829, 929, 1129 1229, 또는 1329)이 비-패터닝 디바이스 층이 있는 기판 상에 형성된다. 도 15의 실시예에서, 내부식성 층이 비-패터닝 디바이스 층의 전체 표면 위에 블랭킷 코팅(즉, 비-패터닝 층)으로서 형성된다. (1504)에서, 에칭 마스크, 가령, 에칭 마스크(628, 728, 828, 또는 928)가 블랭킷 코팅에서 내부식성 층의 표면 위에 형성된다. (1506)에서, 가령, 도 2a-2c와 관련하여 일반적으로 앞서 언급된 바와 같이 UV 광의 패턴에 노출시킴으로써, 에칭 방지 물질이 직접 쓰기 노출된 또는 광-노출된다. (1508)에서, 에칭 방지 물질이 현상되어, 가령, UV 광에 노출되지 않거나(네거티브 톤 공정의 경우) UV 광에 노출된(포지티브 통 공정의 경우) 에칭 방지 물질을 제거함으로써, 패터닝된 에칭 마스크를 형성할 수 있다.

도 16은 본 발명에 따르는 기판 상에 언더컷 저항 에칭 마스크를 형성하기 위한 흐름도(1600)의 또 다른 실시예를 보여주는 흐름도이다. (1602)에서, 내부식성 층(가령, 내부식성 층(629, 729, 829, 929, 1129 1229, 또는 1329))이 비-패터닝 디바이스 층을 갖는 기판 위에 비-패터닝 디바이스 층 위의 블랭킷 코팅으로 형성된다. (1604)에서, 패터닝된 에칭 마스크(가령, 에칭 마스크(628, 728, 828, 또는 928))가 비-패터닝 내부식성 코팅 위에 제조된다.

도 17은 본 발명에 따르는 디바이스를 형성하는 흐름도(1700)의 또 다른 실시예를 보여주는 흐름도이다. (1702)에서, 비-패터닝 디바이스 층, 비제한적 예를 들면, 구리 필름이 기판의 전기 절연 표면 상으로 적층된다. (1704)에서, 내부식성 층(가령, 내부식성 층(629, 729, 829, 929, 1129, 1229, 또는 1329))이 구리 필름 위에 블랭킷 코팅으로 형성된다. (1706)에서, 블랭킷-코팅된 내부식성 물질 위에 희망 패턴으로 액상 에칭-방지 잉크를 인쇄하고 액체를 건조하여 에칭 마스크를 형성함으로써 에칭 마스크(가령, 에칭 방지 마스크(628, 728, 828, 또는 928))가 제조된다. (1708)에서, 분사-유형 습식 에칭이 수행되어 에칭 마스크 물질에 의해 덮이지 않는 구리 필름의 영역을 에칭할 수 있다. (1710)에서, 에칭 마스크가 구리 필름의 나머지 부분으로부터 박리되어 형성된 전도성 특징부를 노출시킬 수 있다. 다양한 실시예에서, 내부식성 층은 프라이머 층이고, 액상 에칭-방지 잉크는 잉크젯 노즐에 의해 전달되는 액적의 형태로 표면에 도포될 수 있고, 프라이머 표면과 접촉되면, 비제한적 예를 들어, 에칭 방지 잉크와 프라이머 층 간 상호작용에 의해 트리거되는 화학 반응으로 인해, 이러한 액적은 곧(가령, 마이크로초 수준으로) 효과적으로 제위치에 부동화되거나 "동결"되어, 프라이머 표면 상의 잉크 액적의 추가 이동 또는 확산이 크게 감소 또는 전체적으로 중단되며, 국제 특허 번호 WO2016/193978 A2 및 WO2016/025949 A1에 기재되어 있다. 다양한 실시예에서, 프라이머 층과 액상 에칭 마스크는 상호작용하여 2-성분 에칭 마스크 물질을 형성할 수 있다.

도 18은 본 발명의 실시예에 따라 디바이스를 제작하기 위한 장치(1800)의 블록도를 도시한다. 장치(1800)는 인클로저(1802)를 포함할 수 있다. 다양한 실시예에서, 인클로저(1802)는 대기 입자 여과, 상대 습도의 제어, 온도의 제어, 또는 공정 환경 내 그 밖의 다른 공정 조건 제어를 제공하도록 구성될 수 있다. 장치(1800)는 제1 기판 이송 메커니즘(1804), 및 상기 제1 기판 이송 메커니즘(1804)으로부터의 기판을 수용하도록 구성된 기판 투입 유닛(1806)을 포함할 수 있다. 기판은 도 6a-9c와 관련하여 언급된 비-패터닝 디바이스 층, 가령, 기판(602, 702, 802, 또는 902) 및 비-패터닝 디바이스 층(604, 704, 804, 또는 904)을 포함할 수 있다. 제1 증착 모듈(1808)은 도 6a-9c 및 11-13c와 관련하여 언급된 제1 층, 가령, 내부식성 층(629, 729, 829, 929, 1129, 1229, 또는 1329)을 비-패터닝된 디바이스 층 위에 증착하도록 구성되며, 여기서 제1 증착 모듈(1808)은 제1 물질을 기판 상으로 증착하는 부분 및 비제한적 예를 들면, 제1 물질의 건조, 경화, 또는 그 밖의 다른 처리에 의해, 증착된 제1 물질을 더 처리하여 내부식성 층을 형성하는 부분을 포함할 수 있다. 제2 증착 모듈(1812)은 내부식성 무?ㄹ 층 위해 에칭 마스크, 가령, 도 6a-9d와 관련하여 기재된 에칭 마스크(628, 728, 828, 또는 928)를 증착하도록 구성된다. 제2 증착 모듈(1812)은 제2 물질을 기판 상으로 증착하는 부분 및 비제한적 예를 들면 제2 물질의 건조, 경화, 현상, 광-노출, 레이저 직접 쓰기, 또는 그 밖의 다른 처리에 의해, 증착된 제2 물질을 더 처리하여 에칭 마스크를 형성하는 부분을 포함할 수 있다. 장치(1800)는 기판을 제2 기판 이송 메커니즘(도시되지 않음)으로 제공하는 기판 출력 유닛(1820)을 포함할 수 있다. 제1 기판 이송 메커니즘(1804)은 기판을 이전 처리 모듈 또는 장치에서 장치(1800)로 이송할 수 있고, 제2 기판 이송 메커니즘은 기판을 다음 처리 모듈 또는 장치로 이송할 수 있다.

다양한 실시예에서, 제1 증착 모듈(1808) 및 제2 증착 모듈(1812)은 방법, 가령, 잉크젯 인쇄, 분사, 적층화, 스핀 코팅, 또는 그 밖의 다른 임의의 증착 방법, 비제한적 예를 들면, 앞서 기재된 증착 방법 중 임의의 방법에 의해 물질을 증착하도록 구성될 수 있다.

일부 실시예에서, 장치는 기판 입력 유닛(1806)으로부터 기판을 수용하고, 기판을 세정하며, 제1 증착 모듈(1808)에 기판을 이송하도록 구성된 기판 세정 모듈(1807)을 포함한다. 일부 실시예에서, 제1 증착 모듈(1808) 및 제2 증착 모듈(1812)은 단일 모듈일 수 있다. 일부 실시예에서, 장치(1800)는 에칭 마스크에 의해 보호되지 않는 비-패터닝 디바이스 층 내 물질을 에칭하도록 구성된 에칭 모듈(1816) 및 기판 상의 비-패터닝 디바이스 층의 물질의 에칭 후 기판으로부터 에칭 마스크를 제거하도록 구성된 박리 모듈(1818)을 포함한다.

도 19는 본 발명의 또 다른 실시예에 따르는 예시적 작업 흐름(1900)을 보여준다. (1902)에서, 제1 반응 성분을 포함하는 프라이머 층이 비-패터닝 디바이스 층, 가령, 금속 표면, 가령, 구리 포일 상으로 도포된다. 프라이머 층은 내부식성 층, 가령, 상기 실시예와 연관된 내부식성 층(629, 729, 829, 929, 1129, 1229, 또는 1329)일 수 있다. (1904)에서, 제2 반응 성분을 포함하는 제2 조성을 포함하는 액상 에칭 방지 잉크의 프라이머 층 상으로의 이미지별 인쇄에 의해 2-성분 에칭 방지 마스크가 제조된다. 에칭 방지 잉크의 상호작용으로부터 도출된 2-성분 물질은, 상기 실시예에 관련하여 기재된 에칭 마스크, 가령, (628, 728, 828, 또는 928)를 포함할 수 있다. 제2 조성은 제1 반응 성분과 화학 반응을 겪을 수 있는 제2 반응 성분을 포함할 수 있다. 다양한 실시예에서, 에칭 방지 잉크는 액상 에칭-방지 잉크는 잉크젯 노즐에 의해 전달되는 액적의 형태로 표면에 도포될 수 있고, 프라이머 표면과 접촉되면, 비제한적 예를 들어, 에칭 방지 잉크와 프라이머 층 간 상호작용에 의해 트리거되는 화학 반응으로 인해, 이러한 액적은 곧(가령, 마이크로초 수준으로) 효과적으로 제위치에 부동화되거나 "동결"되어, 프라이머 표면 상의 잉크 액적의 추가 이동 또는 확산이 크게 감소 또는 전체적으로 중단되며, 국제 특허 번호 WO2016/193978 A2 및 WO2016/025949 A1에 기재되어 있다. (1906)에서, 프라이머 층의 비-마스킹 부분(즉, 에칭 마스크에 의해 덮이지 않는 프라이머 층의 일부분)이 에칭 공정 전, 또는 동안 제거된다. (1908)에서, 금속 표면의 비-마스킹 부분이 에칭되어 패터닝된 디바이스 층, 가령, 상기 실시예와 관련하여 기재된 패터닝된 디바이스 층(630, 730, 830, 930, 1130, 1230, 또는 1330)을 형성할 수 있다. (1910)에서, 에칭 방지 마스크가 제거되어 패터닝된 디바이스 층을 노출시킬 수 있다.

실시예 1-3

이하의 비교 예시가 수행되어, 내부식성 물질을 이용하지 않는 종래의 공정과 비교해서, 본 발명의 실시예를 이용해 획득된 언더컷의 감소를 보일 수 있다.

이하에서 상세히 기재될 예시 2 및 3에서, 폴리이민계 에이전트 조성물이 우선 Epson stylus 4900 잉크젯 인쇄기를 이용해 ½ Oz (17 ㎛)의 구리 두께를 갖는 FR4 구리 클래드 기판 상부에 도포되었다. 그 후, 에칭 방지 마스크가 폴리이민 층의 상부에 도포되었다. 수성 에칭 방지 조성물이 습윤제로서 10% 프로필렌 글리콜 및 이온 교환제로서 1% (w/w) 2-아미노-2-메틸 프로판올, 계면활성제로서 BYK가 공급한 0.3% (w/w)의 BYK 348, 및 착색제로서 2 % (w/w)의 Bayscript BA Cyan을 이용하여 제조되었다.에칭 방지 용액은 음이온 에칭 방지제로서 24% Joncryl 8085 스티렌 아크릴 수지 용액을 더 포함했다. 이하의 기재에서, % (w/w)는 조성물의 중량에 대한 중량의 퍼센티지로 된 물질의 농도의 척도이다. 인쇄된 시료가 80℃에서 건조되었다. 산성 에칭 용액을 담고 있는 에칭제 배쓰를 이용해, 보호되지 않는 노출된 영역으로부터 구리가 에칭되었다. 에칭된 기판을 25℃의 온도의 수용액 중 1% (w/w) NaOH에 침지하고, 그 후 FR4 구리 기판을 물로 세정하고 25℃의 공기를 이용해 건조함으로써 에칭 방지 마스크가 박리되었다. 예시 1에서, 기저 에이전트 층을 도포하지 않고 또 다른 시료가 제조되었다.

실시예 1: 에칭 방지 패턴이, Epson stylus 4900 잉크젯 인쇄기를 이용해, 코팅되지 않은 구리 FR4 기판의 상부 상에 ½ Oz (17 ㎛)의 구리 두께로 인쇄되었다. 실시예 1에 따라 만들어진 구리 와이어 시료의 단면도의 마이크로그래프를 도시하는 도 20을 참조할 수 있다. 수성 에칭 방지 조성물이 습윤제로서 10% 프로필렌 글리콜 및 이온 교환제로서 1% (w/w) 2-아미노-2-메틸 프로판올, 계면활성제로서 BYK가 공급한 0.3% (w/w)의 BYK 348, 및 착색제로서 2 % (w/w)의 Bayscript BA Cyan을 이용하여 제조되었다.에칭 방지 용액은 음이온 에칭 방지 반응 성분으로서 24% Joncryl 8085 스티렌 아크릴 수지 용액을 더 포함했다. 에칭 방지의 건조, 에칭 및 제거가 앞서 기재된 바와 같이 실시되었다. 도 20에서 나타날 수 있듯이, 구리 측벽의 기울기가 비교적 높다. 형성된 전도성 특징부의 상태 치수가 측정되었고 에칭 계수가 1.5로 계산되었다.

실시예 2: 에칭 방지 패턴이 폴리이민계 코팅으로 코팅된 구리 FR4 기판의 상부 상에 인쇄되었다. 폴리이민 수용액이 BASF가 공급한 수용액 중 10% (w/w) LUPASOL G100(5000의 분자 중량을 갖는 폴리에틸렌이민), 10% (w/w) 프로필렌 글리콜, 10% n-프로판올 및 Evonik Industries가 공급하는 TEGO 500의 0.3% (w/w)의 혼합물로서 제조되었다. 폴리-이민 용액은 Epson stylus 4900 잉크젯 인쇄기를 이용해 제조되었다. 폴리이민계 코팅이 실온에서 건조되게 하여, 결정 형성 없이 기판의 전체 표면을 덮는 0.075㎛의 건조 두께를 갖는 완전 투명한 균일 코팅을 도출했다. 에칭 방지 조성물이 앞서 기재된 바와 같이 공정 및 물질을 이용해 코팅된 구리 기판 상에 인쇄되었다. 형성된 전도성 특징부의 상태 치수가 측정되었고 에칭 계수가 2.5로 계산되었다.

실시예 3: 에칭 방지 패턴이 폴리이민계 코팅으로 코팅된 구리 FR4 기판의 상부 상에 인쇄되었다. 본 발명의 실시예에 따라 실시예 3에 따라 만들어진 구리 와이어 시료의 단면도의 마이크로그래프를 도시하는 도 21을 참조할 수 있다. Epson stylus 4900 잉크젯 인쇄기를 이용해 폴리이민계 코팅이 FR4 기판의 상부 상에 코팅되었다. 폴리이민 용액이 BASF가 공급한 10% (w/w) LUPASOL HF(25,000의 분자 중량을 갖는 폴리에틸렌이민)의 수용액, 10% (w/w) 프로필렌 글리콜, 10% n-프로판올 및 Evonik Industries가 공급하는 TEGO 500의 0.3% (w/w)의 혼합물로서 제조되었다. 코팅된 플레이트가 실온에서 건조되게 하여, 결정 형성 없이 전체 표면을 덮는 0.075㎛ 두께의 건조 층을 갖는 완전 투명한 균일 코팅을 도출하였다.

에칭 방지 조성물이 실시예 1에서 상술한 바와 같이 제조되었다. 마스킹되지 않는 구리의 에칭 및 에칭 방지 마스크의 제거가 실시예 1과 관련하여 기재된 바와 같이 실시되었다. 도 21에 도시된 바와 같이, 구리 와이어의 측벽의 기울기가 도 20에 도시된 언더컷 제거 층 없이 제조된 시료보다 훨씬 적다. 형성된 전도성 특징부의 상태 치수가 측정되었고 에칭 계수가 측정되었고, 7.5인 것이 발견되었다.

표 1은 세 가지 실시예의 결과의 일부 특징을 요약한다.

표 1:

다음의 비교 예시가 수행되어 프라이머 층 및 잉크젯 인쇄된 에칭 방지 잉크를 이용한 에칭 마스크의 형성의 개선을 보여줄 수 있으며, 프라이머 층과 접촉할 때, 프라이머 층의 성분과 에칭 방지 잉크 사이에 하나 이상의 반응이 발생하여, 2-성분 에칭 마스크 물질이 형성되고 에칭 방지 잉크의 액적이 빠르게(가령, 마이크로초 수준으로) 부동화 또는 동결되며, 이러한 액적의 후속 확산 및/또는 이동이 크게 감소된다.

실시예 4-12

Epson stylus 4900 잉크젯 인쇄기를 이용해 예시적 에칭 방지 조성물(본 명세서에 기재된 제2 조성물)이 1/2 Oz, 1/3 Oz 및 1 Oz의 두께를 갖는 FR4 구리 클래드 기판 상에 인쇄되었다. 일부 경우, 지정 패턴에 따라 에칭 방지 조성물이 그 위에 선택적으로 인쇄되는 고정화 층(fixating layer)을 형성하는 고정화 조성물(본 명세서에 기재된 제1 조성물)과 함께 Epson stylus 4900 잉크젯 인쇄기를 이용해 우선 구리가 코팅되었다. 이하의 기재에서, % (w/w)는 조성물의 중량에 대한 중량의 퍼센티지로 된 물질의 농도의 척도이다. Amza [pernix 166]가 공급한 강도 42° Baume의 제2철 클로라이드 에칭제 용약을 담고 있는 에칭제 배쓰를 이용해 에칭 방지제에 의해 보호되지 않고 노출된 영역으로부터 구리가 에칭되었다. 3분 동안 35℃의 온도에서, Walter Lemmen GMBH가 공급한 Spray Developer S31에서 에칭이 수행되었다. 에칭된 기판을 25℃의 온도의 수용액 중 1% (w/w) NaOH에 침지하고, 그 후 FR4 구리 기판을 물로 세정하고 25℃의 공기를 이용해 건조함으로써 에칭 방지 마스크가 박리되었다. 일부 실험에서, 비-보호 구리를 에칭하기 위한 구리 클로라이드 용액을 담고 있는 Universal 또는 Shmidth가 제조한 산업용 에칭 유닛, 가령, 하이퍼 및 수퍼 에칭 유닛을 이용해, 구리 기판이 또한 에칭되었다.

실시예 4 - 비코팅 구리 FR4 기판의 상부에 인쇄된 에칭 방지 조성물(비교 데이터). 에칭 방지 조성물(제2 조성물)이 10% 프로필렌 글리콜 및 1% (w/w) 2-아미노-2-메틸 프로판올, BYK가 공급한 0.3% (w/w)의 BYK 348, 및 2 % (w/w)의 Bayscript BA Cyan을 이용하여 제조되었다. 이들 물질이 음이온 반응 성분으로서 24% Joncryl 8085 스티렌 아크릴 수지 용액을 함유하는 물에서 용해되었다. Epson stylus 4900 잉크젯 인쇄기를 이용해 에칭 방지 조성물이 ½ Oz의 두께를 갖는 FR4 구리 클래드 기판 상에 인쇄되어 에칭 방지 마스크를 생성할 수 있다. 건조된 에칭 방지 두께가 5 마이크론이었다.

에칭 마스크가 시각적으로 검사되었고, 인쇄된 패턴이 매우 열악한 가장자리 형성, 선 단절 및 선들 간 심각한 쇼트를 갖는 매우 열악한 인쇄 품질을 보인다.

실시예 5: 에칭 방지 조성물이 실시예 4에서 상술한 바와 같이 제조되었다. 프라이머 또는 고정화 조성물이 BASF가 공급한 10% (w/w) LUPASOL PR8515(양이온 반응 성분으로서의 폴리에틸렌이민)의 수용액, 10% (w/w) 프로필렌 글리콜, 10% n-프로판올 및 Evonik Industries가 공급하는 TEGO 500의 0.3% (w/w)(억포성 기판 습윤 첨가제)의 혼합물로서 제조되었다.

FR4 구리 기판은 Epson stylus 4900 잉크젯 인쇄기를 이용해 제조되었다. 코팅된 플레이트가 실온에서 건조되게 하여, 어떠한 결정 형성도 없이 전체 표면을 덮는 0.3μ 두께의 건조 층을 갖는 완전 투명한 균일 코팅을 도출하였다. Epson stylus 4900 잉크젯 인쇄기를 이용해 에칭 방지 조성물이 코팅된 구리 기판 상에 인쇄되었고 80℃에서 건조되어 2-성분 에칭 방지 마스크를 생성할 수 있다. 에칭 마스크가 시각적으로 검사되어 실시예 4보다 더 우수한 인쇄 품질을 나타내지만 넓어진 라인 및 라인들간 쇼트를 갖는 여전히 비교적 열악한 인쇄 품질을 보인다. 마스킹되지 않는 구리의 에칭 및 에칭 방지 마스크의 제거가 실시예 4과 관련하여 기재된 바와 같이 실시되었다. 에칭 공정이 동일한 넓은 라인 및 라인들 간 쇼트를 갖는 에칭 방지 마스크와 동일한 이미지를 가진 후 와이어 패턴이 생성되었다. 특정 경우 실시예 5에서 나타나는 바와 같은 인쇄 품질이 충분할 수 있음을 알아야 한다.

실시예 6 - 에칭 방지 조성물이 실시예 4에서 상술한 바와 같이 제조되었다. 고정화 조성물이, 실시예 5에서 상세히 기재된 바대로, 그러나 0.3% (w/w) TEGO 500를 13% (w/w) 농축 HCl를 함유하는 0.3% (w/w) TEGO 500로 대체하여 제조되었다.

FR4 구리 기판은 실시예 5에서 상세히 기재된 바와 같이 Epson stylus 4900 잉크젯 인쇄기를 이용해 실시예 5에 기재된 바와 같이 코팅 층의 건조가 형성된 후 제조되었다. 실시예 5와 유사하게, 에칭 방지 조성물이 코팅된 구리 기판 상에 잉크젯-인쇄되었고 80℃에서 건조되어 2-성분 에칭 방지 마스크를 생성할 수 있다. 에칭 방지 패턴이 2밀리미터까지 작아진 두께를 갖는 잘 형성된 얇은 라인, 선명한 가장자리를 가지며 어떠한 라인 깨짐도 없는 높은 인쇄 품질을 보였다. 마스킹되지 않는 구리의 에칭 및 에칭 방지 마스크의 제거가 실시예 4과 관련하여 기재된 바와 같이 실시되었다. 에칭 및 박리 공정에 의해 생성된 와이어링 패턴이 15 마이크론까지 작아진 폭을 갖는 얇은 라인, 선명한 가장자리를 갖고 어떠한 라인 깨짐도 없는 잘 형성된 패턴을 보여준다.

실시예 7 - 2-성분 반응, 염산(HCl)을 함유하는 반응성 양이온 조성물로 코팅된 구리 표면 상에 인쇄된 에칭 방지 조성물 에칭 방지 조성물이 실시예 4에서 상술한 바와 같이 제조되었다. 고정화 조성물이 (수용액 중 20% 폴리머로서 ISP가 공급한) 10% (w/w) Styleze W-20의 수용액, BYK 348의 0.1 %, 및 13% (w/w) 농축 HCl의 혼합물로서 제조되었다.

F4F 구리 기판이 Mayer 로드를 이용해 고정화 조성물로 덮여서, 0.4μ의 두께를 갖는 건조 층을 생성할 수 있다. 코팅된 기판이 건조되어서, 결정 형성 없이, 전체 구리 표면 위에 완전 투명한 코팅을 도출했다. 실시예 5와 유사하게, 에칭 방지 조성물이 코팅된 구리 기판 상에 잉크젯-인쇄되었고 80℃에서 건조되어 2-성분 에칭 방지 마스크를 생성할 수 있다.

에칭 방지 패턴이 2밀리미터까지 작아진 잘 형성된 얇은 라인, 선명한 가장자리를 가지며 어떠한 라인 깨짐도 없는 높은 인쇄 품질을 보였다. 기판을 25 ℃의 온도의 물에 2분 동안 침지함으로써 에칭 방지 조성물에 의해 덮이지 않았던 고정화 층의 나머지 부분이 세정되었고 80℃로 건조되었다. 노출된 구리의 에칭 및 에칭 방지 마스크의 제거가 실시예 4에서 기재된 바와 같이 실시되었다. 기판 상의 와이어 패턴이 선명한 가장자리를 갖고 라인 깨짐을 갖지 않는 2 mil까지 작아진 폭을 갖는 잘 형성된 얇은 라인을 보였다.

실시예 8 - 2-성분 반응, 염산(HCl)을 함유하는 반응성 양이온 조성물로 코팅된 구리 표면 상에 인쇄된 에칭 방지 조성물 에칭 방지 조성물이 실시예 4에서 상술한 바와 같이 제조되었다. 고정화 조성물이 (수용액 중 56%로서 BASF가 공급하는) 10% (w/w) Lupasol HF의 수용액, 13% (w/w) 농축 HCl를 함유하는 BYK 348의 0.1%의 혼합물로서 제조되었다.

FR4 구리 기판이 Mayer 로드를 이용해 고정화 조성물로 덮여서, 1 μ의 두께를 갖는 건조 층을 생성할 수 있다. 코팅된 기판이 건조되어서, 결정 형성 없이, 전체 구리 표면 위에 완전 투명한 코팅을 도출했다. 실시예 5와 유사하게, 에칭 방지 조성물이 코팅된 구리 기판 상에 잉크젯-인쇄되었고 80℃에서 건조되어 2-성분 에칭 방지 마스크를 생성할 수 있다.

에칭 방지 패턴이 2mil까지 작아진 잘 형성된 얇은 라인, 선명한 가장자리를 가지며 어떠한 라인 깨짐도 없는 높은 인쇄 품질을 보였다. 기판을 25 ℃의 온도의 물에 3분 동안 침지함으로써 에칭 방지 조성물에 의해 덮이지 않았던 고정화 층의 나머지 부분이 세정되었고 80℃로 건조되었다. 노출된 구리의 에칭 및 에칭 방지 마스크의 제거가 실시예 4에서 기재된 바와 같이 실시되었다. 기판 상의 와이어 패턴이 선명한 가장자리를 갖고 라인 깨짐을 갖지 않는 2 mil까지 작아진 폭을 갖는 잘 형성된 얇은 라인을 보였다.

실시예 9 - 2-성분 반응, 염산(HCl)을 함유하는 반응성 양이온 조성물로 코팅된 구리 표면 상에 인쇄된 에칭 방지 조성물 에칭 방지 조성물이 실시예 5에서 상술한 바와 같이 제조되었다. 고정화 조성물이 (수용액 중 49%로서 BASF가 공급하는) 10% (w/w) Lupasol PN 50의 수용액, 13% (w/w) 농축 HCl를 함유하는 BYK 348의 0.1%의 혼합물로서 제조되었다.

FR4 구리 기판이 Mayer 로드를 이용해 고정화 조성물로 덮여서, 1 μ의 두께를 갖는 건조 층을 생성할 수 있다. 코팅된 기판이 건조되어서, 결정 형성 없이, 전체 구리 표면 위에 완전 투명한 코팅을 도출했다. 실시예 5와 유사하게, 에칭 방지 조성물이 코팅된 구리 기판 상에 잉크젯-인쇄되었고 80℃에서 건조되어 2-성분 에칭 방지 마스크를 생성할 수 있다.

에칭 방지 패턴이 2밀리미터까지 작아진 잘 형성된 얇은 라인, 선명한 가장자리를 가지며 어떠한 라인 깨짐도 없는 높은 인쇄 품질을 보였다. 고정화 층의 잔여물이 실시예 8에서 기재된 바대로 세정되었다. 노출된 구리의 에칭 및 에칭 방지 마스크의 제거가 실시예 1에서 기재된 바와 같이 실시되었다. 기판 상의 와이어 패턴이 선명한 가장자리를 갖고 라인 깨짐을 갖지 않는 2 mil까지 작아진 폭을 갖는 잘 형성된 얇은 라인을 보였다.

실시예 10 - 2-성분 반응, 시트르산을 함유하는 반응성 조성물로 코팅된 구리 표면 상에 인쇄된 에칭 방지 조성물 에칭 방지 조성물이 실시예 4에서 상술한 바와 같이 제조되었다. 고정화 조성물이 Evonik Industries가 공급한 0.3% (w/w) TEGO 500(억포성 기판 습윤 첨가제)를 함유하는, 10% (w/w) 시트르산의 수용액, 25% (w/w) 프로필렌 글리콜의 혼합물로서 제작되었다.

FR4 구리 기판은 Epson stylus 4900 잉크젯 인쇄기를 이용해 고정화 조성물로 코팅되었다. 코팅된 플레이트가 실온에서 건조되게 하여, 어떠한 결정 형성도 없이 전체 표면을 덮는 0.3μ 두께의 건조 층을 갖는 완전 투명한 균일 코팅을 도출하였다. 실시예 5와 유사하게, 에칭 방지 조성물이 코팅된 구리 기판 상에 잉크젯-인쇄되었고 80℃에서 건조되어 2-성분 에칭 방지 마스크를 생성할 수 있다.

에칭 방지 패턴이 2 mil까지 작아진 잘 형성된 얇은 라인, 선명한 가장자리를 가지며 어떠한 라인 깨짐도 없는 높은 인쇄 품질을 보였다. 노출된 구리의 에칭 및 에칭 방지 마스크의 제거가 실시예 4에서 기재된 바와 같이 실시되었다. 기판 상의 와이어 패턴이 선명한 가장자리를 갖고 라인 깨짐을 갖지 않는 2 mil까지 작아진 폭을 갖는 잘 형성된 얇은 라인을 보였다.

실시예 11 - 2-성분 반응, 에칭 방지 조성물을 함유하는 코팅 조성물이 실시예 4에서 기재된 바와 같이 제조되었다. 고정화 조성물이 2.5% (w/w) Zn(NO3)2의 수용액, 3.75% (w/w) 칼슘 아세테이트, 0.2% (w/w) Capstone 51, 5% (w/w) n-프로판올 및 (BASF가 공급하는) 5% (w/w) Lupasol FG의 혼합물로서 제조되었다.

FR4 구리 기판이 Mayer 로드를 이용해 고정화 조성물로 덮여서, 0.5μ의 두께를 갖는 건조 층을 생성할 수 있다. 코팅된 기판이 건조되어서, 결정 형성 없이, 전체 구리 표면 위에 완전 투명한 코팅을 도출했다. 실시예 5와 유사하게, 에칭 방지 조성물이 코팅된 구리 기판 상에 잉크젯-인쇄되었고 80℃에서 건조되어 2-성분 에칭 방지 마스크를 생성할 수 있다.

실시예 5와 유사하게, 에칭 방지 조성물이 코팅된 구리 기판 상에 잉크젯-인쇄되었고 80℃에서 건조되어 2-성분 에칭 방지 마스크를 생성할 수 있다.

에칭 방지 패턴이 2 mil까지 작아진 잘 형성된 얇은 라인, 선명한 가장자리를 가지며 어떠한 라인 깨짐도 없는 높은 인쇄 품질을 보였다. 노출된 구리의 에칭 및 에칭 방지 마스크의 제거가 실시예 4에서 기재된 바와 같이 실시되었다. 기판 상의 와이어 패턴이 선명한 가장자리를 갖고 라인 깨짐을 갖지 않는 2 mil까지 작아진 폭을 갖는 잘 형성된 얇은 라인을 보였다.

실시예 12 - 에칭 방지 조성물이 8% (w/w) PVA의 수용액, (수용액 중 42% 폴리머로서 공급된) 24% Joncryl 8085 스티렌 아크릴 수지 용액, 및 1.5%의 2-아미노 2-메틸 프로판올의 혼합물로서 제조되었다.

고정화 조성화가 다음과 같이 제조되었다: 2 % (w/w)의 Basacid Red 495, 10% (w/w) 프로필렌 글리콜, 10%의 n-프로판올, 0.3% (w/w) TEG0500, (BASF가 공급하는) 10% (w/w) Lupasol G20, 농축된 12% (w/w) HCl 함유 FR4 구리 기판이 Mayer 로드를 이용해 에칭 방지 조성물로 덮여서, 2.4 μ의 두께를 갖는 건조 층을 생성할 수 있다. 코팅된 기판이 건조되어서, 결정 형성 없이, 전체 구리 표면 위에 완전 투명한 코팅을 도출했다. 고정화 조성물이 코팅된 구리 기판 상에 잉크젯-인쇄되었고 80℃에서 건조되어 2-성분 에칭 방지 마스크를 생성할 수 있다.

실시예 5와 유사하게, 에칭 방지 조성물이 코팅된 구리 기판 상에 잉크젯-인쇄되었고 80℃에서 건조되어 2-성분 에칭 방지 마스크를 생성할 수 있다.