KR20180004009A - 입자 및 금속들 성능 향상들을 위한 esc 세라믹 측벽 개질 - Google Patents

입자 및 금속들 성능 향상들을 위한 esc 세라믹 측벽 개질 Download PDFInfo

- Publication number

- KR20180004009A KR20180004009A KR1020170081734A KR20170081734A KR20180004009A KR 20180004009 A KR20180004009 A KR 20180004009A KR 1020170081734 A KR1020170081734 A KR 1020170081734A KR 20170081734 A KR20170081734 A KR 20170081734A KR 20180004009 A KR20180004009 A KR 20180004009A

- Authority

- KR

- South Korea

- Prior art keywords

- sidewalls

- ceramic layer

- layer

- base plate

- protective layer

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/687—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches

- H01L21/68714—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support

- H01L21/68757—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support characterised by a coating or a hardness or a material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/6835—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B37/00—Joining burned ceramic articles with other burned ceramic articles or other articles by heating

- C04B37/008—Joining burned ceramic articles with other burned ceramic articles or other articles by heating by means of an interlayer consisting of an organic adhesive, e.g. phenol resin or pitch

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B37/00—Joining burned ceramic articles with other burned ceramic articles or other articles by heating

- C04B37/02—Joining burned ceramic articles with other burned ceramic articles or other articles by heating with metallic articles

- C04B37/023—Joining burned ceramic articles with other burned ceramic articles or other articles by heating with metallic articles characterised by the interlayer used

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B41/00—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone

- C04B41/009—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone characterised by the material treated

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B41/00—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone

- C04B41/45—Coating or impregnating, e.g. injection in masonry, partial coating of green or fired ceramics, organic coating compositions for adhering together two concrete elements

- C04B41/50—Coating or impregnating, e.g. injection in masonry, partial coating of green or fired ceramics, organic coating compositions for adhering together two concrete elements with inorganic materials

- C04B41/5025—Coating or impregnating, e.g. injection in masonry, partial coating of green or fired ceramics, organic coating compositions for adhering together two concrete elements with inorganic materials with ceramic materials

- C04B41/5045—Rare-earth oxides

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B41/00—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone

- C04B41/80—After-treatment of mortars, concrete, artificial stone or ceramics; Treatment of natural stone of only ceramics

- C04B41/81—Coating or impregnation

- C04B41/85—Coating or impregnation with inorganic materials

- C04B41/87—Ceramics

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C28/00—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D

- C23C28/04—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D only coatings of inorganic non-metallic material

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C28/00—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D

- C23C28/04—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D only coatings of inorganic non-metallic material

- C23C28/042—Coating for obtaining at least two superposed coatings either by methods not provided for in a single one of groups C23C2/00 - C23C26/00 or by combinations of methods provided for in subclasses C23C and C25C or C25D only coatings of inorganic non-metallic material including a refractory ceramic layer, e.g. refractory metal oxides, ZrO2, rare earth oxides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/6831—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using electrostatic chucks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/687—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches

- H01L21/68714—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support

- H01L21/68735—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support characterised by edge profile or support profile

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/687—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches

- H01L21/68714—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support

- H01L21/68785—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support characterised by the mechanical construction of the susceptor, stage or support

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2237/00—Aspects relating to ceramic laminates or to joining of ceramic articles with other articles by heating

- C04B2237/02—Aspects relating to interlayers, e.g. used to join ceramic articles with other articles by heating

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2237/00—Aspects relating to ceramic laminates or to joining of ceramic articles with other articles by heating

- C04B2237/30—Composition of layers of ceramic laminates or of ceramic or metallic articles to be joined by heating, e.g. Si substrates

- C04B2237/32—Ceramic

- C04B2237/34—Oxidic

- C04B2237/343—Alumina or aluminates

-

- C—CHEMISTRY; METALLURGY

- C04—CEMENTS; CONCRETE; ARTIFICIAL STONE; CERAMICS; REFRACTORIES

- C04B—LIME, MAGNESIA; SLAG; CEMENTS; COMPOSITIONS THEREOF, e.g. MORTARS, CONCRETE OR LIKE BUILDING MATERIALS; ARTIFICIAL STONE; CERAMICS; REFRACTORIES; TREATMENT OF NATURAL STONE

- C04B2237/00—Aspects relating to ceramic laminates or to joining of ceramic articles with other articles by heating

- C04B2237/30—Composition of layers of ceramic laminates or of ceramic or metallic articles to be joined by heating, e.g. Si substrates

- C04B2237/32—Ceramic

- C04B2237/36—Non-oxidic

- C04B2237/366—Aluminium nitride

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Ceramic Engineering (AREA)

- Materials Engineering (AREA)

- Organic Chemistry (AREA)

- General Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Structural Engineering (AREA)

- Inorganic Chemistry (AREA)

- Metallurgy (AREA)

- Mechanical Engineering (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Drying Of Semiconductors (AREA)

- Container, Conveyance, Adherence, Positioning, Of Wafer (AREA)

Abstract

기판 프로세싱 시스템을 위한 기판 지지부는 베이스 플레이트 및 베이스 플레이트 상에 배치된 세라믹 층을 포함한다. 세라믹 층은 하부 표면, 기판을 지지하도록 구성된 상부 표면, 및 하부 표면으로부터 상부 표면으로 연장하는 세라믹 층의 주변부 주위의 측벽들을 포함하고, 그리고 세라믹 층은 제 1 재료를 포함한다. 본드 층은 베이스 플레이트와 세라믹 층 사이에 제공된다. 보호성 층은 세라믹 층의 측벽들 상에 형성된다. 보호성 층은 제 1 재료와 상이한 제 2 재료를 포함한다.

Description

본 개시는 기판 프로세싱 시스템들, 그리고 보다 구체적으로 기판 지지부의 세라믹 층의 측벽들을 보호하기 위한 시스템들 및 방법들에 관한 것이다.

본 명세서에 제공된 배경 기술 설명은 일반적으로 본 개시의 맥락을 제공하기 위한 것이다. 본 발명자들의 성과로서 본 배경기술 섹션에 기술되는 정도의 성과, 뿐만 아니라 출원시 종래 기술로서 인정되지 않을 수도 있는 기술의 양태들은 본 개시에 대한 종래 기술로서 명시적으로나 암시적으로 인정되지 않는다.

기판 프로세싱 시스템들은 반도체 웨이퍼들과 같은 기판들을 처리하도록 사용될 수도 있다. 기판 상에서 수행될 수도 있는 예시적인 프로세스들은 이로 제한되지 않지만, CVD (chemical vapor deposition), ALD (atomic layer deposition), 전도체 에칭, 및/또는 다른 에칭, 증착, 또는 세정 프로세스들을 포함한다. 기판은 기판 프로세싱 시스템의 프로세싱 챔버 내에서 페데스탈, ESC (electrostatic chuck) 와 같은 기판 지지부 상에 배치될 수도 있다. 에칭 동안, 하나 이상의 전구체들을 포함한 가스 혼합물들은 프로세싱 챔버 내로 도입될 수도 있고 그리고 플라즈마는 화학 반응들을 개시하도록 사용될 수도 있다.

ESC와 같은 기판 지지부는 웨이퍼를 지지하도록 배치된 세라믹 층을 포함할 수도 있다. 예를 들어, 웨이퍼는 프로세싱 동안 세라믹 층에 클램핑될 수도 있다. 세라믹 층은 이로 제한되지 않지만, 필러를 가진 실리콘, 에폭시 매트릭스 재료, 등을 포함한 재료들을 포함할 수도 있는 본딩 층을 사용하여 기판 지지부의 베이스 플레이트에 본딩될 수도 있다. 베이스 플레이트는 냉각된 알루미늄 베이스 플레이트를 포함할 수도 있다.

기판 프로세싱 시스템을 위한 기판 지지부는 베이스 플레이트 및 베이스 플레이트 상에 배치된 세라믹 층을 포함한다. 세라믹 층은 하부 표면, 기판을 지지하도록 구성된 상부 표면, 및 하부 표면으로부터 상부 표면으로 연장하는 세라믹 층의 주변부 둘레의 측벽들을 포함하고, 그리고 세라믹 층은 제 1 재료를 포함한다. 본딩 층은 베이스 플레이트와 세라믹 층 사이에 제공된다. 보호 층은 세라믹 층의 측벽들 상에 형성된다. 보호 층은 제 1 재료와 상이한 제 2 재료를 포함한다.

다른 특징들에서, 제 2 재료는 비-알루미나 기반 재료이다. 제 2 재료는 이트륨 옥사이드 스프레이코팅이다. 제 2 재료는 제 1 재료보다 플라즈마에 대해 보다 큰 내성을 갖는다. 보호 층의 두께는 0.005" 내지 0.010"이다.

다른 특징들에서, 보호 층은 하부 표면에 인접한 측벽들의 하단 에지로부터 상부 표면에 인접한 측벽들의 상단 에지로 연장한다. 보호 층은 하부 표면에 인접한 측벽들의 하단 에지로부터 상부 표면에 인접한 측벽들의 상단 에지로부터 미리 결정된 거리까지 연장한다. 미리 결정된 거리는 상단 에지로부터 적어도 0.001"이다.

여전히 다른 특징들에서, 상부 표면에 인접한 측벽들의 상단 에지는 챔퍼처리된다 (chamfered). 보호 층의 두께는 하부 표면에 인접한 측벽들의 하단 에지 및 상부 표면에 인접한 측벽들의 상단 에지 중 적어도 하나에서 테이퍼진다. 보호 층의 두께는 0.005" 내지 0.010"로부터 0.001"로 테이퍼진다. 보호 시일은 베이스 플레이트와 세라믹 층의 하부 표면 사이의 본딩 층의 주변부 들레에 배치되고 그리고 보호 시일은 세라믹 층의 하부 표면 상으로 연장하지 않는다.

기판 프로세싱 시스템을 위한 기판 지지부를 형성하기 위한 방법은 베이스 플레이트를 제공하는 단계, 베이스 플레이트 상에 본딩 층을 증착하는 단계, 및 베이스 플레이트 상에 세라믹 층을 배치하는 단계를 포함한다. 세라믹 층은 하부 표면, 기판을 지지하도록 구성된 상부 표면, 및 하부 표면으로부터 상부 표면으로 연장하는 세라믹 층의 주변부 둘레의 측벽들을 포함하고, 그리고 세라믹 층은 제 1 재료를 포함한다. 방법은 세라믹 층의 측벽들 상에 보호 층을 형성하는 단계로서, 보호 층은 제 1 재료와 상이한 제 2 재료를 포함하는, 세라믹 층의 측벽들 상에 보호 층을 형성하는 단계, 세라믹 층의 측벽들을 폴리싱하는 단계, 및 세라믹 층의 측벽들을 산 에칭하는 단계 중 적어도 하나를 더 포함한다.

다른 특징들에서, 제 2 재료는 비-알루미나 기반 재료이다. 보호 층을 형성하는 단계는 세라믹 층의 측벽들 상에 이트륨 옥사이드 스프레이코팅을 도포하는 단계를 포함한다. 제 2 재료는 제 1 재료보다 플라즈마에 대해 보다 큰 내성을 갖는다.

다른 특징들에서, 세라믹 층의 측벽들을 폴리싱하는 단계는 30 μin 미만의 표면 거칠기로 측벽들을 폴리싱하는 단계를 포함한다. 세라믹 층의 측벽들을 폴리싱하는 단계는 10 μin 미만의 표면 거칠기로 측벽들을 폴리싱하는 단계를 포함한다.

여전히 다른 특징들에서, 세라믹 층의 측벽들을 산 에칭하는 단계는 측벽들의 유리상 재료의 외측 부분을 제거하도록 측벽들을 산 에칭하는 단계를 포함한다.

본 개시의 적용 가능성의 추가의 영역들은 상세한 기술, 청구항들 및 도면들로부터 분명해질 것이다. 상세한 기술 및 구체적인 예들은 오직 예시의 목적들을 위해 의도된 것이고 본 개시의 범위를 제한하도록 의도되지 않는다.

본 개시는 상세한 기술 및 첨부된 도면들로부터 보다 완전히 이해될 것이다.

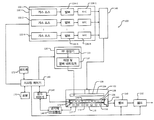

도 1은 본 개시의 원리들에 따른 기판 지지부를 포함한 예시적인 기판 프로세싱 시스템의 기능적 블록도이다.

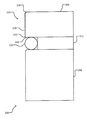

도 2a는 본 개시의 원리들에 따른 보호 층을 포함한 예시적인 기판 지지부이다.

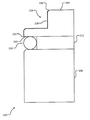

도 2b는 본 개시의 원리들에 따른 보호 층을 포함한 또 다른 예시적인 기판 지지부이다.

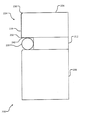

도 2c는 본 개시의 원리들에 따른 보호 층을 포함한 또 다른 예시적인 기판 지지부이다.

도 3은 본 개시의 원리들에 따른 기판 지지부를 형성하는 제 1 예시적인 방법의 단계들을 예시한다.

도 4는 본 개시의 원리들에 따른 기판 지지부를 형성하는 제 2 예시적인 방법의 단계들을 예시한다.

도 5는 본 개시의 원리들에 따른 기판 지지부를 형성하는 제 3 예시적인 방법의 단계들을 예시한다.

도면들에서, 참조 번호들은 유사한 그리고/또는 동일한 엘리먼트들 (elements) 을 식별하기 위해 재사용될 수도 있다.

도 1은 본 개시의 원리들에 따른 기판 지지부를 포함한 예시적인 기판 프로세싱 시스템의 기능적 블록도이다.

도 2a는 본 개시의 원리들에 따른 보호 층을 포함한 예시적인 기판 지지부이다.

도 2b는 본 개시의 원리들에 따른 보호 층을 포함한 또 다른 예시적인 기판 지지부이다.

도 2c는 본 개시의 원리들에 따른 보호 층을 포함한 또 다른 예시적인 기판 지지부이다.

도 3은 본 개시의 원리들에 따른 기판 지지부를 형성하는 제 1 예시적인 방법의 단계들을 예시한다.

도 4는 본 개시의 원리들에 따른 기판 지지부를 형성하는 제 2 예시적인 방법의 단계들을 예시한다.

도 5는 본 개시의 원리들에 따른 기판 지지부를 형성하는 제 3 예시적인 방법의 단계들을 예시한다.

도면들에서, 참조 번호들은 유사한 그리고/또는 동일한 엘리먼트들 (elements) 을 식별하기 위해 재사용될 수도 있다.

관련 출원들의 상호 참조

본 출원은 2016년 7월 1일 출원된 미국 가출원 번호 제 62/357,513 호의 이익을 주장한다. 상기 참조된 출원의 전체 개시는 전체가 참조로서 본 명세서에 인용된다.

기판 프로세싱 시스템의 프로세싱 챔버 내에서 ESC (electrostatic chuck) 와 같은 기판 지지부는 전도성 베이스 플레이트에 본딩된 세라믹 층을 포함할 수도 있다. 단지 예를 들면, 세라믹 층은 금속 옥사이드 바인더들을 가진 제 1, 주 재료 (예를 들어, 알루미늄 옥사이드 입자들, 알루미늄 나이트라이드, 등) 를 포함할 수도 있다. 다른 예들에서, 금속 옥사이드 바인더들은 생략될 수도 있다. 주 재료의 순도는 90 % 이상일 수도 있다.

세라믹 층은 기판 지지부의 외측 에지에서 챔버 내의 라디칼들, 이온들, 반응성 종들, 등을 포함한 플라즈마에 노출될 수도 있다. 플라즈마에 대한 노출은 세라믹 층의 부분들로 하여금 이로 제한되지 않지만, 불소화, 이온 충격, 등을 포함한 프로세스 메커니즘들에 기인하여 시간에 걸쳐 부식되게 (즉, 마모되게) 할 수도 있다. 이러한 마모는 세라믹 층의 재료들로 하여금 프로세싱 챔버의 반응 볼륨 내로 이동하게 할 수도 있고, 이는 기판 프로세싱에 부정적으로 영향을 줄 수도 있다. 예를 들어, 세라믹 층으로부터 제거된 직접적인 분자 및/또는 입자 재료는 플라즈마 내에 부유될 수도 있고, 그리고 에지 링 또는 다른 프로세스 챔버 하드웨어 상에 증착될 수도 있다. 이어서 이 재료는 차후의 프로세싱 동안 기판의 표면 상에 재증착될 수 있다. 즉, 플라즈마에 대한 노출에 기인하여 세라믹 층의 마모는 프로세스 챔버의 오염 및 입자 생성을 유발할 수도 있고, 기판 디펙트들을 발생시킨다.

본 개시의 원리들에 따른 시스템들 및 방법들은 플라즈마에 대한 세라믹 층의 재료의 노출에 의해 유발된 오염 및 입자 생성을 감소시키도록 세라믹 층의 측벽의 하나 이상의 개질들을 구현한다. 일 예에서, 세라믹 층의 측벽들은 보호 층 또는 코팅으로 코팅된다. 보호 층은 비-알루미나 기반 재료, 예컨대, 이트륨 옥사이드 스프레이코팅을 포함할 수도 있다. 보호 층은 프로세싱 챔버 내의 반응성 종과 세라믹 층 사이에 배리어를 제공한다. 또 다른 예에서, 세라믹 층의 측벽들은 폴리싱된다. 폴리싱은 측벽들의 표면적을 감소시켜서, 플라즈마에 노출된 재료량을 감소시킨다. 여전히 또 다른 예에서, 세라믹 층의 측벽들은 산 에칭된다. 측벽들을 산 에칭하는 것은 세라믹 층으로부터의 재료를 선제적으로 그리고 우선적으로 제거하고 그렇지 않으면 세라믹 층으로부터의 재료는 다른 플라즈마 프로세스들 동안 제거되고 그리고 챔버 내에 불순물들을 발생시킬 것이다.

이제 도 1을 참조하면, 예시적인 기판 프로세싱 시스템 (100) 이 도시된다. 단지 예를 들면, 기판 프로세싱 시스템 (100) 은 RF 플라즈마를 사용한 에칭 및/또는 다른 적합한 기판 프로세싱을 수행하기 위해 사용될 수도 있다. 기판 프로세싱 시스템 (100) 은 기판 프로세싱 시스템 (100) 의 다른 컴포넌트들 (components) 을 둘러싸고 그리고 RF 플라즈마를 담는 프로세싱 챔버 (102) 를 포함한다. 기판 프로세싱 챔버 (102) 는 상부 전극 (104) 및 기판 지지부 (106), 예컨대, ESC를 포함한다. 동작 동안, 기판 (108) 은 기판 지지부 (106) 상에 배치된다. 특정한 기판 프로세싱 시스템 (100) 및 챔버 (102) 가 예로서 도시되지만, 본 개시의 원리들은 리모트 플라즈마 생성 및 전달 (예를 들어, 마이크로파 튜브를 사용함), 등을 구현하는, 플라즈마를 인 시츄로 생성하는 기판 프로세싱 시스템과 같은, 다른 타입들의 기판 프로세싱 시스템들 및 챔버들에 적용될 수도 있다.

단지 예를 들면, 상부 전극 (104) 은 프로세스 가스들을 도입하고 분배하는 샤워헤드 (109) 를 포함할 수도 있다. 샤워헤드 (109) 는 프로세싱 챔버의 상단 표면에 연결된 일 단부를 포함한 스템 부분을 포함할 수도 있다. 베이스 부분은 일반적으로 원통형이고 그리고 프로세싱 챔버의 상단 표면으로부터 이격된 위치에서 스템 부분의 반대편의 단부로부터 방사상으로 외측으로 연장한다. 샤워헤드의 베이스 부분의 대면플레이트 또는 기판-대면 표면은, 프로세스 가스 또는 퍼지 가스가 흐르는 복수의 홀들을 포함한다. 대안적으로, 상부 전극 (104) 은 전도성 플레이트를 포함할 수도 있고 그리고 프로세스 가스들은 또 다른 방식으로 도입될 수도 있다.

기판 지지부 (106) 는 하부 전극으로서 작용하는 전도성 베이스 플레이트 (110) 를 포함한다. 베이스 플레이트 (110) 는 세라믹 층 (112) 을 지지한다. 일부 예들에서, 세라믹 층 (112) 은 세라믹 멀티-존 가열 플레이트와 같은 가열 층을 포함할 수도 있다. 내열 층 (114) (예를 들어, 본딩 층) 은 세라믹 층 (112) 과 베이스 플레이트 (110) 사이에 배치될 수도 있다. 베이스 플레이트 (110) 는 베이스 플레이트 (110) 를 통해 냉각제를 흘리기 위한 하나 이상의 냉각제 채널들 (116) 을 포함할 수도 있다.

RF 생성 시스템 (120) 은 RF 전압을 생성하고 RF 전압을 상부 전극 (104) 및 하부 전극 (예를 들어, 기판 지지부 (106) 의 베이스 플레이트 (110)) 중 하나에 출력한다. 상부 전극 (104) 및 베이스 플레이트 (110) 중 다른 하나는 DC 접지되거나, AC 접지되거나 플로팅할 (floating) 수도 있다. 단지 예를 들면, RF 생성 시스템 (120) 은 매칭 및 분배 네트워크 (124) 에 의해 상부 전극 (104) 또는 베이스 플레이트 (110) 에 피딩되는 (feed) RF 전압을 생성하는 RF 전압 생성기 (122) 를 포함할 수도 있다. 다른 예들에서, 플라즈마는 유도적으로 또는 리모트로 생성될 수도 있다. 예시적인 목적들을 위해 도시된 바와 같이, RF 생성 시스템 (120) 이 CCP (capacitively coupled plasma) 시스템에 대응하지만, 본 개시의 원리들은 또한 다른 적합한 시스템들, 예컨대, 단지 예를 들면 TCP (transformer coupled plasma) 시스템들, CCP 캐소드 시스템들, 리모트 마이크로파 플라즈마 생성 및 전달 시스템들, 등으로 구현될 수도 있다.

가스 전달 시스템 (130) 은 하나 이상의 가스 소스들 (132-1, 132-2, ..., 및 132-N) (집합적으로 가스 소스들 (132)) 을 포함하고, 여기서 N은 0보다 큰 정수이다. 가스 소스들은 하나 이상의 전구체들 및 전구체들의 혼합물들을 공급한다. 가스 소스들은 또한 퍼지 가스를 공급할 수도 있다. 기화된 전구체가 또한 사용될 수도 있다. 가스 소스들 (132) 은 밸브들 (134-1, 134-2, ..., 및 134-N) (집합적으로 밸브들 (134)) 및 질량 유량 제어기들 (136-1, 136-2, ..., 및 136-N) (집합적으로 질량 유량 제어기들 (136)) 에 의해 매니폴드 (140) 에 연결된다. 매니폴드 (140) 의 출력은 프로세싱 챔버 (102) 에 피딩된다. 단지 예를 들면, 매니폴드 (140) 의 출력은 샤워헤드 (109) 에 피딩된다.

온도 제어기 (142) 는 세라믹 층 (112) 내에 배치된 TCE들 (thermal control elements) (144) 과 같은 복수의 가열 엘리먼트들에 연결될 수도 있다. 예를 들어, 가열 엘리먼트들 (144) 은 이로 제한되지 않지만, 멀티-존 가열 플레이트 내의 각각의 존들에 대응하는 매크로 가열 엘리먼트들 및/또는 멀티-존 가열 플레이트의 복수의 존들에 걸쳐 배치된 마이크로 가열 엘리먼트들의 어레이를 포함할 수도 있다. 온도 제어기 (142) 는 기판 지지부 (106) 및 기판 (108) 의 온도를 제어하기 위해 복수의 가열 엘리먼트들 (144) 을 제어하도록 사용될 수도 있다. 본 개시의 원리들에 따른 가열 엘리먼트들 (144) 각각은 이하에 보다 상세히 기술되는 바와 같이 양 TCR을 가진 제 1 재료 및 음 TCR을 가진 제 2 재료를 포함한다.

온도 제어기 (142) 는 채널들 (116) 을 통해 냉각제 플로우를 제어하도록 냉각제 어셈블리 (146) 와 연통할 수도 있다. 예를 들어, 냉각제 어셈블리 (146) 는 냉각제 펌프 및 저장소를 포함할 수도 있다. 온도 제어기 (142) 는 기판 지지부 (106) 를 냉각하도록 채널들 (116) 을 통해 냉각제를 선택적으로 흘리기 위해서 냉각제 어셈블리 (146) 를 동작시킨다.

밸브 (150) 및 펌프 (152) 는 프로세싱 챔버 (102) 로부터 반응물질들을 배기하도록 사용될 수도 있다. 시스템 제어기 (160) 는 기판 프로세싱 시스템 (100) 의 컴포넌트들을 제어하도록 사용될 수도 있다. 로봇 (170) 은 기판 지지부 (106) 상으로 기판들을 전달하고, 그리고 기판 지지부 (106) 로부터 기판들을 제거하도록 사용될 수도 있다. 예를 들어, 로봇 (170) 은 기판들을 기판 지지부 (106) 와 로드록 (172) 사이에서 이송할 수도 있다. 분리된 제어기들로서 도시되지만, 온도 제어기 (142) 는 시스템 제어기 (160) 내에 구현될 수도 있다. 일부 예들에서, 보호 시일 (176) 은 세라믹 층 (112) 과 베이스 플레이트 (110) 사이의 본딩 층 (114) 의 주변부 들레에 제공될 수도 있다.

세라믹 층 (112) 은 본 개시의 원리들에 따라 개질되는 측벽들을 포함한다. 예를 들어, 세라믹 층 (112) 의 측벽들은 이하에 보다 상세히 기술되는 바와 같이 보호 층으로 코팅되고, 폴리싱되고, 그리고/또는 산 에칭된다.

이제 도 2a, 도 2b, 및 도 2c를 참조하면, 예시적인 기판 지지부들 (200) 의 각각의 부분들이 도시된다. 도 2a에서, 기판 지지부 (200) 는 계단형이 아닌 세라믹 층 구성을 갖는 것으로 도시된다. 도 2b에서, 기판 지지부 (200) 는 계단형 세라믹 층 구성을 갖는 것으로 도시된다. 기판 지지부 (200) 는 베이스 플레이트 (208) 상에 배치된 세라믹 층 (204) 을 포함한다. 일부 예들에서, 세라믹 층 (204) 은 가열 층으로서 구성된 세라믹 플레이트 (예를 들어, 임베딩된 가열 엘리먼트들을 포함한 세라믹 플레이트) 에 대응할 수도 있다. 세라믹 층 (204) 은 금속 옥사이드 바인더들을 갖거나 갖지 않은, 알루미늄 옥사이드 입자들, 알루미늄 나이트라이드, 등과 같은 제 1 (예를 들어, 주) 재료를 포함한다. 본딩 층 (212) 은 세라믹 층 (204) 과 베이스 플레이트 (208) 사이에 제공된다. 보호 시일 (220) 은 세라믹 층 (204) 과 베이스 플레이트 (208) 사이의 본딩 층 (212) 의 주변부 들레에 제공될 수도 있다. 단순성을 위해 도 2a 및 도 2b에서 생략된 에지 링은 도 1에 도시된 바와 같이 베이스 플레이트 (208) 와 세라믹 층 (204) 의 외측 에지 둘레에 배치될 수도 있다.

세라믹 층 (204) 의 측벽들 (224) 은 에지 링과 세라믹 층 (204) 사이의 갭과 오버랩하는 기판 및/또는 에지 링에 의해 부분적으로 보호될 수도 있지만, 그럼에도 불구하고 측벽들 (224) 은 프로세싱 동안 플라즈마에 노출된다. 따라서, 세라믹 층 (204) 의 측벽들 (224) 은 제 2 재료를 포함한 보호 층 또는 코팅 (228) 으로 코팅된다. 보호 층 (228) 은 세라믹 층 (204) 의 측벽들 (224) 과 프로세싱 챔버 내의 반응성 종 사이에 배리어를 제공한다.

일 예에서, 보호 층 (228) 은 이트륨 옥사이드 스프레이코팅 (예를 들어, 플라즈마 스프레이코팅) 과 같은 비-알루미나 기반 재료를 포함할 수도 있지만, 보다 큰 플라즈마에 대한 내마모성을 가진 다른 적합한 재료들이 사용될 수도 있다. 다른 예들에서, 보호 층 (228) 은 세라믹 층 (204) 을 보호하지만 플라즈마에 대한 노출에 의해 유발된 마모에 취약한 희생적 재료를 포함한다. 희생적 재료는 세라믹 층 (204) 의 측벽들 (224) 위에 보호 층 (228) 을 유지하도록 주기적으로 교체 (예를 들어, 스프레이코팅 기법들을 통해 재도포) 될 것이다. 예를 들어, 희생적 재료는 미리 결정된 양의 시간 및/또는 미리 결정된 수의 프로세스 단계들, 사용 시간들, 등 후에 교체될 수도 있다.

보호 층 (228) 은 목표된 두께로 세라믹 층 (204) 의 전체 원주 둘레에 측벽들 (224) 에 도포된다. 보호 층 (228) 이 세라믹 층 (204) 으로부터 디라미네이팅할 (delaminate) 가능성을 감소시키면서 측벽들 (224) 이 완전히 커버되도록 보호 층 (228) 의 두께가 선택된다. 일 예에서, 보호 층 (228) 의 두께는 5 내지 10 mil (즉, 0.005" 내지 0.010") 두께이다.

보호 층 (228) 은 측벽 (224) 의 하단 에지 (232) 와 측벽 (224) 의 상단 에지 (236) 사이에서 연장한다. 일 예에서, 보호 층 (228) 은 상단 에지 (236) 로 완전히 연장하지 않고 대신 도시된 바와 같이 상단 에지 (236) 로부터 공칭 거리 (예를 들어, 1 mil, 또는 0.001") 에서 종결된다. 따라서, 상단 에지 (236) 에서의 보호 층 (228) 과 세라믹 층 (204) 의 상부 표면에 클램핑된 기판 사이의 콘택트는 방지된다. 유사하게, 보호 층 (228) 은 하단 에지 (232) 에서의 보호 층 (228) 과 시일 (220) 사이의 콘택트를 방지하도록 세라믹 층 (204) 아래로 연장하지 않는다. 이 방식으로, 보호 층 (228) 에 대한 손상은 방지될 수도 있다. 그러나, 일부 예들에서, 보호 층 (228) 은 도 2c에 도시된 바와 같이 상단 에지 (236) 로 그리고/또는 세라믹 층 (204) 의 하단 표면 (240) 상으로 완전히 연장할 수도 있다. 측벽 (224) 의 상단 에지 (236) 는 도시된 바와 같이 챔퍼처리될 수도 있다. 일부 예들에서, 보호 층 (228) 의 두께는 하단 에지 (232) 및/또는 상단 에지 (236) 근방에서 테이퍼질 수도 있다. 단지 예를 들면, 보호 층 (228) 은 상단 에지 (236) 에서 5 내지 10 mil 두께로부터 1 mil 두께로 테이퍼질 수도 있다.

또 다른 예에서, 세라믹 층 (204) 의 측벽들 (224) 은 폴리싱된다. 폴리싱은 측벽들 (224) 의 표면적을 감소시키고, 이에 따라 플라즈마에 노출된 재료의 양을 감소시킨다. 단지 예를 들면, 측벽들 (224) 은 30 내지 60 μin의 초기 표면 거칠기를 가질 수도 있다. 역으로, 본 개시의 원리들에 따른 측벽들 (224) 은 30 μin 미만의 표면 거칠기로 폴리싱된다. 일 예에서, 측벽들 (224) 은 1 내지 20 μin의 표면 거칠기로 폴리싱된다. 또 다른 예에서, 측벽들 (224) 은 10 μin 미만, 3 μin 미만, 또는 1 μin 미만의 표면 거칠기로 초-폴리싱된다 (ultra-polished).

측벽들 (224) 은 적합한 세라믹 폴리싱 시스템들 및 방법들을 사용하여 폴리싱될 수도 있다. 일 예에서, 측벽들 (224) 은 폴리싱 기판 (예를 들어, 브러시) 및 폴리싱 재료 (예를 들어, 다이아몬드 입자 폴리싱 페이스트) 를 사용하여 폴리싱된다.

여전히 또 다른 예에서, 세라믹 층 (204) 의 측벽들 (224) 은 산 에칭된다. 측벽들 (224) 을 산 에칭하는 것은 세라믹 층 (204) 으로부터의 재료를 선제적으로 제거하고 그렇지 않으면 세라믹 층 (204) 으로부터의 재료는 다른 플라즈마 프로세스들 동안 제거되고 그리고 챔버 내에 불순물들을 발생시킬 것이다.

예를 들어, 세라믹 층 (204) 은 알루미나 또는 나이트라이드 재료 및 소결 산 (sintering aid) 을 사용하여 형성될 수도 있다. 소결 산은 칼슘 옥사이드, 마그네슘 옥사이드, 실리콘 다이옥사이드, 등과 같은 재료들을 포함할 수도 있다. 또한, 세라믹 재료는 결국 복수의 상들, 예컨대, 결정질, 알루미나-풍부 상 및 혼합된 재료 유리상을 포함할 수도 있다. 통상적으로, 세라믹 층 (204) 의 유리상은 플라즈마에 노출될 때 에칭 및/또는 스퍼터링에 대해 알루미나 상보다 큰 민감성을 갖는다. 측벽들 (224) 을 산 에칭하는 것은 세라믹 층 (204) 으로부터 유리상 재료의 외측 부분 (예를 들어, 외측 미크론) 을 제거한다. 이 방식으로, 스퍼터링 및/또는 재증착과 연관된 유리상 재료는 세라믹 층 (204) 으로부터 선제적으로 제거된다. 측벽들 (224) 의 산 에칭을 수행하기 위한 예시적인 재료들은 이로 제한되지 않지만, 질산 및 불산을 포함한다.

이제 도 3을 참조하면, 본 개시의 원리들에 따른 기판 지지부를 형성하는 제 1 예시적인 방법 300이 304에서 시작된다. 308에서, 베이스 플레이트가 제공된다. 312에서, 본딩 층이 베이스 플레이트 상에 증착된다. 316에서, 세라믹 층이 본딩 층 상에 배치된다. 320에서, 도 2a, 도 2b, 및 도 2c에서 상기에 기술된 바와 같이 보호 층이 세라믹 층의 측벽들 상에 증착된다. 예를 들어, 보호 층은 세라믹 층 상에 스프레이코팅된다. 324에서, 보호 시일이 본딩 층 둘레에 배치된다. 일부 예들에서, 보호 시일은 320에서 보호 층을 증착하기 전에 본딩 층 둘레에 배치될 수도 있다. 다른 예들에서, 보호 층은 본딩 층 상에 세라믹 층을 배치하기 전에 세라믹 층의 측벽들 상에 증착될 수도 있다. 즉, 보호 층은 기판 지지부를 어셈블하기 전에 도포될 수도 있다. 방법 300은 328에서 종료된다.

이제 도 4를 참조하면, 본 개시의 원리들에 따른 기판 지지부를 형성하는 제 2 예시적인 방법 400이 404에서 시작된다. 408에서, 베이스 플레이트가 제공된다. 412에서, 본딩 층이 베이스 플레이트 상에 증착된다. 416에서, 세라믹 층이 본딩 층 상에 배치된다. 420에서, 도 2a, 도 2b, 및 도 2c에서 상기에 기술된 바와 같이 세라믹 층의 측벽들이 폴리싱된다. 예를 들어, 세라믹 층의 측벽들은 (예를 들어, 폴리싱 기판 및 폴리싱 재료를 사용하여) 30 μin 미만의 표면 거칠기로 폴리싱된다. 424에서, 보호 시일이 본딩 층 둘레에 배치된다. 일부 예들에서, 보호 시일은 420에서 측벽들을 폴리싱하기 전에 본딩 층 둘레에 배치될 수도 있다. 다른 예들에서, 세라믹 층의 측벽들은 본딩 층 상에 세라믹 층을 배치하기 전에 폴리싱될 수도 있다. 즉, 폴리싱은 기판 지지부를 어셈블하기 전에 수행될 수도 있다. 방법 400은 428에서 종료된다.

이제 도 5를 참조하면, 본 개시의 원리들에 따른 기판 지지부를 형성하는 제 3 예시적인 방법 500이 504에서 시작된다. 508에서, 베이스 플레이트가 제공된다. 512에서, 본딩 층이 베이스 플레이트 상에 증착된다. 516에서, 세라믹 층이 본딩 층 상에 배치된다. 520에서, 도 2a, 도 2b, 및 도 2c에서 상기에 기술된 바와 같이 세라믹 층의 측벽들이 산 에칭된다. 예를 들어, 세라믹 층의 측벽들은 측벽들로부터 유리상 재료의 외측 부분을 제거하도록 (예를 들어, 질산 및/또는 불산을 사용하여) 산 에칭된다. 524에서, 보호 시일은 본딩 층 둘레에 배치된다. 일부 예들에서, 보호 시일은 520에서 측벽들을 산 에칭하기 전에 본딩 층 둘레에 배치될 수도 있다. 다른 예들에서, 세라믹 층의 측벽들은 본딩 층 상에 세라믹 층을 배치하기 전에 산 에칭될 수도 있다. 즉, 산 에칭은 기판 지지부를 어셈블하기 전에 수행될 수도 있다. 방법 500은 528에서 종료된다.

전술한 기술은 단순히 특성을 예시하는 것이고 어떠한 방식으로도 본 개시, 이의 애플리케이션, 또는 용도를 제한하도록 의도되지 않는다. 본 개시의 광범위한 교시들은 다양한 형태들로 구현될 수 있다. 따라서, 본 개시는 특정한 예들을 포함하지만, 본 개시의 진정한 범위는 다른 수정들이 도면들, 명세서, 및 이하의 청구항들을 연구함으로써 명백해질 것이기 때문에 그렇게 제한되지 않아야 한다. 방법 내에서 하나 이상의 단계들은 본 개시의 원리들을 변경하지 않고 상이한 순서로 (또는 동시에) 실행될 수도 있다는 것이 이해되어야 한다. 또한, 실시예들 각각이 특정한 피처들을 갖는 것으로 상기에 기술되지만, 본 개시의 임의의 실시예에 대해 기술된 임의의 하나 이상의 이들 피처들은, 조합이 명시적으로 기술되지 않아도, 임의의 다른 실시예들의 피처들로 및/또는 임의의 다른 실시예들의 피처들과 조합하여 구현될 수 있다. 즉, 기술된 실시예들은 상호 배타적이지 않고, 하나 이상의 실시예들의 또 다른 실시예와의 치환들이 본 개시의 범위 내에 남는다.

엘리먼트들 간 (예를 들어, 모듈들, 회로 엘리먼트들, 반도체 층들, 등 간) 의 공간적 및 기능적 관계들은, "연결된 (connected)", "인게이지된 (engaged)", "커플링된 (coupled)", "인접한 (adjacent)", "옆에 (next to)", "~의 상단에 (on top of)", "위에 (above)", "아래에 (below)", 및 "배치된 (disposed)"을 포함하는, 다양한 용어들을 사용하여 기술된다. "직접적 (direct)"인 것으로 명시적으로 기술되지 않는 한, 제 1 엘리먼트와 제 2 엘리먼트 간의 관계가 상기 개시에서 기술될 때, 이 관계는 제 1 엘리먼트와 제 2 엘리먼트 사이에 다른 중개하는 엘리먼트가 존재하지 않는 직접적인 관계일 수 있지만, 또한 제 1 엘리먼트와 제 2 엘리먼트 사이에 (공간적으로 또는 기능적으로) 하나 이상의 중개하는 엘리먼트들이 존재하는 간접적인 관계일 수 있다. 본 명세서에서 사용된 바와 같이, 구 A, B, 및 C 중 적어도 하나는 비배타적인 논리 OR를 사용하여, 논리적으로 (A 또는 B 또는 C) 를 의미하는 것으로 해석되어야 하고, "적어도 하나의 A, 적어도 하나의 B, 및 적어도 하나의 C"를 의미하도록 해석되지 않아야 한다.

일부 구현예들에서, 제어기는 상술한 실례들의 일부일 수 있는 시스템의 일부이다. 이러한 시스템들은, 프로세싱 툴 또는 툴들, 챔버 또는 챔버들, 프로세싱용 플랫폼 또는 플랫폼들, 및/또는 특정 프로세싱 컴포넌트들 (웨이퍼 페데스탈, 가스 플로우 시스템, 등) 을 포함하는, 반도체 프로세싱 장비를 포함할 수 있다. 이러한 시스템들은 반도체 웨이퍼 또는 기판의 프로세싱 이전에, 프로세싱 동안에 그리고 프로세싱 이후에 그들의 동작을 제어하기 위한 전자장치에 통합될 수도 있다. 전자장치는 시스템 또는 시스템들의 다양한 컴포넌트들 또는 하위부품들을 제어할 수도 있는 "제어기"로서 지칭될 수도 있다. 제어기는, 시스템의 프로세싱 요건들 및/또는 타입에 따라서, 예를 들어 프로세싱 가스들의 전달, 온도 설정사항들 (예를 들어, 가열 및/또는 냉각), 압력 설정사항들, 진공 설정사항들, 전력 설정사항들, 무선 주파수 (RF) 생성기 설정사항들, RF 매칭 회로 설정사항들, 주파수 설정사항들, 플로우 레이트 설정사항들, 유체 전달 설정사항들, 위치 및 동작 설정사항들, 툴들 및 다른 전달 툴들 및/또는 특정 시스템과 연결되거나 인터페이싱된 로드록들 내외로의 웨이퍼 전달들을 포함하는, 본 명세서에 개시된 프로세스들 중 임의의 프로세스를 제어하도록 프로그램될 수도 있다.

일반적으로 말하면, 제어기는 인스트럭션들을 수신하고 인스트럭션들을 발행하고 동작을 제어하고 세정 동작들을 인에이블하고, 엔드포인트 측정들을 인에이블하는 등을 하는 다양한 집적 회로들, 로직, 메모리, 및/또는 소프트웨어를 갖는 전자장치로서 규정될 수도 있다. 집적 회로들은 프로그램 인스트럭션들을 저장하는 펌웨어의 형태의 칩들, 디지털 신호 프로세서들 (DSP), ASIC (application specific integrated circuit) 으로서 규정되는 칩들 및/또는 프로그램 인스트럭션들 (예를 들어, 소프트웨어) 을 실행하는 하나 이상의 마이크로프로세서들, 또는 마이크로제어기들을 포함할 수도 있다. 프로그램 인스트럭션들은 반도체 웨이퍼 상에서 또는 반도체 웨이퍼에 대한 특정 프로세스를 실행하기 위한 동작 파라미터들을 규정하는, 다양한 개별 설정사항들 (또는 프로그램 파일들) 의 형태로 제어기로 또는 시스템으로 전달되는 인스트럭션들일 수도 있다. 일부 실시예들에서, 동작 파라미터들은 하나 이상의 층들, 재료들, 금속들, 옥사이드들, 실리콘, 실리콘 다이옥사이드, 표면들, 회로들, 및/또는 웨이퍼의 다이들의 제조 동안에 하나 이상의 프로세싱 단계들을 달성하도록 프로세스 엔지니어에 의해서 규정된 레시피의 일부일 수도 있다.

제어기는, 일부 구현예들에서, 시스템에 통합되거나, 시스템에 커플링되거나, 이와 달리 시스템에 네트워킹되거나, 또는 이들의 조합으로 되는 컴퓨터에 커플링되거나 이의 일부일 수도 있다. 예를 들어, 제어기는 웨이퍼 프로세싱의 리모트 액세스를 가능하게 할 수 있는 공장 (fab) 호스트 컴퓨터 시스템의 전부 또는 일부이거나 "클라우드" 내에 있을 수도 있다. 컴퓨터는 제조 동작들의 현 진행을 모니터링하고, 과거 제조 동작들의 이력을 조사하고, 복수의 제조 동작들로부터 경향들 또는 성능 계측치들을 조사하고, 현 프로세싱의 파라미터들을 변경하고, 현 프로세싱을 따르는 프로세싱 단계들을 설정하고, 또는 새로운 프로세스를 시작하기 위해서 시스템으로의 리모트 액세스를 인에이블할 수도 있다. 일부 예들에서, 리모트 컴퓨터 (예를 들어, 서버) 는 로컬 네트워크 또는 인터넷을 포함할 수도 있는 네트워크를 통해서 프로세스 레시피들을 시스템에 제공할 수 있다. 리모트 컴퓨터는 차후에 리모트 컴퓨터로부터 시스템으로 전달될 파라미터들 및/또는 설정사항들의 입력 또는 프로그래밍을 가능하게 하는 사용자 인터페이스를 포함할 수도 있다. 일부 예들에서, 제어기는 하나 이상의 동작들 동안에 수행될 프로세스 단계들 각각에 대한 파라미터들을 특정한, 데이터의 형태의 인스트럭션들을 수신한다. 이 파라미터들은 제어기가 제어하거나 인터페이싱하도록 구성된 툴의 타입 및 수행될 프로세스의 타입에 특정적일 수 있다는 것이 이해되어야 한다. 따라서, 상술한 바와 같이, 제어기는 예를 들어 서로 네트워킹되어서 함께 공통 목적을 위해서, 예를 들어 본 명세서에 기술된 프로세스들 및 제어들을 위해서 협력하는 하나 이상의 개별 제어기들을 포함함으로써 분산될 수도 있다. 이러한 목적을 위한 분산형 제어기의 예는 챔버 상의 프로세스를 제어하도록 조합되는, (예를 들어, 플랫폼 레벨에서 또는 리모트 컴퓨터의 일부로서) 원격으로 위치한 하나 이상의 집적 회로들과 통신하는 챔버 상의 하나 이상의 집적 회로들일 수 있다.

비한정적으로, 예시적인 시스템들은 플라즈마 에칭 챔버 또는 모듈, 증착 챔버 또는 모듈, 스핀-린스 챔버 또는 모듈, 금속 도금 챔버 또는 모듈, 세정 챔버 또는 모듈, 베벨 에지 에칭 챔버 또는 모듈, PVD (physical vapor deposition) 챔버 또는 모듈, CVD (chemical vapor deposition) 챔버 또는 모듈, ALD (atomic layer deposition) 챔버 또는 모듈, ALE (atomic layer etch) 챔버 또는 모듈, 이온 주입 챔버 또는 모듈, 트랙 (track) 챔버 또는 모듈, 및 반도체 웨이퍼들의 제조 및/또는 제작 시에 사용되거나 연관될 수도 있는 임의의 다른 반도체 프로세싱 시스템들을 포함할 수도 있다.

상술한 바와 같이, 툴에 의해서 수행될 프로세스 단계 또는 단계들에 따라서, 제어기는, 반도체 제조 공장 내의 툴 위치들 및/또는 로드 포트들로부터/로 웨이퍼들의 컨테이너들을 이동시키는 재료 이송 시에 사용되는, 다른 툴 회로들 또는 모듈들, 다른 툴 컴포넌트들, 클러스터 툴들, 다른 툴 인터페이스들, 인접 툴들, 이웃하는 툴들, 공장 도처에 위치한 툴들, 메인 컴퓨터, 다른 제어기 또는 툴들 중 하나 이상과 통신할 수도 있다.

Claims (19)

- 기판 프로세싱 시스템을 위한 기판 지지부에 있어서,

베이스 플레이트;

상기 베이스 플레이트 상에 배치된 세라믹 층으로서, 상기 세라믹 층은 하부 표면, 기판을 지지하도록 구성된 상부 표면, 및 상기 하부 표면으로부터 상기 상부 표면으로 연장하는 상기 세라믹 층의 주변부 둘레의 측벽들을 포함하고, 그리고 상기 세라믹 층은 제 1 재료를 포함하는, 상기 세라믹 층;

상기 베이스 플레이트와 상기 세라믹 층 사이에 제공된 본딩 층; 및

상기 세라믹 층의 상기 측벽들 상에 형성된 보호 층으로서, 상기 보호 층은 상기 제 1 재료와 상이한 제 2 재료를 포함하는, 상기 보호 층을 포함하는, 기판 프로세싱 시스템을 위한 기판 지지부. - 제 1 항에 있어서,

상기 제 2 재료는 비-알루미나 기반 재료인, 기판 프로세싱 시스템을 위한 기판 지지부. - 제 1 항에 있어서,

상기 제 2 재료는 이트륨 옥사이드 스프레이코팅인, 기판 프로세싱 시스템을 위한 기판 지지부. - 제 1 항에 있어서,

상기 제 2 재료는 상기 제 1 재료보다 플라즈마에 대해 보다 큰 내성을 갖는, 기판 프로세싱 시스템을 위한 기판 지지부. - 제 1 항에 있어서,

상기 보호 층의 두께는 0.005" 내지 0.010"인, 기판 프로세싱 시스템을 위한 기판 지지부. - 제 1 항에 있어서,

상기 보호 층은 상기 하부 표면에 인접한 상기 측벽들의 하단 에지로부터 상기 상부 표면에 인접한 상기 측벽들의 상단 에지로 연장하는, 기판 프로세싱 시스템을 위한 기판 지지부. - 제 1 항에 있어서,

상기 보호 층은 상기 하부 표면에 인접한 상기 측벽들의 하단 에지로부터 상기 상부 표면에 인접한 상기 측벽들의 상단 에지로부터 미리 결정된 거리까지 연장하는, 기판 프로세싱 시스템을 위한 기판 지지부. - 제 7 항에 있어서,

상기 미리 결정된 거리는 상기 상단 에지로부터 적어도 0.001"인, 기판 프로세싱 시스템을 위한 기판 지지부. - 제 1 항에 있어서,

상기 상부 표면에 인접한 상기 측벽들의 상단 에지는 챔퍼처리되는 (chamfered), 기판 프로세싱 시스템을 위한 기판 지지부. - 제 1 항에 있어서,

상기 보호 층의 두께는 상기 하부 표면에 인접한 상기 측벽들의 하단 에지 및 상기 상부 표면에 인접한 상기 측벽들의 상단 에지 중 적어도 하나에서 테이퍼지는, 기판 프로세싱 시스템을 위한 기판 지지부. - 제 10 항에 있어서,

상기 보호 층의 상기 두께는 0.005" 내지 0.010"로부터 0.001"로 테이퍼지는, 기판 프로세싱 시스템을 위한 기판 지지부. - 제 1 항에 있어서,

상기 베이스 플레이트와 상기 세라믹 층의 상기 하부 표면 사이의 상기 본딩 층의 주변부 들레에 배치된 보호 시일을 더 포함하고, 상기 보호 시일은 상기 세라믹 층의 상기 하부 표면 상으로 연장하지 않는, 기판 프로세싱 시스템을 위한 기판 지지부. - 기판 프로세싱 시스템을 위한 기판 지지부를 형성하기 위한 방법에 있어서,

베이스 플레이트를 제공하는 단계;

상기 베이스 플레이트 상에 본딩 층을 증착하는 단계;

상기 베이스 플레이트 상에 세라믹 층을 배치하는 단계로서, 상기 세라믹 층은 하부 표면, 기판을 지지하도록 구성된 상부 표면, 및 상기 하부 표면으로부터 상기 상부 표면으로 연장하는 상기 세라믹 층의 주변부 둘레의 측벽들을 포함하고, 그리고 상기 세라믹 층은 제 1 재료를 포함하는, 상기 베이스 플레이트 상에 상기 세라믹 층을 배치하는 단계; 및

상기 세라믹 층의 상기 측벽들 상에 보호 층을 형성하는 단계로서, 상기 보호 층은 상기 제 1 재료와 상이한 제 2 재료를 포함하는, 상기 세라믹 층의 상기 측벽들 상에 상기 보호 층을 형성하는 단계,

상기 세라믹 층의 상기 측벽들을 폴리싱하는 단계, 및

상기 세라믹 층의 상기 측벽들을 산 에칭하는 단계 중 적어도 하나를 포함하는, 기판 프로세싱 시스템을 위한 기판 지지부를 형성하기 위한 방법. - 제 13 항에 있어서,

상기 제 2 재료는 비-알루미나 기반 재료인, 기판 프로세싱 시스템을 위한 기판 지지부를 형성하기 위한 방법. - 제 13 항에 있어서,

상기 보호 층을 형성하는 단계는 상기 세라믹 층의 상기 측벽들 상에 이트륨 옥사이드 스프레이코팅을 도포하는 단계를 포함하는, 기판 프로세싱 시스템을 위한 기판 지지부를 형성하기 위한 방법. - 제 13 항에 있어서,

상기 제 2 재료는 상기 제 1 재료보다 플라즈마에 대해 보다 큰 내성을 갖는, 기판 프로세싱 시스템을 위한 기판 지지부를 형성하기 위한 방법. - 제 13 항에 있어서,

상기 세라믹 층의 상기 측벽들을 폴리싱하는 단계는 30 μin 미만의 표면 거칠기로 상기 측벽들을 폴리싱하는 단계를 포함하는, 기판 프로세싱 시스템을 위한 기판 지지부를 형성하기 위한 방법. - 제 13 항에 있어서,

상기 세라믹 층의 상기 측벽들을 폴리싱하는 단계는 10 μin 미만의 표면 거칠기로 상기 측벽들을 폴리싱하는 단계를 포함하는, 기판 프로세싱 시스템을 위한 기판 지지부를 형성하기 위한 방법. - 제 13 항에 있어서,

상기 세라믹 층의 상기 측벽들을 산 에칭하는 단계는 상기 측벽들의 유리상 재료의 외측 부분을 제거하도록 상기 측벽들을 산 에칭하는 단계를 포함하는, 기판 프로세싱 시스템을 위한 기판 지지부를 형성하기 위한 방법.

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201662357513P | 2016-07-01 | 2016-07-01 | |

| US62/357,513 | 2016-07-01 | ||

| US15/594,091 | 2017-05-12 | ||

| US15/594,091 US20180005867A1 (en) | 2016-07-01 | 2017-05-12 | Esc ceramic sidewall modification for particle and metals performance enhancements |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20180004009A true KR20180004009A (ko) | 2018-01-10 |

Family

ID=60807764

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020170081734A KR20180004009A (ko) | 2016-07-01 | 2017-06-28 | 입자 및 금속들 성능 향상들을 위한 esc 세라믹 측벽 개질 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20180005867A1 (ko) |

| JP (1) | JP7186494B2 (ko) |

| KR (1) | KR20180004009A (ko) |

| CN (1) | CN107579031A (ko) |

| TW (1) | TW201812980A (ko) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11133211B2 (en) * | 2018-08-22 | 2021-09-28 | Lam Research Corporation | Ceramic baseplate with channels having non-square corners |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1193233A1 (en) * | 2000-02-07 | 2002-04-03 | Ibiden Co., Ltd. | Ceramic substrate for semiconductor production/inspection device |

| JP2001319967A (ja) | 2000-05-11 | 2001-11-16 | Ibiden Co Ltd | セラミック基板の製造方法 |

| US6613442B2 (en) * | 2000-12-29 | 2003-09-02 | Lam Research Corporation | Boron nitride/yttria composite components of semiconductor processing equipment and method of manufacturing thereof |

| JP4397271B2 (ja) | 2003-05-12 | 2010-01-13 | 東京エレクトロン株式会社 | 処理装置 |

| JP2008016709A (ja) | 2006-07-07 | 2008-01-24 | Shinko Electric Ind Co Ltd | 静電チャックおよびその製造方法 |

| US9543181B2 (en) * | 2008-07-30 | 2017-01-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | Replaceable electrostatic chuck sidewall shield |

| JP5876992B2 (ja) | 2011-04-12 | 2016-03-02 | 株式会社日立ハイテクノロジーズ | プラズマ処理装置 |

| KR20170109690A (ko) | 2012-04-26 | 2017-09-29 | 어플라이드 머티어리얼스, 인코포레이티드 | Esc 본딩 접착제 부식을 방지하기 위한 방법들 및 장치 |

| CN104241183B (zh) * | 2013-06-08 | 2017-09-08 | 中微半导体设备(上海)有限公司 | 静电吸盘的制造方法,静电吸盘及等离子体处理装置 |

| KR101385950B1 (ko) | 2013-09-16 | 2014-04-16 | 주식회사 펨빅스 | 정전척 및 정전척 제조 방법 |

| JP6296770B2 (ja) | 2013-11-29 | 2018-03-20 | 日本特殊陶業株式会社 | 基板載置装置 |

| KR20160015510A (ko) * | 2014-07-30 | 2016-02-15 | 삼성전자주식회사 | 정전척 어셈블리, 이를 구비하는 반도체 제조장치, 및 이를 이용한 플라즈마 처리방법 |

-

2017

- 2017-05-12 US US15/594,091 patent/US20180005867A1/en not_active Abandoned

- 2017-06-27 TW TW106121344A patent/TW201812980A/zh unknown

- 2017-06-28 KR KR1020170081734A patent/KR20180004009A/ko not_active Application Discontinuation

- 2017-06-30 JP JP2017128341A patent/JP7186494B2/ja active Active

- 2017-06-30 CN CN201710521432.0A patent/CN107579031A/zh active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| CN107579031A (zh) | 2018-01-12 |

| JP7186494B2 (ja) | 2022-12-09 |

| US20180005867A1 (en) | 2018-01-04 |

| TW201812980A (zh) | 2018-04-01 |

| JP2018014491A (ja) | 2018-01-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7401589B2 (ja) | 静電チャック接合のための永久二次浸食封じ込め | |

| TWI783960B (zh) | 具有改良的處理均勻性之基板支撐件 | |

| JP6739940B2 (ja) | 埋め込み電極を伴うガス分配セラミック板 | |

| KR102521717B1 (ko) | 아킹 (arcing) 을 감소시키기 위한 헬륨 플러그 설계 | |

| CN111771273A (zh) | 具有陶瓷基板的多板式静电卡盘 | |

| JP2023502137A (ja) | プラズマチャンバの低温焼結コーティング | |

| KR20180016300A (ko) | 부분적으로 그물 형상이고 부분적으로 거의 그물 형상인 실리콘 카바이드 cvd | |

| JP7470101B2 (ja) | 寿命が延長された閉じ込めリング | |

| JP7186494B2 (ja) | 粒子性能および金属性能の改善のためのescセラミック側壁の加工 | |

| TWI849145B (zh) | 基板處理系統用的縮小直徑承載環硬件 | |

| TW202231136A (zh) | 用於浮動變壓器耦合電漿腔室氣體板的承載環 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |