KR20170103689A - 플라즈마 프로세싱 시스템들을 위한 고순도 sp3 결합들을 가진 화학적 기상 증착 (cvd) 다이아몬드 코팅을 포함한 에지 링들과 같은 컴포넌트들 - Google Patents

플라즈마 프로세싱 시스템들을 위한 고순도 sp3 결합들을 가진 화학적 기상 증착 (cvd) 다이아몬드 코팅을 포함한 에지 링들과 같은 컴포넌트들 Download PDFInfo

- Publication number

- KR20170103689A KR20170103689A KR1020170027531A KR20170027531A KR20170103689A KR 20170103689 A KR20170103689 A KR 20170103689A KR 1020170027531 A KR1020170027531 A KR 1020170027531A KR 20170027531 A KR20170027531 A KR 20170027531A KR 20170103689 A KR20170103689 A KR 20170103689A

- Authority

- KR

- South Korea

- Prior art keywords

- diamond coating

- plasma

- bonds

- processing chamber

- purity

- Prior art date

Links

- 238000012545 processing Methods 0.000 title claims abstract description 95

- 238000000576 coating method Methods 0.000 title claims abstract description 88

- 239000010432 diamond Substances 0.000 title claims abstract description 79

- 229910003460 diamond Inorganic materials 0.000 title claims abstract description 79

- 239000011248 coating agent Substances 0.000 title claims abstract description 76

- 238000005229 chemical vapour deposition Methods 0.000 title claims abstract description 33

- 239000000758 substrate Substances 0.000 claims abstract description 68

- NJPPVKZQTLUDBO-UHFFFAOYSA-N novaluron Chemical compound C1=C(Cl)C(OC(F)(F)C(OC(F)(F)F)F)=CC=C1NC(=O)NC(=O)C1=C(F)C=CC=C1F NJPPVKZQTLUDBO-UHFFFAOYSA-N 0.000 claims abstract description 41

- 238000000034 method Methods 0.000 claims description 38

- 238000009826 distribution Methods 0.000 claims description 18

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 9

- 239000000463 material Substances 0.000 claims description 9

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 5

- 238000009616 inductively coupled plasma Methods 0.000 claims description 5

- 229910052710 silicon Inorganic materials 0.000 claims description 5

- 239000010703 silicon Substances 0.000 claims description 5

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 claims description 5

- 235000012239 silicon dioxide Nutrition 0.000 claims description 5

- 239000000377 silicon dioxide Substances 0.000 claims description 4

- 229910004298 SiO 2 Inorganic materials 0.000 claims description 3

- 239000007789 gas Substances 0.000 description 69

- 230000008569 process Effects 0.000 description 20

- 238000005530 etching Methods 0.000 description 9

- 235000012431 wafers Nutrition 0.000 description 9

- 239000004065 semiconductor Substances 0.000 description 8

- 230000007797 corrosion Effects 0.000 description 7

- 238000005260 corrosion Methods 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 7

- 239000000203 mixture Substances 0.000 description 7

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 5

- 229910052799 carbon Inorganic materials 0.000 description 5

- 230000006698 induction Effects 0.000 description 5

- 150000002500 ions Chemical class 0.000 description 5

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 239000002243 precursor Substances 0.000 description 4

- 238000010926 purge Methods 0.000 description 4

- 239000000376 reactant Substances 0.000 description 4

- 238000000151 deposition Methods 0.000 description 3

- 230000008021 deposition Effects 0.000 description 3

- 238000005215 recombination Methods 0.000 description 3

- 230000006798 recombination Effects 0.000 description 3

- 230000001154 acute effect Effects 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 238000001816 cooling Methods 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000012530 fluid Substances 0.000 description 2

- 239000008246 gaseous mixture Substances 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 238000004380 ashing Methods 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000000112 cooling gas Substances 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 230000005672 electromagnetic field Effects 0.000 description 1

- 230000003628 erosive effect Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 239000007943 implant Substances 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 239000010410 layer Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 239000012811 non-conductive material Substances 0.000 description 1

- -1 oxides Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/687—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches

- H01L21/68714—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support

- H01L21/68757—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support characterised by a coating or a hardness or a material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/02274—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/50—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating using electric discharges

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/4401—Means for minimising impurities, e.g. dust, moisture or residual gas, in the reaction chamber

- C23C16/4404—Coatings or surface treatment on the inside of the reaction chamber or on parts thereof

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/455—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for introducing gases into reaction chamber or for modifying gas flows in reaction chamber

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/458—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for supporting substrates in the reaction chamber

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/458—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating characterised by the method used for supporting substrates in the reaction chamber

- C23C16/4582—Rigid and flat substrates, e.g. plates or discs

- C23C16/4583—Rigid and flat substrates, e.g. plates or discs the substrate being supported substantially horizontally

- C23C16/4585—Devices at or outside the perimeter of the substrate support, e.g. clamping rings, shrouds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32009—Arrangements for generation of plasma specially adapted for examination or treatment of objects, e.g. plasma sources

- H01J37/32082—Radio frequency generated discharge

- H01J37/32091—Radio frequency generated discharge the radio frequency energy being capacitively coupled to the plasma

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32009—Arrangements for generation of plasma specially adapted for examination or treatment of objects, e.g. plasma sources

- H01J37/32082—Radio frequency generated discharge

- H01J37/321—Radio frequency generated discharge the radio frequency energy being inductively coupled to the plasma

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32009—Arrangements for generation of plasma specially adapted for examination or treatment of objects, e.g. plasma sources

- H01J37/32357—Generation remote from the workpiece, e.g. down-stream

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32431—Constructional details of the reactor

- H01J37/32458—Vessel

- H01J37/32477—Vessel characterised by the means for protecting vessels or internal parts, e.g. coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32431—Constructional details of the reactor

- H01J37/32623—Mechanical discharge control means

- H01J37/32642—Focus rings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32431—Constructional details of the reactor

- H01J37/32715—Workpiece holder

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32431—Constructional details of the reactor

- H01J37/32798—Further details of plasma apparatus not provided for in groups H01J37/3244 - H01J37/32788; special provisions for cleaning or maintenance of the apparatus

- H01J37/32807—Construction (includes replacing parts of the apparatus)

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02115—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material being carbon, e.g. alpha-C, diamond or hydrogen doped carbon

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02296—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer

- H01L21/02299—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment

- H01L21/02312—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment treatment by exposure to a gas or vapour

- H01L21/02315—Forming insulating materials on a substrate characterised by the treatment performed before or after the formation of the layer pre-treatment treatment by exposure to a gas or vapour treatment by exposure to a plasma

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02527—Carbon, e.g. diamond-like carbon

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/6831—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using electrostatic chucks

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/687—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches

- H01L21/68714—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support

- H01L21/68721—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support characterised by edge clamping, e.g. clamping ring

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/687—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches

- H01L21/68714—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support

- H01L21/68735—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support characterised by edge profile or support profile

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Plasma & Fusion (AREA)

- Analytical Chemistry (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Chemical Vapour Deposition (AREA)

- Plasma Technology (AREA)

- Drying Of Semiconductors (AREA)

Abstract

플라즈마 프로세싱 시스템을 위한 페데스탈은 기판 지지 표면을 포함한다. 환형 에지 링은 기판 지지 표면의 주변 주위에 배치된다. CVD (chemical vapor deposition) 다이아몬드 코팅은 환형 링의 플라즈마-노출된 표면 상에 배치된다. CVD 다이아몬드 코팅은 sp3 결합들을 포함한다. 다이아몬드 코팅 내의 sp3 결합들의 순도는 90 % 초과이다.

Description

본 개시는 기판들을 위한 플라즈마 프로세싱 시스템들, 보다 구체적으로 기판들을 위한 플라즈마 프로세싱 시스템들의 프로세싱 챔버들 내에서 사용되는 에지 링들과 같은 컴포넌트들에 관한 것이다.

본 명세서에 제공된 배경 기술 설명은 일반적으로 본 개시의 맥락을 제공하기 위한 것이다. 본 발명자들의 성과로서 본 배경기술 섹션에 기술되는 정도의 성과, 뿐만 아니라 출원시 종래 기술로서 인정되지 않을 수도 있는 기술의 양태들은 본 개시에 대한 종래 기술로서 명시적으로나 암시적으로 인정되지 않는다.

기판 프로세싱 시스템들은 반도체 웨이퍼들과 같은 기판들의 증착, 에칭 및/또는 다른 처리를 수행하도록 사용될 수도 있다. 기판은 기판 프로세싱 시스템의 프로세싱 챔버 내에서 페데스탈 상에 배치될 수도 있다. 예를 들어 에칭 또는 증착 동안, 하나 이상의 전구체들을 포함한 가스 혼합물이 프로세싱 챔버 내로 도입되고 그리고 플라즈마는 기판을 에칭하거나 기판 상에 막을 증착하도록 스트라이킹될 (strike) 수도 있다.

에지 링들은 기판의 방사상으로 외측 에지 근방에서 플라즈마의 프로파일을 조정하도록 사용된다. 예를 들어 에칭 프로세스에서, 에지 링은 에칭 레이트 또는 에칭 프로파일을 조정하도록 사용될 수도 있다. 에지 링은 통상적으로 기판의 방사상으로 외측 에지 주위에서 페데스탈 상에 위치된다. 기판의 방사상으로 외측 에지에서의 프로세스 조건들은 에지 링의 포지션, 에지 링의 내측 에지의 형상 또는 프로파일, 기판의 상부 표면에 대한 에지 링의 높이, 에지 링의 재료, 등을 변화시킴으로써 수정될 수 있다.

에지 링을 변화시키는 것은 보통 프로세싱 챔버가 개방될 것을 요구하고, 이는 바람직하지 않다. 즉, 에지 링의 에지 효과는 프로세싱 챔버를 개방하지 않고 변경될 수 없다. 에지 링이 에칭 동안 플라즈마에 의해 부식될 때, 에지 효과가 변화한다.

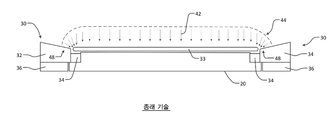

이제 도 1 및 도 2를 참조하면, 기판 프로세싱 시스템은 페데스탈 (20) 및 에지 링 (30) 을 포함할 수도 있다. 에지 링 (30) 은 하나 이상의 부분들을 포함할 수도 있다. 도 1 및 도 2의 예에서, 에지 링 (30) 은 기판 (33) 의 방사상으로 외측 에지 근방에 배치된 제 1 환형 부분 (32) 을 포함한다. 제 2 환형 부분 (34) 은 기판 (33) 아래에서 제 1 환형 부분으로부터 방사상으로 내측에 위치된다. 제 3 환형 부분 (36) 은 제 1 환형 부분 (32) 아래에 배치된다. 사용 동안, 플라즈마 (42) 는 기판 (33) 의 노출된 부분들을 에칭하도록 기판 (33) 으로 지향된다. 에지 링 (30) 은 기판 (33) 의 균일한 에칭이 발생하게 플라즈마의 성형을 돕도록 배치된다.

도 2에서, 에지 링 (30) 이 사용된 후에, 에지 링 (30) 의 방사상으로 내측 부분의 상부 표면은 48로 식별된 바와 같이 부식을 나타낼 수도 있다. 그 결과, 플라즈마 (42) 는 44에서 볼 수 있는 바와 같이 기판 (33) 의 방사상으로 내측 부분들의 에칭보다 빠른 레이트로 기판 (33) 의 방사상으로 외측 에지를 에칭하려는 경향이 있을 수도 있다.

코팅들은 프로세싱 챔버 내의 에지 링 및 다른 컴포넌트들의 내부식성을 개선하도록 사용된다. 예를 들어, 다이아몬드-같은 탄소 코팅이 테스트되었다. 그러나, 코팅은 산소 플라즈마에 의해 매우 신속하게 에칭되었다. 반도체 제조 장비 산업은 다이아몬드-같은 탄소 코팅들의 고 에칭 레이트에 기인하여 에지 링 부식을 감소시키기 위한 다른 방법들을 추구한다.

플라즈마 프로세싱 시스템을 위한 페데스탈은 기판 지지 표면을 포함한다. 환형 에지 링은 기판 지지 표면의 주변 주위에 배치된다. 다이아몬드 코팅은 환형 링의 플라즈마-노출된 표면 상에 배치된다. 다이아몬드 코팅은 sp3 결합들을 포함한다. 다이아몬드 코팅 내의 sp3 결합들의 순도는 90 % 초과이다.

다른 특징들에서, 다이아몬드 코팅 내의 sp3 결합들의 순도는 95 % 초과이다. 다이아몬드 코팅 내의 sp3 결합들의 순도는 99 % 초과이다. 다이아몬드 코팅은 CVD (chemical vapor deposition) 를 사용하여 환형 에지 링 상에 증착된다.

플라즈마 프로세싱 시스템은 프로세싱 챔버를 포함한다. 페데스탈은 프로세싱 챔버 내에 배치된다. 플라즈마 소스는 프로세싱 챔버 내에서 플라즈마를 생성한다. 플라즈마 소스는 CCP (capacitively-coupled plasma) 소스를 포함한다. 플라즈마 소스는 ICP (inductively-coupled plasma) 소스를 포함한다.

플라즈마 프로세싱 시스템은 프로세싱 챔버를 포함한다. 페데스탈은 프로세싱 챔버 내에 배치된다. 리모트 플라즈마 소스는 플라즈마를 프로세싱 챔버로 공급한다.

플라즈마 프로세싱 시스템은 프로세싱 챔버 및 프로세싱 챔버로 플라즈마를 공급하거나 프로세싱 챔버 내에서 플라즈마를 생성하는 것 중 하나를 하기 위한 플라즈마 소스르르 포함한다. 프로세싱 챔버 내에 배치된 적어도 하나의 컴포넌트 (component) 는 다이아몬드 코팅을 포함한다. 다이아몬드 코팅은 sp3 결합들을 포함한다. 다이아몬드 코팅 내의 sp3 결합들의 순도는 90 % 초과이다.

다른 특징들에서, 다이아몬드 코팅 내의 sp3 결합들의 순도는 95 % 초과이다. 다이아몬드 코팅 내의 sp3 결합들의 순도는 99 % 초과이다. 다이아몬드 코팅은 CVD (chemical vapor deposition) 를 사용하여 적어도 하나의 컴포넌트 상에 증착된다.

다른 특징들에서, 적어도 하나의 컴포넌트는 에지 링, 챔버 벽, 가스 분배 디바이스, 가스 주입기, 프로세싱 챔버 내로의 윈도우, 및 페데스탈의 상부 표면으로 구성된 그룹으로부터 선택된다.

플라즈마 프로세싱 시스템을 위한 에지 링은 환형 링 및 사용 동안 플라즈마에 노출되는 환형 링의 표면 상에 배치된 다이아몬드 코팅을 포함한다. 다이아몬드 코팅은 sp3 결합들을 포함한다. 다이아몬드 코팅 내의 sp3 결합들의 순도는 90 % 초과이다.

다른 특징들에서, 다이아몬드 코팅 내의 sp3 결합들의 순도는 95 % 초과이다. 다이아몬드 코팅 내의 sp3 결합들의 순도는 99 % 초과이다. 다이아몬드 코팅은 CVD (chemical vapor deposition) 를 사용하여 환형 링 상에 증착된다. 환형 링은 실리콘 (Si), 실리콘 카바이드 (SiC) 및 실리콘 다이옥사이드 (SiO2) 로 구성된 그룹으로부터 선택된 재료로 이루어진다.

본 개시의 적용 가능성의 추가의 영역들은 상세한 기술, 청구항들 및 도면들로부터 분명해질 것이다. 상세한 기술 및 구체적인 예들은 오직 예시의 목적들을 위해 의도된 것이고 본 개시의 범위를 제한하도록 의도되지 않는다.

본 개시는 상세한 기술 및 첨부된 도면들로부터 보다 완전히 이해될 것이다.

도 1은 종래 기술에 따른, 페데스탈 및 에지 링의 측단면도이다.

도 2는 에지 링이 플라즈마에 의해 부식된 (eroded) 후, 종래 기술에 따른, 페데스탈 및 에지 링의 측단면도이다.

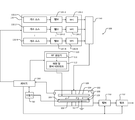

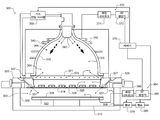

도 3은 본 개시에 따른, 고순도 sp3 결합들을 가진 CVD 다이아몬드 코팅을 포함한 에지 링 및 페데스탈의 예의 측단면도이다.

도 4 내지 도 6은 프로세싱 챔버 및 프로세싱 챔버 내에 위치된 고순도 sp3 결합들을 가진 다이아몬드 코팅을 가진 적어도 하나의 컴포넌트를 포함한 다양한 기판 프로세싱 시스템들의 기능적 블록도들이다.

도면들에서, 참조 번호들은 유사한 그리고/또는 동일한 엘리먼트들 (elements) 을 식별하기 위해 재사용될 수도 있다.

도 1은 종래 기술에 따른, 페데스탈 및 에지 링의 측단면도이다.

도 2는 에지 링이 플라즈마에 의해 부식된 (eroded) 후, 종래 기술에 따른, 페데스탈 및 에지 링의 측단면도이다.

도 3은 본 개시에 따른, 고순도 sp3 결합들을 가진 CVD 다이아몬드 코팅을 포함한 에지 링 및 페데스탈의 예의 측단면도이다.

도 4 내지 도 6은 프로세싱 챔버 및 프로세싱 챔버 내에 위치된 고순도 sp3 결합들을 가진 다이아몬드 코팅을 가진 적어도 하나의 컴포넌트를 포함한 다양한 기판 프로세싱 시스템들의 기능적 블록도들이다.

도면들에서, 참조 번호들은 유사한 그리고/또는 동일한 엘리먼트들 (elements) 을 식별하기 위해 재사용될 수도 있다.

관련 출원들에 대한 상호 참조

이 출원은 2016년 3월 3일 출원된 미국 가출원 제 62/303,091 호 및 2016년 3월 21일 출원된 미국 가출원 제 62/310,993 호의 이득을 주장한다. 상기 언급된 출원들의 전체 개시들은 참조로서 본 명세서에 인용된다.

본 개시는 플라즈마 프로세싱 챔버 내에서 사용되는 에지 링에 관한 것이다. 에지 링의 플라즈마-대면 표면은 CVD (chemical vapor deposition) 다이아몬드 코팅으로 코팅된다. 상기에 기술된 다이아몬드-같은 탄소 코팅들은 다이아몬드-같은 탄소 코팅들 내의 sp2 결합들의 고농도에 기인하여 플라즈마 애플리케이션들에서 실패한다고 여겨진다. 일부 예들에서, 본 명세서에 기술된 CVD 다이아몬드 코팅은 고순도 sp3 결합들을 포함한다. 고순도 sp3 결합들을 갖는 것은 CVD 다이아몬드 코팅으로 하여금 보다 긴 기간들 동안 플라즈마 부식에 견디게 한다.

고순도의 sp3 결합들은 챔버 성능 및 내부식성을 개선한다. 고순도 sp3 결합들을 가진 CVD 다이아몬드 코팅을 사용한 에지 링들은 코팅의 저 플라즈마 부식 레이트에 기인하여 MTBC (mean time between change) 를 개선한다. CVD 다이아몬드 코팅은 깨끗하게 에칭될 수 있고, 이는 기판 상 (on-substrate) 디펙트들을 감소시킨다. CVD 다이아몬드 코팅은 또한 고 열 전도도를 갖고, 이는 기판들의 에지들에서의 에칭 균일성을 개선한다. 일부 예들에서, CVD 다이아몬드 코팅은 미국 캘리포니아 95054 산타 클라라 버턴 드라이브 3901 소재의 Element Six Technologies U.S. Corporation에 의해 공급된다.

에지 링은 플라즈마 프로세싱 챔버 내에서 소모성 컴포넌트들을 위해 사용되는 실리콘, 실리콘 카바이드 (SiC), 석영, 및 다른 재료들로 이루어진 에지 링들에 대한 교체품으로서 사용될 수도 있다. 일부 예들의 테스트에서, 본 명세서에 기술된 CVD 다이아몬드 코팅을 가진 에지 링들은 CVD 다이아몬드 코팅이 없고 외관상 잔여물이 없는 SiC를 사용하는 에지 링들보다 MTBC를 개선하였다. 보다 저 부식 레이트 및 주로 탄소의 사용에 기인하여, 기판 상 디펙트들은 상대적으로 낮아질 것으로 기대된다. 다이아몬드 코팅을 가진 에지 링은 장비 제작업자들이 차세대 입자 사양들을 충족하고 MTBC를 개선하는 것을 도울 것이다.

보다 저 부식 레이트에 기인하여, 에지 링들의 기하학적 구조는 보다 큰 수의 RFH들 (RF hours) 동안 유지될 수 있고, RFH들은 소비자들이 동일한 MTBC를 유지하길 원한다면 보다 많은 프로세스 반복을 허용한다.

에지 링들에 대해 기술될지라도, 본 개시의 원리들은 또한 기판 프로세싱 챔버의 다른 컴포넌트들을 사용하여 구현될 수도 있다. 예를 들어, 이로 제한되지 않지만, 플라즈마 한정 슈라우드들/링들, 샤워헤드의 컴포넌트들 또는 상부 전극, 등을 포함한 컴포넌트들은 CVD 다이아몬드 코팅으로 코팅될 수도 있다.

이제 도 3을 참조하면, 기판 프로세싱 시스템은 페데스탈 (20) 및 에지 링 (80) 을 포함할 수도 있다. 에지 링 (80) 은 단일의 피스 또는 2 개 이상의 부분들을 포함할 수도 있다. 도 3의 예에서, 에지 링 (80) 은 기판 (33) 의 방사상으로 외측 에지 근방에 (또는 페데스탈 (20) 의 기판 지지 표면 근방에) 배치되는 제 1 환형 부분 (82) 을 포함한다. 제 2 환형 부분 (84) 은 기판 (33) 아래에서 제 1 환형 부분으로부터 방사상으로 내측에 위치된다. 제 3 환형 부분 (86) 은 제 1 환형 부분 (82) 아래에 배치된다.

에지 링 (80) 의 제 1 환형 부분 (82) 의 단면의 형상이 직사각형으로 도시되지만, 다른 형상들을 가진 단면들이 사용될 수도 있다. 일부 예들에서, 에지 링은 실리콘 (Si), 실리콘 카바이드 (SiC) 및 실리콘 다이옥사이드 (SiO2) 로 구성된 그룹으로부터 선택된 재료로 이루어진다. 구체적인 에지 링 재료들이 본 명세서에 개시되지만, 다른 재료들이 사용될 수 있다.

에지 링 (80) 의 제 1 환형 부분 (82) 은 다이아몬드 코팅 (90) 을 포함한다. 일부 예들에서, 다이아몬드 코팅은 CVD (chemical vapor deposition) 를 사용하여 증착된다. 일부 예들에서, 다이아몬드 코팅은 1 ㎛ 내지 1 ㎜의 두께를 갖는다. 다른 예들에서, 다이아몬드 코팅은 100 ㎛ 내지 1 ㎜의 두께를 갖는다. 다른 예들에서, 다이아몬드 코팅은 250 ㎛ 내지 1 ㎜의 두께를 갖는다. 일부 예들에서, sp3 결합들의 순도는 90 % 초과이다. 다른 예들에서, sp3 결합들의 순도는 95 % 초과이다. 다른 예들에서, sp3 결합들의 순도는 99 % 초과이다. 다른 예들에서, sp3 결합들의 순도는 99.5 % 초과이다 (예를 들어 > 99.85 %).

다이아몬드 코팅 (90) 이 제 1 환형 부분 (82) 의 플라즈마-대면 표면들 상에 도시되지만, 다이아몬드 코팅 (90) 은 또한 플라즈마-대면 표면들 또는 제 1, 제 2 및 제 3 환형 부분들 (82, 84 및 86) 의 전체 외측 표면 상에 증착될 수도 있다.

사용 동안, 플라즈마 (42) 는 기판 (33) 의 노출된 부분들을 에칭하도록 기판 (33) 으로 지향된다. 에지 링 (80) 은 기판 (33) 의 균일한 에칭이 발생하게 플라즈마의 성형을 돕도록 배치된다.

에지 링 (80) 에 도포되는 것으로서 본 명세서에 기술될지라도, 본 개시의 코팅은 기판 프로세싱 시스템의 다른 컴포넌트들 (예를 들어, 플라즈마 에칭 프로세스 및/또는 증착 프로세스가 수행되는 기판 프로세싱 챔버의 컴포넌트들) 에 도포될 수도 있다. 단지 예를 들면, 본 개시의 코팅은 이로 제한되지 않지만, 에지 링들, 윈도우들 (예를 들어, RF 윈도우들, 유전체 윈도우들, 등), 주입기들, 라이너들, 챔버 벽들, 및 페데스탈/페데스탈 (예를 들어, 척, 예컨대, 정전 척) 의 다양한 컴포넌트들을 포함한 컴포넌트들에 도포될 수도 있다.

이제 도 4를 참조하면, RF 플라즈마를 사용하여 에칭을 수행하기 위한 기판 프로세싱 시스템 (100) 의 예가 도시된다. 상기에 기술된 바와 같이 다이아몬드 코팅 (도 4에서 "d"로 식별됨) 으로 코팅될 수도 있는 기판 프로세싱 시스템 (100) 내의 다양한 컴포넌트들의 예들이 도시된다. 기판 프로세싱 시스템 (100) 은 기판 프로세싱 시스템 (100) 의 다른 컴포넌트들을 둘러싸고 그리고 RF 플라즈마를 담는 프로세싱 챔버 (102) 를 포함한다. 일부 예들에서, 프로세싱 챔버 (102) 의 내벽 표면들은 다이아몬드 코팅 (d) 으로 코팅된다. 기판 프로세싱 시스템 (100) 은 상부 전극 (104) 및 하부 전극 (107) 을 포함한 페데스탈 (106) 을 포함한다. 일부 예들에서, 상부 전극은 다이아몬드 코팅 (d) 으로 코팅된다. 일부 예들에서, 페데스탈 (106) 의 하나 이상의 표면들은 다이아몬드 코팅 (d) 으로 코팅된다. 에지 링 (103) 은 페데스탈 (106) 에 의해 지지되고 그리고 기판 (108) 주위에 배치된다. 일부 예들에서, 에지 링 (103) 은 다이아몬드 코팅 (d) 으로 코팅된다. 동작 동안, 기판 (108) 은 상부 전극 (104) 과 하부 전극 (107) 사이에서 페데스탈 (106) 상에 배치된다.

단지 예를 들면, 상부 전극 (104) 은 프로세스 가스들을 도입하고 분배하는 샤워헤드 (109) 를 포함할 수도 있다. 샤워헤드 (109) 는 프로세싱 챔버의 상단 표면에 연결된 일 단부를 포함한 스템 부분을 포함할 수도 있다. 베이스 부분은 일반적으로 실린더형이고 그리고 프로세싱 챔버의 상단 표면으로부터 이격되는 위치에서 스템 부분의 반대편의 단부로부터 방사상으로 외측으로 연장한다. 샤워헤드의 베이스 부분의 기판-대면 표면 또는 대면 플레이트는 프로세스 가스 또는 퍼지 가스가 흐르는 복수의 홀들을 포함한다. 대안적으로, 상부 전극 (104) 은 도전성 플레이트를 포함할 수도 있고 그리고 프로세스 가스들은 또 다른 방식으로 도입될 수도 있다. 하부 전극 (107) 은 비전도성 페데스탈 내에 배치될 수도 있다. 대안적으로, 페데스탈 (106) 은 하부 전극 (107) 으로서 작용하는 전도성 플레이트를 포함하는 정전 척을 포함할 수도 있다.

RF 생성 시스템 (110) 은 RF 전압을 생성하고 그리고 RF 전압을 상부 전극 (104) 및 하부 전극 (107) 중 하나에 출력한다. 상부 전극 (104) 및 하부 전극 (107) 중 다른 하나는 DC 접지되거나, AC 접지되거나 플로팅할 (floating) 수도 있다. 단지 예를 들면, RF 생성 시스템 (110) 은 매칭 및 분배 네트워크 (112) 에 의해 상부 전극 (104) 또는 하부 전극 (107) 에 피딩된 (feed) RF 전압을 생성하는 RF 전압 생성기 (111) 를 포함할 수도 있다. 다른 예들에서, 플라즈마는 유도적으로 또는 리모트로 생성될 수도 있다.

가스 전달 시스템 (130) 은 하나 이상의 가스 소스들 (132-1, 132-2, ..., 및 132-N) (집합적으로 가스 소스들 (132)) 을 포함하고, 여기서 N은 0보다 큰 정수이다. 가스 소스들은 하나 이상의 전구체들 및 전구체들의 혼합물들을 공급한다. 가스 소스들은 또한 퍼지 가스를 공급할 수도 있다. 기화된 전구체가 또한 사용될 수도 있다. 가스 소스들 (132) 은 밸브들 (134-1, 134-2, ..., 및 134-N) (집합적으로 밸브들 (134)) 및 질량 유량 제어기들 (136-1, 136-2, ..., 및 136-N) (집합적으로 질량 유량 제어기들 (136)) 에 의해 매니폴드 (140) 에 연결된다. 매니폴드 (140) 의 출력은 프로세싱 챔버 (102) 에 피딩된다. 단지 예를 들면, 매니폴드 (140) 의 출력은 샤워헤드 (109) 에 피딩된다.

가열기 (142) 는 페데스탈 (106) 내에 배치된 가열기 코일 (미도시) 에 연결될 수도 있다. 가열기 (142) 는 페데스탈 (106) 및 기판 (108) 의 온도를 제어하도록 사용될 수도 있다. 밸브 (150) 및 펌프 (152) 는 프로세싱 챔버 (102) 로부터 반응물질들을 배출하도록 사용될 수도 있다. 제어기 (160) 는 기판 프로세싱 시스템 (100) 의 컴포넌트들을 제어하도록 사용될 수도 있다.

이제 도 5를 참조하면, 본 개시에 따른, 기판 프로세싱 시스템 (210) 의 예가 도시된다. 기판 프로세싱 시스템 (210) 내의 다양한 컴포넌트들은 상기에 기술된 바와 같이 다이아몬드 코팅 (d) 으로 코팅될 수도 있다. 기판 프로세싱 시스템 (210) 은 TCP 코일들 (216) 에 연결되는 TCCT (transformer-coupled capacitive tuning) 회로 (214) 에 연결된 RF 소스 (212) 를 포함한다. TCCT 회로 (214) 는 통상적으로 하나 이상의 고정 또는 가변 커패시터들 (215) 을 포함한다. TCCT 회로 (214) 의 예는 전체가 참조로서 본 명세서에 인용되는, Long 등에 공동으로 양도된 미국 공보 제 2013/0135058 호에 도시되고 기술된다. TCP 코일들 (216) 은 코일들의 쌍 또는 내측 코일 쌍 및 외측 코일 쌍을 포함할 수도 있다.

TCP 코일들 (216) 은 유전체 윈도우 (224) 에 인접하게 배치된다. 일부 예들에서, 유전체 윈도우 (224) 의 하나 이상의 표면들은 다이아몬드 코팅으로 코팅된다. 유전체 윈도우 (224) 는 프로세싱 챔버 (228) 의 일 측면을 따라 배치된다. 일부 예들에서, 프로세싱 챔버 (228) 의 내벽 표면들은 다이아몬드 코팅 (d) 으로 코팅된다. 프로세싱 챔버 (228) 는 기판 (234) 을 지지하는 페데스탈 (232) 을 더 포함한다. 일부 예들에서, 페데스탈 (232) 의 하나 이상의 표면들은 다이아몬드 코팅 (d) 으로 코팅된다. 일부 예들에서, 페데스탈 (232) 은 상기에 기술된 바와 같이 다이아몬드 코팅으로 코팅되는 에지 링 (미도시) 을 포함한다. 페데스탈 (232) 은 정전 척, 기계 척 또는 다른 타입의 척을 포함할 수도 있다. 플라즈마 (240) 는 프로세싱 챔버 (228) 의 내부에 생성된다. 플라즈마 (240) 는 기판 (234) 의 노출된 표면을 에칭한다. RF 소스 (250) 및 바이어스 매칭 회로 (252) 는 동작 동안 페데스탈 (232) 을 바이어싱하도록 사용될 수도 있다.

가스 전달 시스템 (256) 은 프로세싱 챔버 (228) 로 가스 혼합물을 공급하도록 사용될 수도 있다. 가스 전달 시스템 (256) 은 프로세스 가스 소스들 (257), 계량 시스템 (258), 예컨대, 밸브들 및 질량 유량 제어기들, 및 매니폴드 (259) 를 포함할 수도 있다. 가열기 (264) 는 페데스탈 (232) 을 미리 결정된 온도로 가열하도록 사용될 수도 있다. 배기 시스템 (265) 은 퍼지 또는 배기에 의해 프로세싱 챔버 (228) 로부터 반응물질들을 제거하도록 밸브 (266) 및 펌프 (267) 를 포함한다.

제어기 (254) 는 에칭 프로세스를 제어하도록 사용될 수도 있다. 제어기 (254) 는 시스템 파라미터들을 모니터링하고 그리고 가스 혼합물의 전달, 플라즈마의 스트라이킹, 유지 및 소화, 반응물질들의 제거, 냉각 가스의 공급, 등을 제어한다.

이제 도 6을 참조하면, 본 개시에 따른, 기판을 에칭하거나 애싱하기 위한 기판 프로세싱 챔버 (300) 가 도시된다. 기판 프로세싱 시스템 (300) 내의 다양한 컴포넌트들은 상기에 기술된 바와 같이 다이아몬드 코팅 (d) 으로 코팅될 수도 있다. 특정한 타입의 기판 프로세싱 챔버가 도시되고 기술되지만, 본 명세서에 기술된 개선들은 다양한 다른 기판 프로세싱 챔버들에 적용될 수도 있다.

기판 프로세싱 챔버 (300) 는 하부 챔버 구역 (302) 및 상부 챔버 구역 (304) 을 포함한다. 하부 챔버 구역 (302) 은 챔버 측벽 표면들 (308), 챔버 하단 표면 (310) 및 가스 분배 디바이스 (314) 의 하부 표면에 의해 규정된다. 일부 예들에서, 가스 분배 디바이스 (314) 의 하나 이상의 표면들은 다이아몬드 코팅으로 코팅된다.

상부 챔버 구역 (304) 은 가스 분배 디바이스 (314) 의 상부 표면 및 상부 챔버 구역 (304) 의 내측 표면 (318) 에 의해 규정된다. 일부 예들에서, 상부 챔버 및 하부 챔버의 내벽 표면들은 다이아몬드 코팅 (d) 으로 코팅된다. 일부 예들에서, 상부 챔버 구역 (304) 은 돔 형상을 가질 수도 있지만, 다른 형상들이 사용될 수 있다. 일부 예들에서, 상부 챔버 구역 (304) 은 제 1 지지부 (321) 상에 놓인다. 일부 예들에서, 제 1 지지부 (321) 는 환형 형상을 갖는다. 일부 예들에서, 제 1 지지부 (321) 는 이하에 더 기술될 바와 같이, 프로세스 가스를 상부 챔버 구역 (304) 으로 전달하기 위한 하나 이상의 가스 플로우 채널들 (323) 을 포함한다. 일부 예들에서, 프로세스 가스는 가스 분배 디바이스 (314) 를 포함한 평면에 대해 예각으로 상측 방향으로 하나 이상의 가스 플로우 채널들 (323) 에 의해 전달되지만, 다른 각도들/방향들이 사용될 수도 있다. 일부 예들에서, 가스 플로우 채널들 (323) 은 제 1 지지부 (321) 주위에 균일하게 이격된다.

제 1 지지부 (321) 는 제 2 지지부 (325) 상에 놓일 수도 있다. 일부 예들에서, 제 1 지지부 및 제 2 지지부는 다이아몬드 코팅으로 코팅된다. 일부 예들에서, 제 2 지지부는 환형 형상을 갖는다. 제 2 지지부 (325) 는 프로세스 가스를 하부 챔버 구역 (302) 으로 전달하기 위한 하나 이상의 가스 플로우 채널들 (327) 을 규정한다. 일부 예들에서, 가스 플로우 채널들은 제 2 지지부 (325) 주위에 균일하게 이격된다. 일부 예들에서, 가스 분배 디바이스 (314) 내의 가스 쓰루홀들 (331) 은 가스 플로우 채널들 (327) 과 정렬된다. 다른 예들에서, 가스 분배 디바이스 (314) 는 보다 작은 직경을 갖고 그리고 가스 쓰루홀들 (331) 이 필요하지 않다. 일부 예들에서, 프로세스 가스는 가스 분배 디바이스 (314) 를 포함한 평면에 대해 예각으로 기판을 향하여 하측 방향으로 하나 이상의 가스 플로우 채널들 (327) 에 의해 전달되지만, 다른 각도들/방향들이 사용될 수도 있다.

다른 예들에서, 편평한 상단 표면을 가진 상부 챔버 구역 (304) 은 실린더형이고 그리고 편평한 유도 코일이 사용될 수도 있다. 여전히 다른 예들에서, 샤워헤드와 페데스탈 사이에 위치된 스페이서를 가진 단일의 챔버가 사용될 수도 있다.

페데스탈 (322) 은 하부 챔버 구역 (302) 내에 배치된다. 일부 예들에서, 페데스탈 (322) 은 정전 척 (ESC) 을 포함하지만, 다른 타입들의 페데스탈들이 사용될 수 있다. 기판 (326) 은 에칭 동안 페데스탈 (322) 의 상부 표면 상에 배치된다. 일부 예들에서, 페데스탈의 하나 이상의 표면들은 다이아몬드 코팅으로 코팅된다. 일부 예들에서, 기판 (326) 의 온도는 가열기 플레이트, 유체 채널들을 가진 선택 가능한 냉각 플레이트 및 하나 이상의 센서들 (모두 미도시) 에 의해 제어될 수도 있지만; 임의의 다른 적합한 페데스탈 온도 제어 시스템이 사용될 수도 있다.

일부 예들에서, 가스 분배 디바이스 (314) 는 샤워헤드 (예를 들어, 복수의 쓰루홀들 (329) 을 가진 플레이트 (328)) 를 포함한다. 복수의 쓰루홀들 (329) 은 플레이트 (328) 의 상부 표면으로부터 플레이트 (328) 의 하부 표면으로 연장한다. 일부 예들에서, 쓰루홀들 (329) 은 0.4" 내지 0.75" 범위의 직경을 갖고 그리고 샤워헤드는 전도성 재료로 이루어진 임베딩된 (embedded) 전극을 가지며 세라믹과 같은 비-전도성 재료 또는 알루미늄과 같은 전도성 재료로 이루어진다.

하나 이상의 유도 코일들 (340) 은 상부 챔버 구역 (304) 의 외측 부분 주위에 배치된다. 에너자이징될 (energized) 때, 하나 이상의 유도 코일들 (340) 은 상부 챔버 구역 (304) 의 내부에 전자기장을 생성한다. 가스 주입기 (342) 는 하나 이상의 가스 혼합물들을 가스 전달 시스템 (350) 으로부터 주입한다. 일부 예들에서, 가스 주입기 (342) 는 가스를 하측 방향으로 지향시키는 중심 주입 위치 및 가스를 하측 방향에 대해 비스듬히 주입하는 하나 이상의 측면 주입 위치들을 포함한다. 일부 예들에서, 가스 주입기 (342) 의 노출된 표면은 다이아몬드 코팅으로 코팅된다. 일부 예들에서, 가스 전달 시스템 (350) 은 제 1 플로우 레이트로 가스 혼합물의 제 1 부분을 중심 주입 위치로 전달하고 그리고 제 2 플로우 레이트로 가스 혼합물의 제 2 부분을 가스 주입기 (342) 의 측면 주입 위치(들)로 전달한다. 다른 예들에서, 상이한 가스 혼합물들이 가스 주입기 (342) 에 의해 전달된다. 일부 예들에서, 가스 전달 시스템 (350) 은 이하에 기술될 바와 같이, 튜닝 가스를 가스 플로우 채널들 (323 및 327) 로 그리고/또는 프로세싱 챔버 내의 다른 위치들로 전달한다. 일부 예들에서, 튜닝 가스는 이온화된 종의 볼륨의 위치를 가변함으로써 에칭 또는 애시 레이트들 및/또는 선택도를 조정하도록 가변된다.

플라즈마 생성기 (370) 는 하나 이상의 유도 코일들 (340) 로 출력되는 RF 전력을 생성하도록 사용될 수도 있다. 플라즈마는 상부 챔버 구역 (304) 내에서 생성된다. 일부 예들에서, 플라즈마 생성기 (370) 는 RF 생성기 (372) 및 매칭 네트워크 (374) 를 포함한다. 매칭 네트워크 (374) 는 하나 이상의 유도 코일들 (340) 의 임피던스에 RF 생성기 (372) 의 임피던스를 매칭한다. 일부 예들에서, 가스 분배 디바이스 (314) 는 접지와 같은 기준 전위에 연결된다. 밸브 (378) 및 펌프 (380) 는 하부 및 상부 챔버 구역들 (302, 304) 의 내부의 압력을 제어하도록 그리고 하부 및 상부 챔버 구역들 (302, 304) 각각으로부터 반응물질들을 배기하도록 사용될 수도 있다.

제어기 (376) 는 프로세스 가스, 퍼지 가스, RF 플라즈마 및 챔버 압력의 플로우를 제어하도록 가스 전달 시스템 (350), 밸브 (378), 펌프 (380), 및/또는 플라즈마 생성기 (370) 와 통신한다. 일부 예들에서, 플라즈마는 하나 이상의 유도 코일들 (340) 에 의해 상부 챔버 구역 (304) 내부에서 유지된다. 하나 이상의 가스 혼합물들은 가스 주입기 (342) 를 사용하여 챔버의 상단 부분으로부터 도입되고 그리고 플라즈마는 접지될 수도 있는 가스 분배 디바이스 (314) 를 사용하여 상부 챔버 구역 (304) 내에 한정된다.

상부 챔버 구역 (304) 내에 플라즈마를 한정시키는 것은 플라즈마 종의 볼륨 재결합 및 가스 분배 디바이스 (314) 를 통한 목표된 에천트 종의 유출을 허용한다. 일부 예들에서, 기판 (326) 에 인가된 RF 바이어스는 없다. 그 결과, 기판 (326) 상에 활성 시스가 없고 그리고 임의의 유한한 에너지를 가진 이온들이 기판과 부딪치지 않는다. 일부 양의 이온들은 플라즈마 구역으로부터 가스 분배 디바이스 (314) 를 통해 확산할 것이다. 그러나, 확산하는 플라즈마의 양은 상부 챔버 구역 (304) 내부에 위치된 플라즈마보다 한 자릿수 적다. 플라즈마 내의 대부분의 이온들은 고압들에서의 볼륨 재결합에 의해 손실된다. 가스 분배 디바이스 (314) 의 상부 표면에서의 표면 재결합 손실은 또한 가스 분배 디바이스 (314) 아래의 이온 밀도를 낮춘다.

다른 예들에서, RF 바이어스 생성기 (384) 가 제공되고 그리고 RF 생성기 (386) 및 매칭 네트워크 (388) 를 포함한다. RF 바이어스는 가스 분배 디바이스 (314) 와 페데스탈 사이에서 플라즈마를 생성하도록 또는 이온들을 끌어당기기 위해 기판 (326) 상에 자기 바이어스 (self-bias) 를 생성하도록 사용될 수 있다. 제어기 (376) 는 RF 바이어스를 제어하도록 사용될 수도 있다.

전술한 기술은 단순히 특성을 예시하는 것이고 어떠한 방식으로도 본 개시, 이의 애플리케이션, 또는 용도를 제한하도록 의도되지 않는다. 본 개시의 광범위한 교시들은 다양한 형태들로 구현될 수 있다. 따라서, 본 개시는 특정한 예들을 포함하지만, 본 개시의 진정한 범위는 다른 수정들이 도면들, 명세서, 및 이하의 청구항들을 연구함으로써 명백해질 것이기 때문에 그렇게 제한되지 않아야 한다. 방법 내에서 하나 이상의 단계들은 본 개시의 원리들을 변경하지 않고 상이한 순서로 (또는 동시에) 실행될 수도 있다는 것이 이해되어야 한다. 또한, 실시예들 각각이 특정한 피처들을 갖는 것으로 상기에 기술되지만, 본 개시의 임의의 실시예에 대해 기술된 임의의 하나 이상의 이들 피처들은, 조합이 명시적으로 기술되지 않아도, 임의의 다른 실시예들의 피처들로 및/또는 임의의 다른 실시예들의 피처들과 조합하여 구현될 수 있다. 즉, 기술된 실시예들은 상호 배타적이지 않고, 하나 이상의 실시예들의 또 다른 실시예와의 치환들이 본 개시의 범위 내에 남는다.

엘리먼트들 간 (예를 들어, 모듈들, 회로 엘리먼트들, 반도체 층들, 등 간) 의 공간적 및 기능적 관계들은, "연결된 (connected)", "인게이지된 (engaged)", "커플링된 (coupled)", "인접한 (adjacent)", "옆에 (next to)", "~의 상단에 (on top of)", "위에 (above)", "아래에 (below)", 및 "배치된 (disposed)"을 포함하는, 다양한 용어들을 사용하여 기술된다. "직접적 (direct)"인 것으로 명시적으로 기술되지 않는 한, 제 1 엘리먼트와 제 2 엘리먼트 간의 관계가 상기 개시에서 기술될 때, 이 관계는 제 1 엘리먼트와 제 2 엘리먼트 사이에 다른 중개하는 엘리먼트가 존재하지 않는 직접적인 관계일 수 있지만, 또한 제 1 엘리먼트와 제 2 엘리먼트 사이에 (공간적으로 또는 기능적으로) 하나 이상의 중개하는 엘리먼트들이 존재하는 간접적인 관계일 수 있다. 본 명세서에서 사용된 바와 같이, 구 A, B, 및 C 중 적어도 하나는 비배타적인 논리 OR를 사용하여, 논리적으로 (A 또는 B 또는 C) 를 의미하는 것으로 해석되어야 하고, "적어도 하나의 A, 적어도 하나의 B, 및 적어도 하나의 C"를 의미하도록 해석되지 않아야 한다.

일부 구현예들에서, 제어기는 상술한 실례들의 일부일 수 있는 시스템의 일부이다. 이러한 시스템들은, 프로세싱 툴 또는 툴들, 챔버 또는 챔버들, 프로세싱용 플랫폼 또는 플랫폼들, 및/또는 특정 프로세싱 컴포넌트들 (웨이퍼 페데스탈, 가스 플로우 시스템, 등) 을 포함하는, 반도체 프로세싱 장비를 포함할 수 있다. 이러한 시스템들은 반도체 웨이퍼 또는 기판의 프로세싱 이전에, 프로세싱 동안에 그리고 프로세싱 이후에 그들의 동작을 제어하기 위한 전자장치에 통합될 수도 있다. 전자장치는 시스템 또는 시스템들의 다양한 컴포넌트들 또는 하위부품들을 제어할 수도 있는 "제어기"로서 지칭될 수도 있다. 제어기는, 시스템의 프로세싱 요건들 및/또는 타입에 따라서, 예를 들어 프로세싱 가스들의 전달, 온도 설정사항들 (예를 들어, 가열 및/또는 냉각), 압력 설정사항들, 진공 설정사항들, 전력 설정사항들, 무선 주파수 (RF) 생성기 설정사항들, RF 매칭 회로 설정사항들, 주파수 설정사항들, 플로우 레이트 설정사항들, 유체 전달 설정사항들, 위치 및 동작 설정사항들, 툴들 및 다른 전달 툴들 및/또는 특정 시스템과 연결되거나 인터페이싱된 로드록들 내외로의 웨이퍼 전달들을 포함하는, 본 명세서에 개시된 프로세스들 중 임의의 프로세스를 제어하도록 프로그램될 수도 있다.

일반적으로 말하면, 제어기는 인스트럭션들을 수신하고 인스트럭션들을 발행하고 동작을 제어하고 세정 동작들을 인에이블하고, 엔드포인트 측정들을 인에이블하는 등을 하는 다양한 집적 회로들, 로직, 메모리, 및/또는 소프트웨어를 갖는 전자장치로서 규정될 수도 있다. 집적 회로들은 프로그램 인스트럭션들을 저장하는 펌웨어의 형태의 칩들, 디지털 신호 프로세서들 (DSP), ASIC (application specific integrated circuit) 으로서 규정되는 칩들 및/또는 프로그램 인스트럭션들 (예를 들어, 소프트웨어) 을 실행하는 하나 이상의 마이크로프로세서들, 또는 마이크로제어기들을 포함할 수도 있다. 프로그램 인스트럭션들은 반도체 웨이퍼 상에서 또는 반도체 웨이퍼에 대한 특정 프로세스를 실행하기 위한 동작 파라미터들을 규정하는, 다양한 개별 설정사항들 (또는 프로그램 파일들) 의 형태로 제어기로 또는 시스템으로 전달되는 인스트럭션들일 수도 있다. 일부 실시예들에서, 동작 파라미터들은 하나 이상의 층들, 재료들, 금속들, 산화물들, 실리콘, 이산화 실리콘, 표면들, 회로들, 및/또는 웨이퍼의 다이들의 제조 동안에 하나 이상의 프로세싱 단계들을 달성하도록 프로세스 엔지니어에 의해서 규정된 레시피의 일부일 수도 있다.

제어기는, 일부 구현예들에서, 시스템에 통합되거나, 시스템에 커플링되거나, 이와 달리 시스템에 네트워킹되거나, 또는 이들의 조합으로 되는 컴퓨터에 커플링되거나 이의 일부일 수도 있다. 예를 들어, 제어기는 웨이퍼 프로세싱의 원격 액세스를 가능하게 할 수 있는 공장 (fab) 호스트 컴퓨터 시스템의 전부 또는 일부이거나 "클라우드" 내에 있을 수도 있다. 컴퓨터는 제조 동작들의 현 진행을 모니터링하고, 과거 제조 동작들의 이력을 조사하고, 복수의 제조 동작들로부터 경향들 또는 성능 계측치들을 조사하고, 현 프로세싱의 파라미터들을 변경하고, 현 프로세싱을 따르는 프로세싱 단계들을 설정하고, 또는 새로운 프로세스를 시작하기 위해서 시스템으로의 원격 액세스를 인에이블할 수도 있다. 일부 예들에서, 원격 컴퓨터 (예를 들어, 서버) 는 로컬 네트워크 또는 인터넷을 포함할 수도 있는 네트워크를 통해서 프로세스 레시피들을 시스템에 제공할 수 있다. 원격 컴퓨터는 차후에 원격 컴퓨터로부터 시스템으로 전달될 파라미터들 및/또는 설정사항들의 입력 또는 프로그래밍을 가능하게 하는 사용자 인터페이스를 포함할 수도 있다. 일부 예들에서, 제어기는 하나 이상의 동작들 동안에 수행될 프로세스 단계들 각각에 대한 파라미터들을 특정한, 데이터의 형태의 인스트럭션들을 수신한다. 이 파라미터들은 제어기가 제어하거나 인터페이싱하도록 구성된 툴의 타입 및 수행될 프로세스의 타입에 특정적일 수 있다는 것이 이해되어야 한다. 따라서, 상술한 바와 같이, 제어기는 예를 들어 서로 네트워킹되어서 함께 공통 목적을 위해서, 예를 들어 본 명세서에 기술된 프로세스들 및 제어들을 위해서 협력하는 하나 이상의 개별 제어기들을 포함함으로써 분산될 수도 있다. 이러한 목적을 위한 분산형 제어기의 예는 챔버 상의 프로세스를 제어하도록 조합되는, (예를 들어, 플랫폼 레벨에서 또는 원격 컴퓨터의 일부로서) 원격으로 위치한 하나 이상의 집적 회로들과 통신하는 챔버 상의 하나 이상의 집적 회로들일 수 있다.

비한정적으로, 예시적인 시스템들은 플라즈마 에칭 챔버 또는 모듈, 증착 챔버 또는 모듈, 스핀-린스 챔버 또는 모듈, 금속 도금 챔버 또는 모듈, 세정 챔버 또는 모듈, 베벨 에지 에칭 챔버 또는 모듈, PVD (physical vapor deposition) 챔버 또는 모듈, CVD (chemical vapor deposition) 챔버 또는 모듈, ALD (atomic layer deposition) 챔버 또는 모듈, ALE (atomic layer etch) 챔버 또는 모듈, 이온 주입 챔버 또는 모듈, 트랙 (track) 챔버 또는 모듈, 및 반도체 웨이퍼들의 제조 및/또는 제작 시에 사용되거나 연관될 수도 있는 임의의 다른 반도체 프로세싱 시스템들을 포함할 수도 있다.

상술한 바와 같이, 툴에 의해서 수행될 프로세스 단계 또는 단계들에 따라서, 제어기는, 반도체 제조 공장 내의 툴 위치들 및/또는 로드 포트들로부터/로 웨이퍼들의 컨테이너들을 이동시키는 재료 이송 시에 사용되는, 다른 툴 회로들 또는 모듈들, 다른 툴 컴포넌트들, 클러스터 툴들, 다른 툴 인터페이스들, 인접 툴들, 이웃하는 툴들, 공장 도처에 위치한 툴들, 메인 컴퓨터, 다른 제어기 또는 툴들 중 하나 이상과 통신할 수도 있다.

Claims (20)

- 플라즈마 프로세싱 시스템을 위한 페데스탈에 있어서,

기판 지지 표면;

상기 기판 지지 표면의 주변 주위에 배치된 환형 에지 링; 및

상기 환형 링의 플라즈마-노출된 표면 상에 배치된 다이아몬드 코팅을 포함하고,

상기 다이아몬드 코팅은 sp3 결합들을 포함하고, 그리고

상기 다이아몬드 코팅 내의 상기 sp3 결합들의 순도는 90 % 초과인, 플라즈마 프로세싱 시스템을 위한 페데스탈. - 제 1 항에 있어서,

상기 다이아몬드 코팅 내의 상기 sp3 결합들의 상기 순도는 95 % 초과인, 플라즈마 프로세싱 시스템을 위한 페데스탈. - 제 1 항에 있어서,

상기 다이아몬드 코팅 내의 상기 sp3 결합들의 상기 순도는 99 % 초과인, 플라즈마 프로세싱 시스템을 위한 페데스탈. - 제 1 항에 있어서,

상기 다이아몬드 코팅은 CVD (chemical vapor deposition) 를 사용하여 상기 환형 에지 링 상에 증착되는, 플라즈마 프로세싱 시스템을 위한 페데스탈. - 프로세싱 챔버로서, 제 1 항에 기재된 페데스탈이 상기 프로세싱 챔버 내에 배치되는, 상기 프로세싱 챔버; 및

상기 프로세싱 챔버 내에서 플라즈마를 생성하기 위한 플라즈마 소스를 포함하는, 플라즈마 프로세싱 시스템. - 제 5 항에 있어서,

상기 플라즈마 소스는 CCP (capacitively-coupled plasma) 소스를 포함하는, 플라즈마 프로세싱 시스템. - 제 5 항에 있어서,

상기 플라즈마 소스는 ICP (inductively-coupled plasma) 소스를 포함하는, 플라즈마 프로세싱 시스템. - 프로세싱 챔버로서, 제 1 항에 기재된 페데스탈이 상기 프로세싱 챔버 내에 배치되는, 상기 프로세싱 챔버; 및

상기 프로세싱 챔버로 플라즈마를 공급하기 위한 리모트 플라즈마 소스를 포함하는, 플라즈마 프로세싱 시스템. - 프로세싱 챔버;

상기 프로세싱 챔버로 플라즈마를 공급하거나 상기 프로세싱 챔버 내에서 플라즈마를 생성하는 것 중 하나를 하기 위한 플라즈마 소스; 및

다이아몬드 코팅을 포함하는, 상기 프로세싱 챔버 내에 배치된 적어도 하나의 컴포넌트 (component) 를 포함하고,

상기 다이아몬드 코팅은 sp3 결합들을 포함하고, 그리고

상기 다이아몬드 코팅 내의 상기 sp3 결합들의 순도는 90 % 초과인, 플라즈마 프로세싱 시스템. - 제 9 항에 있어서,

상기 다이아몬드 코팅 내의 상기 sp3 결합들의 상기 순도는 95 % 초과인, 플라즈마 프로세싱 시스템. - 제 9 항에 있어서,

상기 다이아몬드 코팅 내의 상기 sp3 결합들의 상기 순도는 99 % 초과인, 플라즈마 프로세싱 시스템. - 제 9 항에 있어서,

상기 다이아몬드 코팅은 CVD (chemical vapor deposition) 를 사용하여 상기 적어도 하나의 컴포넌트 상에 증착되는, 플라즈마 프로세싱 시스템. - 제 9 항에 있어서,

상기 적어도 하나의 컴포넌트는,

에지 링;

챔버 벽;

가스 분배 디바이스;

가스 주입기;

상기 프로세싱 챔버 내로의 윈도우; 및

페데스탈의 상부 표면으로 구성된 그룹으로부터 선택되는, 플라즈마 프로세싱 시스템. - 플라즈마 프로세싱 시스템을 위한 에지 링에 있어서,

환형 링; 및

사용 동안 플라즈마에 노출되는 상기 환형 링의 표면 상에 배치된 다이아몬드 코팅을 포함하고,

상기 다이아몬드 코팅은 sp3 결합들을 포함하고, 그리고

상기 다이아몬드 코팅 내의 상기 sp3 결합들의 순도는 90 % 초과인, 플라즈마 프로세싱 시스템을 위한 에지 링. - 제 14 항에 있어서,

상기 다이아몬드 코팅 내의 상기 sp3 결합들의 상기 순도는 95 % 초과인, 플라즈마 프로세싱 시스템을 위한 에지 링. - 제 14 항에 있어서,

상기 다이아몬드 코팅 내의 상기 sp3 결합들의 상기 순도는 99 % 초과인, 플라즈마 프로세싱 시스템을 위한 에지 링. - 제 14 항에 있어서,

상기 다이아몬드 코팅은 CVD (chemical vapor deposition) 를 사용하여 상기 환형 링 상에 증착되는, 플라즈마 프로세싱 시스템을 위한 에지 링. - 제 14 항에 있어서,

상기 환형 링은 실리콘 (Si), 실리콘 카바이드 (SiC) 및 실리콘 다이옥사이드 (SiO2) 로 구성된 그룹으로부터 선택된 재료로 이루어지는, 플라즈마 프로세싱 시스템을 위한 에지 링. - 제 14 항에 있어서,

상기 다이아몬드 코팅은 1 ㎛ 내지 1 ㎜의 두께를 갖는, 플라즈마 프로세싱 시스템을 위한 에지 링. - 제 14 항에 있어서,

상기 다이아몬드 코팅은 100 ㎛ 내지 1 ㎜의 두께를 갖는, 플라즈마 프로세싱 시스템을 위한 에지 링.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020220029212A KR102556603B1 (ko) | 2016-03-03 | 2022-03-08 | 플라즈마 프로세싱 시스템들을 위한 고순도 sp3 결합들을 가진 화학적 기상 증착 (cvd) 다이아몬드 코팅을 포함한 에지 링들과 같은 컴포넌트들 |

Applications Claiming Priority (6)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201662303091P | 2016-03-03 | 2016-03-03 | |

| US62/303,091 | 2016-03-03 | ||

| US201662310993P | 2016-03-21 | 2016-03-21 | |

| US62/310,993 | 2016-03-21 | ||

| US15/428,744 | 2017-02-09 | ||

| US15/428,744 US11008655B2 (en) | 2016-03-03 | 2017-02-09 | Components such as edge rings including chemical vapor deposition (CVD) diamond coating with high purity SP3 bonds for plasma processing systems |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020220029212A Division KR102556603B1 (ko) | 2016-03-03 | 2022-03-08 | 플라즈마 프로세싱 시스템들을 위한 고순도 sp3 결합들을 가진 화학적 기상 증착 (cvd) 다이아몬드 코팅을 포함한 에지 링들과 같은 컴포넌트들 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20170103689A true KR20170103689A (ko) | 2017-09-13 |

Family

ID=59724242

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020170027531A KR20170103689A (ko) | 2016-03-03 | 2017-03-03 | 플라즈마 프로세싱 시스템들을 위한 고순도 sp3 결합들을 가진 화학적 기상 증착 (cvd) 다이아몬드 코팅을 포함한 에지 링들과 같은 컴포넌트들 |

| KR1020220029212A KR102556603B1 (ko) | 2016-03-03 | 2022-03-08 | 플라즈마 프로세싱 시스템들을 위한 고순도 sp3 결합들을 가진 화학적 기상 증착 (cvd) 다이아몬드 코팅을 포함한 에지 링들과 같은 컴포넌트들 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020220029212A KR102556603B1 (ko) | 2016-03-03 | 2022-03-08 | 플라즈마 프로세싱 시스템들을 위한 고순도 sp3 결합들을 가진 화학적 기상 증착 (cvd) 다이아몬드 코팅을 포함한 에지 링들과 같은 컴포넌트들 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US11008655B2 (ko) |

| JP (1) | JP2017166065A (ko) |

| KR (2) | KR20170103689A (ko) |

| CN (2) | CN107393797B (ko) |

| SG (2) | SG10202008553TA (ko) |

| TW (2) | TWI737686B (ko) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10784091B2 (en) | 2017-09-29 | 2020-09-22 | Taiwan Semiconductor Manufacturing Co., Ltd. | Process and related device for removing by-product on semiconductor processing chamber sidewalls |

| WO2019112903A1 (en) * | 2017-12-05 | 2019-06-13 | Lam Research Corporation | System and method for edge ring wear compensation |

| CN109994351B (zh) * | 2018-01-02 | 2021-07-13 | 台湾积体电路制造股份有限公司 | 离子布植机及离子布植机腔室的制造方法 |

| WO2019177837A1 (en) * | 2018-03-13 | 2019-09-19 | Applied Materials, Inc | Support ring with plasma spray coating |

| US11515128B2 (en) * | 2018-08-28 | 2022-11-29 | Lam Research Corporation | Confinement ring with extended life |

| KR102305539B1 (ko) * | 2019-04-16 | 2021-09-27 | 주식회사 티씨케이 | SiC 엣지 링 |

| JP7412923B2 (ja) * | 2019-08-23 | 2024-01-15 | 東京エレクトロン株式会社 | エッジリング、プラズマ処理装置及びエッジリングの製造方法 |

| CN112899662A (zh) * | 2019-12-04 | 2021-06-04 | 江苏菲沃泰纳米科技股份有限公司 | Dlc制备装置和制备方法 |

| CN112853482B (zh) * | 2020-12-31 | 2022-09-27 | 武汉大学深圳研究院 | 一种微波等离子体-磁控溅射复合气相沉积原位制备100面金刚石的方法及设备 |

| CN114318287B (zh) * | 2021-12-23 | 2023-11-03 | 深圳技术大学 | 金刚石自支撑膜的制备方法和金刚石自支撑膜 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5190823A (en) * | 1989-07-31 | 1993-03-02 | General Electric Company | Method for improving adhesion of synthetic diamond coatings to substrates |

| US5167714A (en) * | 1989-09-29 | 1992-12-01 | Nordson Corporation | Powder coating system with configurable controller and dew point detection |

| US5952060A (en) * | 1996-06-14 | 1999-09-14 | Applied Materials, Inc. | Use of carbon-based films in extending the lifetime of substrate processing system components |

| US6508911B1 (en) * | 1999-08-16 | 2003-01-21 | Applied Materials Inc. | Diamond coated parts in a plasma reactor |

| US6605352B1 (en) * | 2000-01-06 | 2003-08-12 | Saint-Gobain Ceramics & Plastics, Inc. | Corrosion and erosion resistant thin film diamond coating and applications therefor |

| US6537429B2 (en) * | 2000-12-29 | 2003-03-25 | Lam Research Corporation | Diamond coatings on reactor wall and method of manufacturing thereof |

| JP4028274B2 (ja) * | 2002-03-26 | 2007-12-26 | 住友大阪セメント株式会社 | 耐食性材料 |

| US7247348B2 (en) * | 2004-02-25 | 2007-07-24 | Honeywell International, Inc. | Method for manufacturing a erosion preventative diamond-like coating for a turbine engine compressor blade |

| KR100782663B1 (ko) * | 2004-02-26 | 2007-12-07 | 다이킨 고교 가부시키가이샤 | 불소 함유 엘라스토머 조성물 |

| US7658802B2 (en) * | 2005-11-22 | 2010-02-09 | Applied Materials, Inc. | Apparatus and a method for cleaning a dielectric film |

| WO2007103911A2 (en) * | 2006-03-06 | 2007-09-13 | Diamond Innovations, Inc. | Prosthesis for joint replacement |

| US20090029067A1 (en) * | 2007-06-28 | 2009-01-29 | Sciamanna Steven F | Method for producing amorphous carbon coatings on external surfaces using diamondoid precursors |

| US7629031B2 (en) * | 2007-07-13 | 2009-12-08 | Sub-One Technology, Inc. | Plasma enhanced bonding for improving adhesion and corrosion resistance of deposited films |

| JP2009123795A (ja) * | 2007-11-13 | 2009-06-04 | Hitachi Kokusai Electric Inc | 半導体装置の製造方法及び基板処理装置 |

| DE102010054875B4 (de) * | 2010-12-17 | 2012-10-31 | Eagleburgmann Germany Gmbh & Co. Kg | Reibungsarmer Gleitring mit kostengünstiger Diamantbeschichtung |

| US9059678B2 (en) | 2011-04-28 | 2015-06-16 | Lam Research Corporation | TCCT match circuit for plasma etch chambers |

| US10242848B2 (en) * | 2014-12-12 | 2019-03-26 | Lam Research Corporation | Carrier ring structure and chamber systems including the same |

-

2017

- 2017-02-09 US US15/428,744 patent/US11008655B2/en active Active

- 2017-03-02 TW TW106106790A patent/TWI737686B/zh active

- 2017-03-02 TW TW110128839A patent/TWI793701B/zh active

- 2017-03-02 JP JP2017039058A patent/JP2017166065A/ja active Pending

- 2017-03-03 SG SG10202008553TA patent/SG10202008553TA/en unknown

- 2017-03-03 CN CN201710122891.1A patent/CN107393797B/zh active Active

- 2017-03-03 KR KR1020170027531A patent/KR20170103689A/ko not_active IP Right Cessation

- 2017-03-03 CN CN202110539388.2A patent/CN113506719B/zh active Active

- 2017-03-03 SG SG10201701713TA patent/SG10201701713TA/en unknown

-

2022

- 2022-03-08 KR KR1020220029212A patent/KR102556603B1/ko active IP Right Grant

Also Published As

| Publication number | Publication date |

|---|---|

| KR20220036924A (ko) | 2022-03-23 |

| SG10202008553TA (en) | 2020-10-29 |

| CN107393797A (zh) | 2017-11-24 |

| TWI793701B (zh) | 2023-02-21 |

| CN107393797B (zh) | 2021-06-08 |

| CN113506719B (zh) | 2024-06-04 |

| TWI737686B (zh) | 2021-09-01 |

| CN113506719A (zh) | 2021-10-15 |

| SG10201701713TA (en) | 2017-10-30 |

| JP2017166065A (ja) | 2017-09-21 |

| KR102556603B1 (ko) | 2023-07-17 |

| TW201800596A (zh) | 2018-01-01 |

| US20170253974A1 (en) | 2017-09-07 |

| TW202217038A (zh) | 2022-05-01 |

| US11008655B2 (en) | 2021-05-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102556603B1 (ko) | 플라즈마 프로세싱 시스템들을 위한 고순도 sp3 결합들을 가진 화학적 기상 증착 (cvd) 다이아몬드 코팅을 포함한 에지 링들과 같은 컴포넌트들 | |

| JP7530874B2 (ja) | 可動エッジリング設計 | |

| TWI783960B (zh) | 具有改良的處理均勻性之基板支撐件 | |

| CN110383454B (zh) | 底部边缘环和中部边缘环 | |

| US20190244793A1 (en) | Tapered upper electrode for uniformity control in plasma processing | |

| KR20180006307A (ko) | 전기적 아크 및 발광을 방지하고 프로세스 균일도를 개선하기 위한 피처들을 갖는 정전 척 | |

| KR20180016300A (ko) | 부분적으로 그물 형상이고 부분적으로 거의 그물 형상인 실리콘 카바이드 cvd | |

| TWI827654B (zh) | 用於基板處理系統之侷限環與在基板處理系統中使用侷限環的方法 | |

| WO2020219408A1 (en) | High temperature heating of a substrate in a processing chamber | |

| CN114008738B (zh) | 用于衬底处理系统的缩小直径承载环硬件 | |

| JP2018014491A (ja) | 粒子性能および金属性能の改善のためのescセラミック側壁の加工 | |

| WO2021146099A1 (en) | Multizone gas distribution plate for trench profile optimization | |

| WO2020154244A1 (en) | Substrate processing system including dual ion filter for downstream plasma |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| AMND | Amendment | ||

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application | ||

| AMND | Amendment | ||

| X601 | Decision of rejection after re-examination |