KR20160125411A - 에러 검출 최적화를 용이하게 하는 공유된 버스를 통한 비트 할당 - Google Patents

에러 검출 최적화를 용이하게 하는 공유된 버스를 통한 비트 할당 Download PDFInfo

- Publication number

- KR20160125411A KR20160125411A KR1020167024390A KR20167024390A KR20160125411A KR 20160125411 A KR20160125411 A KR 20160125411A KR 1020167024390 A KR1020167024390 A KR 1020167024390A KR 20167024390 A KR20167024390 A KR 20167024390A KR 20160125411 A KR20160125411 A KR 20160125411A

- Authority

- KR

- South Korea

- Prior art keywords

- bits

- word

- bit

- significant

- optimization

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

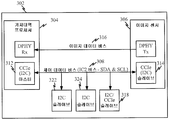

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4282—Bus transfer protocol, e.g. handshake; Synchronisation on a serial bus, e.g. I2C bus, SPI bus

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M13/00—Coding, decoding or code conversion, for error detection or error correction; Coding theory basic assumptions; Coding bounds; Error probability evaluation methods; Channel models; Simulation or testing of codes

- H03M13/03—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words

- H03M13/05—Error detection or forward error correction by redundancy in data representation, i.e. code words containing more digits than the source words using block codes, i.e. a predetermined number of check bits joined to a predetermined number of information bits

- H03M13/09—Error detection only, e.g. using cyclic redundancy check [CRC] codes or single parity bit

- H03M13/095—Error detection codes other than CRC and single parity bit codes

- H03M13/096—Checksums

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/16—Error detection or correction of the data by redundancy in hardware

- G06F11/1675—Temporal synchronisation or re-synchronisation of redundant processing components

- G06F11/1679—Temporal synchronisation or re-synchronisation of redundant processing components at clock signal level

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/22—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing

- G06F11/2205—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing using arrangements specific to the hardware being tested

- G06F11/221—Detection or location of defective computer hardware by testing during standby operation or during idle time, e.g. start-up testing using arrangements specific to the hardware being tested to test buses, lines or interfaces, e.g. stuck-at or open line faults

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/30—Monitoring

- G06F11/3003—Monitoring arrangements specially adapted to the computing system or computing system component being monitored

- G06F11/3027—Monitoring arrangements specially adapted to the computing system or computing system component being monitored where the computing system component is a bus

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4282—Bus transfer protocol, e.g. handshake; Synchronisation on a serial bus, e.g. I2C bus, SPI bus

- G06F13/4291—Bus transfer protocol, e.g. handshake; Synchronisation on a serial bus, e.g. I2C bus, SPI bus using a clocked protocol

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2213/00—Indexing scheme relating to interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F2213/0016—Inter-integrated circuit (I2C)

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Quality & Reliability (AREA)

- Computing Systems (AREA)

- Probability & Statistics with Applications (AREA)

- Computer Hardware Design (AREA)

- Mathematical Physics (AREA)

- Information Transfer Systems (AREA)

- Error Detection And Correction (AREA)

- Detection And Prevention Of Errors In Transmission (AREA)

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201461946647P | 2014-02-28 | 2014-02-28 | |

| US61/946,647 | 2014-02-28 | ||

| US14/634,106 US20150248373A1 (en) | 2014-02-28 | 2015-02-27 | Bit allocation over a shared bus to facilitate an error detection optimization |

| US14/634,106 | 2015-02-27 | ||

| PCT/US2015/018202 WO2015131164A1 (en) | 2014-02-28 | 2015-02-28 | Bit allocation over a shared bus to facilitate an error detection optimization |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20160125411A true KR20160125411A (ko) | 2016-10-31 |

Family

ID=54006839

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020167024390A Withdrawn KR20160125411A (ko) | 2014-02-28 | 2015-02-28 | 에러 검출 최적화를 용이하게 하는 공유된 버스를 통한 비트 할당 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20150248373A1 (enExample) |

| EP (1) | EP3111561A1 (enExample) |

| JP (1) | JP2017511044A (enExample) |

| KR (1) | KR20160125411A (enExample) |

| CN (1) | CN106068505A (enExample) |

| WO (1) | WO2015131164A1 (enExample) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9778971B2 (en) * | 2011-09-27 | 2017-10-03 | Mitsubishi Electric Corporation | Slave device, master device, and communication method |

| US9690725B2 (en) | 2014-01-14 | 2017-06-27 | Qualcomm Incorporated | Camera control interface extension with in-band interrupt |

| US9996488B2 (en) | 2013-09-09 | 2018-06-12 | Qualcomm Incorporated | I3C high data rate (HDR) always-on image sensor 8-bit operation indicator and buffer over threshold indicator |

| US9519603B2 (en) | 2013-09-09 | 2016-12-13 | Qualcomm Incorporated | Method and apparatus to enable multiple masters to operate in a single master bus architecture |

| US10353837B2 (en) | 2013-09-09 | 2019-07-16 | Qualcomm Incorporated | Method and apparatus to enable multiple masters to operate in a single master bus architecture |

| EP3055929A1 (en) | 2013-10-09 | 2016-08-17 | Qualcomm Incorporated | ERROR DETECTION CAPABILITY OVER CCIe PROTOCOL |

| US9684624B2 (en) | 2014-01-14 | 2017-06-20 | Qualcomm Incorporated | Receive clock calibration for a serial bus |

| WO2015126983A1 (en) * | 2014-02-18 | 2015-08-27 | Qualcomm Incorporated | Technique to avoid metastability condition and avoid unintentional state changes of legacy i2c devices on a multi-mode bus |

| US10019306B2 (en) * | 2016-04-27 | 2018-07-10 | Western Digital Technologies, Inc. | Collision detection for slave storage devices |

| WO2017189206A1 (en) * | 2016-04-27 | 2017-11-02 | Qualcomm Incorporated | I3c high data rate (hdr) always-on image sensor 8-bit operation indicator and buffer over threshold indicator |

| JP6786871B2 (ja) | 2016-05-18 | 2020-11-18 | ソニー株式会社 | 通信装置、通信方法、プログラム、および、通信システム |

| US20180054216A1 (en) * | 2016-08-22 | 2018-02-22 | Qualcomm Incorporated | Flipped bits for error detection and correction for symbol transition clocking transcoding |

| JP6953226B2 (ja) * | 2017-08-04 | 2021-10-27 | ソニーセミコンダクタソリューションズ株式会社 | 通信装置、通信方法、プログラム、および、通信システム |

| JP7031961B2 (ja) | 2017-08-04 | 2022-03-08 | ソニーセミコンダクタソリューションズ株式会社 | 通信装置、通信方法、プログラム、および、通信システム |

| JP2023089317A (ja) * | 2020-05-11 | 2023-06-28 | ソニーセミコンダクタソリューションズ株式会社 | 通信装置及び通信システム |

| TWI837031B (zh) * | 2023-06-28 | 2024-03-21 | 明泰科技股份有限公司 | I2c匯流排監控裝置 |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1983001360A1 (en) * | 1981-10-08 | 1983-04-14 | Furse, Anthony, Gordon | Data communication system |

| FR2542531B1 (fr) * | 1983-03-09 | 1988-05-20 | Telephonie Ind Commerciale | Procede et dispositifs de transcodage d'informations binaires pour transmission multiplexe temporelle |

| US5872519A (en) * | 1992-05-22 | 1999-02-16 | Directed Electronics, Inc. | Advanced embedded code hopping system |

| DE69226766T2 (de) * | 1992-06-22 | 1999-04-15 | International Business Machines Corp., Armonk, N.Y. | Knotenpunkt und Schnittstelle für isochronen Token-Ring |

| US6370668B1 (en) * | 1999-07-23 | 2002-04-09 | Rambus Inc | High speed memory system capable of selectively operating in non-chip-kill and chip-kill modes |

| US8639849B2 (en) * | 2001-12-17 | 2014-01-28 | Sutech Data Solutions Co., Llc | Integrated circuits for high speed adaptive compression and methods therefor |

| JP3973630B2 (ja) * | 2004-01-20 | 2007-09-12 | シャープ株式会社 | データ伝送装置およびデータ伝送方法 |

| JP2007164765A (ja) * | 2005-11-15 | 2007-06-28 | Matsushita Electric Ind Co Ltd | Iicバス通信システム、スレーブ装置およびiicバス通信制御方法 |

| US7502992B2 (en) * | 2006-03-31 | 2009-03-10 | Emc Corporation | Method and apparatus for detecting presence of errors in data transmitted between components in a data storage system using an I2C protocol |

| US7707349B1 (en) * | 2006-06-26 | 2010-04-27 | Marvell International Ltd. | USB isochronous data transfer for a host based laser printer |

| US7738570B2 (en) * | 2006-12-22 | 2010-06-15 | Qimonda Ag | Sender, receiver and method of transferring information from a sender to a receiver |

| US8055988B2 (en) * | 2007-03-30 | 2011-11-08 | International Business Machines Corporation | Multi-bit memory error detection and correction system and method |

| TWI363520B (en) * | 2007-12-31 | 2012-05-01 | Htc Corp | Methods and systems for error detection of data transmission |

| US7990992B2 (en) * | 2008-06-19 | 2011-08-02 | Nokia Corporation | Electronically configurable interface |

| JP2010250048A (ja) * | 2009-04-15 | 2010-11-04 | Panasonic Corp | 送信装置、受信装置、データ伝送システム、及び画像表示装置 |

| CN102770851B (zh) * | 2010-02-26 | 2016-01-20 | 惠普发展公司,有限责任合伙企业 | 恢复不稳定总线的稳定性 |

| JP5510275B2 (ja) * | 2010-11-08 | 2014-06-04 | 株式会社デンソー | 通信システム、マスタノード、スレーブノード |

| CN202372971U (zh) * | 2010-11-29 | 2012-08-08 | 意法半导体股份有限公司 | 电子设备和电子系统 |

| US8842775B2 (en) * | 2011-08-09 | 2014-09-23 | Alcatel Lucent | System and method for power reduction in redundant components |

| EP3055929A1 (en) * | 2013-10-09 | 2016-08-17 | Qualcomm Incorporated | ERROR DETECTION CAPABILITY OVER CCIe PROTOCOL |

-

2015

- 2015-02-27 US US14/634,106 patent/US20150248373A1/en not_active Abandoned

- 2015-02-28 WO PCT/US2015/018202 patent/WO2015131164A1/en not_active Ceased

- 2015-02-28 JP JP2016554356A patent/JP2017511044A/ja active Pending

- 2015-02-28 KR KR1020167024390A patent/KR20160125411A/ko not_active Withdrawn

- 2015-02-28 CN CN201580010556.1A patent/CN106068505A/zh active Pending

- 2015-02-28 EP EP15711929.8A patent/EP3111561A1/en not_active Withdrawn

Also Published As

| Publication number | Publication date |

|---|---|

| JP2017511044A (ja) | 2017-04-13 |

| EP3111561A1 (en) | 2017-01-04 |

| US20150248373A1 (en) | 2015-09-03 |

| CN106068505A (zh) | 2016-11-02 |

| WO2015131164A1 (en) | 2015-09-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20160125411A (ko) | 에러 검출 최적화를 용이하게 하는 공유된 버스를 통한 비트 할당 | |

| US9678828B2 (en) | Error detection capability over CCIe protocol | |

| US9811499B2 (en) | Transcoding and transmission over a serial bus | |

| JP6625557B2 (ja) | センサーグローバルバス | |

| US9519603B2 (en) | Method and apparatus to enable multiple masters to operate in a single master bus architecture | |

| US10579581B2 (en) | Multilane heterogeneous serial bus | |

| US10402365B2 (en) | Data lane validation procedure for multilane protocols | |

| US9990330B2 (en) | Simultaneous edge toggling immunity circuit for multi-mode bus | |

| US9672176B2 (en) | Slave identifier scanning and hot-plug capability over CCIe bus |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

Patent event date: 20160902 Patent event code: PA01051R01D Comment text: International Patent Application |

|

| PG1501 | Laying open of application | ||

| PC1203 | Withdrawal of no request for examination |