KR20150031181A - 발광 장치 - Google Patents

발광 장치 Download PDFInfo

- Publication number

- KR20150031181A KR20150031181A KR20140118738A KR20140118738A KR20150031181A KR 20150031181 A KR20150031181 A KR 20150031181A KR 20140118738 A KR20140118738 A KR 20140118738A KR 20140118738 A KR20140118738 A KR 20140118738A KR 20150031181 A KR20150031181 A KR 20150031181A

- Authority

- KR

- South Korea

- Prior art keywords

- transistor

- potential

- wiring

- pixel

- light emitting

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/04—Structural and physical details of display devices

- G09G2300/0404—Matrix technologies

- G09G2300/0417—Special arrangements specific to the use of low carrier mobility technology

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0819—Several active elements per pixel in active matrix panels used for counteracting undesired variations, e.g. feedback or autozeroing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0852—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor being a dynamic memory with more than one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0262—The addressing of the pixel, in a display other than an active matrix LCD, involving the control of two or more scan electrodes or two or more data electrodes, e.g. pixel voltage dependent on signals of two data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/0291—Details of output amplifiers or buffers arranged for use in a driving circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0233—Improving the luminance or brightness uniformity across the screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/029—Improving the quality of display appearance by monitoring one or more pixels in the display panel, e.g. by monitoring a fixed reference pixel

- G09G2320/0295—Improving the quality of display appearance by monitoring one or more pixels in the display panel, e.g. by monitoring a fixed reference pixel by monitoring each display pixel

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Control Of El Displays (AREA)

Abstract

화상의 표시가 행해지는 기간 내에, 구동용 트랜지스터의 임계값 전압, 이동도 등의 전기적 특성에 기인하는 화소간의 휘도의 변동을 보정할 수 있는 발광 장치를 제공한다.

화소와, 상기 화소로부터 추출된 전류의 값을 정보로서 포함하는 신호를 생성하는 제1 회로와, 상기 신호에 따라서, 화상 신호를 보정하는 제2 회로를 갖고, 상기 화소는, 발광 소자와, 상기 화상 신호에 따라서 드레인 전류의 값이 정해지는 트랜지스터와, 상기 발광 소자에의 상기 드레인 전류의 공급을 제어하는 제1 스위치와, 상기 드레인 전류의 상기 화소로부터의 추출을 제어하고, 게다가 상기 발광 소자에의 상기 드레인 전류의 공급을 제어하는 제2 스위치를 갖는 발광 장치.

화소와, 상기 화소로부터 추출된 전류의 값을 정보로서 포함하는 신호를 생성하는 제1 회로와, 상기 신호에 따라서, 화상 신호를 보정하는 제2 회로를 갖고, 상기 화소는, 발광 소자와, 상기 화상 신호에 따라서 드레인 전류의 값이 정해지는 트랜지스터와, 상기 발광 소자에의 상기 드레인 전류의 공급을 제어하는 제1 스위치와, 상기 드레인 전류의 상기 화소로부터의 추출을 제어하고, 게다가 상기 발광 소자에의 상기 드레인 전류의 공급을 제어하는 제2 스위치를 갖는 발광 장치.

Description

본 발명은 물건, 방법, 또는, 제조 방법에 관한 것이다. 또는, 본 발명은 공정(process), 기계(machine), 제품(manufacture) 또는, 조성물(composition of matter)에 관한 것이다. 특히, 본 발명의 일 형태는, 반도체 장치, 표시 장치, 발광 장치, 축전 장치, 그들의 구동 방법, 또는 그들의 제조 방법에 관한 것이다. 특히, 본 발명의 일 형태는, 트랜지스터가 각 화소에 설치된 발광 장치에 관한 것이다.

발광 소자를 사용한 액티브 매트릭스형 발광 장치는, 화상 신호에 따라서 발광 소자에 공급하는 전류의 값을 제어하는 트랜지스터(구동용 트랜지스터)의 임계값 전압에 변동이 발생하면, 발광 소자의 휘도에도 그 변동이 반영되어 버린다. 상기 임계값 전압의 변동에 의한 발광 소자의 휘도의 변동을 방지하기 위해서, 다음의 특허문헌 1에서는, 임계값 전압 및 이동도의 변동에 의한 발광 소자의 휘도의 변동을, 화소의 내부에서 보정하는 표시 장치에 대해서 기재되어 있다. 또한, 하기의 특허문헌 2에서는, 구동용 트랜지스터의 소스 전압으로부터 임계값 전압 및 이동도를 검출하고, 검출된 임계값 전압 및 이동도에 기초하여, 표시 화상에 따른 프로그램 데이터 신호를 설정하는 표시 장치에 대해서 기재되어 있다.

특허문헌 1의 표시 장치에서는, 이동도의 변동에 기인하는, 구동용 트랜지스터의 드레인 전류의 변동을 정확하게 보정하는 것이 어려워, 화질 향상이라고 하는 점에 있어서 개선의 여지가 남겨져 있다. 또한, 특허문헌 2의 표시 장치와 같이, 화상 신호의 보정에 의해, 임계값 전압 및 이동도의 변동에 기인하는, 구동용 트랜지스터의 드레인 전류의 변동을 방지하는 표시 장치의 경우, 화상 신호의 보정을 행하는 동안에는 화상의 표시를 행할 수 없다. 따라서, 화상 신호의 보정은, 귀선(flyback) 기간 등, 화상의 표시에 관여하지 않는 특정한 짧은 기간 내에서 행할 필요가 있어, 보정의 동작을 제어하는 구동 회로측의 부담이 컸다.

상술한 바와 같은 기술적 배경 하에서, 본 발명의 일 형태는, 화상의 표시가 행해지는 기간 내에, 구동용 트랜지스터의 임계값 전압, 이동도 등의 전기적 특성에 기인하는 화소간의 휘도의 변동을 보정할 수 있는 발광 장치의 제공을, 과제의 하나로 한다. 또는, 본 발명의 일 형태는, 신규 발광 장치의 제공을, 과제의 하나로 한다. 또한, 이들 과제의 기재는, 다른 과제의 존재를 방해하는 것은 아니다. 또한, 본 발명의 일 형태는, 반드시 이들 과제 모두를 해결할 필요는 없다. 또한, 이들 이외의 과제는, 명세서, 도면, 청구항 등의 기재로부터, 저절로 명확해지는 것이며, 명세서, 도면, 청구항 등의 기재로부터, 이들 이외의 과제를 추출하는 것이 가능하다.

본 발명의 일 형태에 따른 발광 장치는, 화소와, 상기 화소로부터 추출된 전류의 값을 정보로서 포함하는 신호를 생성하는 제1 회로와, 상기 신호에 따라서, 화상 신호를 보정하는 제2 회로를 갖고, 상기 화소는, 발광 소자와, 상기 화상 신호에 따라서 드레인 전류의 값이 정해지는 트랜지스터와, 상기 발광 소자에의 상기 드레인 전류의 공급을 제어하는 제1 스위치와, 상기 드레인 전류의 상기 화소로부터의 추출을 제어하고, 게다가 상기 발광 소자에의 상기 드레인 전류의 공급을 제어하는 제2 스위치를 갖는다.

본 발명의 일 형태에 따르면, 화상의 표시가 행해지는 기간 내에, 구동용 트랜지스터의 임계값 전압, 이동도 등의 전기적 특성에 기인하는 화소간의 휘도의 변동을 보정하는 발광 장치를, 제공할 수 있다. 또는, 신규 반도체 장치, 표시 장치 또는 발광 장치, 등을 제공할 수 있다. 또한, 이들 효과의 기재는, 다른 효과의 존재를 방해하는 것은 아니다. 또한, 본 발명의 일 형태는, 반드시 이들 효과의 모두를 가질 필요는 없다. 또한, 이들 이외의 효과는, 명세서, 도면, 청구항 등의 기재로부터, 저절로 명확해지는 것이며, 명세서, 도면, 청구항 등의 기재로부터, 이들 이외의 효과를 추출하는 것이 가능하다.

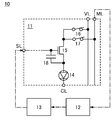

도 1은 발광 장치의 구성예를 도시하는 도면.

도 2는 발광 장치의 구체적인 구성예를 도시하는 도면.

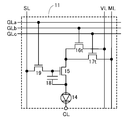

도 3은 화소의 구성예를 도시하는 도면.

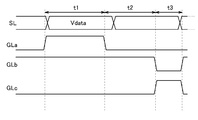

도 4는 화소의 타이밍차트.

도 5는 화소의 동작을 모식적으로 도시하는 도면.

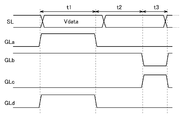

도 6은 화소의 타이밍차트.

도 7은 화소의 동작을 모식적으로 도시하는 도면.

도 8은 화소의 동작을 모식적으로 도시하는 도면.

도 9는 화소의 동작을 모식적으로 도시하는 도면.

도 10은 용량 소자라고 발광 소자가 직렬로 접속되어 있는 모습을, 모식적으로 도시하는 도면.

도 11은 화소의 구성예를 도시하는 도면.

도 12는 화소의 타이밍차트.

도 13은 화소의 동작을 모식적으로 도시하는 도면.

도 14는 화소의 타이밍차트.

도 15는 화소의 동작을 모식적으로 도시하는 도면.

도 16은 화소의 동작을 모식적으로 도시하는 도면.

도 17은 화소의 동작을 모식적으로 도시하는 도면.

도 18은 모니터 회로의 회로도.

도 19는 화소부와 선택 회로의 구성을 도시하는 도면.

도 20은 발광 장치의 단면도.

도 21은 트랜지스터의 단면도.

도 22는 발광 장치의 사시도.

도 23은 전자 기기의 도면.

도 24는 화소의 레이아웃을 도시하는 도면.

도 2는 발광 장치의 구체적인 구성예를 도시하는 도면.

도 3은 화소의 구성예를 도시하는 도면.

도 4는 화소의 타이밍차트.

도 5는 화소의 동작을 모식적으로 도시하는 도면.

도 6은 화소의 타이밍차트.

도 7은 화소의 동작을 모식적으로 도시하는 도면.

도 8은 화소의 동작을 모식적으로 도시하는 도면.

도 9는 화소의 동작을 모식적으로 도시하는 도면.

도 10은 용량 소자라고 발광 소자가 직렬로 접속되어 있는 모습을, 모식적으로 도시하는 도면.

도 11은 화소의 구성예를 도시하는 도면.

도 12는 화소의 타이밍차트.

도 13은 화소의 동작을 모식적으로 도시하는 도면.

도 14는 화소의 타이밍차트.

도 15는 화소의 동작을 모식적으로 도시하는 도면.

도 16은 화소의 동작을 모식적으로 도시하는 도면.

도 17은 화소의 동작을 모식적으로 도시하는 도면.

도 18은 모니터 회로의 회로도.

도 19는 화소부와 선택 회로의 구성을 도시하는 도면.

도 20은 발광 장치의 단면도.

도 21은 트랜지스터의 단면도.

도 22는 발광 장치의 사시도.

도 23은 전자 기기의 도면.

도 24는 화소의 레이아웃을 도시하는 도면.

이하에서는, 본 발명의 실시 형태에 대해서 도면을 사용해서 상세히 설명한다. 단, 본 발명은 이하의 설명에 한정되지 않고, 본 발명의 취지 및 그 범위로부터 일탈하지 않고 그 형태 및 상세를 다양하게 변경할 수 있는 것은, 당업자라면 용이하게 이해된다. 따라서, 본 발명은 이하에 나타내는 실시 형태의 기재 내용에 한정해서 해석되는 것은 아니다.

또한, 본 명세서에 있어서 접속이란 전기적인 접속을 의미하고 있으며, 전류, 전압 또는 전위가, 공급 가능 또는 전송 가능한 상태로 할 수 있는 회로 구성이 되어 있는 경우에 상당한다. 따라서, 접속하고 있는 회로 구성이란, 직접 접속하고 있는 회로 구성을 반드시 가리키는 것은 아니고, 전류, 전압 또는 전위가, 공급 가능 또는 전송 가능한, 배선, 저항, 다이오드, 트랜지스터 등의 소자를 통해서 전기적으로 접속하고 있는 회로 구성도, 그 범주에 포함한다.

또한, 회로도 상에는 독립되어 있는 구성 요소끼리가 접속되어 있는 경우에도, 실제로는, 예를 들어 배선의 일부가 전극으로서도 기능하는 경우 등, 하나의 도전막이, 복수의 구성 요소의 기능을 겸하고 있는 경우도 있다. 본 명세서에 있어서 접속이란, 이러한, 하나의 도전막이, 복수의 구성 요소의 기능을 겸하고 있는 경우도, 그 범주에 포함시킨다.

또한, 트랜지스터의 소스란, 반도체막으로서 기능하는 반도체막의 일부인 소스 영역, 또는 상기 반도체막에 전기적으로 접속된 소스 전극을 의미한다. 마찬가지로, 트랜지스터의 드레인이란, 반도체막으로서 기능하는 반도체막의 일부인 드레인 영역, 또는 상기 반도체막에 전기적으로 접속된 드레인 전극을 의미한다. 또한, 게이트는 게이트 전극을 의미한다.

트랜지스터가 갖는 소스와 드레인은, 트랜지스터의 채널형 및 각 단자에 부여되는 전위의 고저에 따라, 그 부르는 쪽이 바뀐다. 일반적으로, n채널형 트랜지스터에서는, 낮은 전위가 부여되는 단자가 소스라고 불리고, 높은 전위가 부여되는 단자가 드레인이라고 불린다. 또한, p 채널형 트랜지스터에서는, 낮은 전위가 부여되는 단자가 드레인이라고 불리고, 높은 전위가 부여되는 단자가 소스라고 불린다. 본 명세서에서는, 편의상, 소스와 드레인이 고정되어 있다고 가정하여, 트랜지스터의 접속 관계를 설명하는 경우가 있지만, 실제로는 상기 전위의 관계에 따라서 소스와 드레인을 부르는 쪽이 바뀐다.

<발광 장치의 구성예>

도 1에, 본 발명의 일 형태에 따른 발광 장치의 구성을, 일례로서 나타낸다. 도 1에 도시하는 발광 장치(10)는 화소(11)와, 모니터 회로(12)와, 화상 처리 회로(13)를 갖는다. 화소(11)는 발광 소자(14), 트랜지스터(15), 스위치(16), 스위치(17) 및 용량 소자(18)를 갖는다.

발광 소자(14)는 LED(Light Emitting Diode)나 OLED(Organic Light Emitting Diode) 등의, 전류 또는 전압에 의해 휘도가 제어되는 소자를 그 범주에 포함하고 있다. 예를 들어, OLED는, EL층과, 양극과, 음극을 적어도 갖고 있다. EL층은 양극과 음극 사이에 설치된 단층 또는 복수의 층으로 구성되어 있고, 이들 층 가운데, 발광성의 물질을 포함하는 발광층을 적어도 포함하고 있다. EL층은, 음극과 양극간의 전위차가, 발광 소자(14)의 임계값 전압 이상이 되었을 때에 공급되는 전류에 의해, 일렉트로루미네센스가 얻어진다. 일렉트로루미네센스에는, 일중항 여기 상태로부터 기저 상태로 되돌아갈 때의 발광(형광)과 삼중항 여기 상태로부터 기저 상태로 되돌아갈 때의 발광(인광)이 포함된다.

트랜지스터(15)는 배선 SL을 통해서 화소(11)에 입력된 화상 신호에 따라서, 드레인 전류의 값이 정해진다. 또한, 트랜지스터(15)는 통상의 게이트(제1 게이트) 외에, 임계값 전압을 제어하기 위한 백 게이트(제2 게이트)를 갖고 있어도 된다. 또한, 도 1에서는, 트랜지스터(15)가 n채널형인 경우를 예시하고 있고, 트랜지스터(15)의 소스 및 드레인 중 한쪽이, 발광 소자(14)의 양극에 접속되어 있다. 트랜지스터(15)가 p 채널형인 경우에는, 트랜지스터(15)의 소스는, 발광 소자(14)의 음극에 접속된다.

또한, 스위치(16)는 트랜지스터(15)의 드레인 전류의, 발광 소자(14)로의 공급을 제어하는 기능을 갖는다. 스위치(17)는 트랜지스터(15)의 드레인 전류의, 화소(11)로부터의 추출을 제어하는 기능과, 트랜지스터(15)의 드레인 전류의, 발광 소자(14)에의 공급을 제어하는 기능을 갖는다. 구체적으로, 스위치(16)는 트랜지스터(15)의 소스 및 드레인 중 다른 쪽과, 배선 VL 사이의 도통 상태를 제어하는 기능을 갖는다. 또한, 스위치(17)는 트랜지스터(15)의 소스 및 드레인 중 다른 쪽과, 배선 ML 사이의 도통 상태를 제어하는 기능을 갖는다. 배선 ML로부터 스위치(17)를 통해서 추출된, 트랜지스터(15)의 드레인 전류는, 모니터 회로(12)에 공급된다.

스위치(16) 또는 스위치(17)는, 예를 들어 트랜지스터를 단수 또는 복수 사용해서 구성할 수 있다. 또는, 스위치(16) 또는 스위치(17)는 단수 또는 복수의 트랜지스터에 더하여, 용량 소자를 사용하고 있어도 된다.

또한, 본 명세서 등에 있어서, 스위치로서는, 다양한 형태의 것을 사용할 수 있다. 스위치는, 도통 상태(온 상태) 또는, 비도통 상태(오프 상태)가 되어, 전류를 흘릴지 흘리지 않을지를 제어하는 기능을 갖고 있다. 또는, 스위치는, 전류를 흘리는 경로를 선택해서 전환하는 기능을 갖고, 예를 들어 경로 1에 전류를 흘릴 수 있게 할지, 경로 2에 전류를 흘릴 수 있게 할지를 선택해서 전환하는 기능을 갖고 있다. 스위치의 일례로서는, 전기적 스위치 또는 기계적인 스위치 등을 사용할 수 있다. 즉, 스위치는, 전류를 제어할 수 있는 것이면 된고, 특정한 것에 한정되지 않는다. 스위치의 일례로서는, 트랜지스터(예를 들어, 바이폴라 트랜지스터, MOS트랜지스터 등), 다이오드(예를 들어, PN 다이오드, PIN 다이오드, 숏키 다이오드, MIM(Metal Insulator Metal) 다이오드, MIS(Metal Insulator Semiconductor) 다이오드, 다이오드 접속의 트랜지스터 등), 또는 이들을 조합한 논리 회로 등이 있다. 기계적인 스위치의 일례로서는, 디지털 마이크로미러 디바이스(DMD)와 같이, MEMS(마이크로 일렉트로 메커니컬 시스템) 기술을 사용한 스위치가 있다. 그 스위치는, 기계적으로 움직이게 하는 것이 가능한 전극을 갖고, 그 전극이 움직이는 것에 의해, 도통과 비도통을 제어해서 동작한다.

트랜지스터(15)가 n채널형인 경우, 발광 소자(14)의 음극은, 배선 CL에 접속되어 있다. 그리고, 배선 VL의 전위가, 배선 CL의 전위에 발광 소자(14)의 임계값 전압 Vthe와, 트랜지스터(15)의 임계값 전압 Vth를 가산한 전위보다 높은 경우, 스위치(16)가 온이 되면, 트랜지스터(15)의 드레인 전류가 발광 소자(14)에 공급된다. 그리고, 발광 소자(14)의 휘도는, 드레인 전류의 값에 의해 정해진다. 또한, 배선 ML의 전위가, 배선 CL의 전위에 발광 소자(14)의 임계값 전압 Vthe와, 트랜지스터(15)의 임계값 전압 Vth를 가산한 전위보다 높은 경우, 스위치(17)가 온이 되면, 트랜지스터(15)의 드레인 전류가 발광 소자(14)에 공급된다. 그리고, 발광 소자(14)의 휘도는, 드레인 전류의 값에 의해 정해진다.

트랜지스터(15)가 p 채널형인 경우, 발광 소자(14)의 양극은, 배선 CL에 접속된다. 또한, 배선 CL의 전위가, 배선 VL의 전위에 발광 소자(14)의 임계값 전압 Vthe와, 트랜지스터(15)의 임계값 전압 Vth를 가산한 전위보다 높은 경우, 스위치(16)가 온이 되면, 트랜지스터(15)의 드레인 전류가 발광 소자(14)에 공급된다. 그리고, 발광 소자(14)의 휘도는, 드레인 전류의 값에 의해 정해진다. 또한, 배선 CL의 전위가, 배선 ML의 전위에 발광 소자(14)의 임계값 전압 Vthe와, 트랜지스터(15)의 임계값 전압 Vth를 가산한 전위보다 높은 경우, 스위치(17)가 온이 되면, 트랜지스터(15)의 드레인 전류가 발광 소자(14)에 공급된다. 그리고, 발광 소자(14)의 휘도는, 드레인 전류의 값에 의해 정해진다.

용량 소자(18)는 트랜지스터(15)의 게이트와, 소스 및 드레인 중 한쪽 사이의 전위차를, 유지하는 기능을 갖는다. 단, 용량 소자(18)는 예를 들어 트랜지스터(15)의 게이트와 반도체막 사이에 형성되는 게이트 용량이 충분히 큰 경우 등은, 반드시 화소(11)에 설치할 필요는 없다.

화소(11)는 발광 소자(14), 트랜지스터(15), 스위치(16), 스위치(17), 용량 소자(18) 뿐만 아니라, 트랜지스터, 용량 소자, 저항, 인덕터 등의 다른 회로 소자를 더 갖고 있어도 된다.

또한, 모니터 회로(12)는 스위치(17)를 통해서 화소(11)로부터 추출된, 트랜지스터(15)의 드레인 전류를 사용해서, 그 전류의 값을 정보로서 포함하는 신호를, 생성하는 기능을 갖는다. 모니터 회로(12)로서, 예를 들어 적분 회로 등의, 전류 전압 변환 회로를 사용할 수 있다.

화상 처리 회로(13)는 모니터 회로(12)에서 생성된 상기 신호에 따라서, 화소(11)에 입력되는 화상 신호를 보정하는 기능을 갖는다. 구체적으로는, 모니터 회로(12)에서 생성된 신호로부터, 트랜지스터(15)의 드레인 전류가 원하는 값보다 크다고 판단된 경우, 트랜지스터(15)의 드레인 전류가 작아지도록, 화상 신호를 보정한다. 반대로, 모니터 회로(12)에서 생성된 신호로부터, 트랜지스터(15)의 드레인 전류가 원하는 값보다 작다고 판단된 경우, 트랜지스터(15)의 드레인 전류가 커지도록, 화상 신호를 보정한다.

화상 신호의 보정에 의해, 화소(11) 사이에 존재하는 트랜지스터(15)의 임계값 전압의 변동뿐만 아니라, 트랜지스터(15)의 이동도 등의 그 외의 전기적 특성의 변동도, 보정할 수 있다. 따라서, 화소(11) 내에서, 임계값 전압의 보정을 행하는 경우보다, 화소(11) 사이에 있어서의 발광 소자(14)의 휘도의 변동을, 더욱 억제할 수 있다.

그리고, 화소(11)에서는, 화상 신호의 보정을 행하는 경우에는, 스위치(17)를 통해서 드레인 전류를 추출하고, 화상 신호의 보정을 행하지 않는 경우에는, 스위치(16)를 통해서 발광 소자(14)에의 드레인 전류의 공급을 행한다. 즉, 본 발명의 일 형태에서는, 드레인 전류가 흐르는 경로를, 스위치(16)와 스위치(17)의 온과 오프의 선택, 즉 스위칭에 의해, 전환할 수 있다. 따라서, 복수의 화소(11)에 각각 접속된 복수의 배선 VL이, 서로 전기적으로 접속되어 있었다고 하더라도, 선택된 화소(11)로부터의 드레인 전류의 추출과, 선택된 화소(11) 이외의 화소(11)에 있어서의, 화상 신호에 기초한 계조의 표시를, 병행해서 행할 수 있다. 따라서, 본 발명의 일 형태에서는, 화상의 표시와 화상 신호의 보정을 병행해서 행할 수 있으므로, 화상의 표시에 관여하지 않는 특정한 짧은 기간 내에서 화상 신호의 보정을 행할 필요가 없어, 화상 신호의 보정 동작을 제어하는 구동 회로측의 부담을 경감할 수 있다.

또한, 본 발명의 일 형태에서는, 화상 신호에 따라서 트랜지스터(15)의 드레인 전류의 값을 정하기 전에, 스위치(17)를 온으로 해서, 배선 ML의 전위를 변화시킴으로써, 화소(11) 내에서 트랜지스터(15)의 임계값 전압의 보정을 행하는 것도 가능하다. 또는, 트랜지스터(15)의 소스 및 드레인 중 한쪽에, 스위치를 통해서 전위의 공급을 행할 수 있는 구성을, 도 1에 도시하는 화소(11)에 추가함으로써, 화소(11) 내에서 트랜지스터(15)의 임계값 전압의 보정을 행하는 것도 가능하다.

화소(11) 내에 있어서의 임계값 전압의 보정(이하, 내부 보정이라 칭함)을 행하지 않고, 화상 처리 회로(13)에 있어서의 화상 신호의 보정(이하, 외부 보정이라 칭함)을 행하는 경우에도, 화소(11) 사이에 존재하는 트랜지스터(15)의 임계값 전압의 변동뿐만 아니라, 이동도 등, 임계값 전압 이외의 트랜지스터(15)의 전기적 특성의 변동도 보정할 수 있다. 단, 외부 보정에 더하여 내부 보정도 행하는 경우, 임계값 전압의 마이너스 시프트 또는 플러스 시프트의 보정은, 내부 보정에 의해 행해진다. 따라서, 외부 보정에서는, 이동도 등의, 트랜지스터(15)에 있어서의 임계값 전압 이외의 전기적 특성의 변동을 보정하면 된다. 따라서, 외부 보정에 더하여 내부 보정도 행하는 경우, 외부 보정만을 행하는 경우에 비해, 보정 후에 있어서의 화상 신호의 전위의 진폭을, 작게 억제할 수 있다. 따라서, 화상 신호의 전위의 진폭이 너무 크기 때문에, 계조값간에 있어서의 화상 신호의 전위차가 커져서, 화상 내의 휘도의 변화를 매끄러운 그라데이션으로 표현하는 것이 어려워진다고 하는 사태가 발생하는 것을 방지할 수 있어, 화질이 저하되는 것을 방지할 수 있다.

<발광 장치의 구체적인 구성예>

이어서, 도 1에 도시한 발광 장치(10)의, 보다 상세한 구성의 일례에 대해서 설명한다. 도 2에, 본 발명의 일 형태에 따른 발광 장치(10)의 구성을, 블록도에서 일례로서 나타낸다. 또한, 블록도에서는, 구성 요소를 기능별로 분류하고, 서로 독립된 블록으로서 나타내고 있지만, 실제의 구성 요소는 기능별로 완전히 구분하는 것이 어려우며, 하나의 구성 요소가 복수의 기능에 관여될 수도 있다.

도 2에 도시하는 발광 장치(10)는 화소(11)를 화소부(24)에 복수 갖는 패널(25)과, 컨트롤러(26)와, CPU(27)와, 화상 처리 회로(13)와, 화상 메모리(28)와, 메모리(29)와, 모니터 회로(12)를 갖는다. 또한, 도 2에 도시하는 발광 장치(10)는 패널(25)에, 구동 회로(30)와, 구동 회로(31)를 갖는다.

CPU(27)는, 외부로부터 입력된 명령 또는 CPU(27) 내에 설치된 메모리에 기억되어 있는 명령을 디코드하고, 발광 장치(10)가 갖는 각종 회로의 동작을 통괄적으로 제어함으로써, 그 명령을 실행하는 기능을 갖는다.

모니터 회로(12)는 화소(11)로부터 추출된 드레인 전류로부터, 상기 드레인 전류의 값을 정보로서 포함하는 신호를 생성한다. 메모리(29)는 상기 신호에 포함되는 상기 정보를 기억하는 기능을 갖는다.

화상 메모리(28)는 발광 장치(10)에 입력된 화상 데이터(32)를 기억하는 기능을 갖는다. 또한, 도 2에서는, 화상 메모리(28)를 1개만 발광 장치(10)에 설치하는 경우를 예시하고 있지만, 복수의 화상 메모리(28)가 발광 장치(10)에 설치되어 있어도 된다. 예를 들어, 적, 청, 녹 등의 색상에 각각 대응하는 3개의 화상 데이터(32)에 의해, 화소부(24)에 풀 컬러의 화상이 표시되는 경우, 각 화상 데이터(32)에 대응한 화상 메모리(28)를 각각 설치할 수도 있다.

화상 메모리(28)에는, 예를 들어 DRAM(Dynamic Random Access Memory), SRAM(Static Random Access Memory) 등의 기억 회로를 사용할 수 있다. 또는, 화상 메모리(28)에, VRAM(Video RAM)을 사용해도 된다.

화상 처리 회로(13)는 CPU(27)로부터의 명령에 따라, 화상 데이터(32)의 화상 메모리(28)에의 기입과, 화상 데이터(32)의 화상 메모리(28)로부터의 판독을 행하여, 화상 데이터(32)로부터 화상 신호 Sig를 생성하는 기능을 갖는다. 또한, 화상 처리 회로(13)는 CPU(27)로부터의 명령에 따라, 메모리(29)에 기억되어 있는 정보를 판독하고, 그 정보를 사용해서, 화상 신호의 보정을 행하는 기능을 갖는다.

컨트롤러(26)는 화상 정보를 갖는 화상 신호 Sig가 입력되면, 패널(25)의 사양에 맞춰서 화상 신호 Sig에 신호 처리를 실시한 후, 패널(25)에 공급하는 기능을 갖는다.

구동 회로(31)는 화소부(24)가 갖는 복수의 화소(11)를 행마다 선택하는 기능을 갖는다. 또한, 구동 회로(30)는 컨트롤러(26)로부터 부여된 화상 신호 Sig를, 구동 회로(31)에 의해 선택된 행의 화소(11)에 공급하는 기능을 갖는다.

또한, 컨트롤러(26)는 구동 회로(30)나 구동 회로(31) 등의 구동에 사용되는 각종 구동 신호를, 패널(25)에 공급하는 기능을 갖는다. 구동 신호에는, 구동 회로(30)의 동작을 제어하는 스타트 펄스 신호 SSP, 클럭 신호 SCK, 래치 신호 LP, 구동 회로(31)의 동작을 제어하는 스타트 펄스 신호 GSP, 클럭 신호 GCK 등이 포함된다.

또한, 발광 장치(10)는, 발광 장치(10)가 갖는 CPU(27)에, 정보나 명령을 부여하는 기능을 갖는 입력 장치를 갖고 있어도 된다. 입력 장치로서, 키보드, 포인팅 디바이스, 터치 패널, 센서 등을 사용할 수 있다.

<화소의 구성예 1>

이어서, 도 1에 도시하는 발광 장치(10)가 갖는 화소(11)의 구체적인 구성예에 대해서 설명한다.

도 3에, 화소(11)의 회로도의 일례를 나타낸다. 화소(11)는 트랜지스터(15)와, 스위치(16)로서 기능하는 트랜지스터(16t)와, 스위치(17)로서 기능하는 트랜지스터(17t)와, 용량 소자(18)와, 발광 소자(14)와, 트랜지스터(19)를 갖는다.

발광 소자(14)의 화소 전극은, 화소(11)에 입력되는 화상 신호 Sig에 따라서 그 전위가 제어된다. 또한, 발광 소자(14)의 휘도는, 화소 전극과 공통 전극 사이의 전위차에 의해 정해진다. 예를 들어, OLED를 발광 소자(14)로서 사용하는 경우, 양극과 음극 중 어느 한쪽이 화소 전극으로서 기능하고, 다른 쪽이 공통 전극으로서 기능한다. 도 3에서는, 발광 소자(14)의 양극을 화소 전극으로서 사용하고, 발광 소자(14)의 음극을 공통 전극으로서 사용한 화소(11)의 구성을 예시하고 있다.

트랜지스터(19)는 배선 SL과, 트랜지스터(15)의 게이트 사이의 도통 상태를 제어하는 기능을 갖는다. 트랜지스터(15)는 소스 및 드레인 중 한쪽이, 발광 소자(14)의 양극에 접속되어 있다. 트랜지스터(16t)는 배선 VL과, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽 사이의 도통 상태를 제어하는 기능을 갖는다. 트랜지스터(17t)는 배선 ML과, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽 사이의 도통 상태를 제어하는 기능을 갖는다. 용량 소자(18)의 한 쌍 전극 중, 한쪽은 트랜지스터(15)의 게이트에 접속되고, 다른 쪽은 발광 소자(14)의 양극에 접속되어 있다.

또한, 트랜지스터(19)의 스위칭은, 트랜지스터(19)의 게이트에 접속된 배선 GLa의 전위에 따라서 행해진다. 트랜지스터(16t)의 스위칭은, 트랜지스터(16t)의 게이트에 접속된 배선 GLb의 전위에 따라서 행해진다. 트랜지스터(17t)의 스위칭은, 트랜지스터(17t)의 게이트에 접속된 배선 GLc의 전위에 따라서 행해진다.

화소(11)가 갖는 트랜지스터에는, 산화물 반도체나, 비정질, 미결정, 다결정, 또는 단결정의, 실리콘, 또는 게르마늄 등의 반도체를 사용할 수 있다. 트랜지스터(19)가 산화물 반도체를 채널 형성 영역에 포함함으로써, 트랜지스터(19)의 오프 전류를 매우 작게 할 수 있다. 그리고, 상기 구성을 갖는 트랜지스터(19)를 화소(11)에 사용함으로써 통상의 실리콘이나 게르마늄 등의 반도체로 형성된 트랜지스터를 트랜지스터(19)에 사용하는 경우에 비해, 트랜지스터(15)의 게이트에 축적된 전하의 누설을 방지할 수 있다.

따라서, 정지 화상과 같이, 연속되는 몇몇 프레임 기간에 걸쳐서, 화소부에 동일한 화상 정보를 갖는 화상 신호 Sig가 기입되는 경우 등은, 구동 주파수를 낮게 하는, 바꾸어 말하면 일정 기간 내에 있어서의 화소부에의 화상 신호 Sig의 기입 횟수를 적게 해도, 화상의 표시를 유지할 수 있다. 예를 들어, 고순도화된 산화물 반도체를 트랜지스터(19)의 반도체막에 사용함으로써 화상 신호 Sig의 기입의 간격을 10초 이상, 바람직하게는 30초 이상, 더욱 바람직하게는 1분 이상으로 할 수 있다. 그리고, 화상 신호 Sig가 기입되는 간격을 길게 하면 할수록, 소비 전력을 보다 저감시킬 수 있다.

또한, 화상 신호 Sig의 전위를 보다 긴 기간에 걸쳐서 유지할 수 있기 때문에, 트랜지스터(15)의 게이트 전위를 유지하기 위한 용량 소자(18)를 화소(11)에 설치하지 않더라도, 표시되는 화질이 저하되는 것을 방지할 수 있다. 따라서, 용량 소자(18)를 설치하지 않음으로써, 또는 용량 소자(18)의 사이즈를 작게 함으로써, 화소(11)의 개구율을 높일 수 있기 때문에, 발광 소자(14)의 장수명화를 실현하고, 나아가서는, 발광 장치(10)의 신뢰성을 높일 수 있다.

또한, 도 3에 있어서, 화소(11)는, 필요에 따라서, 트랜지스터, 다이오드, 저항 소자, 용량 소자, 인덕터 등의 그 외의 회로 소자를, 더 갖고 있어도 된다.

또한, 도 3에 있어서, 각 트랜지스터는, 게이트를, 반도체막의 한측(片側)에 적어도 갖고 있으면 되지만, 반도체막을 사이에 두고 존재하는 한 쌍의 게이트를 갖고 있어도 된다. 한 쌍의 게이트 중 한쪽을 백 게이트라 하면, 통상의 게이트 및 백 게이트에 동일한 레벨의 전위가 부여되어 있어도 되고, 백 게이트에만 접지 전위 등의 고정 전위가 부여되어 있어도 된다. 백 게이트에 부여하는 전위의 높이를 제어함으로써, 트랜지스터의 임계값 전압을 제어할 수 있다. 또한, 백 게이트를 설치함으로써, 채널 형성 영역이 늘어나, 드레인 전류의 증가를 실현할 수 있다. 또한, 백 게이트를 설치함으로써, 반도체막에 공핍층이 생기기 쉬워지기 때문에, S값의 개선을 도모할 수 있다.

또한, 도 3에서는, 트랜지스터가 모두 n채널형인 경우를 예시하고 있다. 화소(11) 내의 트랜지스터가 모두 동일한 채널형인 경우, 트랜지스터의 제작 공정에 있어서, 반도체막에 일 도전성을 부여하는 불순물 원소의 첨가 등의 공정을, 일부 생략할 수 있다. 단, 본 발명의 일 형태에 따른 발광 장치에서는, 반드시 화소(11) 내의 트랜지스터가 모두 n채널형일 필요는 없다. 발광 소자(14)의 음극이 배선 CL에 접속되어 있는 경우, 적어도 트랜지스터(15)는 n채널형인 것이 바람직하고, 발광 소자(14)의 양극이 배선 CL에 접속되어 있는 경우, 적어도 트랜지스터(15)는 p 채널형인 것이 바람직하다.

또한, 도 3에서는, 화소(11) 내의 트랜지스터가, 단수의 게이트를 가짐으로써, 단수의 채널 형성 영역을 갖는 싱글 게이트 구조인 경우를 예시하고 있지만, 본 발명의 일 형태는 이 구성에 한정되지 않는다. 화소(11) 내의 트랜지스터 중 어느 하나 또는 모두가, 전기적으로 접속된 복수의 게이트를 가짐으로써, 복수의 채널 형성 영역을 갖는 멀티 게이트 구조여도 된다.

<외부 보정의 동작예 1>

이어서, 도 3에 도시하는 화소(11)의, 외부 보정의 동작예에 대해서 설명한다.

도 4에, 도 3에 도시하는 화소(11)에 접속되는 배선 GLa, 배선 GLb, 배선 GLc의 전위와, 배선 SL에 공급되는 화상 신호 Sig의 전위의 타이밍차트를 예시한다. 또한, 도 4에 도시하는 타이밍차트는, 도 3에 도시하는 화소(11)에 포함되는 트랜지스터가 모두 n채널형인 경우를 예시하는 것이다. 또한, 도 5에, 각 기간에 있어서의 화소(11)의 동작을 모식적으로 도시한다. 단, 도 5에서는, 화소(11)의 동작을 이해하기 쉽게 나타내기 위해, 트랜지스터(15) 이외의 트랜지스터를, 스위치로서 도시한다.

먼저, 기간 t1에서는, 배선 GLa에 하이 레벨의 전위가 부여되고, 배선 GLb에 하이 레벨의 전위가 부여되고, 배선 GLc에 로우 레벨의 전위가 부여된다. 따라서, 도 5의 (A)에 도시한 바와 같이, 트랜지스터(19) 및 트랜지스터(16t)가 온으로 되고, 트랜지스터(17t)는 오프로 된다. 그리고, 배선 SL에는, 화상 신호 Sig의 전위 Vdata가 부여되어 있고, 전위 Vdata는, 트랜지스터(19)를 통해서 트랜지스터(15)의 게이트(노드 A로서 도시함)에 부여된다.

또한, 배선 VL에는 전위 Vano가 부여되고, 배선 CL에는 전위 Vcat가 부여된다. 전위 Vano는, 전위 Vcat에 발광 소자(14)의 임계값 전압 Vthe를 가산한 전위보다 높게 하는 것이 바람직하다. 배선 VL의 전위 Vano는, 트랜지스터(16t)를 통해서, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽(노드 B로서 도시함)에 부여된다. 따라서, 전위 Vdata에 따라서, 트랜지스터(15)의 드레인 전류의 값이 정해진다. 그리고, 상기 드레인 전류가 발광 소자(14)에 공급됨으로써, 발광 소자(14)의 휘도가 정해진다.

계속해서, 기간 t2에서는, 배선 GLa에 로우 레벨의 전위가 부여되고, 배선 GLb에 하이 레벨의 전위가 부여되고, 배선 GLc에 로우 레벨의 전위가 부여된다. 따라서, 트랜지스터(16t)가 온으로 되고, 트랜지스터(19) 및 트랜지스터(17t)가 오프로 된다. 트랜지스터(19)가 오프가 됨으로써, 트랜지스터(15)의 게이트에 있어서, 전위 Vdata가 유지된다. 또한, 배선 VL에는 전위 Vano가 부여되고, 배선 CL에는 전위 Vcat가 부여된다. 따라서, 발광 소자(14)에서는, 기간 t1에 있어서 정해진 휘도가 유지된다.

계속해서, 기간 t3에서는, 배선 GLa에 로우 레벨의 전위가 부여되고, 배선 GLb에 로우 레벨의 전위가 부여되고, 배선 GLc에 하이 레벨의 전위가 부여된다. 따라서, 도 5의 (B)에 도시한 바와 같이, 트랜지스터(17t)가 온으로 되고, 트랜지스터(19) 및 트랜지스터(16t)가 오프로 된다. 또한, 배선 CL에는 전위 Vcat가 부여된다. 그리고, 배선 ML에는 전위 Vano가 부여되고, 게다가 모니터 회로에 접속된다.

상기 동작에 의해, 트랜지스터(17t)를 통해서, 트랜지스터(15)의 드레인 전류는, 발광 소자(14)에 공급된다. 게다가, 상기 드레인 전류는, 배선 ML을 통해서 모니터 회로에도 공급된다. 모니터 회로는, 배선 ML에 흐르는 드레인 전류를 사용해서, 그 드레인 전류의 값을 정보로서 포함하는 신호를 생성한다. 그리고, 본 발명의 일 형태에 따른 발광 장치에서는, 상기 신호를 사용해서, 화소(11)에 공급되는 화상 신호 Sig의 전위 Vdata의 값을 보정할 수 있다.

또한, 도 3에 도시하는 화소(11)를 갖는 발광 장치에서는, 기간 t2의 동작 후에 기간 t3의 동작을 항상 행할 필요는 없다. 예를 들어, 발광 장치에 있어서, 기간 t1 내지 기간 t2의 동작을 복수회 반복한 후에, 기간 t3의 동작을 행하도록 해도 된다. 또한, 1행의 화소(11)에 있어서 기간 t3의 동작을 행한 후, 최소의 계조값 0에 대응하는 화상 신호를, 그 동작을 행한 1행의 화소(11)에 기입함으로써, 발광 소자(14)를 비발광의 상태로 한 후, 다음 행의 화소(11)에 있어서, 기간 t3의 동작을 행하도록 해도 된다.

<외부 보정과 내부 보정의 동작예 1>

이어서, 도 3에 도시하는 화소(11)의, 내부 보정과 외부 보정의 동작예에 대해서 설명한다.

도 6에, 도 3에 도시하는 화소(11)에 접속되는 배선 GLa, 배선 GLb, 배선 GLc의 전위와, 배선 SL에 공급되는 전위와, 배선 ML에 공급되는 전위의 타이밍차트를 예시한다. 또한, 도 6에 도시하는 타이밍차트는, 도 3에 도시하는 화소(11)에 포함되는 트랜지스터가 모두 n채널형인 경우를 예시하는 것이다. 또한, 도 7 내지 도 9에, 각 기간에 있어서의, 화소(11)의 동작을 모식적으로 도시한다. 단, 도 7에서는, 화소(11)의 동작을 이해하기 쉽게 나타내기 위해, 트랜지스터(15) 이외의 트랜지스터를, 스위치로서 도시한다.

먼저, 기간 t1에서는, 배선 GLa에 하이 레벨의 전위가 부여되고, 배선 GLb에 로우 레벨의 전위가 부여되고, 배선 GLc에 하이 레벨의 전위가 부여된다. 따라서, 도 7의 (A)에 도시한 바와 같이, 트랜지스터(19) 및 트랜지스터(17t)가 온으로 되고, 트랜지스터(16t)는 오프로 된다. 또한, 배선 ML에는 전위 Vano가 부여되고, 배선 CL에는 전위 Vcat가 부여되고, 배선 SL에는 전위 V0이 부여된다. 그리고, 배선 SL의 전위 V0은, 트랜지스터(19)를 통해서 트랜지스터(15)의 게이트(노드 A)에 부여되고, 배선 ML의 전위 Vano는, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽(노드 B)에 부여된다.

전위 V0은, 발광 소자(14)의 임계값 전압 Vthe 및 트랜지스터(15)의 임계값 전압 Vth를, 전위 Vcat에 가산한 전위보다 낮게 하는 것이 바람직하다. 전위 V0을 상기 값으로 설정함으로써, 기간 t1에 있어서 트랜지스터(15)를 오프로 하고, 발광 소자(14)에 전류가 흐르는 것을 방지할 수 있다.

계속해서, 기간 t2에서는, 배선 GLa에 하이 레벨의 전위가 부여되고, 배선 GLb에 로우 레벨의 전위가 부여되고, 배선 GLc에 하이 레벨의 전위가 부여된다. 따라서, 도 7의 (B)에 도시한 바와 같이, 트랜지스터(19) 및 트랜지스터(17t)가 온으로 되고, 트랜지스터(16t)는 오프로 된다. 또한, 배선 ML에는 전위 V1이 부여되고, 배선 CL에는 전위 Vcat가 부여되고, 배선 SL에는 전위 V0이 부여된다. 그리고, 배선 SL의 전위 V0은, 트랜지스터(19)를 통해서 트랜지스터(15)의 게이트에 부여되고, 배선 ML의 전위 V1은, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽에 부여된다.

전위 V1은, 전위 V0으로부터 트랜지스터(15)의 임계값 전압 Vth를 차감한 전위보다 충분히 낮은 것이 바람직하다. 상기 구성이 의해, 트랜지스터(15)는 온으로 되고, 배선 ML의 전위 V1이, 트랜지스터(15)의 소스 및 드레인 중 한쪽(노드 C로서 도시함)에 부여된다.

또한, 기간 t2에서는, 전위 V1을, 전위 Vcat에 발광 소자(14)의 임계값 전압 Vthe를 가산한 전위보다 충분히 낮게 할 수 있으므로, 발광 소자(14)는 발광하지 않는다.

계속해서, 기간 t3에서는, 배선 GLa에 하이 레벨의 전위가 부여되고, 배선 GLb에 로우 레벨의 전위가 부여되고, 배선 GLc에 하이 레벨의 전위가 부여된다. 따라서, 도 8의 (A)에 도시한 바와 같이, 트랜지스터(19) 및 트랜지스터(17t)가 온으로 되고, 트랜지스터(16t)는 오프로 된다. 또한, 배선 ML에는 전위 Vano가 부여되고, 배선 CL에는 전위 Vcat가 부여되고, 배선 SL에는 전위 V0이 부여된다. 그리고, 배선 SL의 전위 V0은, 트랜지스터(19)를 통해서 트랜지스터(15)의 게이트에 부여되고, 배선 ML의 전위 Vano는, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽에 부여된다.

기간 t3의 개시 시에는, 트랜지스터(15)는 온인 상태에 있기 때문에, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽에 배선 ML의 전위 Vano가 부여됨으로써, 트랜지스터(15)를 통해서 용량 소자(18)의 전하가 방출된다. 그리고, 트랜지스터(15)의 소스 및 드레인 중 한쪽(노드 C)은 전위 V1로부터 상승을 시작하여, 최종적으로는 전위 V0-Vth로 수렴된다. 따라서, 트랜지스터(15)는 오프가 되고, 용량 소자(18)에는, 임계값 전압 Vth가 취득된다.

또한, 기간 t3에서는, 트랜지스터(15)의 소스 및 드레인 중 한쪽(노드 C)는 전위 V0-Vth이며, 전위 Vcat에 발광 소자(14)의 임계값 전압 Vthe를 가산한 전위보다 낮기 때문에, 발광 소자(14)는 발광하지 않는다.

계속해서, 기간 t4에서는, 배선 GLa에 하이 레벨의 전위가 부여되고, 배선 GLb에 로우 레벨의 전위가 부여되고, 배선 GLc에 로우 레벨의 전위가 부여된다. 따라서, 도 8의 (B)에 도시한 바와 같이, 트랜지스터(19)가 온으로 되고, 트랜지스터(16t) 및 트랜지스터(17t)는 오프로 된다. 또한, 배선 CL에는 전위 Vcat가 부여되고, 배선 SL에는 화상 신호 Sig의 전위 Vdata가 부여된다. 또한, 도 6에서는, 기간 t4에 있어서, 배선 ML에 전위 Vano가 부여되어 있는 경우를 예시하고 있지만, 기간 t4에 있어서의 배선 ML에는, 전위 Vano 이외의 전위가 부여되어 있어도 된다.

배선 SL에 부여되는 전위 Vdata는, 트랜지스터(19)를 통해서 트랜지스터(15)의 게이트(노드 A)에 부여된다. 또한, 전위 Vdata는, 화상 신호 Sig가 갖는 화상 정보에 따라 그 높이가 다르다. 도 6에서는, 기간 t4에 있어서의 배선 SL에, 하이 레벨의 전위 Vdata(H)가 부여되는 경우와, 로우 레벨의 전위 Vdata(L)이 부여되는 경우의, 양쪽을 도시하고 있다.

또한, 기간 t4 종료 시에 있어서의 트랜지스터(15)의 소스 및 드레인 중 한쪽(노드 C)의 전위 V2에 대해서, 이하에 설명한다.

도 3에 도시하는 화소(11)에서는, 용량 소자(18)와 발광 소자(14)가 직렬로 접속된 구성을 갖고 있다. 도 10에, 용량 소자(18)와 발광 소자(14)가 직렬로 접속되어 있는 모습을, 모식적으로 도시한다. 도 10에서는, 발광 소자(14)가 용량 소자의 하나인 것으로 해서, 도시하고 있다. 도 10의 (A)는 기간 t3 종료 시에 상당하고, 도 10의 (B)는 기간 t4 종료 시에 상당한다. 도 10의 (A)에 도시한 바와 같이, 기간 t3 종료 시에서는, 트랜지스터(15)의 게이트(노드 A)에는 전위 V0이 부여되고, 트랜지스터(15)의 소스 및 드레인 중 한쪽(노드 C)는 전위 V0-Vth가 되어 있고, 배선 CL에는 전위 Vcat가 부여되어 있다. 그리고, 도 10의 (B)에 도시한 바와 같이, 기간 t4 종료 시에서는, 트랜지스터(15)가 오프인 경우, 노드 A에 전위 Vdata가 부여되면, 노드 C의 전위 V2는, 용량 소자(18)가 갖는 용량값 C1과, 발광 소자(14)가 갖는 용량값 C2의 비에 의해 결정된다.

단, 전위 Vdata의 높이에 따라서는, 기간 t4에 있어서 트랜지스터(15)가 온이 된다. 기간 t4에 있어서 트랜지스터(15)가 온인 경우, 트랜지스터(15)를 통해서, 노드 C에 전하가 유입되기 때문에, 노드 C의 전위 V2는, 용량 소자(18)가 갖는 용량값 C1과, 발광 소자(14)가 갖는 용량값 C2의 비에 의해서만 정해지지 않고, 노드 C에 유입되는 전하량에 따라 그 값이 변화된다.

구체적으로, 기간 t4 종료 시에 있어서의 노드 C의 전위를 전위 V2라 하면, 기간 t4에 있어서의, 노드 C에 대한 노드 A의 전압, 즉 트랜지스터(15)의 게이트 전압 Vgs는, 이하의 수학식 1로 표현된다. 또한, Q1은, 노드 C에 유입되는 전하량을 의미한다.

[수학식 1]

Vgs=Vdata-V2=C2(Vdata-V0)/(C1+C2)+Vth-Q1/(C1+C2)

또한, 기간 t4 종료 시에 있어서의, 이상적인 게이트 전압 Vgs는 Vgs=Vdata-V0+Vth이다. 게이트 전압 Vgs가 상기 값을 갖고 있으면, 트랜지스터(15)의 임계값 전압 Vth에 변동이 발생하더라도, 이러한 변동은 트랜지스터(15)의 드레인 전류에 영향을 미치지 못하게 된다. 게이트 전압 Vgs를 이상적인 값에 가깝게 하기 위해서는, 수학식 1에서, C2/(C1+C2)을 1에 가깝게 하는 것이 바람직한 것을 알 수 있다. 즉, 발광 소자(14)의 용량값 C2가, 용량 소자(18)의 용량값 C1보다 충분히 크면, 게이트 전압 Vgs를 이상적인 값에 가깝게 할 수 있으므로, 바람직하다.

또한, 게이트 전압 Vgs를 이상적인 값에 가깝게 하기 위해서는, 수학식 1에서, Q1/(C1+C2)를 작게 하는 것이 바람직한 것을 알 수 있다. 즉, 노드 C에 유입되는 전하량 Q1을 작게 하는 것이, 게이트 전압 Vgs를 이상적인 값에 가깝게 하는 데 있어서, 바람직하다. 따라서, 전하량 Q1을 작게 하기 위해서 기간 t4는 가능한 한 짧은 쪽이 좋다.

또한, 도 3에 도시한 화소(11)를 갖는 발광 장치에서는, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽과, 트랜지스터(15)의 게이트가 전기적으로 분리되어 있으므로, 각각의 전위를 개별로 제어할 수 있다. 따라서, 기간 t3에 있어서, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽의 전위를, 트랜지스터(15)의 게이트 전위에, 임계값 전압 Vth를 가산한 전위보다 높은 값으로 설정할 수 있다. 그로 인해, 트랜지스터(15)가 노멀리 온인 경우에, 즉 임계값 전압 Vth가 마이너스인 값을 갖고 있는 경우에, 트랜지스터(15)에 있어서, 소스의 전위가 게이트의 전위 V0보다 높아질 때까지, 용량 소자(18)에 전하를 축적할 수 있다. 따라서, 본 발명의 일 형태에 따른 발광 장치에서는, 트랜지스터(15)가 노멀리 온이어도, 기간 t3에 있어서 용량(18)에 임계값 전압을 취득할 수 있어, 기간 t3에 있어서, 임계값 전압 Vth를 가미한 값이 되도록, 트랜지스터(15)의 게이트 전압 Vgs를 설정할 수 있다.

따라서, 본 발명의 일 형태에 따른 발광 장치에서는, 예를 들어 트랜지스터(15)의 반도체막에 산화물 반도체를 사용한 경우 등에, 트랜지스터(15)가 노멀리 온으로 되더라도, 표시 얼룩을 저감시킬 수 있어, 높은 화질의 표시를 행할 수 있다.

기간 t4에 있어서 설정된 게이트 전압 Vgs는, 용량 소자(18)에 있어서 유지된다.

계속해서, 기간 t5에서는, 배선 GLa에 로우 레벨의 전위가 부여되고, 배선 GLb에 하이 레벨의 전위가 부여되고, 배선 GLc에 로우 레벨의 전위가 부여된다. 따라서, 도 9의 (A)에 도시한 바와 같이, 트랜지스터(16t)가 온으로 되고, 트랜지스터(19) 및 트랜지스터(17t)가 오프로 된다. 트랜지스터(19)가 오프가 됨으로써, 트랜지스터(15)의 게이트에 있어서, 전위 Vdata가 유지된다. 또한, 배선 VL에는 전위 Vano가 부여되고, 배선 CL에는 전위 Vcat가 부여된다. 따라서, 발광 소자(14)에서는, 기간 t4에 있어서 정해진 휘도가 유지된다.

또한, 도 6에서는, 기간 t5에 있어서, 배선 ML에 전위 Vano가 부여되어 있는 경우를 예시하고 있지만, 기간 t5에 있어서의 배선 ML에는, 전위 Vano 이외의 전위가 부여되어 있어도 된다.

계속해서, 기간 t6에서는, 배선 GLa에 로우 레벨의 전위가 부여되고, 배선 GLb에 로우 레벨의 전위가 부여되고, 배선 GLc에 하이 레벨의 전위가 부여된다. 따라서, 도 9의 (B)에 도시한 바와 같이, 트랜지스터(17t)가 온으로 되고, 트랜지스터(19) 및 트랜지스터(16t)가 오프로 된다. 또한, 배선 CL에는 전위 Vcat가 부여된다. 그리고, 배선 ML에는 전위 Vano가 부여되고, 게다가 모니터 회로에 접속된다.

상기 동작에 의해, 트랜지스터(17t)를 통해서, 트랜지스터(15)의 드레인 전류는, 발광 소자(14)에 공급된다. 게다가, 상기 드레인 전류는, 배선 ML을 통해서 모니터 회로에도 공급된다. 모니터 회로는, 배선 ML에 흐르는 드레인 전류를 사용해서, 그 드레인 전류의 값을 정보로서 포함하는 신호를 생성한다. 그리고, 본 발명의 일 형태에 따른 발광 장치에서는, 상기 신호를 사용해서, 화소(11)에 공급되는 화상 신호 Sig의 전위 Vdata의 값을 보정할 수 있다.

또한, 도 3에 도시하는 화소(11)를 갖는 발광 장치에서는, 기간 t5의 동작 후에 기간 t6의 동작을 항상 행할 필요는 없다. 예를 들어, 발광 장치에 있어서, 기간 t1 내지 기간 t5의 동작을 복수회 반복한 후에, 기간 t6의 동작을 행하도록 해도 된다. 또한, 1행의 화소(11)에 있어서 기간 t6의 동작을 행한 후, 최소의 계조값 0에 대응하는 화상 신호를, 그 동작을 행한 1행의 화소(11)에 기입함으로써, 발광 소자(14)를 비발광의 상태로 한 후, 다음 행의 화소(11)에 있어서, 기간 t6의 동작을 행하도록 해도 된다.

<화소의 구성예 2>

이어서, 도 1에 도시하는 발광 장치(10)가 갖는 화소(11)의, 도 3과는 다른 구성예에 대해서 설명한다.

도 11에, 화소(11)의 회로도 일례를 나타낸다. 도 11에 도시하는 화소(11)는 트랜지스터(15), 스위치(16)로서 기능하는 트랜지스터(16t), 스위치(17)로서 기능하는 트랜지스터(17t), 용량 소자(18), 발광 소자(14) 및 트랜지스터(19)에 더하여, 트랜지스터(20)를 갖는 점에 있어서, 도 3에 도시하는 화소(11)와 구성이 다르다.

트랜지스터(20)는 배선 RL과, 발광 소자(14)의 양극 사이의 도통 상태를 제어하는 기능을 갖는다. 그리고, 트랜지스터(20)의 스위칭은, 트랜지스터(20)의 게이트에 접속된 배선 GLd의 전위에 따라서 행해진다.

또한, 도 11에 있어서, 화소(11)는, 필요에 따라서, 트랜지스터, 다이오드, 저항 소자, 용량 소자, 인덕터 등의 그 외의 회로 소자를, 더 갖고 있어도 된다.

<외부 보정의 동작예 2>

이어서, 도 11에 도시하는 화소(11)의, 외부 보정의 동작예에 대해서 설명한다.

도 12에, 도 11에 도시하는 화소(11)에 접속되는 배선 GLa, 배선 GLb, 배선 GLc, 배선 GLd의 전위와, 배선 SL에 공급되는 화상 신호 Sig의 전위의 타이밍차트를 예시한다. 또한, 도 12에 도시하는 타이밍차트는, 도 11에 도시하는 화소(11)에 포함되는 트랜지스터가 모두 n채널형인 경우를 예시하는 것이다. 또한, 도 13에, 각 기간에 있어서의 화소(11)의 동작을 모식적으로 도시한다. 단, 도 13에서는, 화소(11)의 동작을 이해하기 쉽게 나타내기 위해, 트랜지스터(15) 이외의 트랜지스터를, 스위치로서 도시한다.

먼저, 기간 t1에서는, 배선 GLa에 하이 레벨의 전위가 부여되고, 배선 GLb에 하이 레벨의 전위가 부여되고, 배선 GLc에 로우 레벨의 전위가 부여되고, 배선 GLd에 하이 레벨의 전위가 부여된다. 따라서, 도 13의 (A)에 도시한 바와 같이, 트랜지스터(19), 트랜지스터(16t) 및 트랜지스터(20)가 온으로 되고, 트랜지스터(17t)는 오프로 된다. 또한, 배선 SL에는, 화상 신호 Sig의 전위 Vdata가 부여되어 있고, 전위 Vdata는, 트랜지스터(19)를 통해서 트랜지스터(15)의 게이트(노드 A)에 부여된다. 따라서, 전위 Vdata에 따라, 트랜지스터(15)의 드레인 전류의 값이 정해진다. 그리고, 배선 VL에는 전위 Vano가 부여되고, 배선 RL에는 전위 V1이 부여되기 때문에, 그 드레인 전류는, 트랜지스터(16t) 및 트랜지스터(20)를 통해서, 배선 VL과 배선 RL 사이로 흐른다.

전위 Vano는, 전위 Vcat에 발광 소자(14)의 임계값 전압 Vthe를 가산한 전위보다 높게 하는 것이 바람직하다. 배선 VL의 전위 Vano는, 트랜지스터(16t)를 통해서, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽(노드 B)에 부여된다. 또한, 배선 RL에 부여된 전위 V1은, 트랜지스터(20)를 통해서 트랜지스터(15)의 소스 및 드레인 중 한쪽(노드 C)에 부여된다. 배선 CL에는 전위 Vcat가 부여된다.

또한, 전위 V1은, 전위 V0으로부터 트랜지스터(15)의 임계값 전압 Vth를 차감한 전위보다 충분히 낮은 것이 바람직하다. 기간 t1에서는, 전위 V1을, 전위 Vcat에 발광 소자(14)의 임계값 전압 Vthe를 가산한 전위보다 충분히 낮게 할 수 있으므로, 발광 소자(14)는 발광하지 않는다.

계속해서, 기간 t2에서는, 배선 GLa에 로우 레벨의 전위가 부여되고, 배선 GLb에 하이 레벨의 전위가 부여되고, 배선 GLc에 로우 레벨의 전위가 부여되고, 배선 GLd에 로우 레벨의 전위가 부여된다. 따라서, 트랜지스터(16t)가 온으로 되고, 트랜지스터(19), 트랜지스터(17t) 및 트랜지스터(20)가 오프로 된다. 트랜지스터(19)가 오프가 됨으로써, 트랜지스터(15)의 게이트에 있어서, 전위 Vdata가 유지된다.

또한, 배선 VL에는 전위 Vano가 부여되고, 배선 CL에는 전위 Vcat가 부여된다. 따라서, 기간 t1에 있어서 값이 정해진 트랜지스터(15)의 드레인 전류는, 트랜지스터(20)가 오프가 됨으로써, 발광 소자(14)에 공급된다. 그리고, 발광 소자(14)에 상기 드레인 전류가 공급됨으로써, 발광 소자(14)의 휘도가 정해지고, 그 휘도는 기간 t2에 있어서 유지된다.

계속해서, 기간 t3에서는, 배선 GLa에 로우 레벨의 전위가 부여되고, 배선 GLb에 로우 레벨의 전위가 부여되고, 배선 GLc에 하이 레벨의 전위가 부여되고, 배선 GLd에 로우 레벨의 전위가 부여된다. 따라서, 도 13의 (B)에 도시한 바와 같이, 트랜지스터(17t)가 온으로 되고, 트랜지스터(19), 트랜지스터(16t) 및 트랜지스터(20)가 오프로 된다. 또한, 배선 CL에는 전위 Vcat가 부여된다. 그리고, 배선 ML에는 전위 Vano가 부여되고, 게다가 모니터 회로에 접속된다.

상기 동작에 의해, 트랜지스터(17t)를 통해서, 트랜지스터(15)의 드레인 전류는, 발광 소자(14)에 공급된다. 게다가, 상기 드레인 전류는, 배선 ML을 통해서 모니터 회로에도 공급된다. 모니터 회로는, 배선 ML에 흐르는 드레인 전류를 사용해서, 그 드레인 전류의 값을 정보로서 포함하는 신호를 생성한다. 그리고, 본 발명의 일 형태에 따른 발광 장치에서는, 상기 신호를 사용해서, 화소(11)에 공급되는 화상 신호 Sig의 전위 Vdata의 값을 보정할 수 있다.

또한, 도 11에 도시하는 화소(11)를 갖는 발광 장치에서는, 기간 t2의 동작 후에 기간 t3의 동작을 항상 행할 필요는 없다. 예를 들어, 발광 장치에 있어서, 기간 t1 내지 기간 t2의 동작을 복수회 반복한 후에, 기간 t3의 동작을 행하도록 해도 된다. 또한, 1행의 화소(11)에 있어서 기간 t3의 동작을 행한 후, 최소의 계조값 0에 대응하는 화상 신호를, 그 동작을 행한 1행의 화소(11)에 기입함으로써, 발광 소자(14)를 비발광의 상태로 한 후, 다음 행의 화소(11)에 있어서, 기간 t3의 동작을 행하도록 해도 된다.

또한, 도 11에 도시하는 화소(11)에서는, 발광 소자(14)의 열화 등에 의해, 발광 소자(14)의 양극과 음극간의 저항값이 화소 사이에서 변동되더라도, 전위 Vdata를 트랜지스터(15)의 게이트(노드 A)에 부여할 때, 트랜지스터(15)의 소스의 전위를 소정의 전위 V1로 설정할 수 있다. 따라서, 화소 사이에 있어서 발광 소자(14)의 휘도에 변동이 발생하는 것을, 방지할 수 있다.

<외부 보정과 내부 보정의 동작예 2>

이어서, 도 11에 도시하는 화소(11)의, 내부 보정과 외부 보정의 동작예에 대해서 설명한다.

도 14에, 도 11에 도시하는 화소(11)에 접속되는 배선 GLa, 배선 GLb, 배선 GLc, 배선 GLd의 전위와, 배선 SL에 공급되는 전위의 타이밍차트를 예시한다. 또한, 도 14에 도시하는 타이밍차트는, 도 11에 도시하는 화소(11)에 포함되는 트랜지스터가 모두 n채널형인 경우를 예시하는 것이다. 또한, 도 15 내지 도 17에, 각 기간에 있어서의, 화소(11)의 동작을 모식적으로 도시한다. 단, 도 15에서는, 화소(11)의 동작을 이해하기 쉽게 나타내기 위해, 트랜지스터(15) 이외의 트랜지스터를, 스위치로서 도시한다.

먼저, 기간 t1에서는, 배선 GLa에 하이 레벨의 전위가 부여되고, 배선 GLb에 로우 레벨의 전위가 부여되고, 배선 GLc에 하이 레벨의 전위가 부여되고, 배선 GLd에 하이 레벨의 전위가 부여된다. 따라서, 도 15의 (A)에 도시한 바와 같이, 트랜지스터(19), 트랜지스터(20) 및 트랜지스터(17t)가 온으로 되고, 트랜지스터(16t)는 오프로 된다. 또한, 배선 ML에는 전위 Vano가 부여되고, 배선 CL에는 전위 Vcat가 부여되고, 배선 SL에는 전위 V0이 부여되고, 배선 RL에는 전위 V1이 부여된다. 그리고, 배선 SL의 전위 V0은, 트랜지스터(19)를 통해서 트랜지스터(15)의 게이트(노드 A)에 부여되고, 배선 ML의 전위 Vano는, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽(노드 B)에 부여된다. 또한, 배선 RL에 부여된 전위 V1은, 트랜지스터(20)를 통해서 트랜지스터(15)의 소스 및 드레인 중 한쪽(노드 C)에 부여된다.

전위 V0은, 발광 소자(14)의 임계값 전압 Vthe 및 트랜지스터(15)의 임계값 전압 Vth를, 전위 Vcat에 가산한 전위보다 낮게 하는 것이 바람직하다. 또한, 전위 V1은, 전위 V0으로부터 트랜지스터(15)의 임계값 전압 Vth를 차감한 전위보다 충분히 낮은 것이 바람직하다.

기간 t1에서는, 트랜지스터(15)의 게이트 전압 Vgs가 전위 V0과 전위 V1의 전위차가 되기 때문에, 임계값 전압보다 커지고, 트랜지스터(15)는 온이 된다. 그리고, 배선 ML에는 전위 Vano가 부여되고, 배선 RL에는 전위 V1이 부여되기 때문에, 트랜지스터(15)의 드레인 전류는, 트랜지스터(17t) 및 트랜지스터(20)를 통해서, 배선 VL과 배선 RL 사이로 흐른다.

계속해서, 기간 t2에서는, 배선 GLa에 하이 레벨의 전위가 부여되고, 배선 GLb에 로우 레벨의 전위가 부여되고, 배선 GLc에 하이 레벨의 전위가 부여되고, 배선 GLd에 로우 레벨의 전위가 부여된다. 따라서, 도 15의 (B)에 도시한 바와 같이, 트랜지스터(19) 및 트랜지스터(17t)가 온으로 되고, 트랜지스터(16t) 및 트랜지스터(20)는 오프로 된다. 또한, 배선 ML에는 전위 Vano가 부여되고, 배선 CL에는 전위 Vcat가 부여되고, 배선 SL에는 전위 V0이 부여된다. 그리고, 배선 SL의 전위 V0은, 트랜지스터(19)를 통해서 트랜지스터(15)의 게이트에 부여되고, 배선 ML의 전위 Vano는, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽(노드 B)에 부여된다.

기간 t2의 개시 시에는, 트랜지스터(15)는 온인 상태에 있기 때문에, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽에 배선 ML의 전위 Vano가 부여됨으로써, 트랜지스터(15)를 통해서 용량 소자(18)의 전하가 방출된다. 그리고, 트랜지스터(15)의 소스 및 드레인 중 한쪽(노드 C)은 전위 V1로부터 상승을 시작하여, 최종적으로는 전위 V0-Vth로 수렴된다. 따라서, 트랜지스터(15)는 오프가 되고, 용량 소자(18)에는, 임계값 전압 Vth가 취득된다.

또한, 기간 t2에서는, 트랜지스터(15)의 소스 및 드레인 중 한쪽(노드 C)은 전위 V0-Vth이며, 전위 Vcat에 발광 소자(14)의 임계값 전압 Vthe를 가산한 전위보다 낮기 때문에, 발광 소자(14)는 발광하지 않는다.

계속해서, 기간 t3에서는, 배선 GLa에 하이 레벨의 전위가 부여되고, 배선 GLb에 로우 레벨의 전위가 부여되고, 배선 GLc에 로우 레벨의 전위가 부여되고, 배선 GLd에 로우 레벨의 전위가 부여된다. 따라서, 도 16의 (A)에 도시한 바와 같이, 트랜지스터(19)가 온으로 되고, 트랜지스터(16t), 트랜지스터(17t) 및 트랜지스터(20)는 오프로 된다. 또한, 배선 CL에는 전위 Vcat가 부여되고, 배선 SL에는 화상 신호 Sig의 전위 Vdata가 부여된다.

배선 SL에 부여되는 전위 Vdata는, 트랜지스터(19)를 통해서 트랜지스터(15)의 게이트(노드 A)에 부여된다. 또한, 전위 Vdata는, 화상 신호 Sig가 갖는 화상 정보에 따라 그 높이가 다르다. 도 14에서는, 기간 t4에 있어서의 배선 SL에, 하이 레벨의 전위 Vdata(H)가 부여되는 경우와, 로우 레벨의 전위 Vdata(L)이 부여되는 경우의, 양쪽을 도시하고 있다.

또한, 도 11에 도시하는 화소(11)의, 기간 t3 종료 시에 있어서의 노드 C의 전위 V2에 대해서는, 도 3에 도시하는 화소(11)의, 기간 t4 종료 시에 있어서의 노드 C의 전위 V2와 마찬가지로, 트랜지스터(15)가 오프인 경우, 용량 소자(18)가 갖는 용량값 C1과, 발광 소자(14)가 갖는 용량값 C2의 비에 의해 결정된다. 그리고, 기간 t3에 있어서 트랜지스터(15)가 온인 경우에는, 노드 C에 전하가 유입되기 때문에, 기간 t3 종료 시에 있어서의 노드 C의 전위 V2는, 용량 소자(18)가 갖는 용량값 C1과, 발광 소자(14)가 갖는 용량값 C2의 비에 의해서만 정해지지 않고, 노드 C에 유입되는 전하량에 의해 그 값이 변화된다. 구체적으로, 기간 t3 종료 시에 있어서의 트랜지스터(15)의 게이트 전압 Vgs는, 상술한 수학식 1로 표현된다.

또한, 기간 t3 종료 시에 있어서의, 이상적인 게이트 전압 Vgs는 Vgs=Vdata-V0+Vth이다. 게이트 전압 Vgs가 상기 값을 갖고 있으면, 트랜지스터(15)의 임계값 전압 Vth에 변동이 발생하더라도, 이러한 변동은 트랜지스터(15)의 드레인 전류에 영향을 미치지 못하게 된다. 게이트 전압 Vgs를 이상적인 값에 가깝게 하기 위해서는, 수학식 1에서, C2/(C1+C2)을 1에 가깝게 하는 것이 바람직한 것을 알 수 있다. 즉, 발광 소자(14)의 용량값 C2가, 용량 소자(18)의 용량값 C1보다 충분히 크면, 게이트 전압 Vgs를 이상적인 값에 가깝게 할 수 있으므로, 바람직하다.

또한, 게이트 전압 Vgs를 이상적인 값에 가깝게 하기 위해서는, 수학식 1에서, Q1/(C1+C2)를 작게 하는 것이 바람직한 것을 알 수 있다. 즉, 노드 C에 유입되는 전하량 Q1을 작게 하는 것이, 게이트 전압 Vgs를 이상적인 값에 가깝게 하는 데 있어서, 바람직하다. 따라서, 전하량 Q1을 작게 하기 위해서 기간 t3은 가능한 한 짧은 쪽이 좋다.

또한, 도 11에 도시한 화소(11)를 갖는 발광 장치에서는, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽과, 트랜지스터(15)의 게이트가 전기적으로 분리되어 있으므로, 각각의 전위를 개별로 제어할 수 있다. 따라서, 기간 t2에 있어서, 트랜지스터(15)의 소스 및 드레인 중 다른 쪽의 전위를, 트랜지스터(15)의 게이트 전위에, 임계값 전압 Vth를 가산한 전위보다 높은 값으로 설정할 수 있다. 그로 인해, 트랜지스터(15)가 노멀리 온인 경우에, 즉 임계값 전압 Vth가 마이너스의 값을 갖고 있는 경우에, 트랜지스터(15)에 있어서, 소스의 전위가 게이트의 전위 V0보다 높아질 때까지, 용량 소자(18)에 전하를 축적할 수 있다. 따라서, 본 발명의 일 형태에 따른 발광 장치에서는, 트랜지스터(15)가 노멀리 온이어도, 기간 t2에 있어서 용량(18)에 임계값 전압을 취득할 수 있고, 기간 t3에 있어서, 임계값 전압 Vth를 가미한 값이 되도록, 트랜지스터(15)의 게이트 전압 Vgs를 설정할 수 있다.

따라서, 본 발명의 일 형태에 따른 발광 장치에서는, 예를 들어 트랜지스터(15)의 반도체막에 산화물 반도체를 사용한 경우 등에, 트랜지스터(15)가 노멀리 온으로 되더라도, 표시 얼룩을 저감시킬 수 있어, 높은 화질의 표시를 행할 수 있다.

기간 t3에 있어서 설정된 게이트 전압 Vgs는, 용량 소자(18)에 있어서 유지된다.

계속해서, 기간 t4에서는, 배선 GLa에 로우 레벨의 전위가 부여되고, 배선 GLb에 하이 레벨의 전위가 부여되고, 배선 GLc에 로우 레벨의 전위가 부여되고, 배선 GLd에 로우 레벨의 전위가 부여된다. 따라서, 도 16의 (B)에 도시한 바와 같이, 트랜지스터(16t)가 온으로 되고, 트랜지스터(19), 트랜지스터(17t) 및 트랜지스터(20)가 오프로 된다. 트랜지스터(19)가 오프가 됨으로써, 트랜지스터(15)의 게이트에 있어서, 전위 Vdata가 유지된다. 또한, 배선 VL에는 전위 Vano가 부여되고, 배선 CL에는 전위 Vcat가 부여된다. 따라서, 발광 소자(14)에서는, 기간 t3에 있어서 정해진 휘도가 유지된다.

계속해서, 기간 t5에서는, 배선 GLa에 로우 레벨의 전위가 부여되고, 배선 GLb에 로우 레벨의 전위가 부여되고, 배선 GLc에 하이 레벨의 전위가 부여되고, 배선 GLd에 로우 레벨의 전위가 부여된다. 따라서, 도 17에 도시한 바와 같이, 트랜지스터(17t)가 온으로 되고, 트랜지스터(19), 트랜지스터(16t) 및 트랜지스터(20)가 오프로 된다. 또한, 배선 CL에는 전위 Vcat가 부여된다. 그리고, 배선 ML에는 전위 Vano가 부여되고, 게다가 모니터 회로에 접속된다.

상기 동작에 의해, 트랜지스터(17t)를 통해서, 트랜지스터(15)의 드레인 전류는, 발광 소자(14)에 공급된다. 게다가, 상기 드레인 전류는, 배선 ML을 통해서 모니터 회로에도 공급된다. 모니터 회로는, 배선 ML에 흐르는 드레인 전류를 사용해서, 그 드레인 전류의 값을 정보로서 포함하는 신호를 생성한다. 그리고, 본 발명의 일 형태에 따른 발광 장치에서는, 상기 신호를 사용해서, 화소(11)에 공급되는 화상 신호 Sig의 전위 Vdata의 값을 보정할 수 있다.

또한, 도 11에 도시하는 화소(11)를 갖는 발광 장치에서는, 기간 t4의 동작 후에 기간 t5의 동작을 항상 행할 필요는 없다. 예를 들어, 발광 장치에 있어서, 기간 t1 내지 기간 t4의 동작을 복수회 반복한 후에, 기간 t5의 동작을 행하도록 해도 된다. 또한, 1행의 화소(11)에 있어서 기간 t5의 동작을 행한 후, 최소의 계조값 0에 대응하는 화상 신호를, 그 동작을 행한 1행의 화소(11)에 기입함으로써, 발광 소자(14)를 비발광의 상태로 한 후, 다음 행의 화소(11)에 있어서, 기간 t5의 동작을 행하도록 해도 된다.

<모니터 회로의 구성예>

이어서, 모니터 회로(12)의 구성예를 도 18에 도시하였다. 도 18에 도시하는 모니터 회로(12)는 연산 증폭기(60)와, 용량 소자(61)와, 스위치(62)를 갖는다.

용량 소자(61)가 갖는 한 쌍의 전극 중 한쪽은, 연산 증폭기(60)의 반전 입력 단자 (-)에 접속되고, 용량 소자(61)가 갖는 한 쌍의 전극 중 다른 쪽은, 연산 증폭기(60)의 출력 단자에 접속되어 있다. 스위치(62)는 용량 소자(61)에 축적되어 있는 전하를 방출시키는 기능을 갖고 있으며, 구체적으로는 용량 소자(61)가 갖는 한 쌍의 전극간의 도통 상태를 제어하는 기능을 갖는다. 연산 증폭기(60)의 비반전 입력 단자 (+)는 배선(68)에 접속되어 있고, 배선(68)에는 전위 Vano 또는 전위 V1이 공급된다.

본 발명의 일 형태에서는, 내부 보정을 행하기 위해서, 화소(11)의 배선 ML에 전위 Vano 또는 전위 V1을 공급할 때에는, 모니터 회로(12)를 전압 폴로워(voltage follower)로서 기능시킨다. 구체적으로는, 스위치(62)를 온으로 함으로써, 배선(68)에 공급되는 전위 Vano 또는 전위 V1을, 모니터 회로(12)를 통해서, 배선 TER로부터 배선 ML에 공급할 수 있다.

또한, 외부 보정을 행하기 위해서, 화소(11)로부터 배선 ML을 통해서 전류를 추출할 때에는, 먼저 모니터 회로(12)를 전압 폴로워로서 기능시킴으로써, 배선 ML에 전위 Vano를 공급한 후, 모니터 회로(12)를 적분 회로로 해서 기능시킴으로써, 화소(11)로부터 추출한 전류를 전압으로 변환한다. 구체적으로는, 스위치(62)를 온으로 함으로써, 배선(68)에 공급된 전위 Vano를, 모니터 회로(12)를 통해서 배선 ML에 공급한 후, 스위치(62)를 오프로 한다. 스위치(62)가 오프인 상태에 있어서, 화소(11)로부터 배선 TER에 드레인 전류가 추출되면, 용량 소자(61)에 전하가 축적되어, 용량 소자(61)가 갖는 한 쌍의 전극 사이에 전압이 발생한다. 상기 전압은, 드레인 전류에 의해, 배선 TER에 추출된 전하의 총량에 비례하므로, 연산 증폭기(60)의 출력 단자에 접속된 배선 OUT에는, 소정의 기간 내에 있어서의 드레인 전류에 의한 전하의 총량에 대응한 전위가 부여되고, 그 전위가 드레인 전류의 값의 정보를 포함하는 신호로서, 화상 처리 회로에 공급된다.

또한, 도 3에 도시하는 화소(11)의 경우, 내부 보정을 행할 때, 도 7 및 도 8로 도시한 바와 같이, 화소(11)의 배선 ML에 공급하는 전위를, 전위 Vano와 전위 V1로 전환하고 있다. 상기 전위의 전환은, 모니터 회로(12)의 배선(68)에 공급되는 전위를 전위 Vano와 전위 V1로 전환함으로써 행할 수 있다.

또한, 전위 V1이 공급되는 배선과, 모니터 회로(12)의 배선 TER 중 어느 한쪽을 선택하고, 선택된 배선과 화소(11)의 배선 ML을 전기적으로 접속하는 기능을 갖는 선택 회로를, 발광 장치에 설치해도 된다. 상기 선택 회로를 발광 장치에 설치하는 경우, 모니터 회로(12)의 배선(68)에 전위 Vano를, 다른 전위로 전환하지 않고 공급해도 된다.

<화소부와 선택 회로의 접속 구성>

이어서, 도 2에 도시하는 화소부(24)와 선택 회로(64)의, 접속 구성의 일례에 대해서 설명한다. 도 19에, 화소부(24)와, 선택 회로(64)의 구성을 예시한다.

도 19에 도시하는 화소부(24)에는, 복수의 화소(11)와, GL1 내지 배선 GLy로 나타나는 복수의 배선 GL과, 배선 SL1 내지 배선 SLx로 나타나는 복수의 배선 SL과, 배선 ML1 내지 배선 MLx로 나타나는 복수의 배선 ML과, 배선 VL1 내지 배선 VLx로 나타나는 복수의 배선 VL이 설치되어 있다. GL1 내지 배선 GLy 각각은, 각 화소(11)에 포함되는 복수의 트랜지스터의 게이트에 각각 접속된, 복수의 배선에 상당한다. 예를 들어, 도 3에서 도시하는 화소(11)의 경우, 배선 GLa 내지 배선 GLc가, GL1 내지 배선 GLy 중 어느 하나에 상당한다. 또한, 예를 들어 도 11에서 도시하는 화소(11)의 경우, 배선 GLa 내지 배선 GLd가, GL1 내지 배선 GLy 중 어느 하나에 상당한다. 그리고, 복수의 화소(11)는 배선 GL 중 적어도 1개와, 배선 SL 중 적어도 1개와, 배선 ML 중 적어도 1개와, 배선 VL 중 적어도 1개에, 각각 접속되어 있다.

또한, 화소부(24)에 설치되는 배선의 종류 및 그 수는, 화소(11)의 구성, 수 및 배치에 의해 정할 수 있다. 구체적으로, 도 19에 도시하는 화소부(24)의 경우, x열×y행의 화소(11)가 매트릭스 형상으로 배치되어 있고, 배선 GL1 내지 배선 GLy, 배선 SL1 내지 배선 SLx, 배선 ML1 내지 배선 MLx, 배선 VL1 내지 배선 VLx가, 화소부(24) 내에 배치되어 있는 경우를 예시하고 있다.

그리고, 선택 회로(64)는 배선 ML1 내지 배선 MLx와, 모니터 회로(도시하지 않음)의 배선 TER 사이의 도통 상태를 제어하는 기능을 갖는다. 구체적으로, 선택 회로(64)는 전위 V1이 공급되는 배선(67)과 1의 배선 ML 사이의 도통 상태를 제어하는 스위치(65)와, 상기 1의 배선 ML과 배선 TER 사이의 도통 상태를 제어하는 스위치(66)를 갖는다.

<발광 장치의 단면 구조>

도 20에, 본 발명의 일 형태에 따른 발광 장치의, 화소부의 단면 구조를 일례로서 나타낸다. 또한, 도 20에서는, 도 3에 도시하는 화소(11)가 갖는 트랜지스터(15), 용량 소자(18) 및 발광 소자(14)의 단면 구조를 예시하고 있다.

구체적으로, 도 20에 도시하는 발광 장치는, 기판(400) 위에 트랜지스터(15)와, 용량 소자(18)를 갖는다. 트랜지스터(15)는 게이트로서 기능하는 도전막(401)과, 도전막(401) 위의 절연막(402)과, 절연막(402)을 사이에 두고 도전막(401)과 중첩되는 반도체막(403)과, 반도체막(403)에 전기적으로 접속된 소스 또는 드레인으로서 기능하는 도전막(404) 및 도전막(405)을 갖는다.

용량 소자(18)는 전극으로서 기능하는 도전막(401)과, 도전막(401) 위의 절연막(402)과, 절연막(402)을 사이에 두고 도전막(401)과 중첩되고, 게다가 전극으로서 기능하는 도전막(404)을 갖는다.

절연막(402)으로서는, 산화알루미늄, 산화마그네슘, 산화규소, 산화질화규소, 질화산화규소, 질화규소, 산화갈륨, 산화게르마늄, 산화이트륨, 산화지르코늄, 산화란탄, 산화네오디뮴, 산화하프늄 및 산화탄탈을 1종 이상 포함하는 절연막을, 단층으로 또는 적층시켜서 사용하면 된다. 또한, 본 명세서 중에 있어서, 산화질화물은, 그 조성으로서, 질소보다 산소의 함유량이 많은 재료를 가리키고, 질화산화물은, 그 조성으로서, 산소보다 질소의 함유량이 많은 재료를 가리킨다.

또한, 반도체막(403), 도전막(404) 및 도전막(405) 위에는 절연막(411)이 설치되어 있다. 반도체막(403)으로서 산화물 반도체를 사용하는 경우, 절연막(411)은 반도체막(403)에 산소를 공급시키는 것이 가능한 재료를 사용하는 것이 바람직하다. 상기 재료를 절연막(411)에 사용함으로써, 절연막(411)에 포함되는 산소를 반도체막(403)에 이동시키는 것이 가능하고, 반도체막(403)의 산소 결손량을 저감시킬 수 있다. 절연막(411)에 포함되는 산소의 반도체막(403)으로의 이동은, 절연막(411)을 형성한 후에, 가열 처리를 행함으로써 효율적으로 행할 수 있다.

절연막(411) 위에는 절연막(420)이 설치되어 있고, 절연막(420) 위에는 도전막(424)이 설치되어 있다. 도전막(424)은 절연막(411) 및 절연막(420)에 형성된 개구부에 있어서, 도전막(404)에 접속되어 있다.

절연막(420) 및 도전막(424) 위에는 절연막(425)이 설치되어 있다. 절연막(425)은 도전막(424)과 중첩되는 위치에 개구부를 갖는다. 또한, 절연막(425) 위에 있어서, 절연막(425)의 개구부와는 다른 위치에, 절연막(426)이 설치되어 있다. 그리고, 절연막(425) 및 절연막(426) 위에는, EL층(427) 및 도전막(428)이, 순서대로 적층하도록 설치되어 있다. 도전막(424) 및 도전막(428)이 EL층(427)을 사이에 두고 중첩되는 부분이, 발광 소자(14)로서 기능한다. 그리고, 도전막(424) 및 도전막(428)은 한쪽이 양극, 다른 쪽이 음극으로서 기능한다.

또한, 발광 장치는, 발광 소자(14)를 사이에 두고 기판(400)과 대치하는, 기판(430)을 갖는다. 기판(430) 위, 즉, 발광 소자(14)에 가까운 기판(430)측 면 위에는, 광을 차폐하는 기능을 갖는 차폐막(431)이 설치되어 있다. 그리고, 차폐막(431)은 발광 소자(14)와 중첩되는 영역에 개구부를 갖고 있다. 발광 소자(14)에 중첩되는 개구부에 있어서, 기판(430) 위에는 특정한 파장 범위의 가시광을 투과하는 착색층(432)이 설치되어 있다.

<트랜지스터의 구조>

이어서, 산화물 반도체막에 채널 형성 영역을 갖는 트랜지스터(70)의 구성을, 일례로서 나타낸다.

도 21의 (A)에 도시하는 트랜지스터(70)는, 게이트로서 기능하는 도전막(80)과, 도전막(80) 위의 절연막(81)과, 절연막(81)을 사이에 두고 도전막(80)과 중첩되는 산화물 반도체막(82)과, 산화물 반도체막(82)에 접속된, 소스 및 드레인으로서 기능하는 도전막(83) 및 도전막(84)을 갖는다. 또한, 도 21의 (A)에 도시하는 트랜지스터(70)는 산화물 반도체막(82), 도전막(83) 및 도전막(84) 위에, 순서대로 적층된 절연막(85) 내지 절연막(87)을 갖는다.

또한, 도 21의 (A)에서는, 산화물 반도체막(82), 도전막(83) 및 도전막(84) 위에, 순서대로 적층된 절연막(85) 내지 절연막(87)이 설치되어 있는 경우를 예시하고 있지만, 산화물 반도체막(82), 도전막(83) 및 도전막(84) 위에 설치되는 절연막은, 1층이어도 되고, 3 이상의 복수층이어도 된다.

절연막(86)은 화학양론적 조성 이상의 산소가 포함되어 있고, 가열에 의해 상기 산소의 일부를 산화물 반도체막(82)에 공급하는 기능을 갖는 절연막인 것이 바람직하다. 또한, 절연막(86)은 결함이 적은 것이 바람직하고, 대표적으로는, ESR 측정에 의해 얻어지는, 실리콘의 댕글링 본드로부터 유래되는 g=2.001을 갖는 스핀 밀도가 1×1018spins/㎤ 이하인 것이 바람직하다. 단, 절연막(86)을 산화물 반도체막(82) 위에 직접 설치하면, 절연막(86)의 형성 시에 산화물 반도체막(82)에 대미지가 부여되는 경우, 도 21의 (A)에 도시한 바와 같이, 절연막(85)을 산화물 반도체막(82)과 절연막(86) 사이에 설치하면 된다. 절연막(85)은 그 형성 시에 산화물 반도체막(82)에 부여하는 대미지가 절연막(86)의 경우보다 작고, 게다가 산소를 투과하는 기능을 갖는 절연막인 것이 바람직하다. 단, 산화물 반도체막(82)에 부여되는 대미지를 작게 억제하면서, 산화물 반도체막(82) 위에 절연막(86)을 직접 형성할 수 있는 것이라면, 절연막(85)은 반드시 설치하지 않아도 된다.

절연막(85)은 결함이 적은 것이 바람직하며, 대표적으로는, ESR 측정에 의해 얻어지는, 실리콘의 댕글링 본드로부터 유래되는 g=2.001을 갖는 스핀 밀도가 3×1017spins/㎤ 이하인 것이 바람직하다. 이것은, 절연막(85)에 포함되는 결함 밀도가 많으면, 그 결함에 산소가 결합되어 버려, 절연막(85)에 있어서의 산소의 투과량이 감소되어 버리기 때문이다.

또한, 절연막(85)과 산화물 반도체막(82)의 계면에 결함이 적은 것이 바람직하고, 대표적으로는, 자장의 방향을 막면(film surface)에 평행하게 인가한 ESR 측정에 의해, 산화물 반도체막(82)에 사용되는 산화물 반도체 중 산소 결손으로부터 유래되는 g값이 1.89 이상 1.96 이하인 스핀 밀도가 1×1017spins/㎤ 이하, 나아가 검출 하한 이하인 것이 바람직하다.

또한, 절연막(87)은 산소, 수소, 물의 확산을 방지하는 블로킹 효과를 갖는 것이 바람직하다. 또는, 절연막(87)은 수소, 물의 확산을 방지하는 블로킹 효과를 갖는 것이 바람직하다.

절연막은, 밀도가 높아 치밀할수록, 또한 댕글링 본드가 적어서 화학적으로 안정될수록, 더 높은 블로킹 효과를 나타낸다. 산소, 수소, 물의 확산을 방지하는 블로킹 효과를 나타내는 절연막은, 예를 들어 산화알루미늄, 산화질화알루미늄, 산화갈륨, 산화질화갈륨, 산화이트륨, 산화질화이트륨, 산화하프늄, 산화질화하프늄 등을 사용해서 형성할 수 있다. 수소, 물의 확산을 방지하는 블로킹 효과를 나타내는 절연막은, 예를 들어 질화실리콘, 질화산화실리콘 등을 사용할 수 있다.

절연막(87)이 물, 수소 등의 확산을 방지하는 블로킹 효과를 갖는 경우, 패널 내의 수지나, 패널의 외부에 존재하는 물, 수소 등의 불순물이, 산화물 반도체막(82)에 침입하는 것을 방지할 수 있다. 산화물 반도체막(82)에 산화물 반도체를 사용하는 경우, 산화물 반도체에 침입한 물 또는 수소의 일부는 전자 공여체(도너)로 되기 때문에, 상기 블로킹 효과를 갖는 절연막(87)을 사용함으로써 트랜지스터(70)의 임계값 전압이 도너의 생성에 의해 시프트하는 것을 방지할 수 있다.

또한, 산화물 반도체막(82)에 산화물 반도체를 사용하는 경우, 절연막(87)이 산소의 확산을 방지하는 블로킹 효과를 가짐으로써, 산화물 반도체로부터의 산소가 외부로 확산되는 것을 방지할 수 있다. 따라서, 산화물 반도체 중에 있어서, 도너로 되는 산소 결손이 저감되므로, 트랜지스터(70)의 임계값 전압이 도너의 생성에 의해 시프트하는 것을 방지할 수 있다.

또한, 도 21의 (A)에서는, 산화물 반도체막(82)이 3층의 적층된 산화물 반도체막으로 구성되어 있는 경우를, 예시하고 있다. 구체적으로, 도 21의 (A)에 도시하는 트랜지스터(70)에서는, 산화물 반도체막(82)으로서, 산화물 반도체막(82a) 내지 산화물 반도체막(82c)이 절연막(81)측으로부터 순서대로 적층되어 있다. 트랜지스터(70)의 산화물 반도체막(82)은 적층된 복수의 산화물 반도체막으로 구성되어 있는 것에 한정되는 것은 아니며, 단막의 산화물 반도체막으로 구성되어 있어도 된다.

그리고, 산화물 반도체막(82a) 및 산화물 반도체막(82c)은 산화물 반도체막(82b)을 구성하는 금속 원소 중 적어도 1개를, 그 구성 요소에 포함하고, 전도대 하단부의 에너지가 산화물 반도체막(82b)보다 0.05eV 이상, 0.07eV 이상, 0.1eV 이상 또는 0.15eV 이상, 또한 2eV 이하, 1eV 이하, 0.5eV 이하 또는 0.4eV 이하, 진공 준위에 가까운 산화물막이다. 또한, 산화물 반도체막(82b)은 적어도 인듐을 포함하면, 캐리어 이동도가 높아지기 때문에 바람직하다.

또한, 도 21의 (B)에 도시한 바와 같이, 트랜지스터(70)는 산화물 반도체막(82c)이 도전막(83) 및 도전막(84)의 상층에서 절연막(85)과 중첩되도록 설치되어 있는 구성을 가져도 된다.

또한, 전자 공여체(도너)로 되는 수분 또는 수소 등의 불순물이 저감되고, 게다가 산소 결손이 저감됨으로써 고순도화된 산화물 반도체(purified Oxide Semiconductor)는 캐리어 발생원이 적기 때문에, i형(진성 반도체) 또는 i형에 한없이 가깝게 할 수 있다. 그로 인해, 고순도화된 산화물 반도체막에 채널 형성 영역을 갖는 트랜지스터는, 오프 전류가 현저하게 작아, 신뢰성이 높다. 그리고, 상기 산화물 반도체막에 채널 형성 영역이 형성되는 트랜지스터는, 임계값 전압이 플러스로 되는 전기적 특성(노멀리 오프 특성이라고도 함)이 되기 쉽다.

구체적으로, 고순도화된 산화물 반도체막에 채널 형성 영역을 갖는 트랜지스터의 오프 전류가 작은 것은, 다양한 실험에 의해 증명할 수 있다. 예를 들어, 채널 폭이 1×106㎛로 채널 길이가 10㎛인 소자에서도, 소스 전극과 드레인 전극간의 전압(드레인 전압)이 1V 내지 10V인 범위에 있어서, 오프 전류가, 반도체 파라미터 애널라이저의 측정 한계 이하, 즉 1×10-13A 이하라고 하는 특성을 얻을 수 있다. 이 경우, 트랜지스터의 채널 폭으로 규격화된 오프 전류는, 100zA/㎛ 이하인 것을 알 수 있다. 또한, 용량 소자와 트랜지스터를 접속하고, 용량 소자에 유입 또는 용량 소자로부터 유출되는 전하를 그 트랜지스터로 제어하는 회로를 사용해서, 오프 전류의 측정을 행하였다. 상기 측정에서는, 고순도화된 산화물 반도체막을 상기 트랜지스터의 채널 형성 영역에 사용하여, 용량 소자의 단위 시간당 전하량의 추이로부터 그 트랜지스터의 오프 전류를 측정하였다. 그 결과, 트랜지스터의 소스 전극과 드레인 전극간의 전압이 3V인 경우에, 수십 yA/㎛라고 하는, 더 작은 오프 전류가 얻어지는 것을 알 수 있었다. 따라서, 고순도화된 산화물 반도체막을 채널 형성 영역에 사용한 트랜지스터는, 오프 전류가, 결정성을 갖는 실리콘을 사용한 트랜지스터에 비교해서 현저하게 작다.

또한, 반도체막으로서 산화물 반도체막을 사용하는 경우, 산화물 반도체로서는, 적어도 인듐(In) 또는 아연(Zn)을 포함하는 것이 바람직하다. 또한, 상기 산화물을 사용한 트랜지스터의 전기적 특성의 변동을 저감시키기 위한 스테빌라이저로서, 그들에 더하여 갈륨(Ga)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 주석(Sn)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 하프늄(Hf)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 알루미늄(Al)을 갖는 것이 바람직하다. 또한, 스테빌라이저로서 지르코늄(Zr)을 포함하는 것이 바람직하다.

산화물 반도체 중에서도 In-Ga-Zn계 산화물, In-Sn-Zn계 산화물 등은, 탄화실리콘, 질화갈륨 또는 산화갈륨과는 달리, 스퍼터링법이나 습식법에 의해 전기적 특성이 우수한 트랜지스터를 제작하는 것이 가능하고, 양산성이 우수하다는 이점이 있다. 또한, 탄화실리콘, 질화갈륨 또는 산화갈륨과는 달리, 상기 In-Ga-Zn계 산화물은, 유리 기판 위에 전기적 특성이 우수한 트랜지스터를 제작하는 것이 가능하다. 또한, 기판의 대형화에도 대응이 가능하다.

또한, 다른 스테빌라이저로서, 란타노이드인, 란탄(La), 세륨(Ce), 프라세오디뮴(Pr), 네오디뮴(Nd), 사마륨(Sm), 유로퓸(Eu), 가돌리늄(Gd), 테르븀(Tb), 디스프로슘(Dy), 홀뮴(Ho), 에르븀(Er), 툴륨(Tm), 이테르븀(Yb), 루테튬(Lu) 중 어느 1종 또는 복수종을 포함하고 있어도 된다.

예를 들어, 산화물 반도체로서, 산화인듐, 산화갈륨, 산화주석, 산화아연, In-Zn계 산화물, Sn-Zn계 산화물, Al-Zn계 산화물, Zn-Mg계 산화물, Sn-Mg계 산화물, In-Mg계 산화물, In-Ga계 산화물, In-Ga-Zn계 산화물(IGZO로도 표기함), In-Al-Zn계 산화물, In-Sn-Zn계 산화물, Sn-Ga-Zn계 산화물, Al-Ga-Zn계 산화물, Sn-Al-Zn계 산화물, In-Hf-Zn계 산화물, In-La-Zn계 산화물, In-Pr-Zn계 산화물, In-Nd-Zn계 산화물, In-Ce-Zn계 산화물, In-Sm-Zn계 산화물, In-Eu-Zn계 산화물, In-Gd-Zn계 산화물, In-Tb-Zn계 산화물, In-Dy-Zn계 산화물, In-Ho-Zn계 산화물, In-Er-Zn계 산화물, In-Tm-Zn계 산화물, In-Yb-Zn계 산화물, In-Lu-Zn계 산화물, In-Sn-Ga-Zn계 산화물, In-Hf-Ga-Zn계 산화물, In-Al-Ga-Zn계 산화물, In-Sn-Al-Zn계 산화물, In-Sn-Hf-Zn계 산화물, In-Hf-Al-Zn계 산화물을 사용할 수 있다.

또한, 예를 들어 In-Ga-Zn계 산화물이란, In과 Ga와 Zn을 포함하는 산화물이라고 하는 의미이며, In과 Ga와 Zn의 비율은 상관 없다. 또한, In과 Ga와 Zn 이외의 금속 원소를 포함하고 있어도 된다. In-Ga-Zn계 산화물은, 무전계 시의 저항이 충분히 높고 오프 전류를 충분히 작게 하는 것이 가능하고 또한 이동도도 높다.

예를 들어, In-Sn-Zn계 산화물에서는 비교적 용이하게 높은 이동도가 얻어진다. 그러나, In-Ga-Zn계 산화물에서도, 벌크 내 결함 밀도를 저감시킴으로써 이동도를 높일 수 있다.

이하에서는, 산화물 반도체막의 구조에 대해서 설명한다.

산화물 반도체막은, 단결정 산화물 반도체막과 비단결정 산화물 반도체막으로 크게 구별된다. 비단결정 산화물 반도체막이란, 비정질 산화물 반도체막, 미결정 산화물 반도체막, 다결정 산화물 반도체막, CAAC-OS막 등을 말한다.

비정질 산화물 반도체막은, 막 내에서의 원자 배열이 불규칙하며, 결정 성분을 갖지 않은 산화물 반도체막이다. 미소 영역에서도 결정부를 갖지 않고, 막 전체가 완전한 비정질 구조의 산화물 반도체막이 전형이다.

미결정 산화물 반도체막은, 예를 들어 1㎚ 이상 10㎚ 미만의 크기의 미결정(나노 결정이라고도 함)을 포함한다. 따라서, 미결정 산화물 반도체막은, 비정질 산화물 반도체막보다 원자 배열의 규칙성이 높다. 그로 인해, 미결정 산화물 반도체막은, 비정질 산화물 반도체막보다 결함 준위 밀도가 낮다는 특징이 있다.

CAAC-OS막은, 복수의 결정부를 갖는 산화물 반도체막의 하나이며, 대부분의 결정부는, 1변이 100㎚ 미만인 입방체 내에 수용되는 크기이다. 따라서, CAAC-OS막에 포함되는 결정부는, 1변이 10㎚ 미만, 5㎚ 미만 또는 3㎚ 미만인 입방체 내에 수용되는 크기의 경우도 포함된다. CAAC-OS막은 미결정 산화물 반도체막보다 결함 준위 밀도가 낮다는 특징이 있다. CAAC-OS막을 투과형 전자 현미경(TEM: Transmission Electron Microscope)에 의해 관찰하면, 결정부끼리가 명확한 경계, 즉 결정립계(그레인 바운더리라고도 함)를 확인할 수 없다. 그로 인해, CAAC-OS막은, 결정립계에 기인하는 전자 이동도의 저하가 일어나기 어렵다고 할 수 있다.

CAAC-OS막을, 시료면과 대략 평행한 방향으로부터 TEM에 의해 관찰(단면 TEM 관찰)하면, 결정부에 있어서, 금속 원자가 층상으로 배열되어 있는 것을 확인할 수 있다. 금속 원자의 각 층은, CAAC-OS막의 막을 형성하는 면(피형성면이라고도 함) 또는 상면의 요철을 반영한 형상이며, CAAC-OS막의 피형성면 또는 상면과 평행하게 배열한다.

본 명세서에 있어서, 「평행」이란, 두개의 직선이 -10° 이상 10° 이하인 각도로 배치되어 있는 상태를 말한다. 따라서, -5° 이상 5° 이하인 경우도 포함된다. 또한, 「수직」이란, 두개의 직선이 80° 이상 100° 이하인 각도로 배치되어 있는 상태를 말한다. 따라서, 85° 이상 95° 이하인 경우도 포함된다.

한편, CAAC-OS막을, 시료면과 개략 수직인 방향으로부터 TEM에 의해 관찰(평면 TEM 관찰)하면, 결정부에 있어서, 금속 원자가 삼각 형상 또는 육각형 형상으로 배열되어 있는 것을 확인할 수 있다. 그러나, 다른 결정부 사이에서, 금속 원자의 배열에 규칙성은 보이지 않는다.

단면 TEM 관찰 및 평면 TEM 관찰보다, CAAC-OS막의 결정부는 배향성을 갖고 있는 것을 알 수 있다.

CAAC-OS막에 대하여 X선 회절(XRD: X-Ray Diffraction) 장치를 사용해서 구조 해석을 행하면, 예를 들어 InGaZnO4의 결정을 갖는 CAAC-OS막의 out-of-plane법에 의한 해석에서는, 회절각(2θ)이 31° 근방에 피크가 나타나는 경우가 있다. 이 피크는, InGaZnO4의 결정의 (009)면에 귀속되는 점에서, CAAC-OS막의 결정이 c축 배향성을 갖고, c축이 피형성면 또는 상면에 개략 수직인 방향을 향하고 있는 것을 확인할 수 있다.

한편, CAAC-OS막에 대하여 c축에 개략 수직인 방향으로부터 X선을 입사시키는 in-plane법에 의한 해석에서는, 2θ가 56° 근방에 피크가 나타나는 경우가 있다. 이 피크는, InGaZnO4의 결정의 (110)면에 귀속된다. InGaZnO4의 단결정 산화물 반도체막이면, 2θ를 56° 근방에 고정하고, 시료면의 법선 벡터를 축(φ축)으로서 시료를 회전시키면서 분석(φ 스캔)을 행하면, (110)면과 등가인 결정면에 귀속되는 피크가 6개 관찰된다. 이에 반해, CAAC-OS막인 경우에는, 2θ를 56° 근방에 고정해서 φ 스캔한 경우에도, 명료한 피크가 나타나지 않는다.

이상으로부터, CAAC-OS막에서는, 다른 결정부간에서는 a축 및 b축의 배향은 불규칙하지만, c축 배향성을 가지면서, 또한 c축이 피형성면 또는 상면의 법선 벡터에 평행한 방향을 향하고 있는 것을 알 수 있다. 따라서, 상술한 단면 TEM 관찰로 확인된 층상으로 배열한 금속 원자의 각 층은, 결정의 ab면에 평행한 면이다.

또한, 결정부는, CAAC-OS막을 성막했을 때 또는 가열 처리 등의 결정화 처리를 행했을 때 형성된다. 상술한 바와 같이, 결정의 c축은, CAAC-OS막의 피형성면 또는 상면의 법선 벡터에 평행한 방향으로 배향한다. 따라서, 예를 들어 CAAC-OS막의 형상을 에칭 등에 의해 변화시킨 경우, 결정의 c축이 CAAC-OS막의 피형성면 또는 상면의 법선 벡터와 평행해지지 않는 경우도 있다.

또한, CAAC-OS막 중 결정화도가 균일하지 않아도 된다. 예를 들어, CAAC-OS막의 결정부가, CAAC-OS막의 상면 근방으로부터의 결정 성장에 의해 형성되는 경우, 상면 근방의 영역은, 피형성면 근방의 영역보다 결정화도가 높아지는 경우가 있다. 또한, CAAC-OS막에 불순물을 첨가하는 경우, 불순물이 첨가된 영역의 결정화도가 변화되고, 부분적으로 결정화도가 다른 영역이 형성되는 경우도 있다.

또한, InGaZnO4의 결정을 갖는 CAAC-OS막의 out-of-plane법에 의한 해석에서는, 2θ가 31° 근방인 피크 외에, 2θ가 36° 근방에도 피크가 나타나는 경우가 있다. 2θ가 36° 근방인 피크는, CAAC-OS막 중 일부에, c축 배향성을 갖지 않은 결정이 포함되는 것을 나타내고 있다. CAAC-OS막은 2θ가 31° 근방에 피크를 나타내고, 2θ가 36° 근방에 피크를 나타내지 않는 것이 바람직하다.

CAAC-OS막을 사용한 트랜지스터는, 가시광이나 자외광의 조사에 의한 전기적 특성의 변동이 작다. 따라서, 상기 트랜지스터는 신뢰성이 높다.

또한, 산화물 반도체막은, 예를 들어 비정질 산화물 반도체막, 미결정 산화물 반도체막, CAAC-OS막 중, 2종 이상을 갖는 적층막이어도 된다.

또한, CAAC-OS막을 성막하기 위해서, 이하의 조건을 적용하는 것이 바람직하다.

성막 시의 불순물 혼입을 저감시킴으로써, 불순물에 의해 결정 상태가 무너지는 것을 억제할 수 있다. 예를 들어, 처리실 내에 존재하는 불순물 농도(수소, 물, 이산화탄소 및 질소 등)를 저감시키면 된다. 또한, 성막 가스 중 불순물 농도를 저감시키면 된다. 구체적으로는, 노점이 -80℃ 이하, 바람직하게는 -100℃ 이하인 성막 가스를 사용한다.

또한, 성막 시의 기판 가열 온도를 높임으로써, 기판 도달 후에 스퍼터링 입자의 마이그레이션(migration)이 일어난다. 구체적으로는, 기판 가열 온도를 100℃ 이상 740℃ 이하, 바람직하게는 200℃ 이상 500℃ 이하로 해서 성막한다. 성막 시의 기판 가열 온도를 높임으로써, 평판 형상의 스퍼터링 입자가 기판에 도달한 경우, 기판 위에서 마이그레이션이 일어나, 스퍼터링 입자가 평평한 면이 기판에 부착된다.

또한, 성막 가스 중 산소 비율을 높이고, 전력을 최적화함으로써 성막 시의 플라즈마 대미지를 경감하면 바람직하다. 성막 가스 중 산소 비율은, 30체적% 이상, 바람직하게는 100체적%로 한다.

타깃의 일례로서, In-Ga-Zn계 산화물 타깃에 대해서 이하에 나타내었다.

InOX 분말, GaOY 분말 및 ZnOZ 분말을 소정의 mol수비로 혼합하고, 가압 처리 후, 1000℃ 이상 1500℃ 이하의 온도로 가열 처리를 함으로써 다결정인 In-Ga-Zn계 산화물 타깃으로 한다. 또한, X, Y 및 Z는 임의의 양수이다. 여기서, 소정의 mol수비는, 예를 들어 InOX 분말, GaOY 분말 및 ZnOZ 분말이, 2:2:1, 8:4:3, 3:1:1, 1:1:1, 4:2:3, 1:4:4 또는 3:1:2이다. 또한, 분말의 종류, 및 그 혼합하는 mol수비는, 제작하는 타깃에 따라 적절히 변경하면 된다.

또한, 알칼리 금속은 산화물 반도체를 구성하는 원소가 아니기 때문에, 불순물이다. 알칼리 토금속도, 산화물 반도체를 구성하는 원소가 아닌 경우에 있어서, 불순물로 된다. 특히, 알칼리 금속 중 Na는, 산화물 반도체막에 접하는 절연막이 산화물인 경우, 그 절연막 내로 확산되어 Na+로 된다. 또한, Na는 산화물 반도체막 내에서, 산화물 반도체를 구성하는 금속과 산소의 결합을 분단하거나, 또는 그 결합 사이로 들어간다. 그 결과, 예를 들어 임계값 전압이 마이너스 방향으로 시프트하는 것에 의한 노멀리온화, 이동도의 저하 등의, 트랜지스터의 전기적 특성의 열화가 일어나고, 더하여, 특성의 변동도 발생한다. 구체적으로, 2차 이온 질량 분석법에 의한 Na 농도의 측정값은, 5×1016/㎤ 이하, 바람직하게는 1×1016/㎤ 이하, 더욱 바람직하게는 1×1015/㎤ 이하로 하면 된다. 마찬가지로, Li 농도의 측정값은, 5×1015/㎤ 이하, 바람직하게는 1×1015/㎤ 이하로 하면 된다. 마찬가지로, K 농도의 측정값은, 5×1015/㎤ 이하, 바람직하게는 1×1015/㎤ 이하로 하면 된다.

또한, 인듐을 포함하는 금속 산화물이 사용되고 있는 경우에, 산소와의 결합에너지가 인듐보다 큰 실리콘이나 탄소가, 인듐과 산소의 결합을 절단하고, 산소 결손을 형성하는 경우가 있다. 그로 인해, 실리콘이나 탄소가 산화물 반도체막에 혼입되어 있으면, 알칼리 금속이나 알칼리 토금속의 경우와 마찬가지로, 트랜지스터의 전기적 특성의 열화가 일어나기 쉽다. 따라서, 산화물 반도체막 내에서의 실리콘이나 탄소의 농도는 낮은 것이 바람직하다. 구체적으로, 2차 이온 질량 분석법에 의한 C 농도의 측정값 또는 Si 농도의 측정값은, 1×1018/㎤ 이하로 하면 된다. 상기 구성에 의해, 트랜지스터의 전기적 특성의 열화를 방지할 수 있으며, 반도체 장치의 신뢰성을 높일 수 있다.

또한, 소스 전극 및 드레인 전극에 사용되는 도전성 재료에 따라서는, 소스 전극 및 드레인 전극 중 금속이, 산화물 반도체막으로부터 산소를 인발(引拔)하는 경우가 있다. 이 경우, 산화물 반도체막 중, 소스 전극 및 드레인 전극에 접하는 영역이, 산소 결손의 형성에 의해 n형화된다.

n형화된 영역은, 소스 영역 또는 드레인 영역으로서 기능하기 때문에, 산화물 반도체막과 소스 전극 및 드레인 전극 사이에 있어서의 콘택트 저항을 낮출 수 있다. 따라서, n형화된 영역이 형성됨으로써, 트랜지스터의 이동도 및 온 전류를 높일 수 있고, 그에 의해, 트랜지스터를 사용한 반도체 장치의 고속 동작을 실현할 수 있다.

또한, 소스 전극 및 드레인 전극 중 금속에 의한 산소의 인발은, 소스 전극 및 드레인 전극을 스퍼터링법 등에 의해 형성할 때에 일어날 수 있고, 소스 전극 및 드레인 전극을 형성한 후에 행해지는 가열 처리에 의해서도 일어날 수 있다.

또한, n형화되는 영역은, 산소와 결합되기 쉬운 도전성 재료를 소스 전극 및 드레인 전극에 사용함으로써, 보다 형성되기 쉬워진다. 상기 도전성 재료로서는, 예를 들어 Al, Cr, Cu, Ta, Ti, Mo, W 등을 들 수 있다.

또한, 산화물 반도체막은, 단수의 금속 산화물막으로 구성되어 있는 것에 한정되는 것은 아니며, 적층된 복수의 금속 산화물막으로 구성되어 있어도 된다. 예를 들어, 제1 내지 제3 금속 산화물막이 순서대로 적층되어 있는 반도체막의 경우, 제1 금속 산화물막 및 제3 금속 산화물막은, 제2 금속 산화물막을 구성하는 금속 원소 중 적어도 1개를, 그 구성 요소에 포함하고, 전도대 하단부의 에너지가 제2 금속 산화물막보다 0.05eV 이상, 0.07eV 이상, 0.1eV 이상 또는 0.15eV 이상, 또한 2eV 이하, 1eV 이하, 0.5eV 이하 또는 0.4eV 이하, 진공 준위에 가까운 산화물막이다. 또한, 제2 금속 산화물막은, 적어도 인듐을 포함하면, 캐리어 이동도가 높아지기 때문에 바람직하다.

상기 구성의 반도체막을 트랜지스터가 갖는 경우, 게이트 전극에 전압을 인가함으로써, 반도체막에 전계가 가해지면, 반도체막 내에, 전도대 하단부의 에너지가 작은 제2 금속 산화물막에 채널 영역이 형성된다. 즉, 제2 금속 산화물막과 게이트 절연막 사이에 제3 금속 산화물막이 설치되어 있는 것에 의해, 게이트 절연막과 이격되어 있는 제2 금속 산화물막에, 채널 영역을 형성할 수 있다.

또한, 제3 금속 산화물막은, 제2 금속 산화물막을 구성하는 금속 원소 중 적어도 1개를 그 구성 요소에 포함하기 때문에, 제2 금속 산화물막과 제3 금속 산화물막의 계면에서는, 계면 산란이 일어나기 어렵다. 따라서, 상기 계면에 있어서 캐리어의 움직임이 저해되기 어렵기 때문에, 트랜지스터의 전계 효과 이동도가 높아진다.

또한, 제2 금속 산화물막과 제1 금속 산화물막의 계면에 계면 준위가 형성되면, 계면 근방의 영역에도 채널 영역이 형성되기 때문에, 트랜지스터의 임계값 전압이 변동되어 버린다. 그러나, 제1 금속 산화물막은, 제2 금속 산화물막을 구성하는 금속 원소 중 적어도 1개를 그 구성 요소에 포함하기 때문에, 제2 금속 산화물막과 제1 금속 산화물막의 계면에는, 계면 준위가 형성되기 어렵다. 따라서, 상기 구성에 의해, 트랜지스터의 임계값 전압 등의 전기적 특성의 변동을 저감시킬 수 있다.

또한, 금속 산화물막 사이에 불순물이 존재함으로써, 각 막의 계면에 캐리어의 흐름을 저해하는 계면 준위가 형성되는 일이 없도록, 복수의 산화물 반도체막을 적층시키는 것이 바람직하다. 적층된 금속 산화물막의 막 사이에 불순물이 존재하고 있으면, 금속 산화물막들 사이의 전도대 하단부의 에너지 연속성이 상실되어, 계면 근방에 있어서, 캐리어가 트랩되거나, 또는 재결합에 의해 소멸되어 버리기 때문이다. 막들 사이의 불순물을 저감시킴으로써, 주성분인 1의 금속을 적어도 모두에 갖는 복수의 금속 산화물막을, 단순히 적층시키기보다, 연속 접합(여기서는 특히 전도대 하단부의 에너지가 각 막 사이에서 연속적으로 변화되는 U자형의 웰 구조를 갖고 있는 상태)이 형성되기 쉬워진다.

연속 접합을 형성하기 위해서는, 로드 로크실(load lock chamber)을 구비한 멀티 챔버 방식의 성막 장치(스퍼터링 장치)를 사용해서 각 막을 대기에 접촉시키지 않고 연속해서 적층하는 것이 필요해진다. 스퍼터링 장치에 있어서의 각 챔버는, 산화물 반도체에 있어서 불순물로 되는 물 등을 가능한 한 제거하기 위해 크라이오 펌프와 같은 흡착식 진공 배기 펌프를 사용해서 고진공 배기(5×10-7㎩ 내지 1×10-4㎩ 정도까지)하는 것이 바람직하다. 또는, 터보 분자 펌프와 콜드 트랩을 조합해서 배기계로부터 챔버 내에 기체가 역류하지 않도록 해 두는 것이 바람직하다.

고순도의 진성의 산화물 반도체를 얻기 위해서는, 각 챔버 내를 고진공 배기할 뿐만 아니라, 스퍼터링에 사용하는 가스의 고순도화도 중요하다. 상기 가스로서 사용하는 산소 가스나 아르곤 가스의 노점을, -40℃ 이하, 바람직하게는 -80℃ 이하, 보다 바람직하게는 -100℃ 이하로 하고, 사용하는 가스의 고순도화를 도모함으로써 산화물 반도체막에 수분 등이 도입되는 것을 가능한 한 방지할 수 있다. 구체적으로, 제2 금속 산화물막이 In-M-Zn 산화물(M은, Ga, Y, Zr, La, Ce 또는 Nd)인 경우, 제2 금속 산화물막을 성막하기 위해서 사용하는 타깃에 있어서, 금속 원소의 원자수비를 In:M:Zn=x1:y1:z1로 하면, x1/y1은 1/3 이상 6 이하, 나아가 1 이상 6 이하이며, z1/y1은 1/3 이상 6 이하, 나아가 1 이상 6 이하인 것이 바람직하다. 또한, z1/y1을 1 이상 6 이하로 함으로써, 제2 금속 산화물막으로서 CAAC-OS막이 형성되기 쉬워진다. 타깃의 금속 원소 원자수비의 대표예로서는, In:M:Zn=1:1:1, In:M:Zn=3:1:2 등이 있다.

구체적으로, 제1 금속 산화물막, 제3 금속 산화물막이 In-M-Zn 산화물(M은, Ga, Y, Zr, La, Ce 또는 Nd)인 경우, 제1 금속 산화물막, 제3 금속 산화물막을 성막하기 위해서 사용하는 타깃에 있어서, 금속 원소의 원자수비를 In:M:Zn=x2:y2:z2로 하면, x2/y2<x1/y1이며, z2/y2는, 1/3 이상 6 이하, 나아가 1 이상 6 이하인 것이 바람직하다. 또한, z2/y2를 1 이상 6 이하로 함으로써, 제1 금속 산화물막, 제3 금속 산화물막으로서 CAAC-OS막이 형성되기 쉬워진다. 타깃의 금속 원소 원자수비의 대표예로서는, In:M:Zn=1:3:2, In:M:Zn=1:3:4, In:M:Zn=1:3:6, In:M:Zn=1:3:8 등이 있다.

또한, 제1 금속 산화물막 및 제3 금속 산화물막의 두께는, 3㎚ 이상 100㎚ 이하, 바람직하게는 3㎚ 이상 50㎚ 이하로 한다. 또한, 제2 금속 산화물막의 두께는, 3㎚ 이상 200㎚ 이하, 바람직하게는 3㎚ 이상 100㎚ 이하이고, 더욱 바람직하게는 3㎚ 이상 50㎚ 이하이다.

3층 구조의 반도체막에 있어서, 제1 금속 산화물막 내지 제3 금속 산화물막은, 비정질 또는 결정질의 양쪽 형태를 취할 수 있다. 단, 채널 영역이 형성되는 제2 금속 산화물막이 결정질인 것에 의해, 트랜지스터에 안정된 전기적 특성을 부여할 수 있기 때문에, 제2 금속 산화물막은 결정질인 것이 바람직하다.

또한, 채널 형성 영역이란, 트랜지스터의 반도체막 중, 게이트 전극과 중첩되고, 또한 소스 전극과 드레인 전극에 끼워지는 영역을 의미한다. 또한, 채널 영역이란, 채널 형성 영역에 있어서, 전류가 주로 흐르는 영역을 말한다.

예를 들어, 제1 금속 산화물막 및 제3 금속 산화물막으로서, 스퍼터링법에 의해 형성한 In-Ga-Zn계 산화물막을 사용하는 경우, 제1 금속 산화물막 및 제3 금속 산화물막의 성막에는, In-Ga-Zn계 산화물(In:Ga:Zn=1:3:2[원자수비])인 타깃을 사용할 수 있다. 성막 조건은, 예를 들어 성막 가스로서 아르곤 가스를 30sccm, 산소 가스를 15sccm 사용하고, 압력 0.4㎩로 하고, 기판 온도를 200℃로 하고, DC 전력 0.5㎾로 하면 된다.

또한, 제2 금속 산화물막을 CAAC-OS막으로 하는 경우, 제2 금속 산화물막의 성막에는, In-Ga-Zn계 산화물(In:Ga:Zn=1:1:1[원자수비])이며, 다결정의 In-Ga-Zn계 산화물을 포함하는 타깃을 사용하는 것이 바람직하다. 성막 조건은, 예를 들어 성막 가스로서 아르곤 가스를 30sccm, 산소 가스를 15sccm 사용하고, 압력을 0.4㎩로 하고, 기판의 온도를 300℃로 하여, DC 전력 0.5㎾로 할 수 있다.

또한, 트랜지스터는, 반도체막의 단부가 경사져 있는 구조를 갖고 있어도 되고, 반도체막의 단부가 둥글게 되어 있는 구조를 갖고 있어도 된다.

또한, 복수의 적층된 금속 산화물막을 갖는 반도체막을 트랜지스터에 사용하는 경우에 있어서도, 소스 전극 및 드레인 전극에 접하는 영역이, n형화되어 있어도 된다. 상기 구성에 의해, 트랜지스터의 이동도 및 온 전류를 높여서, 트랜지스터를 사용한 반도체 장치의 고속 동작을 실현할 수 있다. 또한, 복수의 적층된 금속 산화물막을 갖는 반도체막을 트랜지스터에 사용하는 경우, n형화되는 영역은, 채널 영역으로 되는 제2 금속 산화물막에까지 달하고 있는 것이, 트랜지스터의 이동도 및 온 전류를 높이고, 반도체 장치의 한층 더한 고속 동작을 실현하는 데 있어서, 더 바람직하다.

<발광 장치의 외관>

도 22는 본 발명의 일 형태에 따른 발광 장치의 외관 일례를 나타내는 사시도이다. 도 22에 도시하는 발광 장치는, 패널(1601)과, 컨트롤러, 전원 회로, 화상 처리 회로, 화상 메모리, CPU 등이 설치된 회로 기판(1602)과, 접속부(1603)를 갖고 있다. 패널(1601)은 화소가 복수 설치된 화소부(1604)와, 복수의 화소를 행마다 선택하는 구동 회로(1605)와, 선택된 행 내의 화소에의 화상 신호 Sig의 입력을 제어하는 구동 회로(1606)를 갖는다.

회로 기판(1602)으로부터, 접속부(1603)를 통해서, 각종 신호와, 전원의 전위가, 패널(1601)에 입력된다. 접속부(1603)에는, FPC(Flexible Printed Circuit) 등을 사용할 수 있다. 또한, 접속부(1603)에 COF 테이프를 사용하는 경우, 회로 기판(1602) 내의 일부 회로, 또는 패널(1601)이 갖는 구동 회로(1605)나 구동 회로(1606)의 일부 등을 별도로 준비한 칩에 형성해 두고, COF(Chip On Film)법을 사용해서 그 칩을 COF 테이프에 접속해 두어도 된다.

<전자 기기의 구성예>

본 발명의 일 형태에 따른 발광 장치는, 표시 장치, 노트북형 퍼스널 컴퓨터, 기록 매체를 구비한 화상 재생 장치(대표적으로는 DVD: Digital Versatile Disc 등의 기록 매체를 재생하고, 그 화상을 표시할 수 있는 디스플레이를 갖는 장치)에 사용할 수 있다. 그 밖에, 본 발명의 일 형태에 따른 발광 장치를 사용할 수 있는 전자 기기로서, 휴대 전화, 휴대형 게임기, 휴대 정보 단말기, 전자 서적, 비디오 카메라, 디지털 스틸 카메라 등의 카메라, 고글형 디스플레이(헤드 마운트 디스플레이), 네비게이션 시스템, 음향 재생 장치(카 오디오, 디지털 오디오 플레이어 등), 복사기, 팩시밀리, 프린터, 프린터 복합기, 현금 자동 입출금기(ATM), 자동 판매기 등을 들 수 있다. 이들 전자 기기의 구체예를 도 23에 도시하였다.

도 23의 (A)는 표시 장치이며, 하우징(5001), 표시부(5002), 지지대(5003) 등을 갖는다. 본 발명의 일 형태에 따른 발광 장치는, 표시부(5002)에 사용할 수 있다. 또한, 표시 장치에는, 퍼스널 컴퓨터용, TV 방송 수신용, 광고 표시용 등 모든 정보 표시용 표시 장치가 포함된다.

도 23의 (B)는 휴대 정보 단말기이며, 하우징(5101), 표시부(5102), 조작 키(5103) 등을 갖는다. 본 발명의 일 형태에 따른 발광 장치는, 표시부(5102)에 사용할 수 있다.

도 23의 (C)는 표시 장치이며, 곡면을 갖는 하우징(5701), 표시부(5702) 등을 갖는다. 본 발명의 일 형태에 따른 발광 장치에 가요성을 갖는 기판을 사용함으로써 곡면을 갖는 하우징(5701)에 지지된 표시부(5702)에, 그 발광 장치를 사용할 수 있어, 플렉시블하면서 또한 가벼워서 사용하기 편한 표시 장치를 제공할 수 있다.

도 23의 (D)는 휴대형 게임기이며, 하우징(5301), 하우징(5302), 표시부(5303), 표시부(5304), 마이크로폰(5305), 스피커(5306), 조작 키(5307), 스타일러스(5308) 등을 갖는다. 본 발명의 일 형태에 따른 발광 장치는, 표시부(5303) 또는 표시부(5304)에 사용할 수 있다. 표시부(5303) 또는 표시부(5304)에 본 발명의 일 형태에 따른 발광 장치를 사용함으로써 유저의 사용감이 우수하고, 품질의 저하가 일어나기 어려운 휴대형 게임기를 제공할 수 있다. 또한, 도 23의 (D)에 도시한 휴대형 게임기는, 2개의 표시부(5303)와 표시부(5304)를 갖고 있지만, 휴대형 게임기가 갖는 표시부의 수는, 이에 한정되지 않는다.

도 23의 (E)는 전자 서적이며, 하우징(5601), 표시부(5602) 등을 갖는다. 본 발명의 일 형태에 따른 발광 장치는, 표시부(5602)에 사용할 수 있다. 그리고, 가요성을 갖는 기판을 사용함으로써 발광 장치에 가요성을 갖게 할 수 있으므로, 플렉시블하면서 또한 가벼워서 사용하기 편한 전자 서적을 제공할 수 있다.

도 23의 (F)는 휴대 전화이며, 하우징(5901)에, 표시부(5902), 마이크(5907), 스피커(5904), 카메라(5903), 외부 접속부(5906), 조작용 버튼(5905)이 설치되어 있다. 표시부(5902)에, 본 발명의 일 형태에 따른 발광 장치를 사용할 수 있다. 또한, 본 발명의 일 형태에 따른 발광 장치를, 가요성을 갖는 기판에 형성한 경우, 도 23의 (F)에 도시한 바와 같은 곡면을 갖는 표시부(5902)에 그 발광 장치를 적용하는 것이 가능하다.

<화소의 레이아웃>

이어서, 도 3에 도시하는 화소(11)의, 레이아웃의 일례를 도 24에 도시하였다. 또한, 도 24에서는, 화소(11)의 레이아웃을 명확히 하기 위해서, 게이트 절연막 등의 각종 절연막이나 산화물막을 생략하고 있다.

도 24에 도시하는 화소(11)는 트랜지스터(15), 트랜지스터(16t), 트랜지스터(17t), 트랜지스터(19)를 갖는다. 도전막(501)은 트랜지스터(19)의 게이트로서의 기능과, 배선 GLa로서의 기능을 갖는다. 도전막(502)은 배선 SL로서의 기능과, 트랜지스터(19)의 소스 또는 드레인으로서의 기능을 갖는다. 도전막(503)은 트랜지스터(19)의 소스 또는 드레인으로서의 기능을 갖는다. 도전막(504)은 트랜지스터(15)의 게이트로서의 기능을 갖고, 게다가 도전막(503)에 접속되어 있다. 도전막(505)은 배선 VL로서의 기능과, 트랜지스터(16t)의 소스 또는 드레인으로서의 기능을 갖는다. 도전막(506)은 트랜지스터(15)의 소스 또는 드레인으로서의 기능을 갖는다. 도전막(507)은 발광 소자(14)의 화소 전극으로서의 기능을 갖고, 게다가 도전막(506)에 접속되어 있다. 도전막(508)은 트랜지스터(15)의 소스 또는 드레인으로서의 기능과, 트랜지스터(16t)의 소스 또는 드레인으로서의 기능과, 트랜지스터(17t)의 소스 또는 드레인으로서의 기능을 갖는다. 도전막(509)은 트랜지스터(17t)의 소스 또는 드레인으로서의 기능을 갖는다. 도전막(510)은 배선 GLb로서의 기능과, 트랜지스터(16t)의 게이트로서의 기능을 갖는다. 도전막(511)은 배선 GLc로서의 기능과, 트랜지스터(17t)의 게이트로서의 기능을 갖는다. 도전막(512)은 배선 ML로서의 기능을 갖고, 게다가 도전막(509)에 접속되어 있다.

10 : 발광 장치

11 : 화소

12 : 모니터 회로

13 : 화상 처리 회로

14 : 발광 소자

15 : 트랜지스터

16 : 스위치

16t : 트랜지스터

17 : 스위치

17t : 트랜지스터

18 : 용량 소자

19 : 트랜지스터

20 : 트랜지스터

24 : 화소부

25 : 패널

26 : 컨트롤러

27 : CPU

28 : 화상 메모리

29 : 메모리

30 : 구동 회로

31 : 구동 회로

32 : 화상 데이터

60 : 연산 증폭기

61 : 용량 소자

62 : 스위치

64 : 선택 회로

65 : 스위치

66 : 스위치

67 : 배선

68 : 배선

70 : 트랜지스터

80 : 도전막

81 : 절연막

82 : 산화물 반도체막

82a : 산화물 반도체막

82b : 산화물 반도체막

82c : 산화물 반도체막

83 : 도전막

84 : 도전막

85 : 절연막

86 : 절연막

87 : 절연막

400 : 기판

401 : 도전막

402 : 절연막

403 : 반도체막

404 : 도전막

405 : 도전막

411 : 절연막

420 : 절연막

424 : 도전막

425 : 절연막

426 : 절연막

427 : EL층

428 : 도전막

430 : 기판

431 : 차폐막

432 : 착색층

501 : 도전막

502 : 도전막

503 : 도전막

504 : 도전막

505 : 도전막

506 : 도전막

507 : 도전막

508 : 도전막

509 : 도전막

510 : 도전막

511 : 도전막

512 : 도전막

1601 : 패널

1602 : 회로 기판

1603 : 접속부

1604 : 화소부

1605 : 구동 회로

1606 : 구동 회로

5001 : 하우징

5002 : 표시부

5003 : 지지대

5101 : 하우징

5102 : 표시부

5103 : 조작 키

5301 : 하우징

5302 : 하우징

5303 : 표시부

5304 : 표시부

5305 : 마이크로폰

5306 : 스피커

5307 : 조작 키

5308 : 스타일러스

5601 : 하우징

5602 : 표시부

5701 : 하우징

5702 : 표시부

5901 : 하우징

5902 : 표시부

5903 : 카메라

5904 : 스피커

5905 : 버튼

5906 : 외부 접속부

5907 : 마이크

11 : 화소

12 : 모니터 회로

13 : 화상 처리 회로

14 : 발광 소자

15 : 트랜지스터

16 : 스위치

16t : 트랜지스터

17 : 스위치

17t : 트랜지스터

18 : 용량 소자

19 : 트랜지스터

20 : 트랜지스터

24 : 화소부

25 : 패널

26 : 컨트롤러

27 : CPU

28 : 화상 메모리

29 : 메모리

30 : 구동 회로

31 : 구동 회로

32 : 화상 데이터

60 : 연산 증폭기

61 : 용량 소자

62 : 스위치

64 : 선택 회로

65 : 스위치

66 : 스위치

67 : 배선

68 : 배선

70 : 트랜지스터

80 : 도전막

81 : 절연막

82 : 산화물 반도체막

82a : 산화물 반도체막

82b : 산화물 반도체막

82c : 산화물 반도체막

83 : 도전막

84 : 도전막

85 : 절연막

86 : 절연막

87 : 절연막

400 : 기판

401 : 도전막

402 : 절연막

403 : 반도체막

404 : 도전막

405 : 도전막

411 : 절연막

420 : 절연막

424 : 도전막

425 : 절연막

426 : 절연막

427 : EL층

428 : 도전막

430 : 기판

431 : 차폐막

432 : 착색층

501 : 도전막

502 : 도전막

503 : 도전막

504 : 도전막

505 : 도전막

506 : 도전막

507 : 도전막

508 : 도전막

509 : 도전막

510 : 도전막

511 : 도전막

512 : 도전막

1601 : 패널

1602 : 회로 기판

1603 : 접속부

1604 : 화소부

1605 : 구동 회로

1606 : 구동 회로

5001 : 하우징

5002 : 표시부

5003 : 지지대

5101 : 하우징

5102 : 표시부

5103 : 조작 키

5301 : 하우징

5302 : 하우징

5303 : 표시부

5304 : 표시부

5305 : 마이크로폰

5306 : 스피커

5307 : 조작 키

5308 : 스타일러스

5601 : 하우징

5602 : 표시부

5701 : 하우징

5702 : 표시부

5901 : 하우징

5902 : 표시부

5903 : 카메라

5904 : 스피커

5905 : 버튼

5906 : 외부 접속부

5907 : 마이크

Claims (18)

- 발광 장치로서,

화소로서,

트랜지스터로서, 상기 트랜지스터를 통해 흐르는 전류의 값이 화상 신호에 따라 결정되는 상기 트랜지스터;

상기 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속되는 발광 소자;

제1 스위치로서, 상기 제1 스위치의 단자가 상기 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽에 전기적으로 접속되는 상기 제1 스위치;

제2 스위치로서, 상기 제2 스위치의 제1 단자가 상기 트랜지스터의 상기 소스 및 상기 드레인 중 상기 다른 쪽에 전기적으로 접속되는 상기 제2 스위치; 및

제1 용량 소자로서, 상기 제1 용량 소자의 제1 단자가 상기 트랜지스터의 게이트에 전기적으로 접속되고, 상기 제1 용량 소자의 제2 단자가 상기 트랜지스터의 상기 소스 및 상기 드레인 중 상기 한쪽에 전기적으로 접속되는 상기 제1 용량 소자

를 포함하는 상기 화소;

상기 제2 스위치의 제2 단자에 전기적으로 접속되고, 상기 전류의 값에 관한 정보를 포함하는 신호를 생성하는 제1 회로; 및

상기 제1 회로에 전기적으로 접속되고, 상기 신호에 따라 상기 화상 신호를 보정하는 제2 회로

를 포함하는, 발광 장치. - 제1항에 있어서,

상기 트랜지스터는 n채널형 트랜지스터인, 발광 장치. - 제1항에 있어서,

상기 트랜지스터는 산화물 반도체막에 채널 형성 영역을 포함하는, 발광 장치. - 제1항에 있어서,

상기 제1 스위치 및 상기 제2 스위치 각각은 산화물 반도체막에 채널 형성 영역을 포함하는 트랜지스터를 포함하는, 발광 장치. - 제1항에 있어서,

상기 제1 회로는 연산 증폭기, 제2 용량 소자 및 제3 스위치를 포함하고,

상기 제2 용량 소자의 제1 단자 및 상기 제3 스위치의 제1 단자는 상기 연산 증폭기의 입력 단자에 전기적으로 접속되고,

상기 제2 용량 소자의 제2 단자 및 상기 제3 스위치의 제2 단자는 상기 연산 증폭기의 출력 단자에 전기적으로 접속되는, 발광 장치. - 제1항에 있어서,

상기 화소와 상기 제1 회로 사이에 전기적으로 접속되는 선택 회로를 더 포함하는, 발광 장치. - 발광 장치로서,

화소로서,

트랜지스터로서, 상기 트랜지스터를 통해 흐르는 전류의 값이 화상 신호에 따라 결정되는 상기 트랜지스터;

상기 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속되는 발광 소자;

제1 스위치로서, 상기 제1 스위치의 단자가 상기 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽에 전기적으로 접속되는 상기 제1 스위치;

제2 스위치로서, 상기 제2 스위치의 제1 단자가 상기 트랜지스터의 상기 소스 및 상기 드레인 중 상기 다른 쪽에 전기적으로 접속되는 상기 제2 스위치; 및

제3 스위치로서, 상기 제3 스위치의 단자가 상기 트랜지스터의 상기 소스 및 상기 드레인 중 상기 한쪽 및 상기 발광 소자에 전기적으로 접속되는 상기 제3 스위치

를 포함하는 상기 화소;

상기 제2 스위치의 제2 단자에 전기적으로 접속되고, 상기 전류의 값에 관한 정보를 포함하는 신호를 생성하는 제1 회로; 및

상기 제1 회로에 전기적으로 접속되고, 상기 신호에 따라 상기 화상 신호를 보정하는 제2 회로

를 포함하는, 발광 장치. - 제7항에 있어서,

상기 트랜지스터는 n채널형 트랜지스터인, 발광 장치. - 제7항에 있어서,

상기 트랜지스터는 산화물 반도체막에 채널 형성 영역을 포함하는, 발광 장치. - 제7항에 있어서,

상기 제1 스위치, 상기 제2 스위치 및 상기 제3 스위치 각각은 산화물 반도체막에 채널 형성 영역을 포함하는 트랜지스터를 포함하는, 발광 장치. - 제7항에 있어서,

상기 제1 회로는 연산 증폭기, 용량 소자 및 제4 스위치를 포함하고,

상기 용량 소자의 제1 단자 및 상기 제4 스위치의 제1 단자는 상기 연산 증폭기의 입력 단자에 전기적으로 접속되고,

상기 용량 소자의 제2 단자 및 상기 제4 스위치의 제2 단자는 상기 연산 증폭기의 출력 단자에 전기적으로 접속되는, 발광 장치. - 제7항에 있어서,

상기 화소와 상기 제1 회로 사이에 전기적으로 접속되는 선택 회로를 더 포함하는, 발광 장치. - 발광 장치로서,

화소로서,

제1 트랜지스터로서, 상기 제1 트랜지스터의 게이트가 제1 배선에 전기적으로 접속되고, 상기 제1 트랜지스터의 소스 및 드레인 중 한쪽에 화상 신호가 공급되는 상기 제1 트랜지스터;

제2 트랜지스터로서, 상기 제2 트랜지스터의 게이트가 상기 제1 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽에 전기적으로 접속되는 상기 제2 트랜지스터;

상기 제2 트랜지스터의 소스 및 드레인 중 한쪽에 전기적으로 접속되는 발광 소자;

제3 트랜지스터로서, 상기 제3 트랜지스터의 소스 및 드레인 중 한쪽이 상기 제2 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽에 전기적으로 접속되는 상기 제3 트랜지스터; 및

제4 트랜지스터로서, 상기 제4 트랜지스터의 소스 및 드레인 중 한쪽이 상기 제2 트랜지스터의 상기 소스 및 상기 드레인 중 상기 다른 쪽에 전기적으로 접속되는 상기 제4 트랜지스터

를 포함하는 상기 화소;

상기 제4 트랜지스터의 상기 소스 및 상기 드레인 중 다른 쪽에 전기적으로 접속되고, 상기 제2 트랜지스터를 통해 흐르는 전류의 값에 관한 정보를 포함하는 신호를 생성하는 제1 회로; 및

상기 제1 회로에 전기적으로 접속되고, 상기 신호에 따라 상기 화상 신호를 보정하는 제2 회로

를 포함하고,

상기 제3 트랜지스터의 게이트는 제2 배선에 전기적으로 접속되고, 상기 제4 트랜지스터의 게이트는 제3 배선에 전기적으로 접속되는. 발광 장치. - 제13항에 있어서,

상기 제1 트랜지스터 및 상기 제2 트랜지스터 각각은 n채널형 트랜지스터인, 발광 장치. - 제13항에 있어서,

상기 제1 트랜지스터 및 상기 제2 트랜지스터 각각은 산화물 반도체막에 채널 형성 영역을 포함하는, 발광 장치. - 제13항에 있어서,

상기 제3 트랜지스터 및 상기 제4 트랜지스터 각각은 산화물 반도체막에 채널 형성 영역을 포함하는, 발광 장치. - 제13항에 있어서,

상기 제1 회로는 연산 증폭기, 용량 소자 및 스위치를 포함하고,

상기 용량 소자의 제1 단자 및 상기 스위치의 제1 단자는 상기 연산 증폭기의 입력 단자에 전기적으로 접속되고,

상기 용량 소자의 제2 단자 및 상기 스위치의 제2 단자는 상기 연산 증폭기의 출력 단자에 전기적으로 접속되는, 발광 장치. - 제13항에 있어서,

상기 화소와 상기 제1 회로 사이에 전기적으로 접속되는 선택 회로를 더 포함하는, 발광 장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013190038 | 2013-09-13 | ||

| JPJP-P-2013-190038 | 2013-09-13 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20150031181A true KR20150031181A (ko) | 2015-03-23 |

Family

ID=52667535

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR20140118738A KR20150031181A (ko) | 2013-09-13 | 2014-09-05 | 발광 장치 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US9659526B2 (ko) |

| JP (3) | JP6495602B2 (ko) |

| KR (1) | KR20150031181A (ko) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9818765B2 (en) | 2013-08-26 | 2017-11-14 | Apple Inc. | Displays with silicon and semiconducting oxide thin-film transistors |

| KR101597037B1 (ko) | 2014-06-26 | 2016-02-24 | 엘지디스플레이 주식회사 | 구동소자의 전기적 특성 편차를 보상할 수 있는 유기발광 표시장치 |

| KR102417266B1 (ko) | 2015-01-27 | 2022-07-05 | 삼성디스플레이 주식회사 | 표시 장치 및 그 접촉 감지 방법 |

| US9704893B2 (en) | 2015-08-07 | 2017-07-11 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic device |

| US9818344B2 (en) | 2015-12-04 | 2017-11-14 | Apple Inc. | Display with light-emitting diodes |

| JP6854670B2 (ja) | 2016-03-04 | 2021-04-07 | 株式会社半導体エネルギー研究所 | 半導体装置、表示パネル、表示モジュール及び電子機器 |

| US11948959B2 (en) * | 2018-07-27 | 2024-04-02 | Semiconductor Energy Laboratory Co., Ltd. | Imaging device comprising first circuit and second circuit |

| WO2021130585A1 (ja) * | 2019-12-25 | 2021-07-01 | 株式会社半導体エネルギー研究所 | 表示装置、および電子機器 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003043993A (ja) * | 2001-07-27 | 2003-02-14 | Canon Inc | アクティブマトリックス型ディスプレイ |

| SG120889A1 (en) | 2001-09-28 | 2006-04-26 | Semiconductor Energy Lab | A light emitting device and electronic apparatus using the same |

| JP2003150107A (ja) * | 2001-11-09 | 2003-05-23 | Sharp Corp | 表示装置およびその駆動方法 |

| JP2003208127A (ja) * | 2001-11-09 | 2003-07-25 | Sanyo Electric Co Ltd | 表示装置 |

| US7961160B2 (en) | 2003-07-31 | 2011-06-14 | Semiconductor Energy Laboratory Co., Ltd. | Display device, a driving method of a display device, and a semiconductor integrated circuit incorporated in a display device |

| JP4869621B2 (ja) * | 2004-04-28 | 2012-02-08 | 株式会社半導体エネルギー研究所 | 表示装置 |

| EP1796070A1 (en) * | 2005-12-08 | 2007-06-13 | Thomson Licensing | Luminous display and method for controlling the same |

| JP4240059B2 (ja) | 2006-05-22 | 2009-03-18 | ソニー株式会社 | 表示装置及びその駆動方法 |

| KR100801375B1 (ko) * | 2006-06-13 | 2008-02-11 | 한양대학교 산학협력단 | 유기 el 소자 및 이의 구동방법 |

| JP2009008799A (ja) * | 2007-06-27 | 2009-01-15 | Sharp Corp | 表示装置およびその駆動方法 |

| JP5242152B2 (ja) * | 2007-12-21 | 2013-07-24 | グローバル・オーエルイーディー・テクノロジー・リミテッド・ライアビリティ・カンパニー | 表示装置 |

| JP2009265459A (ja) | 2008-04-28 | 2009-11-12 | Fujifilm Corp | 画素回路および表示装置 |

| KR101518324B1 (ko) * | 2008-09-24 | 2015-05-11 | 삼성디스플레이 주식회사 | 표시 장치 및 그 구동 방법 |

| JP5933160B2 (ja) | 2008-12-04 | 2016-06-08 | 株式会社半導体エネルギー研究所 | 表示装置、電子機器及び移動体 |

| JP2010266492A (ja) * | 2009-05-12 | 2010-11-25 | Sony Corp | 画素回路、表示装置、画素回路の駆動方法 |

| TWI416467B (zh) * | 2009-09-08 | 2013-11-21 | Au Optronics Corp | 主動式矩陣有機發光二極體顯示器及其像素電路與資料電流寫入方法 |

| TWI424412B (zh) * | 2010-10-28 | 2014-01-21 | Au Optronics Corp | 有機發光二極體之像素驅動電路 |

| JP6018409B2 (ja) | 2011-05-13 | 2016-11-02 | 株式会社半導体エネルギー研究所 | 発光装置 |

| JP6099336B2 (ja) | 2011-09-14 | 2017-03-22 | 株式会社半導体エネルギー研究所 | 発光装置 |

| KR20190033094A (ko) | 2011-10-18 | 2019-03-28 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치를 구동하는 방법 |

| TWI441138B (zh) * | 2011-12-30 | 2014-06-11 | Au Optronics Corp | 發光二極體電路,驅動發光二極體電路之方法及發光二極體顯示器 |

| CN104170001B (zh) | 2012-03-13 | 2017-03-01 | 株式会社半导体能源研究所 | 发光装置及其驱动方法 |

| US9320111B2 (en) | 2012-05-31 | 2016-04-19 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

| KR102061554B1 (ko) * | 2013-05-28 | 2020-01-03 | 삼성디스플레이 주식회사 | 표시 장치 및 그 구동 방법 |

| US9552767B2 (en) | 2013-08-30 | 2017-01-24 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device |

-

2014

- 2014-09-03 JP JP2014178751A patent/JP6495602B2/ja active Active

- 2014-09-05 KR KR20140118738A patent/KR20150031181A/ko not_active Application Discontinuation

- 2014-09-08 US US14/479,630 patent/US9659526B2/en not_active Expired - Fee Related

-

2019

- 2019-03-07 JP JP2019041451A patent/JP6720372B2/ja active Active

-

2020

- 2020-06-17 JP JP2020104395A patent/JP6907385B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2019091089A (ja) | 2019-06-13 |