KR20130023347A - 반도체 소자 그리고 반도체 소자를 제조하기 위한 방법 - Google Patents

반도체 소자 그리고 반도체 소자를 제조하기 위한 방법 Download PDFInfo

- Publication number

- KR20130023347A KR20130023347A KR1020137001259A KR20137001259A KR20130023347A KR 20130023347 A KR20130023347 A KR 20130023347A KR 1020137001259 A KR1020137001259 A KR 1020137001259A KR 20137001259 A KR20137001259 A KR 20137001259A KR 20130023347 A KR20130023347 A KR 20130023347A

- Authority

- KR

- South Korea

- Prior art keywords

- optical element

- semiconductor device

- semiconductor

- semiconductor chip

- molding compound

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 176

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 22

- 230000003287 optical effect Effects 0.000 claims abstract description 106

- 238000000034 method Methods 0.000 claims abstract description 62

- 230000005855 radiation Effects 0.000 claims abstract description 53

- 239000002861 polymer material Substances 0.000 claims abstract description 22

- 230000005693 optoelectronics Effects 0.000 claims abstract description 10

- 239000000463 material Substances 0.000 claims description 46

- 238000000465 moulding Methods 0.000 claims description 43

- 150000001875 compounds Chemical class 0.000 claims description 37

- 230000008569 process Effects 0.000 claims description 29

- 238000001723 curing Methods 0.000 claims description 23

- 229910052710 silicon Inorganic materials 0.000 claims description 11

- 239000010703 silicon Substances 0.000 claims description 11

- 230000008878 coupling Effects 0.000 claims description 10

- 238000010168 coupling process Methods 0.000 claims description 10

- 238000005859 coupling reaction Methods 0.000 claims description 10

- 238000006243 chemical reaction Methods 0.000 claims description 9

- WZZBNLYBHUDSHF-DHLKQENFSA-N 1-[(3s,4s)-4-[8-(2-chloro-4-pyrimidin-2-yloxyphenyl)-7-fluoro-2-methylimidazo[4,5-c]quinolin-1-yl]-3-fluoropiperidin-1-yl]-2-hydroxyethanone Chemical compound CC1=NC2=CN=C3C=C(F)C(C=4C(=CC(OC=5N=CC=CN=5)=CC=4)Cl)=CC3=C2N1[C@H]1CCN(C(=O)CO)C[C@@H]1F WZZBNLYBHUDSHF-DHLKQENFSA-N 0.000 claims description 8

- 239000002105 nanoparticle Substances 0.000 claims description 7

- 238000001029 thermal curing Methods 0.000 claims description 7

- 230000005670 electromagnetic radiation Effects 0.000 claims description 6

- 150000002118 epoxides Chemical class 0.000 claims description 6

- 238000002156 mixing Methods 0.000 claims description 3

- 206010073306 Exposure to radiation Diseases 0.000 claims description 2

- 230000003213 activating effect Effects 0.000 claims 1

- 230000001939 inductive effect Effects 0.000 claims 1

- 239000010410 layer Substances 0.000 description 38

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 10

- 230000003595 spectral effect Effects 0.000 description 8

- 239000011248 coating agent Substances 0.000 description 7

- 238000000576 coating method Methods 0.000 description 7

- 238000009826 distribution Methods 0.000 description 5

- 239000002800 charge carrier Substances 0.000 description 4

- 238000005259 measurement Methods 0.000 description 4

- 238000002844 melting Methods 0.000 description 4

- 230000008018 melting Effects 0.000 description 4

- 239000000758 substrate Substances 0.000 description 4

- 238000004132 cross linking Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 2

- NYMPGSQKHIOWIO-UHFFFAOYSA-N hydroxy(diphenyl)silicon Chemical class C=1C=CC=CC=1[Si](O)C1=CC=CC=C1 NYMPGSQKHIOWIO-UHFFFAOYSA-N 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 230000000149 penetrating effect Effects 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 229910052582 BN Inorganic materials 0.000 description 1

- PZNSFCLAULLKQX-UHFFFAOYSA-N Boron nitride Chemical compound N#B PZNSFCLAULLKQX-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 230000006978 adaptation Effects 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 239000012790 adhesive layer Substances 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 239000000428 dust Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000001879 gelation Methods 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 238000013007 heat curing Methods 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 230000004941 influx Effects 0.000 description 1

- 229910001092 metal group alloy Inorganic materials 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 229920002635 polyurethane Polymers 0.000 description 1

- 239000004814 polyurethane Substances 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 230000008929 regeneration Effects 0.000 description 1

- 238000011069 regeneration method Methods 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 239000010948 rhodium Substances 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 238000007493 shaping process Methods 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

- -1 sulfide compound Chemical class 0.000 description 1

- 239000002918 waste heat Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/52—Encapsulations

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B29—WORKING OF PLASTICS; WORKING OF SUBSTANCES IN A PLASTIC STATE IN GENERAL

- B29D—PRODUCING PARTICULAR ARTICLES FROM PLASTICS OR FROM SUBSTANCES IN A PLASTIC STATE

- B29D11/00—Producing optical elements, e.g. lenses or prisms

- B29D11/00009—Production of simple or compound lenses

- B29D11/00432—Auxiliary operations, e.g. machines for filling the moulds

- B29D11/00442—Curing the lens material

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B1/00—Optical elements characterised by the material of which they are made; Optical coatings for optical elements

- G02B1/04—Optical elements characterised by the material of which they are made; Optical coatings for optical elements made of organic materials, e.g. plastics

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B27/00—Optical systems or apparatus not provided for by any of the groups G02B1/00 - G02B26/00, G02B30/00

- G02B27/09—Beam shaping, e.g. changing the cross-sectional area, not otherwise provided for

- G02B27/0938—Using specific optical elements

- G02B27/095—Refractive optical elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/483—Containers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/483—Containers

- H01L33/486—Containers adapted for surface mounting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/50—Wavelength conversion elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/50—Wavelength conversion elements

- H01L33/501—Wavelength conversion elements characterised by the materials, e.g. binder

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/50—Wavelength conversion elements

- H01L33/507—Wavelength conversion elements the elements being in intimate contact with parts other than the semiconductor body or integrated with parts other than the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/52—Encapsulations

- H01L33/54—Encapsulations having a particular shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/52—Encapsulations

- H01L33/56—Materials, e.g. epoxy or silicone resin

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/58—Optical field-shaping elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/85909—Post-treatment of the connector or wire bonding area

- H01L2224/8592—Applying permanent coating, e.g. protective coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0008—Processes

- H01L2933/0033—Processes relating to semiconductor body packages

- H01L2933/005—Processes relating to semiconductor body packages relating to encapsulations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0008—Processes

- H01L2933/0033—Processes relating to semiconductor body packages

- H01L2933/0058—Processes relating to semiconductor body packages relating to optical field-shaping elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/62—Arrangements for conducting electric current to or from the semiconductor body, e.g. lead-frames, wire-bonds or solder balls

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Health & Medical Sciences (AREA)

- Ophthalmology & Optometry (AREA)

- Mechanical Engineering (AREA)

- Led Device Packages (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Medicinal Chemistry (AREA)

- Polymers & Plastics (AREA)

- Organic Chemistry (AREA)

Abstract

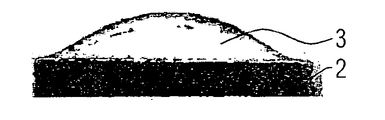

본 발명은 광전자 반도체 칩(2) 그리고 상기 반도체 칩(2)의 방사선 통과 면(20) 상에 배치된 광학 소자(3)를 구비한 반도체 소자(1)와 관련이 있다. 상기 광학 소자(3)는 고굴절 폴리머 물질을 기본으로 한다. 본 발명은 또한 반도체 소자를 제조하기 위한 방법과도 관련이 있다.

Description

본 발명은 반도체 소자 그리고 반도체 소자를 제조하기 위한 방법에 관한 것이다.

본 출원은 독일 특허 출원서 DE 10 2010 024 545.3호를 우선권으로 주장하며, 상기 우선권 서류의 공개 내용은 인용에 의해서 본 출원서에 기록된다.

예를 들어 발광 다이오드와 같은 방사선을 방출하는 반도체 소자들에 의해서 방출되는 방사선의 방사 전력(radiation power)을 증가시키기 위하여 반도체 칩에서는 상기 반도체 칩의 층 구조 또는 기하학적인 구조와 관련하여 여러 가지 변형들이 실행될 수 있다. 하지만, 이와 같은 변형들은 복잡하고 비용 집약적이다.

본 발명의 과제는, 작동 중에 방출되는 방사선의 방사 전력이 상승 되는 반도체 소자를 제공하는 것이다. 본 발명의 또 다른 과제는, 이와 같은 소자를 간단하고도 신뢰할만하게 제조할 수 있는 상기와 같은 반도체 소자를 제조하기 위한 방법을 제시하는 것이다.

상기 과제는 독립 청구항들에 따른 반도체 소자에 의해서 또는 제조 방법에 의해서 해결된다. 추가의 실시 예들 및 합목적성은 종속 청구항들의 대상이다.

한 가지 실시 예에 따르면, 반도체 소자는 광전자 반도체 칩 그리고 상기 반도체 칩의 방사선 통과 면 상에 배치된 광학 소자를 구비한다. 상기 광학 소자는 고굴절 폴리머 물질을 기본으로 한다.

상기 광학 소자는 굴절률이 높다는 자체 특성으로 인해 반도체 칩과 주변 사이에서 발생하는 굴절률 점프를 줄이기 위하여 바람직한 기여를 할 수 있다.

상기와 같은 맥락에서 "고굴절 폴리머 물질을 '기본으로 한다'"는 표현이 의미하는 바는, 상기 고굴절 폴리머 물질이 광학 소자를 위한 기본 재료를 형성한다는 것이다. 상기 기본 재료로서의 고굴절 폴리머 물질에는 예를 들어 반도체 칩 내에서 발생하는 방사선 및/또는 확산체 물질을 변환하기 위한 발광 변환 물질과 같은 추가의 물질이 혼합될 수 있다.

바람직하게 상기 광학 소자는 적어도 80 %의 중량부를 갖는 고굴절 폴리머 물질을 함유한다.

한 가지 개선 예에서는, 고굴절 폴리머 물질 내부에 굴절률을 높이기 위하여 나노 입자들이 제공되었다. 상기 나노 입자들은 바람직하게 고굴절 폴리머 물질의 귤절률보다 더 큰 굴절률을 갖는다. 상기 나노 입자들은 자체 평균 크기와 관련하여 바람직하게는 상기 나노 입자들이 반도체 소자에 의해서 발생 될 그리고/또는 수신 될 방사선을 전혀 흡수하지 않거나 또는 적어도 적은 정도만 흡수하도록 형성되었다.

본 출원서의 틀 안에서 볼 때 "고굴절 재료"란 적어도 1.50의 굴절률을 갖는 재료로 이해된다.

광학 소자의 굴절률, 특히 광학 소자의 폴리머-재료의 굴절률은 바람직하게 적어도 1.52, 특히 바람직하게는 적어도 1.54이다. 또한, 광학 소자의 굴절률은 바람직하게 상기 광학 소자 쪽을 향하고 있는 반도체 소자의 반도체 재료의 굴절률보다 더 작다.

한 가지 바람직한 실시 예에서, 광학 소자는 실리콘, 에폭시드 또는 하이브리드 물질을 함유한다. 예를 들어 디페닐실록산은 1.54의 비교적 높은 굴절률을 갖는 것을 특징으로 한다.

상기 광학 소자는 반도체 칩의 방사선 통과 면을 관통하는 방사선의 빔 포밍(beam forming)을 위해서 이용된다. 이 경우에 상기 빔 포밍은 특히 공간적인 그리고/또는 스펙트럼적인 송출 특성과 관련이 있을 수 있다.

한 가지 실시 예에서, 광학 소자는 반도체 칩으로부터 떨어져서 마주한 측에서 적어도 국부적으로 구부러져 있는데, 특히 반도체 소자에 대한 평면도 상으로 볼 때에는 볼록하게 구부러져 있다. 따라서, 상기 광학 소자는 방사선을 수렴하는 렌즈의 기능을 충족시킬 수 있다.

가로 방향으로 볼 때 상기 광학 소자는 바람직하게 반도체 칩을 가로 방향으로 제한하는 최대 상기 반도체 칩의 한 측면까지 연장된다. 따라서, 상기 광학 소자는 가로 방향으로는 반도체 칩을 넘어서까지 돌출하지 않게 된다. 이 경우에 "가로 방향"이라는 표현은 반도체 칩의 반도체 층들의 주(主) 연장 평면을 따라서 뻗는 한 가지 방향으로 이해될 수 있을 것이다.

따라서, 반도체 칩을 가로 방향으로 제한하는 상기 측면에는 광학 소자를 위한 물질이 없을 수 있다.

한 가지 실시 예에서, 광학 소자는 바람직하게 반도체 칩에 직접적으로 인접한다. 특히 상기 광학 소자는 반도체 소자를 제조할 때에 반도체 칩에 일체로 형성되었다.

한 가지 대안적인 변형 실시 예에서, 광학 소자는 사전에 미리 제작되었으며, 그리고 또한 바람직하게는 결합 층에 의해서 반도체 칩에 고정되었다.

한 가지 바람직한 개선 예에서, 광학 소자 내부에는 발광 변환 재료가 매립되어 있다. 상기 발광 변환 재료는 작동 중에 반도체 칩 내부에서 발생하는 방사선을 적어도 부분적으로 흡수하기 위해서 그리고 다른 파장의 방사선으로 변환시키기 위해서 제공되었다.

한 가지 추가의 바람직한 개선 예에서, 반도체 칩으로부터 떨어져서 마주한 광학 소자의 측에는 하나의 추가의 광학 소자가 배치되어 있으며, 상기 추가의 광학 소자는 고굴절 폴리머 물질을 기본으로 하고, 또한 바람직하게는 볼록하게 구부러져 있다.

상기의 경우에 광학 소자는 스펙트럼적인 빔 포밍을 위해서 이용될 수 있으며, 그리고 상기 추가의 광학 소자는 공간적인 빔 포밍을 위해서 이용될 수 있다.

상기 반도체 칩과 광학 소자 사이에 배치된 결합 층은 바람직하게 고굴절 형태로 형성되었다. 특히 상기 결합 층의 굴절률은 바람직하게 인접하는 광학 소자의 굴절률보다 더 크거나 또는 같다. 상기 결합 층은 고굴절 폴리머 물질, 말하자면 고굴절 실리콘을 기본으로 할 수 있다.

한 가지 추가의 바람직한 실시 예에서, 반도체 소자는 반도체 칩이 그 내부에 매립된 피복을 구비한다. 바람직하게 상기 피복은 광학 소자를 적어도 국부적으로 덮으며, 특히 바람직하게는 완전히 덮는다. 상기 피복은 바람직하게 광학 소자에 적어도 국부적으로 직접 인접한다.

상기 피복은 바람직하게 상기 광학 소자의 굴절률보다 더 작은 그리고 경우에 따라서는 상기 추가 광학 소자의 굴절률보다 더 작은 굴절률을 갖는다.

또한, 상기 피복은 바람직하게 반도체 칩으로부터 떨어져서 마주한 측에서는 적어도 국부적으로 렌즈 형태로 형성되었다. 이와 같은 피복의 형상에 의해서 반도체 소자의 공간적인 송출 특성이 조절될 수 있다.

반도체 소자를 제조하기 위한 방법에서 한 가지 실시 예에 따라 광전자 반도체 칩이 제공된다. 상기 반도체 칩 상에는 광학 소자를 위한 성형 화합물이 제공되며, 이 경우 상기 성형 화합물은 고굴절 폴리머 물질을 기본으로 한다. 상기 성형 화합물은 최고 50 ℃의 온도에서 예비 경화된다. 상기 성형 화합물은 완전히 경화된다.

다른 공정들에 앞서서 진행되는 예비 경화 공정에 의해서는 상기 성형 화합물이 예비 경화 후에 충분한 형태 안정성을 가질 수 있게 된다. 상기 예비 경화 공정은 특히 10 ℃(10 ℃ 포함) 내지 30 ℃(30 ℃ 포함)의 온도에서, 말하자면 실온에서 이루어질 수 있다.

경화 단계 중에 상기 성형 화합물이 녹아서 사라질 위험은 상기 예비 경화 공정에 의해서 줄어들었다. 상기 예비 경화 공정은 바람직하게 성형 화합물이 반도체 칩의 한 측면 위로 진행하지 않도록 이루어진다. 상기 성형 화합물의 경화 공정이 완전히 종료되기 전에 광학 소자의 형태가 원치 않게 변경됨으로써 상기 광학 소자의 품질이 손상되는 상황이 전반적으로 줄어들 수 있다.

한 가지 실시 예에서, 예비 경화 공정은 전자기 방사선에 의해서 유도된다. 바람직하게 상기 예비 경화 공정은 자외 광선에 의해서 이루어진다. 그러나 다른 스펙트럼 범위 안에 있는 방사선, 예를 들면 마이크로파-방사선도 사용될 수 있다.

방사선을 유도하는 경화 공정이 성형 화합물의 더욱 신속한 겔(gel)화를 야기한다는 사실이 드러났다. 그럼으로써 성형 화합물이 녹아서 사라질 위험은 대폭 줄어들게 된다. 그와 달리 순전히 열적인 경화 공정에서는 이때 발생하는 온도 변동이 성형 화합물을 녹일 수 있거나 또는 성형 화합물이 녹는 상황을 촉진할 수 있다.

한 가지 바람직한 실시 예에서, 성형 화합물은 예비 경화 공정 중에 0.2 J/cm2(0.2 J/cm2 포함) 내지 2.0 J/cm2(2.0 J/cm2 포함)의 에너지 유입량을 갖는 방사선에 노출된다. 상기 범위는 광학적 품질이 높은 광학 소자를 제조하기에 특히 적합한 것으로 밝혀졌다.

대안적으로 또는 보완적으로 예비 경화 공정을 위한 성형 화합물은 상기 성형 화합물의 적어도 두 가지 성분을 혼합함으로써 활성화될 수 있다. 이 경우에 상기 성형 화합물의 활성화는 고유하게, 더 상세하게 말하자면 추가의 외부 작용 없이 이루어질 수 있으며, 그리고 예비 경화 효과를 야기할 수 있다. 하지만, 이와 같은 상황은 예를 들어 전자기 방사선에 의해서 추가로 야기되거나 또는 가속될 수 있다.

한 가지 추가의 바람직한 실시 예에서, 성형 화합물의 완전 경화 단계에서는 열적인 경화가 실시된다.

상기 완전 경화 공정은 바람직하게 예비 경화 공정보다 더 높은 온도에서 이루어진다. 예비 경화 공정 중에 이루어지는 성형 화합물의 예비 교차 결합에 의해서는, 열적인 경화 중에 성형 화합물이 열에 의해 녹아서 없어질 위험이 비교적 높은 온도에서도 대폭적으로 줄어들었다.

열적인 경화 공정에서 온도가 높으면 높을수록 경화 단계의 지속 시간은 그만큼 더 줄어들 수 있다. 바람직한 온도는 실온 내지 200 ℃의 온도이며, 특히 바람직한 온도는 50 ℃(50 ℃ 포함) 내지 150 ℃(150 ℃ 포함)이다.

성형 화합물은 광전자 반도체 칩 상에 직접 제공될 수 있다. 대안적으로는 성형 화합물을 제공하기 전에 하나의 추가의 층 또는 하나의 추가의 소자, 예를 들면 발광 변환 재료를 함유하는 소형 플레이트가 제공될 수도 있다.

전술된 방법은 특히 앞에서 기술된 반도체 소자를 제조하기에 적합하다. 그렇기 때문에 반도체 소자와 관련해서 언급된 특징들은 상기 방법에도 이용될 수 있으며, 그리고 그 역도 마찬가지로 가능하다.

추가의 실시 예들 그리고 합목적성은 도면들과 연관된 실시 예들에 대한 아래의 설명으로부터 드러난다.

도 1은 반도체 소자에 대한 제 1 실시 예의 개략적인 단면도이며;

도 2는 도 1에 도시된 제 1 실시 예에 따른 반도체 칩 및 광학 소자의 확대도이고;

도 3은 광학 소자를 구비한 반도체 칩에 대한 제 2 실시 예의 개략적인 단면도이며;

도 4a 내지 도 4e는 광학 소자에 대한 다섯 가지 실시 예의 각각의 단면도이고;

도 5는 사전에 결정된 물질 량의 수배(i)에 해당하는 광학 소자의 중량에 의존하는, 반도체 소자에 의해서 방출되는 방사선의 방사 전력(P: 임의의 단위)을 측정하여 도시한 도면이며; 그리고

도 6a 내지 도 6c는 반도체 소자를 제조하기 위한 방법에 대한 실시 예를 개략적인 단면도로 도시된 중간 단계들을 참조하여 도시한 도면들이다.

도 2는 도 1에 도시된 제 1 실시 예에 따른 반도체 칩 및 광학 소자의 확대도이고;

도 3은 광학 소자를 구비한 반도체 칩에 대한 제 2 실시 예의 개략적인 단면도이며;

도 4a 내지 도 4e는 광학 소자에 대한 다섯 가지 실시 예의 각각의 단면도이고;

도 5는 사전에 결정된 물질 량의 수배(i)에 해당하는 광학 소자의 중량에 의존하는, 반도체 소자에 의해서 방출되는 방사선의 방사 전력(P: 임의의 단위)을 측정하여 도시한 도면이며; 그리고

도 6a 내지 도 6c는 반도체 소자를 제조하기 위한 방법에 대한 실시 예를 개략적인 단면도로 도시된 중간 단계들을 참조하여 도시한 도면들이다.

각각의 도면에서 동일한, 동일한 형태의 또는 동일하게 작용을 하는 소자들에는 동일한 도면 부호가 제공되었다.

도면들 그리고 각각의 도면에 도시된 소자들의 상호 크기 비율은 척도에 맞는 것으로 간주 될 수 없다. 오히려 개별 소자들은 도면에 대한 개관을 명확히 할 목적으로 그리고/또는 이해를 도울 목적으로 과도하게 크게 도시될 수 있다.

반도체 소자에 대한 제 1 실시 예는 도 1에 개략적인 단면도로 도시되어 있다. 반도체 소자(1)는 예를 들어 표면 장착 가능한 장치(surface mounted device, SMD)로서, 말하자면 발광 다이오드-장치로서 구현되었다.

상기 반도체 소자(1)는 광전자 반도체 칩(2) 그리고 상기 광전자 반도체 칩(2)의 방사선 통과 면(20) 상에 배치된 광학 소자(3)를 구비한다.

상기 반도체 소자는 또한 하우징 바디(5)를 포함하며, 상기 하우징 바디는 제 1 콘택(51) 및 제 2 콘택(52)을 구비한 리드 프레임에 일체로 형성되었다. 또한, 상기 하우징 바디(5) 내에는 열 콘택(53)도 형성되어 있다. 제 1 및 제 2 콘택과 달리 상기 열 콘택은 주로 전기적인 콘택팅을 위해서 이용되지 않고, 오히려 반도체 칩 내에서 작동 중에 발생하는 폐열을 방출하기 위해서 이용된다.

상기 제 1 콘택(51) 및 제 2 콘택(52)은 반도체 칩(2)의 작동 중에 상기 반도체 칩(2) 안으로 전하 캐리어를 주입하기 위해서, 특히 방사선의 발생을 목적으로 제공된 상기 반도체 칩의 활성 구역 안으로 전하 캐리어를 주입하기 위해서 이용된다. 상기 반도체 칩(2)은 결합 라인(6), 예를 들어 본딩 와이어를 통해서 제 2 콘택과 전기 전도성으로 결합 되어 있다. 상기 결합 라인은 적어도 국부적으로 광학 소자(3) 외부에서 뻗는다. 상기 결합 라인은 또한 완전히 광학 소자(3) 외부에서 뻗을 수도 있다.

상기 반도체 소자(1)는 또한 피복(4)도 포함한다. 상기 반도체 칩(2) 및 경우에 따라 결합 라인(6)은 상기 피복에 의해서 캡슐화되어 있으며, 그리고 그로 인해 예를 들어 습기, 먼지 또는 기계적인 부하와 같은 외부 영향들로부터 보호된다.

또한, 상기 피복은 반도체 칩(2)으로부터 떨어져서 마주한 측에서 광학 소자(3)를 완전히 변형시킨다.

상기 피복(4)은 예를 들어 에폭시드 혹은 실리콘 또는 에폭시드와 실리콘의 혼합물을 함유할 수 있거나 또는 이와 같은 물질로 이루어질 수 있다.

상기 광학 소자(3)는 고굴절 폴리머 물질을 기본으로 하고, 바람직하게는 적어도 1.52의 굴절률, 특히 바람직하게는 적어도 1.54의 굴절률을 갖는다. 특히 상기 폴리머 물질은 적어도 1.52의 굴절률, 바람직하게는 적어도 1.54의 굴절률을 갖는다. 상기 폴리머 물질은 바람직하게 고굴절 실리콘을 함유한다. 예를 들어 디페닐실록산은 1.54의 비교적 높은 굴절률을 갖는 것을 특징으로 한다. 대안적으로 또는 보완적으로는 예를 들어 에폭시드 또는 하이브리드 물질, 말하자면 폴리우레탄과 같은 다른 폴리머 물질도 사용될 수 있다.

상기 폴리머 물질 안에서는 또한 굴절률을 상승시키기 위하여 폴리머 물질보다 더 큰 굴절률을 갖는 나노 입자가 형성될 수도 있다. 그럼으로써 상기 광학 소자의 굴절률은 대폭 상승 될 수 있다. 바람직하게 상기 나노 입자들은 자체 크기와 관련하여 이 나노 입자들이 반도체 칩의 작동 중에 발생하는 방사선을 전혀 흡수하지 않거나 또는 적어도 적은 정도만 흡수하도록 형성되었다.

상기 반도체 칩(2)으로부터 떨어져서 마주한 측에서 상기 광학 소자는 반도체 소자(1)에 대한 평면도로 볼 때 볼록하게 구부러진 형태로 형성되었으며, 그리고 반도체 칩 내에서 발생 되는 방사선을 수렴하기 위해서 이용된다.

상기 광학 소자(3)는 가로 방향으로는, 더 상세하게 말하자면 반도체 몸체(2)의 반도체 층들의 주(主) 연장 평면에서 뻗는 한 가지 방향을 따라서는 상기 반도체 몸체를 가로 방향으로 제한하는 측면(201)을 넘어서까지 연장되지 않는다. 따라서, 상기 측면(201)에는 광학 소자(3)를 위한 물질이 없다.

상기 반도체 칩(2)은 바람직하게 Ⅲ-Ⅴ-화합물 반도체 물질을 함유한다. 상기 Ⅲ-Ⅴ-반도체 물질들은 자외선(AlxInyGa1 -x- yN) 스펙트럼 범위에서 가시 광선(특히 청색 내지 녹색 방사선을 위한 AlxInyGa1 -x- yN, 또는 특히 황색 내지 적색 방사선을 위한 AlxInyGa1 -x- yP(인화물 화합물 반도체 물질들))스펙트럼 범위를 거쳐 적외선(AlxInyGa1 -x- yAS)(비소화물 화합물 반도체 물질들) 스펙트럼 범위까지의 방사선을 발생하기에 특히 적합하다. 이 경우에는 0 ≤ x ≤ 1, 0 ≤ y ≤ 1 및 x + y ≤ 1, 특히 x ≠ 1, y ≠ 1, x ≠ 0 및/또는 y ≠ 0이 각각 적용된다. Ⅲ-Ⅴ-반도체 물질들에 의해서는, 특히 전술된 물질 계들로부터는 또한 방사선 발생의 경우에 높은 내부 양자 효율에 도달할 수 있다.

상기와 같은 반도체 물질들, 특히 인화물 및 비소화물 화합물 반도체 물질들은 비교적 높은 굴절률을 갖는다.

광학 소자(3)의 높은 굴절률로 인해 방사선 통과 면(20)을 관통하는 방사선에 대한 굴절률은 소자와 비교할 때 상기와 같은 광학 소자 없이도 줄어들었다. 그럼으로써 방사선 통과 면(20)에서의 전반사로 인해 반도체 몸체 내부에 남아서 방출되지 않는 방사선의 비율도 줄어들게 된다. 인화물 반도체 칩(2)의 경우에는 상기 소자(1)로부터 방출되는 방사선의 방사 전력이 상기 광학 소자에 의해서 16 %까지만큼 상승 될 수 있다고 밝혀졌다.

도 2에는 도 1과 관련하여 기술된 제 1 실시 예의 반도체 칩(2) 및 광학 소자(3)가 확대도로 도시되어 있다.

상기 반도체 칩(2)은 반도체 층 시퀀스를 갖춘 반도체 몸체(21)를 구비한다. 바람직하게 에피택셜 방식으로 증착된 상기 반도체 층 시퀀스는 상기 반도체 몸체를 형성하고, 방사선을 발생할 목적으로 제공된 활성 구역(22)을 포함하며, 상기 활성 구역은 제 1 전도 타입의 제 1 반도체 영역(23)과 상기 제 1 전도 타입과 상이한 제 2 전도 타입의 제 2 반도체 영역(24) 사이에 배치되어 있다. 예를 들어 상기 제 1 반도체 영역(23)은 p-전도성으로 그리고 상기 제 2 반도체 영역(24)은 n-전도성으로 구현될 수 있거나 또는 그 역도 마찬가지로 가능하다.

상기 반도체 몸체(21)는 캐리어(27) 상에 배치되어 있으며, 이 경우 상기 캐리어는 예를 들어 반도체 층 시퀀스를 위한 성장 기판일 수 있다. 상기 반도체 몸체(21)로부터 떨어져서 마주한 상기 캐리어의 측에는 제 1 콘택 층(28)이 형성되어 있다. 상기 캐리어로부터 떨어져서 마주한 상기 반도체 몸체(21)의 측(27)에는 제 2 콘택 층(29)이 형성되어 있다. 상기 콘택 층들(28, 29)은 다양한 측으로부터 활성 구역(22) 안으로 전하 캐리어를 주입하기 위해서 제공되었다.

상기 고굴절 광학 소자(3)는 반도체 칩(2)의 방사선 통과 면(20) 상에 형성되어 있다. 상기 광학 소자는 상기 제 2 콘택 층(29)의 적어도 한 부분 그리고 또한 본 도면에 명확하게 도시되어 있지 않은 결합 라인(6)의 한 부분도 덮고 있다.

전술된 실시 예와 달리 상기 두 개의 콘택 층(28, 29)은 반도체 몸체의 동일한 측에 형성될 수도 있다. 예를 들면 상기 반도체 칩이 플립-칩으로 형성될 수 있음으로써, 결과적으로 상기 반도체 칩은 광학 소자(3)의 측에 콘택을 전혀 구비하지 않게 된다. 두 개의 콘택이 광학 소자 쪽을 향하고 있는 측에 배치된 반도체 칩도 사용될 수 있다. 이 경우에는 두 개의 결합 라인이 적어도 국부적으로 상기 광학 소자 내부에서 뻗을 수 있다.

또한, 상기 광학 소자(3)는 방사선 검출기로서 형성된 반도체 칩에도 적합하다.

반도체 소자(1)에 대한 제 2 실시 예는 도 3에 개략적인 단면도로 도시되어 있다. 본 실시 예는 실제로 도 1 및 도 2와 관련하여 기술된 제 1 실시 예에 상응한다. 특히 반도체 칩(2)은 도 1과 관련하여 기술된 바와 같이 표면 장착 가능한 소자의 하우징 바디 안에 배치될 수 있다.

하지만 당연히, 상기 반도체 칩은 도 2에 도시된 반도체 칩과 마찬가지로 다른 형태의 하우징 안에, 예를 들면 방사형-구조의 하우징 안에도 배치될 수 있다.

제 1 실시 예와 달리 광학 소자(3)는 발광 변환 재료(32)가 그 내부에 매립되어 있는 소형 플레이트로서 형성되었다.

상기 광학 소자(3)와 반도체 칩(2) 사이에는 결합 층(31)이 배치되어 있으며, 상기 결합 층에 의해서 광학 소자(3)가 상기 반도체 칩에 고정되어 있다. 더 상세하게 말하자면, 본 실시 예에서 상기 광학 소자는 사전에 미리 제작되었다.

상기 결합 층(31)은 바람직하게 마찬가지로 고굴절 방식으로 구현되었다. 특히 바람직하게 상기 결합 층(31)의 굴절률은 상기 광학 소자(3)의 굴절률보다 크거나 같다. 또한, 상기 결합 층(31)은 바람직하게 고굴절 폴리머 물질, 예를 들어 고굴절 실리콘을 기본으로 한다.

상기 반도체 칩(2)으로부터 떨어져서 마주한 상기 광학 소자(3)의 측에는 하나의 추가 광학 소자(35)가 형성되어 있다. 상기 추가의 광학 소자(35)는 바람직하게 마찬가지로 고굴절 폴리머 물질, 말하자면 실리콘을 기본으로 하며, 반도체 칩(2)으로부터 배출되는 방사선의 빔 포밍을 위해서 이용된다.

상기 결합 층(31) 및 광학 소자(3)에 의해서는 반도체 칩(2)으로부터 배출되는 방사선의 굴절률 점프 현상이 줄어들게 되며, 그 결과 상기 반도체 칩으로부터 배출되는 방사선의 방사 전력도 상승 될 수 있다. 상기 추가의 광학 소자(35)는 방사선 디커플링 및 공간적인 빔 포밍을 더욱 높이기 위해서 이용된다. 하지만, 상기 추가의 광학 소자(35)는 생략될 수도 있다.

상기 광학 소자(3) 안에 있는 발광 변환 재료(32)는 반도체 몸체(21)의 활성 구역(22) 안에서 작동 중에 발생 되는 방사선을 적어도 부분적으로 변환시키기 위해서 제공되었다.

결합 층(31)을 갖춘 상기 광학 소자(3)는 도 2와 관련하여 기술된 반도체 칩에 대한 제 1 실시 예에서도 사용될 수 있다.

도 2에 도시된 반도체 칩과 달리 도 3에 도시된 제 2 실시 예에 따른 반도체 칩은 캐리어(27)를 구비하며, 상기 캐리어는 반도체 몸체(21)의 반도체 층 시퀀스를 위한 성장 기판과 상이하다. 상기 캐리어(27)는 예를 들어 반도체 물질, 말하자면 규소, 갈륨 비소화물 혹은 게르마늄, 또는 세라믹, 말하자면 알루미늄 질화물 혹은 붕소 질화물을 함유할 수 있거나 또는 이와 같은 물질로 이루어질 수 있다. 상기 반도체 몸체(21)는 조립 층(26)에 의해서 상기 캐리어에 고정되어 있다. 예를 들어 상기 조립 층을 위해서는 접착 층 또는 남땜 층이 적합하다.

상기 캐리어(27)는 반도체 몸체(21)를 기계적으로 안정화시킨다. 성장 기판은 이와 같은 목적을 위해서는 더 이상 필요치 않고, 적어도 국부적으로 또는 완전히 얇게 형성되거나 또는 제거될 수 있다. 성장 기판이 제거된 반도체 칩은 박막-반도체 칩으로서도 언급된다.

상기 반도체 칩의 방사선 통과 면(20)으로부터 떨어져서 마주한 측에 상기 반도체 몸체(21)는 미러 층(25)을 구비하며, 상기 미러 층은 캐리어(27)의 방향으로 방출되는 방사선을 상기 방사선 통과 면 쪽으로 반사시킨다. 상기 미러 층(25)은 바람직하게 활성 구역(25) 내에서 발생 되는 방사선에 대하여 고굴절 방식으로 형성되었으며, 그리고 또한 상기 방사선의 입사각과 전반적으로 무관한 높은 반사율을 갖는다. 상기 미러 층은 바람직하게 금속, 예를 들어 은, 로듐, 알루미늄 혹은 크롬 또는 전술된 물질들 중에 적어도 한 가지 물질을 갖는 금속성 합금을 함유한다.

또한, 상기 반도체 몸체(21)와 제 2 콘택 층(29) 사이에는 분배 층(29a)이 형성되어 있다. 상기 분배 층(29a)은 전하 캐리어를 제 1 반도체 영역(23)을 거쳐서 활성 구역(22) 안으로 가로 방향으로 균일하게 주입하기 위해서 제공되었다.

그러나 상기 제 1 반도체 영역(23)의 분로 전도성(shunt conductability)이 충분히 높은 경우에는 상기 분배 층(29a)이 생략될 수도 있다.

상기 분배 층(29a)은 바람직하게 활성 구역(22) 내에서 발생 되는 방사선에 대하여 투명하게 형성되었거나 또는 적어도 반투명하게 형성되었다. 예를 들어 상기 분배 층(29a)은 투명한 전도성 산화물(transparent conductive oxide, TCO), 말하자면 인듐 주석 산화물(ITO) 또는 아연 산화물(ZnO)을 함유할 수 있다. 대안적으로 또는 보완적으로는 방사선을 적어도 부분적으로 관통할 수 있을 정도로 얇은 금속 층도 사용될 수 있다.

상기 반도체 몸체(21), 특히 활성 구역(22)은 예를 들어 질화물 반도체 물질을 기본으로 할 수 있으며, 그리고 청색 또는 자외 광선을 발생할 목적으로 제공될 수 있다. 따라서, 상기 광학 소자(3) 내에서 발광 변환 재료(32)에 의해 변환된 방사선과 더불어 집적된 혼색 광원, 예를 들어 백색 광원이 형성될 수 있다. 이와 같은 반도체 칩을 갖춘 소자를 위해서는 광학 소자(3)로 인해 대략 5 %의 방사 전력의 상승이 관찰되었다.

도 4a 내지 도 4e에는 반도체 칩(2) 상에 있는 광학 소자(3)에 대한 다양한 실시 예들이 도시되어 있다. 상기 광학 소자들은 제조시에 사용되는 물질의 양에 있어서 상호 구별된다. 사용된 물질의 양은 각각의 도면에서 4 양 단위에(도 4a 참조), 5 양 단위에(도 4b 참조), 7 양 단위에(도 4c 참조), 10 양 단위에(도 4d 참조) 그리고 13 양 단위에(도 4e 참조) 달한다.

본 도면들은 물질의 양이 증가함에 따라 광학 소자(3)의 높이, 다시 말해 반도체 칩에 대하여 수직으로의 팽창률이 증가 될 수 있다는 사실을 보여주고 있다. 본 실시 예들에서 상기 높이는 157 ㎛, 175 ㎛, 241 ㎛, 301 ㎛ 또는 365 ㎛에 달한다.

본 도면들은 또한 광학 소자(3)의 제조시에 사용된 성형 화합물이 반도체 칩(2)의 방사선 통과 면 상에 완전히 남아 있고, 상기 반도체 칩의 측면을 넘어서까지 흘러가지 않는다는 사실도 보여주고 있다. 따라서, 반도체 칩으로부터 떨어져서 마주한 측이 구면 만곡부를 갖는 형태에 가까워지는 광학 소자들이 구현될 수 있다.

도 4a 내지 도 4e에 도시된 실시 예들에 대한 상기 광학 소자(3)의 크기의 영향은 도 5에 도시되어 있으며, 이 경우 방출된 방사선의 방사 전력(P)은 사용된 재료 량 함수로서의 임의의 단위들로, 사전에 결정된 양 단위의 수 배(i)로 도시되어 있다.

i = 0에 대한 측정 값들은 고굴절 광학 소자가 없는 상태에서 구조적으로 동일한 소자에 대한 기준 측정이다.

곡선(7)은 상기 측정 값들에 대한 다항식 적응을 나타낸다. 상기 측정들은 방사 전력(P)이 처음에는 광학 소자(3)의 크기가 증가함에 따라 상승한다는 것을 보여준다. 상기 방사 전력의 최댓값은 i = 10에 도달하게 되며, 이 경우 상기 전력 곡선은 비교적 평탄한 최댓값을 갖는다. 따라서, i = 7 내지 i = 13의 범위 안에서는 유사하게 높은 출력 파워가 성취된다. 상기 양 단위(i)의 숫자가 커짐에 따라서 광학 소자의 형태는 구 형태로 만곡 된 곡선 형태에 그만큼 더 강하게 가까워진다. 하지만, 양 단위의 숫자가 증가함에 따라서 필요한 재료 량도 증가하게 되며, 이와 같은 상황은 제조 비용을 더욱 높이게 된다.

반도체 소자를 제조하기 위한 방법에 대한 한 가지 실시 예는 개략적인 단면도로 도시된 중간 단계들을 참조하여 도 6a 내지 도 6c에 도시되어 있다. 상기 방법은 단지 도 1 및 도 2와 관련하여 기술된 제 1 실시 예에 따른 반도체 소자를 제조하기 위한 예로서만 도시된다.

도 6a에 도시된 바와 같이, 광전자 반도체 칩이 제공된다. 상기 광전자 반도체 칩은 특히 연결 캐리어 상에 사전에 미리 고정될 수 있거나 또는 표면 장착 가능한 소자를 위한 하우징 안에 사전에 미리 고정될 수 있다.

상기 반도체 칩(2) 상에는 광학 소자를 위한 성형 화합물(30)이 제공되며, 이 경우 상기 성형 화합물은 고굴절 실리콘을 기본으로 한다. 상기 성형 화합물은 최대 50 ℃의 온도에서, 바람직하게는 10 ℃(10 ℃ 포함) 내지 30 ℃(30 ℃ 포함)의 온도에서 예비 경화된다. 본 실시 예에서 예비 경화 공정은 전자기 방사선에 의해서, 특히 자외선 스펙트럼 범위 안에 있는 방사선에 의해서 이루어진다. 비교적 낮은 온도에서의 예비 경화에 의해서는 성형 화합물이 예비 교차 결합 과정을 거치게 됨으로써, 결과적으로 상기 성형 화합물은 적어도 일시적으로는 충분한 형태 안정성을 얻게 된다.

상기 성형 화합물은 또한 바람직하게 자체 접착 방식으로 형성되었다. 그럼으로써 상기 성형 화합물의 신뢰할만한 제공이 간단해졌다.

그 다음에 이어서 상기 성형 화합물의 완전 경화가 이루어진다. 상기 완전 경화 공정은 예를 들어 열 경화로서 이루어질 수 있으며, 이 경우의 온도는 바람직하게 예비 경화 공정에서의 온도보다 더 높다. 열 경화는 실온에서 사전에 미리 개시될 수 있다. 온도가 높아질수록 경화 공정은 그만큼 더 신속하게 이루어진다. 특히 50 ℃의 온도부터는 상기 경화 공정이 상당히 가속된다. 바람직한 온도는 50 ℃(50 ℃ 포함) 내지 150 ℃(150 ℃)에 달한다. 본 완전 경화 단계에서는 제조될 광학 소자의 특성들, 예를 들어 교차 결합도, 광학 소자의 탄성 및/또는 경도가 조절될 수 있다.

순전히 열에 의한 완전 경화 공정과 달리 상기 완전 경화 공정에 앞서서 이루어지는 예비 경화 공정은 전자기 방사선에 의해서 성형 화합물(30)이 녹아 없어지는 현상을 전혀 야기하지 않거나 또는 이와 같은 현상을 적어도 강하게 줄여줌으로써, 결과적으로 재생 가능성이 높은 고 품질의 광학 소자들이 제조될 수 있게 된다. 상기 광학 소자(3)의 구조적인 성형은 넓은 한계 안에서 변동될 수 있다. 특히 애스팩트 비율(aspect ratio)이 높은, 다시 말해 높이 대 폭의 비율이 높은 광학 소자들이 제조될 수 있다.

예비 경화 공정 중에 방사선의 에너지 유입량은 바람직하게 0.2 J/cm2(0.2 J/cm2 포함) 내지 2.0 J/cm2(2.0 J/cm2 포함)에 달한다.

자외선 스펙트럼 범위 안에 있는 전자기 방사선의 유입은 도 6b에 화살표(8)로 표시되어 있다. 그러나 대안적으로는 다른 스펙트럼 범위 안에 있는 방사선, 예를 들어 마이크로파 방사선도 사용될 수 있다.

상기 실시 예와 달리 예비 경화 공정은 성형 화합물(30) 중에 적어도 두 가지 성분의 혼합에 의해서도 유도될 수 있다. 더 상세하게 말하자면, 이 경우에 예비 경화 공정은 보다 넓은 외부 펄스 없이 유도될 수 있다.

또한, 고굴절 실리콘 대신에 다른 고굴절 폴리머 물질, 예를 들면 에폭시드 또는 하이브리드 물질도 사용될 수 있다.

상기 실시 예에서 성형 화합물(30)은 반도체 칩(2)이 결합 라인(6)에 의해서 사전에 미리 전기적으로 콘택팅 된 후에 제공된다. 다시 말해, 성형 화합물(30)은 상기 결합 라인(6)의 한 부분도 변형시킨다.

전술된 방법에 의해서는, 자체 높은 굴절률로 인해 반도체 칩으로부터의 디커플링 효율의 상승을 야기하는 동시에 자체 형태와 관련하여 특히 신뢰할만하게 제조될 수 있는 광학 소자들을 구비한 반도체 소자들이 제조될 수 있으며, 이 경우에 광학 소자를 위한 물질은 반도체 칩(2)의 측면을 넘어서 뻗지 않는다.

따라서, 반도체 칩으로부터 전체적으로 배출되는 방사선의 방사 전력을 높이는 것에 추가하여 신뢰할만하고 재생 가능하게 조절될 수 있는 구조적인 빔 포밍도 성취될 수 있다.

특히 상기 방법은 성형 화합물(30)을 반도체 물질 상에 직접 제공할 때뿐만 아니라 종래의 방법으로는 광학 소자를 제공하기가 어려웠던 표면들, 예를 들어 실리콘 층 상에 성형 화합물(30)을 직접적으로 제공할 때에도 높은 신뢰성을 갖는 것을 특징으로 한다.

본 발명은 실시 예들을 참조한 설명으로 인해 상기 실시 예들에만 한정되지 않는다. 오히려 본 발명은 각각의 새로운 특징 그리고 상기 특징들의 각각의 조합을 포함하며, 이와 같은 특징 또는 상기 특징 조합 자체가 특허청구범위 및 실시 예들에 명시적으로 기재되어 있지 않더라도, 특히 각각의 특징 조합은 특허청구범위에 포함된 것으로 간주 된다.

Claims (15)

- 광전자 반도체 칩(2) 그리고 상기 반도체 칩의 방사선 통과 면(20) 상에 배치된 광학 소자(3)를 구비한 반도체 소자(1)로서,

상기 광학 소자가 고굴절 폴리머 물질을 기본으로 하는,

반도체 소자. - 제 1 항에 있어서,

상기 광학 소자가 실리콘, 에폭시드 또는 하이브리드 물질을 함유하는,

반도체 소자. - 제 1 항 또는 제 2 항에 있어서,

상기 고굴절 폴리머 물질 안에 굴절률을 높이기 위한 나노 입자들이 매립되어 있는,

반도체 소자. - 제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 광학 소자가 반도체 소자에 대한 평면도 상으로 볼 때 상기 반도체 칩으로부터 떨어져서 마주한 측에서는 볼록하게 구부러져 있는,

반도체 소자. - 제 1 항 내지 제 4 항 중 어느 한 항에 있어서,

상기 광학 소자가 가로 방향으로 최대 상기 반도체 칩의 한 측면(201)까지 연장되는,

반도체 소자. - 제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 광학 소자 안에 발광 변환 재료(32)가 매립되어 있는,

반도체 소자. - 제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 광학 소자 안에 발광 변환 재료(32)가 매립되어 있으며, 그리고 상기 반도체 칩으로부터 떨어져서 마주한 상기 광학 소자의 측에 하나의 추가 광학 소자(35)가 배치되어 있으며, 상기 추가의 광학 소자는 고굴절 폴리머 물질을 기본으로 하고 볼록하게 구부러진,

반도체 소자. - 제 7 항에 있어서,

상기 반도체 칩과 광학 소자 사이에 고굴절 결합 층(31)이 배치되어 있는,

반도체 소자. - 반도체 소자(1)를 제조하기 위한 방법으로서,

상기 방법이

a) 광전자 반도체 칩(2)을 제공하는 단계를 포함하며;

b) 광학 소자(3)를 위한 성형 화합물(30)을 제공하는 단계를 포함하며, 이때 상기 성형 화합물은 고굴절 폴리머 물질을 기본으로 하며;

c) 최대 50 ℃의 온도에서 상기 성형 화합물을 예비 경화하는 단계를 포함하며; 그리고

d) 상기 성형 화합물을 완전 경화하는 단계를 포함하는,

반도체 소자를 제조하기 위한 방법. - 제 9 항에 있어서,

상기 예비 경화 공정을 전자기 방사선에 의해서 유도하는,

반도체 소자를 제조하기 위한 방법. - 제 10 항에 있어서,

상기 성형 화합물을 상기 단계 c)에서 0.2 J/cm2(0.2 J/cm2 포함) 내지 2.0 J/cm2(2.0 J/cm2 포함)의 에너지 유입량을 갖는 방사선에 노출시키는,

반도체 소자를 제조하기 위한 방법. - 제 9 항 내지 제 11 항 중 어느 한 항에 있어서,

상기 성형 화합물을 상기 단계 c)에서 상기 성형 화합물 중에 적어도 두 가지 성분의 혼합에 의해서 활성화하는,

반도체 소자를 제조하기 위한 방법. - 제 9 항 내지 제 12 항 중 어느 한 항에 있어서,

상기 단계 d)를 상기 단계 c)보다 더 높은 온도에서 실시하는,

반도체 소자를 제조하기 위한 방법. - 제 9 항 내지 제 13 항 중 어느 한 항에 있어서,

상기 단계 d)에서 열 경화를 실시하는,

반도체 소자를 제조하기 위한 방법. - 제 9 항 내지 제 14 항 중 어느 한 항에 있어서,

제 1 항 내지 제 8 항 중 어느 한 항에 따른 반도체 소자를 제조하는,

반도체 소자를 제조하기 위한 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102010024545.3 | 2010-06-22 | ||

| DE102010024545.3A DE102010024545B4 (de) | 2010-06-22 | 2010-06-22 | Halbleiterbauelement und Verfahren zur Herstellung eines Halbleiterbauelements |

| PCT/EP2011/058580 WO2011160913A1 (de) | 2010-06-22 | 2011-05-25 | Halbleiterbauelement und verfahren zur herstellung eines halbleiterbauelements |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020177033700A Division KR20170131724A (ko) | 2010-06-22 | 2011-05-25 | 반도체 소자 그리고 반도체 소자를 제조하기 위한 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20130023347A true KR20130023347A (ko) | 2013-03-07 |

Family

ID=44260354

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020137001259A KR20130023347A (ko) | 2010-06-22 | 2011-05-25 | 반도체 소자 그리고 반도체 소자를 제조하기 위한 방법 |

| KR1020177033700A KR20170131724A (ko) | 2010-06-22 | 2011-05-25 | 반도체 소자 그리고 반도체 소자를 제조하기 위한 방법 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020177033700A KR20170131724A (ko) | 2010-06-22 | 2011-05-25 | 반도체 소자 그리고 반도체 소자를 제조하기 위한 방법 |

Country Status (8)

| Country | Link |

|---|---|

| US (2) | US9368699B2 (ko) |

| EP (1) | EP2586069B1 (ko) |

| JP (1) | JP6315988B2 (ko) |

| KR (2) | KR20130023347A (ko) |

| CN (2) | CN105529392B (ko) |

| DE (1) | DE102010024545B4 (ko) |

| TW (2) | TWI545809B (ko) |

| WO (1) | WO2011160913A1 (ko) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102010024545B4 (de) | 2010-06-22 | 2022-01-13 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Halbleiterbauelement und Verfahren zur Herstellung eines Halbleiterbauelements |

| DE102014108368A1 (de) * | 2014-06-13 | 2015-12-17 | Osram Opto Semiconductors Gmbh | Oberflächenmontierbares Halbleiterbauelement und Verfahren zu dessen Herstellung |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6159406A (ja) * | 1984-08-31 | 1986-03-26 | Fujitsu Ltd | プレ−ナ型光ガイドの光結合構造およびその製造方法 |

| DE10023353A1 (de) | 2000-05-12 | 2001-11-29 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement und Verfahren zur Herstellung |

| JP3991612B2 (ja) | 2001-04-09 | 2007-10-17 | 日亜化学工業株式会社 | 発光素子 |

| DE10129785B4 (de) * | 2001-06-20 | 2010-03-18 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement und Verfahren zu seiner Herstellung |

| JP2003224304A (ja) * | 2002-01-28 | 2003-08-08 | Kasei Optonix Co Ltd | 発光装置 |

| JP4241259B2 (ja) | 2003-08-06 | 2009-03-18 | セイコーエプソン株式会社 | マイクロレンズの製造方法 |

| DE10361650A1 (de) | 2003-12-30 | 2005-08-04 | Osram Opto Semiconductors Gmbh | Optoelektronisches Modul und Verfahren zu dessen Herstellung |

| US7645397B2 (en) | 2004-01-15 | 2010-01-12 | Nanosys, Inc. | Nanocrystal doped matrixes |

| DE102005009066A1 (de) | 2005-02-28 | 2006-09-07 | Osram Opto Semiconductors Gmbh | Verfahren zur Herstellung eines optischen und eines strahlungsemittierenden Bauelementes und optisches sowie strahlungsemittierendes Bauelement |

| RU2401846C2 (ru) * | 2006-04-25 | 2010-10-20 | Учреждение Российской академии наук Институт синтетических полимерных материалов им. Н.С. Ениколопова РАН (ИСПМ РАН) | Функциональные полиорганосилоксаны и композиция, способная к отверждению на их основе |

| TWI338380B (en) | 2006-10-11 | 2011-03-01 | Chuan Yu Hung | Light emitting diode incorporating high refractive index material |

| KR20090089431A (ko) * | 2006-11-17 | 2009-08-21 | 쓰리엠 이노베이티브 프로퍼티즈 컴파니 | Led 광원용 광학 접합 조성물 |

| US8029904B2 (en) * | 2006-12-01 | 2011-10-04 | Rohm And Haas Company | Aryl (thio)ether aryl polysiloxane composition and methods for making and using same |

| US8895652B2 (en) | 2007-06-12 | 2014-11-25 | Ajjer, Llc | High refractive index materials and composites |

| JP5318383B2 (ja) * | 2007-08-07 | 2013-10-16 | デクセリアルズ株式会社 | 光学部品封止材及び発光装置 |

| TW200910648A (en) * | 2007-08-31 | 2009-03-01 | Isotech Products Inc | Forming process of resin lens of an LED component |

| JP5578597B2 (ja) | 2007-09-03 | 2014-08-27 | 独立行政法人物質・材料研究機構 | 蛍光体及びその製造方法、並びにそれを用いた発光装置 |

| US20090065792A1 (en) * | 2007-09-07 | 2009-03-12 | 3M Innovative Properties Company | Method of making an led device having a dome lens |

| US10256385B2 (en) * | 2007-10-31 | 2019-04-09 | Cree, Inc. | Light emitting die (LED) packages and related methods |

| US8866169B2 (en) * | 2007-10-31 | 2014-10-21 | Cree, Inc. | LED package with increased feature sizes |

| US9287469B2 (en) | 2008-05-02 | 2016-03-15 | Cree, Inc. | Encapsulation for phosphor-converted white light emitting diode |

| JP2009275196A (ja) * | 2008-05-19 | 2009-11-26 | Sony Corp | 硬化性樹脂材料組成物、光学材料、発光装置及びその製造方法、並びに電子デバイス |

| CN101740707B (zh) * | 2009-12-11 | 2013-11-06 | 晶科电子(广州)有限公司 | 预成型荧光粉贴片及其与发光二极管的封装方法 |

| DE102010024545B4 (de) | 2010-06-22 | 2022-01-13 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Halbleiterbauelement und Verfahren zur Herstellung eines Halbleiterbauelements |

-

2010

- 2010-06-22 DE DE102010024545.3A patent/DE102010024545B4/de active Active

-

2011

- 2011-05-25 US US13/703,180 patent/US9368699B2/en active Active

- 2011-05-25 EP EP11723914.5A patent/EP2586069B1/de active Active

- 2011-05-25 KR KR1020137001259A patent/KR20130023347A/ko active Application Filing

- 2011-05-25 JP JP2013515795A patent/JP6315988B2/ja active Active

- 2011-05-25 WO PCT/EP2011/058580 patent/WO2011160913A1/de active Application Filing

- 2011-05-25 CN CN201610015092.XA patent/CN105529392B/zh active Active

- 2011-05-25 KR KR1020177033700A patent/KR20170131724A/ko active Search and Examination

- 2011-05-25 CN CN201180031248.9A patent/CN102947959B/zh active Active

- 2011-06-20 TW TW104124265A patent/TWI545809B/zh active

- 2011-06-20 TW TW100121392A patent/TWI497776B/zh active

-

2016

- 2016-05-05 US US15/146,984 patent/US9634207B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN102947959B (zh) | 2016-01-27 |

| KR20170131724A (ko) | 2017-11-29 |

| JP2013534728A (ja) | 2013-09-05 |

| TW201208148A (en) | 2012-02-16 |

| DE102010024545A1 (de) | 2011-12-22 |

| CN105529392A (zh) | 2016-04-27 |

| TWI545809B (zh) | 2016-08-11 |

| DE102010024545B4 (de) | 2022-01-13 |

| US9634207B2 (en) | 2017-04-25 |

| CN102947959A (zh) | 2013-02-27 |

| EP2586069B1 (de) | 2017-03-01 |

| US9368699B2 (en) | 2016-06-14 |

| US20130240929A1 (en) | 2013-09-19 |

| JP6315988B2 (ja) | 2018-04-25 |

| CN105529392B (zh) | 2019-10-18 |

| US20160247986A1 (en) | 2016-08-25 |

| TWI497776B (zh) | 2015-08-21 |

| WO2011160913A1 (de) | 2011-12-29 |

| EP2586069A1 (de) | 2013-05-01 |

| TW201541673A (zh) | 2015-11-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10217915B2 (en) | Optoelectronic semiconductor component | |

| US8324647B2 (en) | Light emitting module with optically-transparent thermally-conductive element | |

| TWI387131B (zh) | 發射電磁輻射之光電組件及製造光電組件的方法 | |

| TW569473B (en) | Opto-electronic component | |

| US8294160B2 (en) | Light emitting device including a sealing portion, and method of making the same | |

| US7560741B2 (en) | Lighting module and method for the production thereof | |

| TWI528602B (zh) | 具有遠端磷光層及反射子基板的發光二極體 | |

| US8890140B2 (en) | Radiation-emitting component with a semiconductor chip and a conversion element and method for the production thereof | |

| US9024341B2 (en) | Refractive index tuning of wafer level package LEDs | |

| US20130069088A1 (en) | Light emitting diode with conformal surface electrical contacts with glass encapsulation | |

| KR101168461B1 (ko) | 광전자 소자 및 광전자 소자용 하우징 | |

| US20130207144A1 (en) | Component and method for producing a component | |

| JP6225272B2 (ja) | オプトエレクトロニクス部品 | |

| KR102224848B1 (ko) | 발광 소자 패키지 제조 방법 | |

| CN102057507A (zh) | 具有分隔的波长转换材料的半导体光发射器件及其形成方法 | |

| KR100659900B1 (ko) | 백색 발광 소자 및 그 제조방법 | |

| KR20130066635A (ko) | 광전자 소자 그리고 광전자 소자 및 복합 구조물을 제조하기 위한 방법 | |

| US10615323B2 (en) | Component having a reflector and method of producing components | |

| KR20150127133A (ko) | 광전 소자 및 광전 소자를 제조하기 위한 방법 | |

| US9634207B2 (en) | Semiconductor component and method of producing a semiconductor component | |

| KR20130102117A (ko) | 복합 기판, 복합 기판을 포함하는 반도체 칩 및, 복합 기판과 반도체 칩의 제조 방법 | |

| US20160099390A1 (en) | Optoelectronic semiconductor component | |

| KR101223051B1 (ko) | 엘이디 패키지 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| AMND | Amendment | ||

| E902 | Notification of reason for refusal | ||

| AMND | Amendment | ||

| E601 | Decision to refuse application | ||

| AMND | Amendment | ||

| A107 | Divisional application of patent |