KR20120091906A - 데이터 리텐션 동작을 수행하는 사용자 장치, 저장 장치, 그리고 그것의 데이터 리텐션 방법 - Google Patents

데이터 리텐션 동작을 수행하는 사용자 장치, 저장 장치, 그리고 그것의 데이터 리텐션 방법 Download PDFInfo

- Publication number

- KR20120091906A KR20120091906A KR1020110012009A KR20110012009A KR20120091906A KR 20120091906 A KR20120091906 A KR 20120091906A KR 1020110012009 A KR1020110012009 A KR 1020110012009A KR 20110012009 A KR20110012009 A KR 20110012009A KR 20120091906 A KR20120091906 A KR 20120091906A

- Authority

- KR

- South Korea

- Prior art keywords

- time

- storage device

- retention

- line

- memory

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

Abstract

본 발명은 저장 장치의 데이터 리텐션 방법에 관한 것이다. 본 발명의 리텐션 방법은, 호스트로부터 글로벌 타임(Global time)을 제공받는 단계, 그리고 상기 글로벌 타임(Global time)을 참조하여 저장 데이터를 주기적으로 리프레쉬하는 단계를 포함한다.

Description

본 발명은 반도체 메모리 장치에 관한 것으로, 더욱 상세하게는 글로벌 타임을 참조하여 데이터 리텐션 동작을 수행하는 사용자 장치, 저장 장치 및 그것의 데이터 리텐션 방법에 관한 것이다.

최근에는 디지털 카메라, MP3 플레이어, 휴대 전화, 태블릿 PC 등과 같은 모바일 전자 장치가 많이 사용되고 있다. 이러한 모바일 전자 장치에는 플래시 메모리와 같은 불휘발성 메모리 장치가 데이터의 저장 매체로 사용되고 있다. 불휘발성 메모리 장치는 전원이 차단되더라도 데이터를 잃지 않으며, 저전력 및 고집적 특성을 가진다.

불휘발성 메모리 장치에 있어서, 데이터 보유 특성(Data retention characteristics)은 데이터의 신뢰성에 관련된 중대한 관심사이다. 플래시 메모리 장치의 경우, 플로팅 게이트에 저장된 전하(또는, 전자)는 다양한 원인에 따라 외부로 누설될 수 있다. 예를 들면, 결함 절연막을 통한 열이온 방출 및 전하 확산, 이온 불순물, 시간의 경과 등과 같은 다양한 페일 메커니즘들을 통해 플로팅 게이트로부터 누설될 수 있다. 전하의 누설은 메모리 셀의 문턱 전압의 감소를 야기할 것이다. 반대로 다양한 스트레스에 의해서 메모리 셀의 문턱 전압은 상승할 수도 있다.

결과적으로, 시간의 경과에 따라 메모리 셀에 저장된 데이터가 변경되지 않도록 관리할 필요가 있다. 이러한 데이터의 관리 동작을 데이터 리텐션(Data retention)이라 한다. 데이터 리텐션은 특정 메모리 영역의 데이터를 데이터 리텐션 주기마다 리프레쉬(Refresh)하는 동작을 의미한다. 즉, 선택된 메모리 영역을 소거하고, 소거 전에 기록된 데이터를 재기입하는 동작을 데이터 리텐션이라 한다. 효율적인 데이터 리텐션 스킴을 적용하면, 전하 누설과 같은 원인으로 발생하는 신뢰성 저하를 효과적으로 차단할 수 있다.

본 발명의 목적은 불휘발성 메모리 장치를 포함하는 저장 장치에서 데이터 리텐션의 효율을 높이는 데 있다. 본 발명의 다른 목적은 오프-라인으로 유지된 시간을 참조하여 데이터 리텐션을 수행하는 방법 및 저장 장치를 제공하는 데 있다.

본 발명의 실시 예에 따른 데이터 리텐션 방법은, 호스트로부터 글로벌 타임(Global time)을 제공받는 단계, 그리고 상기 글로벌 타임(Global time)을 참조하여 저장 데이터를 주기적으로 리프레쉬하는 단계를 포함한다.

본 발명의 실시 예에 따른 사용자 장치는, 글로벌 타임을 전송하는 호스트, 그리고 상기 글로벌 타임을 참조하여 저장 데이터를 주기적으로 리프레쉬하는 저장 장치를 포함한다.

본 발명의 실시 예에 따른 저장 장치는, 불휘발성 메모리 장치, 그리고 호스트로부터 제공되는 글로벌 타임에 기반하여 상기 불휘발성 메모리 장치에 저장된 데이터를 주기적으로 리프레쉬하는 메모리 컨트롤러를 포함하되, 상기 호스트에 전기적으로 접속되면, 상기 메모리 컨트롤러는 상기 글로벌 타임을 참조하여 상기 호스트와 전기적으로 분리된 오프-라인 시간을 계산하고, 상기 오프-라인 시간 동안 중단된 리프레쉬 동작을 보상한다.

본 발명에 따르면, 오프-라인 시간을 고려한 데이터 리텐션 동작을 수행할 수 있어, 고신뢰성의 저장 장치를 구현할 수 있다.

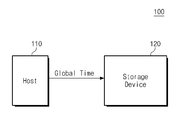

도 1은 본 발명의 실시 예에 따른 사용자 장치를 보여주는 블록도이다.

도 2는 본 발명의 리텐션 동작을 보여주는 도면이다.

도 3은 본 발명에 따른 글로벌 타임(GT)의 제공 방법의 일 실시 예를 보여주는 도면이다.

도 4는 본 발명에 따른 글로벌 타임(GT)의 제공 방법의 다른 실시 예를 보여주는 도면이다.

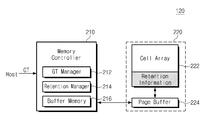

도 5는 본 발명의 실시 예에 따른 저장 장치를 보여주는 블록도이다.

도 6은 본 발명에 따른 리텐션 방법을 보여주는 순서도이다.

도 7은 본 발명의 리텐션 방법을 보여주는 타이밍도이다.

도 8은 본 발명의 보상 리텐션 동작의 일 예를 보여주는 타이밍도이다.

도 9는 본 발명의 보상 리텐션 동작의 다른 예를 보여주는 타이밍도이다.

도 10은 본 발명의 보상 리텐션 동작의 또 다른 예를 보여주는 타이밍도이다.

도 11은 본 발명의 실시 예를 적용한 솔리드 스테이트 디스크(SSD) 시스템을 보여주는 블록도이다.

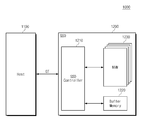

도 12는 본 발명의 실시 예에 따른 메모리 카드를 보여준다.

도 13은 본 발명의 실시 예에 따른 퓨전 메모리 장치를 보여주는 블록도이다.

도 14는 본 발명의 실시 예에 따른 컴퓨팅 시스템을 보여주는 블록도이다.

도 2는 본 발명의 리텐션 동작을 보여주는 도면이다.

도 3은 본 발명에 따른 글로벌 타임(GT)의 제공 방법의 일 실시 예를 보여주는 도면이다.

도 4는 본 발명에 따른 글로벌 타임(GT)의 제공 방법의 다른 실시 예를 보여주는 도면이다.

도 5는 본 발명의 실시 예에 따른 저장 장치를 보여주는 블록도이다.

도 6은 본 발명에 따른 리텐션 방법을 보여주는 순서도이다.

도 7은 본 발명의 리텐션 방법을 보여주는 타이밍도이다.

도 8은 본 발명의 보상 리텐션 동작의 일 예를 보여주는 타이밍도이다.

도 9는 본 발명의 보상 리텐션 동작의 다른 예를 보여주는 타이밍도이다.

도 10은 본 발명의 보상 리텐션 동작의 또 다른 예를 보여주는 타이밍도이다.

도 11은 본 발명의 실시 예를 적용한 솔리드 스테이트 디스크(SSD) 시스템을 보여주는 블록도이다.

도 12는 본 발명의 실시 예에 따른 메모리 카드를 보여준다.

도 13은 본 발명의 실시 예에 따른 퓨전 메모리 장치를 보여주는 블록도이다.

도 14는 본 발명의 실시 예에 따른 컴퓨팅 시스템을 보여주는 블록도이다.

앞의 일반적인 설명 및 다음의 상세한 설명 모두 예시적이라는 것이 이해되어야 하며, 청구된 발명의 부가적인 설명이 제공되는 것으로 여겨져야 한다. 참조 부호들이 본 발명의 바람직한 실시 예들에 상세히 표시되어 있으며, 그것의 예들이 참조 도면들에 표시되어 있다. 가능한 어떤 경우에도, 동일한 참조 번호들이 동일한 또는 유사한 부분을 참조하기 위해서 설명 및 도면들에 사용된다.

이하에서는, 본 발명의 특징 및 기능을 설명하기 위한 불휘발성 저장 매체로서 플래시 메모리 장치를 한 예로서 사용할 것이다. 하지만, 이 기술 분야에 정통한 사람은 여기에 기재된 내용에 따라 본 발명의 다른 이점들 및 성능을 쉽게 이해할 수 있을 것이다. 또한, 저장 매체로서 또 다른 불휘발성 메모리 장치들로 구성될 수 있다. 예를 들면, 저장 매체로서 PRAM, MRAM, ReRAM, FRAM, NOR 플래시 메모리 등이 사용될 수 있으며, 이종의 메모리 장치들이 혼용되는 메모리 시스템에도 적용될 수 있다.

본 발명에서는 '글로벌 타임(Global Time)'이라는 용어가 사용될 것이다. 글로벌 타임은 지구 표준 시각을 의미한다. 예를 들면, 그리니치 천문대를 기준으로 경도에 따라 달리하는 각각의 시간 대역별 표준 시각을 의미한다. 글로벌 타임은 위성 통신망, 유무선 인터넷망과 같은 네트워크를 통해서 실시간으로 제공될 수 있다.

그리고 본 발명에서는 '데이터 리텐션(Data retention)'이란 용어가 사용될 것이다. 데이터 리텐션은 기간의 경과에 따라 전하 누설 등의 원인으로 발생하는 에러를 해결하기 위해서 주기적으로 동일한 데이터를 재기입하는 동작을 말한다. 또한, 본 발명에서는 '온-라인(On-line)' 및 '오프-라인(Off-line)'이라는 용어가 등장한다. '온-라인'은 저장 장치가 호스트에 전기적으로 연결되어 구동되는 상태를 의미한다. 반면, '오프-라인'은 저장 장치가 호스트에서 전기적으로 분리되어 제반 동작이 정지된 상태를 의미한다.

본 발명은 다른 실시 예들을 통해 구현되거나 적용될 수 있을 것이다. 게다가, 상세한 설명은 본 발명의 범위, 기술적 사상 그리고 다른 목적으로부터 상당히 벗어나지 않고 관점 및 응용에 따라 수정되거나 변경될 수 있다. 이하, 본 발명에 따른 실시 예를 첨부된 도면을 참조하여 상세히 설명한다.

도 1은 본 발명의 실시 예에 따른 사용자 장치를 보여주는 블록도이다. 도 1을 참조하면, 본 발명에 따른 사용자 장치(100)는 호스트(110)와 저장 장치(120)를 포함한다. 도시되지는 않았지만, 저장 장치(120)는 불휘발성 메모리(Non-volatile memory)를 포함할 수 있다.

호스트(110)는 저장 장치(120)에 글로벌 타임(Global Time: 이하, GT)을 전송한다. 호스트(110)는 저장 장치(120)가 연결된 온-라인(On-line) 상태에서 주기적으로 글로벌 타임(GT)을 전송할 수 있다. 또는, 호스트(110)는 저장 장치(120)가 호스트(110)에 전기적으로 연결된 후, 한 번만 글로벌 타임(GT)을 전송할 수도 있다. 호스트(110)는, 예를 들면, 개인용/휴대용 컴퓨터, PDA, PMP, MP3 플레이어 등과 같은 휴대용 전자 장치들, HDTV, 그리고 그와 같은 것을 포함할 것이다.

저장 장치(120)는 호스트(110)로부터 전송되는 글로벌 타임(GT)을 참조하여 데이터 리텐션 동작을 수행한다. 데이터 리텐션 동작은, 저장 장치(120)에 저장된 데이터를 독출하고 재기입하는 리프레쉬(Refresh)와, 리프레쉬(Refresh)의 결과를 메타 영역에 업데이트하는 동작을 포함한다.

예를 들면, 저장 장치(120)는 내부에 저장된 데이터를 주기적으로 리프레쉬(Refresh)한다. 저장 장치(120)는 선택된 메모리 영역의 데이터를 읽어낸다. 그리고 저장 장치(120)는 동일한 메모리 영역 또는 다른 메모리 영역에 읽어낸 데이터를 재기입한다. 리프레쉬가 완료되면, 저장 장치(120)는 리프레쉬가 발생한 메모리 영역의 위치 정보 및 리프레쉬가 발생한 시점을 메타 영역에 기입한다. 여기서, 리프레쉬가 발생한 시점은 글로벌 타임(GT)으로 기록된다. 리프레쉬가 발생한 메모리 영역의 위치 정보 및 리프레쉬가 발생한 시점을 이하에서는 리텐션 정보(Retention Information)라 칭하기로 한다.

오프-라인 상태에서 호스트(110)에 접속되면, 저장 장치(120)는 파워-온 리셋(POR) 동작을 수행한다. 그리고 저장 장치(120)는 오프-라인 시간(Off-line period) 동안 데이터 리텐션 동작에 의해서 처리되지 못한 메모리 영역에 대한 보상 리텐션 동작을 수행한다.

보상 리텐션 동작을 위하여, 저장 장치(120)는 메타 영역으로부터 리텐션 정보를 읽는다. 리텐션 정보를 통해, 저장 장치(120)는 오프-라인(Off-line)되기 이전에 최종적으로 데이터 리텐션 동작에 의해 처리된 메모리 영역과, 시각을 파악한다. 그리고 저장 장치(120)는 호스트(110)로부터 전달되는 글로벌 타임(GT)과 데이터 리텐션 정보를 참조하여, 오프-라인(Off-line) 동안 데이터 리텐션 동작으로 처리되지 못한 메모리 영역을 파악한다. 그리고 저장 장치(120)는 이들 메모리 영역에 대한 보상 리텐션 동작을 실시한다.

이상의 본 발명에 따른 사용자 장치(100)에 따르면, 저장 장치(120)는 글로벌 타임(GT)을 참조하여 데이터 리텐션 동작을 수행하므로 오프-라인 시간을 정확히 계산할 수 있다. 저장 장치(120)는 오프-라인(Off-line) 시간 동안 데이터 리텐션 동작에 의해서 처리되지 못한 메모리 영역에 대한 보상 리텐션 동작을 수행한다. 따라서, 오프-라인(Off-line) 시간 동안 실행되지 못한 데이터 리텐션 동작으로부터 야기되는 다양한 문제를 해결할 수 있다.

도 2는 본 발명의 리텐션 동작을 설명하기 위한 도면이다. 도 2를 참조하면, 전하 누설이나 결함과 같은 원인으로 메모리 셀의 문턱 전압은 시간이 경과함에 따라 낮아질 수 있다. 데이터 리텐션 동작은 이렇게 메모리 셀의 낮아진 문턱 전압을 복구시키는 동작이다.

데이터의 기입에 의해서 복수의 메모리 셀들은 프로그램 상태(P1)로 프로그램된다. 프로그램 동작시 메모리 셀들은 검증 전압(Vfy) 이상의 문턱 전압을 갖도록 프로그램된다. 그러나 시간의 경과에 따라, 또는 결함 절연막에 의해서 플로팅 게이트에 주입된 전자가 누설될 수 있다. 이 경우, 메모리 셀의 문턱 전압 산포는 프로그램 상태(P1)로부터 누설 상태(P1′)로 이동할 수 있다.

누설 상태(P1′)는 시간의 경과에 따라 점점 더 낮은 문턱 전압 레벨로 이동할 것이다. 만일, 읽기 전압(Vrd)보다 낮은 문턱 전압을 갖는 메모리 셀들이 발생한다면, 프로그램 상태(P1)로 프로그램된 메모리 셀들 중에는 소거 상태(E0)로 읽혀지는 것들이 생길 수 있다. 이러한 문제를 해결하고, 데이터의 신뢰성을 유지하기 위하여, 메모리 셀은 주기적으로 리텐션 동작에 의해서 프로그램 상태(P1)로 재프로그램해야 한다. 덮어쓰기가 불가능한 메모리 소자에서는 리텐션 대상이 되는 메모리 영역이 먼저 소거된다(①). 그리고 소거된 영역에 소거 이전에 기록되었던 데이터가 재기입될 것이다(②).

결국, 최초에 프로그램 상태(P1)로 프로그램되었던 메모리 셀들은 리텐션 동작에 의해서 소거 상태(E0)로 소거된다. 그 이후에, 소거된 메모리 셀들은 프로그램 상태(P1)로 재프로그램된다. 이러한 절차에 따라 데이터 리텐션 동작이 이루어진다.

여기서, 데이터 리텐션이 플래시 메모리 장치를 예로 설명되었으나, 본 발명은 여기에 국한되지 않는다. 데이터의 기입 후에, 시간의 경과에 따라 메모리 셀의 저항치나 문턱치가 이동(Drift)하는 제반 메모리 소자들에 적용될 수 있을 것이다. 특히, 덮어쓰기 가능한 메모리 소자들은 소거 절차없이 읽혀진 데이터가 재기입될 수 있다. 그리고 데이터 리텐션 동작의 신뢰성을 높이기 위하여, 읽혀진 데이터에 대한 에러 검출 및 정정 동작이 추가될 수 있을 것이다.

도 3은 본 발명에 따른 글로벌 타임(GT)의 제공 방법의 일 예를 보여주는 도면이다. 도 3을 참조하면, 호스트(110)는 저장 장치(120)가 호스트(110)에 접속되면, 글로벌 타임(GT)을 1회 전송한다.

저장 장치(120)는 호스트(110)로부터 제공받은 글로벌 타임(GT)을 참조하여 내부의 카운터를 통해서 지속적으로 글로벌 타임(GT)을 업데이트할 수 있다. 따라서, 온-라인(On-line) 상태 하에서는 저장 장치(120)는 데이터 리텐션 동작을 주기적으로 수행할 수 있다. 주기적으로 실시되는 각각의 데이터 리텐션 동작들에서, 저장 장치(120)는 리프레쉬(Refresh)된 메모리 영역의 위치 정보와, 데이터 리프레쉬가 발생한 글로벌 타임(GT)을 업데이트할 것이다.

어느 순간에, 저장 장치(120)가 호스트(110)로부터 분리되고 오프-라인(Off-line) 상태가 되면, 데이터 리텐션 동작을 포함하는 저장 장치(120)의 제반 내부 동작이 중지될 것이다. 저장 장치(120)가 호스트(110)에 접속되면, 호스트(110)는 이를 감지하고, 글로벌 타임(GT)을 저장 장치(120)로 전송할 것이다. 호스트(110)가 저장 장치(120)의 온-라인(On-line) 여부를 판단하는 방법은, 예를 들면, 플러그 앤 플레이(Plug and Play) 기능을 통해서 지원될 수 있다. 저장 장치(120)의 온-라인 상태가 감지되면, 호스트(110)는 최초 적어도 1회 글로벌 타임(GT)을 저장 장치(120)로 전송한다.

결론적으로, 호스트(110)는 온-라인 상태를 감지하여 글로벌 타임(GT)을 적어도 1회 저장 장치(120)로 전송한다. 저장 장치(120)는 호스트(110)에 전기적으로 접속되어, 오프-라인 상태에서 온-라인 상태로 전환될 때마다 적어도 1회 글로벌 타임(GT)을 수신한다. 그리고 저장 장치(120)는 최초 전달된 글로벌 타임(GT)을 기반으로 온-라인 상태 동안에 내부 글로벌 타임(GT)을 유지할 것이다. 그리고 저장 장치(120)는 내부에서 카운트되는 글로벌 타임(GT)을 참조하여 데이터 리텐션 동작을 주기적으로 실행할 것이다.

특히, 저장 장치(120)는 호스트(110)로부터 제공되는 제 1 글로벌 타임(GT1)과, 오프-라인(Off-line)되기 이전에 마지막으로 데이터 리텐션 동작이 시행된 제 2 글로벌 타임(GT2)을 비교한다. 비교 결과를 참조하여, 저장 장치(120)는 오프-라인 상태로 있었던 시간, 즉 오프-라인 시간(Off-line Period)을 추정할 수 있다. 그리고 추정된 오프-라인 시간을 참조하여, 오프-라인 시간 동안 데이터 리텐션 동작에 의해서 관리되지 못한 메모리 영역을 파악할 수 있다.

도 4는 본 발명의 호스트(110)가 글로벌 타임(GT)을 제공하는 방법의 다른 실시 예를 보여주는 도면이다. 도 4를 참조하면, 호스트(110)는 저장 장치(120)에 글로벌 타임(GT)을 주기적으로 전송한다.

호스트(110)는 저장 장치(120)의 온-라인 상태를 감지하여 글로벌 타임(GT)을 주기적으로 전송한다. 저장 장치(120)는 주기적으로 제공되는 글로벌 타임(GT)을 참조하여 데이터 리텐션 동작을 실시한다. 그리고 저장 장치(120)는 데이터 리텐션 동작이 수행된 시각을 호스트(110)로부터 주기적으로 제공되는 글로벌 타임(GT)으로 기록할 수 있다. 따라서, 저장 장치(110)에서 글로벌 타임(GT)과 내부 카운트 시간을 동기시키기 위한 별도의 카운터는 필요치 않다. 데이터 리텐션 동작이 실시될 때마다, 저장 장치(120)는 데이터가 리프레쉬된 메모리 영역의 위치 정보와 글로벌 타임(GT)을 불휘발성 메모리 영역에 저장할 것이다.

결론적으로, 호스트(110)는 온-라인 상태 동안 주기적으로 글로벌 타임(GT)을 저장 장치(120)로 전송한다. 호스트(110)가 저장 장치(120)의 온-라인 상태를 감지하는 방법은 앞서 도 3에서 설명한 플러그 앤 플래이(Plug and play) 방식의 기능으로 구현될 수 있다. 오프-라인(Off-line) 상태에서 저장 장치(120)가 호스트(110)에 접속되면, 저장 장치(120)는 호스트(110)로부터 최초 제공되는 제 1 글로벌 타임(GT1)과 오프-라인 이전에 수행된 마지막 데이터 리텐션 동작의 제 2 글로벌 타임(GT2)을 비교한다. 그리고 비교 결과를 참조하여 오프-라인 시간을 추정한다. 오프-라인 시간의 추정을 통해서, 저장 장치(120)는 오프-라인 시간 동안, 리텐션 동작에 의해서 관리되지 못한 메모리 영역을 인식할 수 있다. 그리고 저장 장치(120)는 오프-라인 시간 동안 데이터 리텐션 동작에 의해서 관리되지 못한 메모리 영역에 대한 리텐션 동작을 수행한다. 이하에서는, 이러한 리텐션 동작을 보상 리텐션 동작(Compensate retention operation)이라 칭하기로 한다.

도 5는 본 발명의 실시 예에 따른 저장 장치(120)를 예시적으로 보여주는 블록도이다. 도 5를 참조하면, 저장 장치(120)는 메모리 컨트롤러(210)와 플래시 메모리 장치(220)를 포함한다.

메모리 컨트롤러(210)는 호스트(110, 도 1 참조)와 불휘발성 메모리 장치(220)를 인터페이싱한다. 메모리 컨트롤러(210)는 호스트(110)의 쓰기 명령에 응답하여 호스트(110)로부터 제공되는 데이터를 플래시 메모리 장치(220)에 기입하기 위하여 플래시 메모리 장치(220)를 제어한다. 또한, 메모리 컨트롤러(210)는 호스트(110)로부터의 읽기 명령에 응답하여 플래시 메모리 장치(220)의 독출 동작을 제어한다.

메모리 컨트롤러(210)는 호스트(110, 도 1 참조)로부터 제공되는 글로벌 타임(GT)을 참조하여 데이터 리텐션 동작을 수행한다. 글로벌 타임(GT)은 주기적으로 제공될 수 있다. 주기적으로 글로벌 타임(GT)이 제공되는 경우, 메모리 컨트롤러(210)는 호스트(110)로부터 제공된 글로벌 타임(GT)을 데이터 리텐션 동작이 실행된 시점(제 2 글로벌 타임)으로 기록할 수 있다. 그리고 메모리 컨트롤러(210)는 데이터 리텐션 동작이 완료된 메모리 영역에 대한 위치 정보를 저장할 수 있다. 제 2 글로벌 타임과 리텐션 동작의 대상이 되었던 메모리 영역 정보를 리텐션 정보(Retention Information)라 앞서 명명하였다. 리텐션 정보는 데이터 리텐션 동작시마다 플래시 메모리 장치(220)의 메타 데이터 영역에 업데이트될 것이다.

반면, 저장 장치(120)의 온-라인(On-line)의 초기에 1회 글로벌 타임(GT)이 제공되는 경우, 메모리 컨트롤러(210)는 최초 전달되는 글로벌 타임(GT)을 기반으로 내부적인 글로벌 타임을 카운트한다. 그리고, 메모리 컨트롤러(210)는 내부적으로 카운트되는 글로벌 타임(GT)을 기초로 데이터 리텐션 동작이 발생할 때마다 리텐션 정보를 생성하고 업데이트할 것이다.

상술한 기능을 제공하기 위하여, 메모리 컨트롤러(210)는 글로벌 타임 매니저(212), 리텐션 매니저(214), 그리고 버퍼 메모리(214)를 포함할 수 있다.

글로벌 타임 매니저(212)는 호스트(110)로부터 제공되는 글로벌 타임(GT)을 데이터 리텐션 동작시에 시각 정보로 제공할 수 있다. 호스트(110)로부터 주기적으로 글로벌 타임(GT)이 제공되는 경우, 글로벌 타임 매니저(212)는 주기적으로 입력되는 값으로 글로벌 타임(GT)을 업데이트할 것이다. 그리고 글로벌 타임 매니저(212)는 데이터 리텐션 동작이 수행될 때마다, 업데이트된 글로벌 타임(GT)을 리텐션 정보로 제공할 것이다.

반면, 호스트(110)로부터 온-라인(On-line) 상태의 초기에 1회만 글로벌 타임(GT)이 제공되는 경우, 글로벌 타임 매니저(212)는 최초 제공된 글로벌 타임(GT)을 카운트업 할 것이다. 그리고 온-라인 상태 동안 카운트업되는 시각을 글로벌 타임(GT)으로 유지하고, 데이터 리텐션이 실시되는 시점에는 리텐션 정보로 제공할 수 있다.

리텐션 매니저(214)는 플래시 메모리 장치(220)에 저장된 데이터를 주기적으로 리프레쉬하는 데이터 리텐션 동작을 수행한다. 특히, 본 발명의 리텐션 매니저(214)는 데이터 리텐션 동작시에 글로벌 타임 매니저(212)로부터 제공되는 글로벌 타임(GT)을 시각 정보로 저장한다. 저장 장치(120)가 오프-라인 상태로부터 온-라인 상태로 변하면, 리텐션 매니저(214)는 호스트(110)로부터 최초 제공되는 제 1 글로벌 타임(GT1)과, 오프-라인 상태가 되기 이전에 저장된 제 2 글로벌 타임(GT2)을 참조하여, 오프-라인 시간을 추정한다. 리텐션 매니저(214)는 추정된 오프-라인 시간 동안 데이터 리텐션 동작에 따라 처리되지 못한 메모리 영역을 파악할 수 있다. 그리고 리텐션 매니저(214)는 파악된 메모리 영역에 대한 보상 리텐션 동작을 수행한다. 보상 리텐션 동작의 방법은 오프-라인 시간 동안에 리텐션 동작에 따라 처리되지 못한 메모리 영역에 대한 리텐션 동작을 일시에 처리하는 방식으로 구성될 수 있다. 또는, 리텐션 주기를 조정하거나, 일 회에 처리되는 리텐션 데이터의 양을 증가시켜 신속히 보상 리텐션 동작이 수행될 수 있다. 이러한 보상 리텐션 동작은 후술하는 도 8 내지 10에서 상세히 설명하게 될 것이다.

버퍼 메모리(214)는 데이터 리텐션 동작시에 플래시 메모리 장치(220)로부터 읽혀진 데이터를 일시 저장한다. 만일, 리텐션 동작이 플래시 메모리 장치(220)의 최소 소거 단위인 메모리 블록 단위로 이루어진다면, 버퍼 메모리(214)의 사이즈는 적어도 메모리 블록 단위보다는 커야 할 것이다. 리텐션 동작의 대상이 되는 메모리 블록의 데이터가 버퍼 메모리(214)에 저장되면, 메모리 컨트롤러(210)는 리텐션 대상 메모리 블록에 대한 소거 동작을 실시한다. 그리고 소거가 완료되면, 버퍼 메모리(214)에 저장된 데이터가 소거된 메모리 블록에 재기입될 것이다. 이때, 소거된 메모리 블록의 어드레스와, 글로벌 타임이 메타 데이터 영역에 리텐션 정보로써 저장될 것이다.

메모리 컨트롤러(210)는 오프-라인 상태에서 저장 장치(120)가 호스트(110)에 연결되는 시점에, 호스트(110)로부터의 글로벌 타임(GT)을 제공받아 오프-라인 시간을 계산한다. 오프-라인 시간이 계산되면, 오프-라인 시간 동안 데이터 리텐션 동작이 실시되지 못한 메모리 영역에 대한 정보가 도출될 수 있다. 따라서, 메모리 컨트롤러(210)는 오프-라인 동안 데이터 리텐션 동작이 적용되지 못한 메모리 영역에 대한 보상 리텐션 동작을 수행한다. 따라서, 오프-라인 시간에 의해서 발생하는 플래시 메모리 장치들에 포함되는 전체 메모리 영역들에 대한 리텐션 동작의 지연을 차단할 수 있다.

플래시 메모리 장치(220)는 저장 장치(120)의 저장 매체(Storage Medium)로서 제공된다. 플래시 메모리 장치(220)는 셀 어레이(222)와 페이지 버퍼(224)를 포함한다. 셀 어레이(222)는 복수의 메모리 블록들을 포함한다. 그리고 각각의 메모리 블록들은 페이지 단위로 구분될 수 있다. 메모리 블록은 플래시 메모리 장치에서 최소 소거 단위가 된다. 따라서, 데이터 리텐션 동작은 메모리 블록 단위로 이루어질 수 있다. 셀 어레이(222)에는 데이터 리텐션 동작이 발생할 때마다 리텐션 정보를 업데이트하기 위한 메타 데이터 영역을 포함한다. 리텐션 정보에는 데이터 리텐션 동작의 대상이 된 메모리 영역의 어드레스와 글로벌 타임(GT)과 같은 리텐션 이력이 포함된다. 페이지 버퍼(224)는 셀 어레이(222)에 데이터를 기입하거나 독출한다.

플래시 메모리 장치(220)는 대용량의 저장 능력을 가지는 낸드 플래시 메모리(NAND-type Flash memory)로 구성될 수 있다. 또는, 플래시 메모리 장치(220)는 PRAM, MRAM, ReRAM, FRAM 등의 차세대 불휘발성 메모리나 NOR 플래시 메모리로 구성될 수 있다. 데이터 리텐션의 단위가 메모리 블록으로 설명하였으나, 본 발명은 이에 국한되지 않는다. 데이터 리텐션 단위는 메모리의 종류나 특성에 따라서 다양하게 설정될 수 있을 것이다.

이상의 설명에 따르면, 본 발명의 저장 장치(120)는 호스트(110)로부터 제공되는 글로벌 타임(GT)을 참조하여 데이터 리텐션 동작을 수행한다. 특히, 본 발명의 저장 장치(120)는 오프-라인으로부터 온-라인으로 전환되는 시점에 보상 리텐션 동작을 수행한다. 따라서, 오프-라인 시간에 따라 발생하는 전체 메모리 영역에 대한 리텐션 동작의 지연을 차단할 수 있다.

도 6은 본 발명에 따른 리텐션 방법을 간략히 보여주는 순서도이다. 도 6을 참조하면, 글로벌 타임(GT)에 기반한 저장 장치의 데이터 리텐션 동작이 설명될 것이다. 여기서, 저장 장치(120)가 오프-라인 상태에서 온-라인 상태로 전환되는 시점에서의 리텐션 동작이 설명될 것이다.

S110 단계에서, 저장 장치(120)가 호스트(110)에 장착(On-line)되면, 호스트(110)는 글로벌 타임(GT)을 저장 장치(120)로 전송한다. 이때, 저장 장치(120)는 호스트(110)로부터의 글로벌 타임(GT)을 수신하여, 글로벌 타임 매니저(212, 도 5 참조)에 전달된다.

S120 단계에서, 글로벌 타임 매니저(212)는 호스트(110)로부터 수신된 글로벌 타임(GT)과 리텐션 정보(Retention information)를 참조하여 저장 장치(120)의 오프-라인 시간을 계산한다. 즉, 리텐션 정보에는 플래시 메모리 장치(220)의 최종 리텐션 동작이 실시된 글로벌 타임(GT) 정보가 포함되어 있다. 글로벌 타임 매니저(212)는 현재 호스트(110)로부터 제공되는 제 1 글로벌 타임(GT1)과 리텐션 정보로부터 제공되는 제 2 글로벌 타임(GT2)의 시차를 계산하여 오프-라인 시간을 계산한다.

오프-라인 시간의 계산이 완료되면, 저장 장치(120)가 오프-라인 시간 동안 수행하지 못한 리텐션 동작에 대한 정보가 생성될 수 있다. 일반적으로 메모리 블록들은 블록 어드레스 순으로 또는, 프로그램 시간 순서에 따라 데이터 리텐션 동작을 수행할 수 있다. 따라서, 오프-라인 시간이 계산되면, 오프-라인 시간 동안 정상적으로 리텐션이 수행되지 못한 메모리 블록들에 대한 정보가 생성된다.

S130 단계에서, 저장 장치(120)는 오프-라인 시간 동안 수행되지 못한 리텐션 동작을 실시하기 위한 보상 리텐션 동작을 수행한다. 보상 리텐션 동작은 오프-라인 시간 동안 리텐션 동작이 수행되지 못한 메모리 영역들에 대한 리텐션 동작을 온-라인 상태의 초기에 실시하는 동작이다. 보상 리텐션 동작은 다양한 방식에 따라서 이루어질 수 있다. 오프-라인 시간 동안 실행되지 못한 리텐션 동작을 한꺼번에 수행하는 방법이 있을 수 있고, 저장 장치의 퍼포먼스를 고려하여 점진적으로 수행하는 방법이 있을 수 있다. 보상 리텐션 동작의 방법은 후술하는 도 8 내지 10에서 보다 상세하게 설명하기로 한다.

S140 단계에서, 저장 장치(120)는 보상 리텐션 동작에 이어 노말 리텐션 동작을 수행한다. 노말 리텐션 동작은 최초 설정된 주기, 메모리 사이즈, 순서에 따라서 이루어지는 리텐션 동작을 의미한다. 즉, 선택된 메모리 블록의 데이터를 읽어내 버퍼 메모리에 저장하고, 메모리 블록을 소거하고, 버퍼 메모리에 일시 저장된 데이터를 소거된 메모리 블록에 재기입하는 동작이 포함될 것이다. 그리고 리텐션 동작에는 리텐션 동작이 이루어진 메모리 블록의 어드레스, 발생한 시점(글로벌 타임)이 메타 영역에 리텐션 정보로써 저장되는 동작이 더 포함될 것이다.

이상의 본 발명의 실시 예에 따른 리텐션 방법에 따르면, 본 발명의 저장 장치(120)는 오프-라인 시간에 실행되지 못한 리텐션 동작이 온-라인 상태에 이루어지는 보상 리텐션 동작을 수행한다. 따라서, 본 발명의 리텐션 방법에 따르면 오프-라인 시간 동안 실행되지 못한 리텐션 동작에 따른 나머지 메모리 영역의 데이터 신뢰도 저하를 차단할 수 있다.

여기서, 오프-라인 시간 동안 수행되지 못한 동작으로 데이터 리텐션 동작을 예시적으로 설명하였다. 그러나 본 발명은 이에 국한되지 않는다. 예를 들면, 주기적으로 업데이트되어야 하거나 수행되어야 하는 제반 동작에 글로벌 타임을 사용하는 본 발명의 이점이 적용될 수 있을 것이다.

도 7은 본 발명의 리텐션 방법을 간략히 보여주는 타이밍도이다. 도 7을 참조하면, 본 발명의 실시 예에 따른 보상 리텐션 동작의 실행 절차가 간략히 설명될 것이다.

먼저, T1 시점까지는 호스트(110, 도 1 참조)와 저장 장치(120, 도 1 참조)가 전기적으로 접속된 온-라인 상태이다. 온-라인 상태에서, 저장 장치(120)는 주기적으로 리텐션 동작을 수행한다. 예를 들면, 저장 장치(120)는 리텐션 주기(ΔTn)에 따라 선택된 메모리 영역에 대한 리텐션 동작을 수행한다. 그리고 제 1 글로벌 타임(GTm)에서 마지막 리텐션 동작이 실행되고, T1 시점에서 저장 장치(120)는 호스트(110)로부터 전기적으로 분리된다.

T1 시점으로부터 T2 시점까지 저장 장치(120)가 호스트(110)와 전기적으로 분리되는 오프-라인 상태를 유지한다. T1 시점과 T2 시점 사이의 시간 차는 오프-라인 시간(ΔToff)에 대응한다. 그리고 T2 시점에 저장 장치(120)가 호스트(110)에 전기적으로 연결된다.

T2 시점에 저장 장치(120)가 호스트(110)에 연결되면, 저장 장치(120)는 온-라인 상태가 된다. 그러면, 호스트(110)로부터 제 1 글로벌 타임(GTn)을 제공받는다. 저장 장치(120)는 리텐션 동작 후에 저장된 제 2 글로벌 타임(GTm)과 온-라인 상태에서 최초로 전달받은 제 1 글로벌 타임(GTn)을 기반으로 오프-라인 시간(ΔToff)을 추정한다. 그리고 저장 장치(120)는 추정된 오프-라인 시간(ΔToff) 동안 수행되지 못한 리텐션 동작을 보상하기 위한 보상 리텐션 동작을 ΔT1 시간 동안 실시한다. 보상 리텐션 동작이 완료되면, 저장 장치(120)는 노말 리텐션 동작을 최초 설정된 리텐션 주기(ΔTn)에 따라 실행한다.

도 8은 본 발명의 일 실시 예에 따른 보상 리텐션 동작을 보여주는 타이밍도이다. 도 8을 참조하면, 오프-라인 상태에서 온-라인 상태로 전환되면, 저장 장치(120)는 오프-라인 동안 실행되지 못한 리텐션 동작을 일시에 실행한다. 좀더 자세히 설명하면 다음과 같다.

오프-라인 시간(ΔToff) 동안 전기적으로 호스트(110)와 분리 상태로 존재하던 저장 장치(120)가 T1 시점에 호스트(110)와 연결된다. 그러면, 저장 장치(120)는 호스트(110)로부터 제 1 글로벌 타임(GTn)을 수신한다. 그리고 저장 장치(120)는 오프-라인 이전에 수행된 마지막 리텐션 동작에 대한 정보(리텐션 정보)를 메타 영역에서 읽어낸다. 저장 장치(120)는 오프-라인 이전에 수행된 마지막 리텐션 동작 시점에 대응하는 제 2 글로벌 타임(GTm)을 리텐션 정보로부터 추출한다. 저장 장치(120)는 제 1 글로벌 타임(GTn) 및 제 2 글로벌 타임(GTm)을 참조하여 오프-라인 시간을 추정하고, 오프-라인 시간 동안 수행되지 못한 메모리 영역을 계산한다. 그리고 저장 장치(120)는 보상 리텐션 시간(ΔT1) 동안 오프-라인 시간 동안 수행되지 못한 리텐션 동작을 한꺼번에 실시한다. 보상 리텐션 시간(ΔT1) 동안, 보상 리텐션 동작이 완료되면, 저장 장치(120)는 노말 리텐션 동작을 실시한다.

도 9는 본 발명의 다른 실시 예에 따른 보상 리텐션 동작을 보여주는 타이밍도이다. 도 9를 참조하면, 오프-라인 상태에서 온-라인 상태로 전환되면, 저장 장치(120)는 오프-라인 동안 리텐션 동작이 수행되지 못한 메모리 영역을 파악한다. 그리고 파악된 메모리 영역의 크기에 따라 보상 리텐션 동작의 주기(ΔTc)를 결정한다. 결정된 보상 리텐션 주기(ΔTc)에 따라 보상 리텐션 동작을 실행하고, 그 이후에는 노말 리텐션 동작을 수행한다. 좀더 자세히 설명하면 다음과 같다.

오프-라인 시간(ΔToff) 동안 전기적으로 호스트(110)와 분리 상태로 존재하던 저장 장치(120)가 T1 시점에 호스트(110)와 연결된다. 그러면, 저장 장치(120)는 호스트(110)로부터 제 1 글로벌 타임(GTn)을 수신한다. 그리고 저장 장치(120)는 오프-라인 이전에 수행된 마지막 리텐션 동작에 대한 정보(리텐션 정보)를 메타 영역에서 읽어낸다. 저장 장치(120)는 오프-라인 이전에 수행된 마지막 리텐션 동작 시점에 대응하는 제 2 글로벌 타임(GTm)을 리텐션 정보로부터 추출한다. 저장 장치(120)는 제 1 글로벌 타임(GTn) 및 제 2 글로벌 타임(GTm)을 참조하여 오프-라인 시간을 추정하고, 오프-라인 시간 동안 리텐션 동작이 수행되지 못한 메모리 영역의 크기를 계산한다.

저장 장치(120)는 오프-라인 시간(ΔToff) 동안 리텐션 동작이 수행되지 못한 메모리 영역의 크기를 참조하여 보상 리텐션 동작을 위한 보상 리텐션 주기(ΔTc)를 계산한다. 만일, 오프-라인 시간(ΔToff)이 상대적으로 긴 경우, 리텐션 동작이 수행되지 못한 데이터 영역의 사이즈도 클 것이다. 이 경우에는 상대적으로 짧은 보상 리텐션 주기(ΔTc)가 결정되고, 보상 리텐션 시간(ΔT1) 동안 보상 리텐션 동작의 회수는 증가할 것이다. 반면, 오프-라인 시간(ΔToff)이 상대적으로 짧은 경우, 리텐션 동작이 수행되지 못한 데이터 영역의 사이즈는 작을 것이다. 이 경우에는 상대적으로 긴 보상 리텐션 주기(ΔTc)가 결정되고, 보상 리텐션 시간(ΔT1) 동안 보상 리텐션 동작의 회수는 감소할 것이다.

보상 리텐션 시간(ΔT1) 동안 보상 리텐션 동작이 완료되면, 저장 장치(120)는 노말 리텐션 동작을 실시한다.

도 10은 본 발명의 또 다른 실시 예에 따른 보상 리텐션 동작을 보여주는 타이밍도이다. 도 10을 참조하면, 오프-라인 상태에서 온-라인 상태로 전환되면, 저장 장치(120)는 오프-라인 동안 리텐션 동작이 수행되지 못한 메모리 영역을 파악한다. 그리고 파악된 메모리 영역의 크기에 따라 1회의 동작시에 리텐션 수행되는 메모리 사이즈를 결정한다. 좀더 자세히 설명하면 다음과 같다.

오프-라인 시간(ΔToff) 동안 전기적으로 호스트(110)와 분리 상태로 존재하던 저장 장치(120)가 T1 시점에 호스트(110)와 연결된다. 그러면, 저장 장치(120)는 호스트(110)로부터 제 1 글로벌 타임(GTn)을 수신한다. 그리고 저장 장치(120)는 오프-라인 이전에 수행된 마지막 리텐션 동작에 대한 정보(리텐션 정보)를 메타 영역에서 읽어낸다. 저장 장치(120)는 오프-라인 이전에 수행된 마지막 리텐션 동작 시점에 대응하는 제 2 글로벌 타임(GTm)을 리텐션 정보로부터 추출한다. 저장 장치(120)는 제 1 글로벌 타임(GTn) 및 제 2 글로벌 타임(GTm)을 참조하여 오프-라인 시간을 추정하고, 오프-라인 시간 동안 데이터 리텐션 동작이 수행되지 못한 메모리 영역의 크기를 계산한다.

저장 장치(120)는 오프-라인 시간(ΔToff) 동안 데이터 리텐션 동작이 수행되지 못한 메모리 영역의 크기를 참조하여 보상 리텐션 시간 중에 수행되는 1회의 보상 리텐션 동작시 처리되는 데이터 양을 결정한다. 만일, 상대적으로 오프-라인 시간(ΔToff)이 긴 경우, 데이터 리텐션 동작이 수행되지 못한 데이터 영역의 사이즈도 클 것이다. 이 경우에는 1회의 보상 리텐션 동작에 의해서 처리해야 할 데이터의 양은 증가할 것이다. 하지만, 보상 리텐션 시간(ΔT1) 동안 발생하는 보상 리텐션 동작의 주기(ΔTc)는 노말 리텐션 주기(ΔTn)와 동일하다.

반면, 오프-라인 시간(ΔToff)이 상대적으로 짧은 경우, 리텐션 동작이 수행되지 못한 데이터 영역의 사이즈는 작을 것이다. 이 경우에는 1회의 보상 리텐션 동작에 의해서 처리해야 할 데이터의 양은 감소할 것이다. 마찬가지로 보상 리텐션 시간(ΔT1) 동안 발생하는 보상 리텐션 동작의 주기(ΔTc)는 노말 리텐션 주기(ΔTn)와 동일하다.

상술한 보상 리텐션에 의해 처리되는 데이터의 양을 조정하는 실시 예에 따르면, 보상 리텐션 동작이나 노말 리텐션 동작의 주기는 변하지 않는다. 대신, 보상 리텐션 동작 시에는 1회의 리텐션 동작 시에 처리되는 데이터 양이 증가할 뿐이다.

도 11은 본 발명의 실시 예를 적용한 솔리드 스테이트 디스크(SSD) 시스템을 보여주는 블록도이다. 도 11을 참조하면, SSD 시스템(1000)은 호스트(1100)와 SSD(1200)를 포함한다. SSD(1200)는 SSD 컨트롤러(1210), 버퍼 메모리(1220), 그리고 불휘발성 메모리 장치(1230)를 포함한다.

SSD 컨트롤러(1210)는 호스트(1100)와 SSD(1200)와의 물리적 연결을 제공한다. 즉, SSD 컨트롤러(1210)는 호스트(1100)의 버스 포맷(Bus format)에 대응하여 SSD(1200)와의 인터페이싱을 제공한다. 특히, SSD 컨트롤러(1210)는 호스트(1100)로부터 제공되는 명령어를 디코딩한다. 디코딩된 결과에 따라, SSD 컨트롤러(1210)는 불휘발성 메모리 장치(1230)를 액세스한다. 호스트(1100)의 버스 포맷(Bus format)으로 USB(Universal Serial Bus), SCSI(Small Computer System Interface), PCI express, ATA, PATA(Parallel ATA), SATA(Serial ATA), SAS(Serial Attached SCSI) 등이 포함될 수 있다.

SSD 컨트롤러(1210)는 호스트(1100)로부터 제공되는 글로벌 타임(GT)을 참조하여 보상 리텐션 동작을 수행한다. SSD 컨트롤러(1210)는 온-라인 상태에서는 주기적으로 불휘발성 메모리 장치(1230)의 메모리 영역을 읽어내고 버퍼 메모리(1220)에 저장한다. 그리고 데이터가 읽혀진 메모리 영역을 소거한 후, 버퍼 메모리에 저장된 데이터를 소거된 영역에 재기입한다. 특히, 오프-라인 상태에서 온-라인 상태로 전환되는 시점에서, SSD 컨트롤러(1210)는 글로벌 타임에 기반하여 오프-라인 시간(Off-line time)을 계산하고, 계산된 오프-라인 시간을 기반으로 보상 리텐션 동작을 수행한다. 보상 리텐션 동작에 따라 불휘발성 메모리 장치(1230)에 저장된 데이터의 신뢰도가 향상될 수 있다.

버퍼 메모리(1220)에는 호스트(1100)로부터 제공되는 쓰기 데이터 또는 불휘발성 메모리 장치(1230)로부터 읽혀진 데이터가 일시 저장된다. 호스트(1100)의 읽기 요청시에 불휘발성 메모리 장치(1230)에 존재하는 데이터가 캐시되어 있는 경우에는, 버퍼 메모리(1220)는 캐시된 데이터를 직접 호스트(1100)로 제공하는 캐시 기능을 지원한다. 일반적으로, 호스트(1100)의 버스 포맷(예를 들면, SATA 또는 SAS)에 의한 데이터 전송 속도는 SSD(1200)의 메모리 채널의 전송 속도보다 월등히 빠르다. 즉, 호스트(1100)의 인터페이스 속도가 월등히 높은 경우, 대용량의 버퍼 메모리(1220)를 제공함으로써 속도 차이로 발생하는 퍼포먼스 저하를 최소화할 수 있다.

버퍼 메모리(1220)는 대용량의 보조 기억 장치로 사용되는 SSD(1200)에서 충분한 버퍼링을 제공하기 위해 동기식 DRAM(Synchronous DRAM)으로 제공될 수 있다. 하지만, 버퍼 메모리(1220)가 여기의 개시에 국한되지 않음은 이 분야의 통상적인 지식을 습득한 자들에게 자명하다.

불휘발성 메모리 장치(1230)는 SSD(1200)의 저장 매체로서 제공된다. 예를 들면, 불휘발성 메모리 장치(1230)는 대용량의 저장 능력을 가지는 낸드 플래시 메모리(NAND-type Flash memory)로 제공될 수 있다. 불휘발성 메모리 장치(1230)는 복수의 메모리 장치로 구성될 수 있다. 이 경우, 각각의 메모리 장치들은 채널 단위로 SSD 컨트롤러(1210)와 연결된다. 저장 매체로서 불휘발성 메모리 장치(1230)가 낸드 플래시 메모리를 예로 들어 설명되었으나, 또 다른 불휘발성 메모리 장치들로 구성될 수 있다. 예를 들면, 저장 매체로서 PRAM, MRAM, ReRAM, FRAM, NOR 플래시 메모리 등이 사용될 수 있으며, 이종의 메모리 장치들이 혼용되는 메모리 시스템도 적용될 수 있다. 그리고 저장 매체로서 휘발성 메모리 장치(예를 들면, DRAM)이 포함될 수도 있다.

도 12는 본 발명의 실시 예에 따른 메모리 카드의 예를 보여준다. 메모리 카드 시스템(2000)은 호스트(2100)와 메모리 카드(2200)를 포함한다. 호스트(2100)는 호스트 컨트롤러(2110) 및 호스트 접속 유닛(2120)을 포함한다. 메모리 카드(2200)는 카드 접속 유닛(2210), 카드 컨트롤러(2220), 그리고 플래시 메모리(2230)를 포함한다.

호스트 접속 유닛(2120) 및 카드 접속 유닛(2210)은 복수의 핀으로 구성된다. 이들 핀에는 커맨드 핀, 데이터 핀, 클록 핀, 전원 핀 등이 포함되어 있다. 핀의 수는 메모리 카드(2200)의 종류에 따라 달라진다. 예로서, SD 카드는 9개의 핀을 가질 수 있다.

호스트(2100)는 메모리 카드(2200)에 데이터를 쓰거나, 메모리 카드(2200)에 저장된 데이터를 읽는다. 호스트 컨트롤러(2110)는 커맨드(예를 들면, 쓰기 커맨드), 호스트(2100) 내의 클록 발생기(도시되지 않음)에서 발생한 클록 신호(CLK), 그리고 데이터(DATA)를 호스트 접속 유닛(2120)을 통해 메모리 카드(2200)로 전송한다. 특히, 호스트(1210)는 주기적으로 또는 메모리 카드(2200)가 온-라인 상태로 전환되는 초기에 글로벌 타임(GT)을 제공한다.

카드 컨트롤러(2220)는 카드 접속 유닛(2210)을 통해 수신된 쓰기 커맨드에 응답하여, 카드 컨트롤러(2220) 내에 있는 클록 발생기(도시되지 않음)에서 발생한 클록 신호에 동기하여 데이터를 메모리(2230)에 저장한다. 메모리(2230)는 호스트(2100)로부터 전송된 데이터를 저장한다. 예를 들어, 호스트(2100)가 디지털 카메라인 경우에는 영상 데이터를 저장한다.

카드 컨트롤러(2220)는 호스트(2100)로부터 제공되는 글로벌 타임(GT)을 참조하여 보상 리텐션 동작을 수행한다. 카드 컨트롤러(2220)는 온-라인 상태에서는 주기적으로 플래시 메모리 장치(2230)의 메모리 영역들에 대한 리텐션 동작을 수행한다. 그리고 오프-라인 상태에서 온-라인 상태로 전환되는 시점에서, 카드 컨트롤러(2220)는 글로벌 타임에 기반하여 오프-라인 시간(Off-line time)을 계산하고, 계산된 오프-라인 시간을 기반으로 보상 리텐션 동작을 수행한다. 보상 리텐션 동작에 따라 플래시 메모리 장치(2230)에 저장된 데이터의 신뢰도가 향상될 수 있다.

카드 접속 유닛(2210) USB, MMC, PCI-E, SAS, SATA, PATA, SCSI, ESDI, 그리고 IDE 등과 같은 다양한 인터페이스 프로토콜들 중 하나를 통해 외부(예를 들면, 호스트)와 통신하도록 구성될 것이다.

도 13은 본 발명의 글로벌 타임에 기반한 리텐션 동작을 수행하는 퓨전 메모리 장치(3000)를 간략히 보여주는 블록도이다. 예를 들면, 퓨전 메모리 장치로서 원낸드 플래시 메모리 장치에 본 발명의 기술적 특징이 적용될 수 있다. 도 13을 참조하면, 호스트(Host)는 본 발명의 퓨전 메모리 장치(3000)에 글로벌 타임(GT)을 제공한다. 그리고 퓨전 메모리 장치(3000)는 글로벌 타임에 근거하여 오프-라인 시점에 수행되지 못한 리텐션 동작을 보상할 수 있다.

퓨전 메모리 장치(3000)는 서로 다른 프로토콜을 사용하는 장치와의 각종 정보 교환을 위한 호스트 인터페이스(3100)와, 메모리 장치를 구동하기 위한 코드를 내장하거나 데이터를 일시적으로 저장하는 버퍼 램(3200)과, 외부에서 주어지는 제어 신호와 명령어에 응답하여 읽기와 프로그램 및 모든 상태를 제어하는 제어부(3300)와, 명령어와 어드레스, 메모리 장치 내부의 시스템 동작 환경을 정의하는 설정(Configuration) 등의 데이터가 저장되는 레지스터(3400) 및 불휘발성 메모리 셀과 페이지 버퍼로 구성된 낸드 셀 어레이(3500)를 포함한다.

제어부(3300)는 호스트(Host)로부터 제공되는 글로벌 타임(GT)을 참조하여 보상 리텐션 동작을 수행한다. 제어부(3300)는 온-라인 상태에서는 주기적으로 낸드 셀 어레이(3500)의 메모리 영역들에 대한 리텐션 동작을 수행한다. 그리고 오프-라인 상태에서 온-라인 상태로 전환되는 시점에서, 제어부(3300)는 글로벌 타임에 기반하여 오프-라인 시간(Off-line time)을 계산하고, 계산된 오프-라인 시간을 기반으로 보상 리텐션 동작을 수행한다. 보상 리텐션 동작에 따라 낸드 셀 어레이(3500)에 저장된 데이터의 신뢰도가 향상될 수 있다.

도 14에는 본 발명의 실시 예가 적용될 수 있는 컴퓨팅 시스템(4000)이 개략적으로 도시되어 있다. 본 발명에 따른 컴퓨팅 시스템(4000)은 시스템 버스(4700)에 전기적으로 연결된 메모리 시스템(4100), 마이크로프로세서(4200), 램(4300), 사용자 인터페이스(4400), 베이스밴드 칩셋(Baseband chipset)과 같은 모뎀(4500) 및 네트워크 어뎁터(4600)를 포함한다. 메모리 시스템(4100)은 도 11, 도 12, 도 13에 도시된 것과 실질적으로 동일하게 구성될 것이다. 본 발명에 따른 컴퓨팅 시스템(4000)이 모바일 장치인 경우, 컴퓨팅 시스템(4000)의 동작 전압을 공급하기 위한 배터리(미도시됨)가 추가적으로 제공될 것이다. 비록 도면에는 도시되지 않았지만, 본 발명에 따른 컴퓨팅 시스템(4000)에는 응용 칩세트(Application chipset), 카메라 이미지 프로세서(Camera Image Processor: CIS), 모바일 디램, 등이 더 제공될 수 있음은 이 분야의 통상적인 지식을 습득한 자들에게 자명하다. 메모리 시스템(4100)은, 예를 들면, 데이터를 저장하는 데 불휘발성 메모리를 사용하는 SSD(Solid State Drive/Disk)를 구성할 수 있다.

메모리 컨트롤러(4110)는 네트워크 어뎁터(4600)를 통해서 제공되는 글로벌 타임(GT)을 참조하여 보상 리텐션 동작을 수행한다. 메모리 컨트롤러(4110)는 온-라인 상태에서는 주기적으로 플래시 메모리(4120)의 메모리 영역들에 대한 리텐션 동작을 수행한다. 그리고 오프-라인 상태에서 온-라인 상태로 전환되는 시점에서, 메모리 컨트롤러(4110)는 글로벌 타임에 기반하여 오프-라인 시간(Off-line time)을 계산하고, 계산된 오프-라인 시간을 기반으로 보상 리텐션 동작을 수행한다. 보상 리텐션 동작에 따라 플래시 메모리(4120)에 저장된 데이터의 신뢰도가 향상될 수 있다.

본 발명에 따른 불휘발성 메모리 장치 그리고/또는 메모리 컨트롤러는 다양한 형태들의 패키지를 이용하여 실장될 수 있다. 예를 들면, 본 발명에 따른 플래시 메모리 장치 그리고/또는 메모리 컨트롤러는 PoP(Package on Package), Ball grid arrays(BGAs), Chip scale packages(CSPs), Plastic Leaded Chip Carrier(PLCC), Plastic Dual In-Line Package(PDIP), Die in Waffle Pack, Die in Wafer Form, Chip On Board(COB), Ceramic Dual In-Line Package(CERDIP), Plastic Metric Quad Flat Pack(MQFP), Thin Quad Flatpack(TQFP), Small Outline(SOIC), Shrink Small Outline Package(SSOP), Thin Small Outline(TSOP), Thin Quad Flatpack(TQFP), System In Package(SIP), Multi Chip Package(MCP), Wafer-level Fabricated Package(WFP), Wafer-Level Processed Stack Package(WSP), 등과 같은 패키지들을 이용하여 실장될 수 있다.

이상에서와 같이 도면과 명세서에서 최적 실시 예가 개시되었다. 여기서 특정한 용어들이 사용되었으나, 이는 단지 본 발명을 설명하기 위한 목적에서 사용된 것이지 의미 한정이나 특허청구범위에 기재된 본 발명의 범위를 제한하기 위하여 사용된 것은 아니다. 그러므로 본 기술 분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시 예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호 범위는 첨부된 특허청구범위의 기술적 사상에 의해 정해져야 할 것이다.

110 : 호스트 120 : 저장 장치

210 : 메모리 컨트롤러 212 : 글로벌 타임 매니저

214 : 리텐션 매니저 216 : 버퍼 메모리

220 : 불휘발성 메모리 장치 222 : 셀 어레이

224 : 페이지 버퍼 1100 : 호스트

1200 : SSD 1210 : SSD 컨트롤러

1220 : 버퍼 메모리 1230 : 불휘발성 메모리 장치

2100 : 호스트 2110 : 호스트 컨트롤러

2120 : 호스트 접속 유닛 2200 : 메모리 카드

2210 : 카드 접속 유닛 2220 : 카드 컨트롤러

2230 : 플래시 메모리 3100 : 호스트 인터페이스

3200 : 버퍼 램 3300 : 제어부

3400 : 레지스터 3500 : 낸드 셀 어레이

4100 : 메모리 시스템 4110 : 메모리 컨트롤러

4120 : 플래시 메모리 장치 4200 : 중앙처리장치

4300 : 램 4400 : 유저 인터페이스

4500 : 모뎀 4600 : 네트워크 어뎁터

4700 : 시스템 버스

210 : 메모리 컨트롤러 212 : 글로벌 타임 매니저

214 : 리텐션 매니저 216 : 버퍼 메모리

220 : 불휘발성 메모리 장치 222 : 셀 어레이

224 : 페이지 버퍼 1100 : 호스트

1200 : SSD 1210 : SSD 컨트롤러

1220 : 버퍼 메모리 1230 : 불휘발성 메모리 장치

2100 : 호스트 2110 : 호스트 컨트롤러

2120 : 호스트 접속 유닛 2200 : 메모리 카드

2210 : 카드 접속 유닛 2220 : 카드 컨트롤러

2230 : 플래시 메모리 3100 : 호스트 인터페이스

3200 : 버퍼 램 3300 : 제어부

3400 : 레지스터 3500 : 낸드 셀 어레이

4100 : 메모리 시스템 4110 : 메모리 컨트롤러

4120 : 플래시 메모리 장치 4200 : 중앙처리장치

4300 : 램 4400 : 유저 인터페이스

4500 : 모뎀 4600 : 네트워크 어뎁터

4700 : 시스템 버스

Claims (24)

- 저장 장치의 데이터 리텐션 방법에 있어서:

호스트로부터 글로벌 타임(Global time)을 제공받는 단계; 그리고

상기 글로벌 타임(Global time)을 참조하여 저장 데이터를 주기적으로 리프레쉬하는 단계를 포함하는 데이터 리텐션 방법. - 제 1 항에 있어서,

상기 호스트는 상기 저장 장치가 연결된 온-라인 상태에서 상기 글로벌 타임을 주기적으로 또는 적어도 1회 제공하는 데이터 리텐션 방법. - 제 1 항에 있어서,

상기 리프레쉬 단계는, 상기 저장 데이터의 리프레쉬 결과를 리텐션 정보로 저장하는 단계를 더 포함하는 데이터 리텐션 방법. - 제 3 항에 있어서,

상기 리텐션 정보에는 상기 내부 데이터가 저장된 메모리 영역의 위치 정보, 상기 내부 데이터가 리프레쉬된 시각 정보, 후속 리프레쉬 대상 메모리 영역의 위치 정보들 중 적어도 하나를 포함하는 데이터 리텐션 방법. - 제 4 항에 있어서,

상기 리텐션 단계는,

상기 호스트로부터 제 1 글로벌 타임을 제공받는 단계;

상기 저장 장치가 오프-라인(Off-line)되기 이전에 저장된 리텐션 정보로부터 제 2 글로벌 타임을 읽는 단계; 그리고

상기 제 1 및 제 2 글로벌 타임을 참조하여 상기 오프-라인 시간 동안 리텐션 처리되지 못한 메모리 영역을 파악하는 단계를 포함하는 데이터 리텐션 방법. - 제 5 항에 있어서,

상기 오프-라인 시간 동안 처리되지 못한 메모리 영역에 대한 리텐션 동작을 보상하기 위한 보상 리텐션 단계를 더 포함하는 데이터 리텐션 방법. - 제 6 항에 있어서,

상기 보상 리텐션 단계에서, 상기 오프-라인 시간 동안 처리되지 못한 메모리 영역에 대한 리텐션 처리는 한꺼번에 수행되는 데이터 리텐션 방법. - 제 6 항에 있어서,

상기 보상 리텐션 단계에서, 상기 오프-라인 시간 동안 처리되지 못한 메모리 영역에 대한 리텐션 처리는 조정된 리프레쉬 주기에 따라 실시되는 데이터 리텐션 방법. - 제 6 항에 있어서,

상기 보상 리텐션 단계에서, 상기 오프-라인 시간 동안 처리되지 못한 메모리 영역에 대한 리텐션 처리는 상기 리프레쉬 주기에 따라 실시되되, 1회의 리프레쉬 동작 동안에 처리되는 데이터 양이 가변되는 데이터 리텐션 방법. - 글로벌 타임을 전송하는 호스트; 그리고

상기 글로벌 타임을 참조하여 저장 데이터를 주기적으로 리프레쉬하는 저장 장치를 포함하는 사용자 장치. - 제 10 항에 있어서,

상기 호스트는 상기 글로벌 타임을 주기적으로 전송하거나, 또는 상기 저장 장치가 전기적으로 접속된 온-라인 상태에서 적어도 1회 전송하는 사용자 장치. - 제 10 항에 있어서,

상기 저장 장치는 리프레쉬된 데이터의 위치 정보와 시간 정보를 포함하는 리텐션 정보를 메타 데이터 영역에 업데이트하는 사용자 장치. - 제 12 항에 있어서,

상기 저장 장치가 상기 호스트에 연결(On-line)되는 경우, 오프-라인 시간 동안 리프레쉬되지 못한 메모리 영역에 대한 리텐션 처리를 상기 글로벌 타임을 참조하여 수행하는 사용자 장치. - 제 13 항에 있어서,

상기 저장 장치는 상기 글로벌 타임을 참조하여 상기 오프-라인 시간을 추정하고, 상기 리프레쉬되지 못한 메모리 영역을 검출하는 사용자 장치. - 제 14 항에 있어서,

상기 저장 장치는, 상기 리프레쉬되지 못한 메모리 영역을 상기 온-라인 상태의 초기에 한꺼번에 리프레쉬하는 사용자 장치. - 제 14 항에 있어서,

상기 저장 장치는 상기 리프레쉬되지 못한 메모리 영역을 상기 온-라인 상태의 초기에 분산하여 리프레쉬하는 사용자 장치. - 제 16 항에 있어서,

상기 저장 장치는 상기 리프레쉬되지 못한 메모리 영역의 사이즈에 따라 리프레쉬 주기를 조정하는 사용자 장치. - 제 16 항에 있어서,

상기 저장 장치는 상기 리프레쉬되지 못한 영역의 사이즈에 따라 한번에 리프레쉬되는 메모리 양을 조정하는 사용자 장치. - 불휘발성 메모리 장치; 그리고

호스트로부터 제공되는 글로벌 타임에 기반하여 상기 불휘발성 메모리 장치에 저장된 데이터를 주기적으로 리프레쉬하는 메모리 컨트롤러를 포함하되,

상기 호스트에 전기적으로 접속되면, 상기 메모리 컨트롤러는 상기 글로벌 타임을 참조하여 상기 호스트와 전기적으로 분리된 오프-라인 시간을 계산하고, 상기 오프-라인 시간 동안 중단된 리프레쉬 동작을 보상하는 저장 장치. - 제 19 항에 있어서,

상기 호스트는 상기 저장 장치에 상기 글로벌 타임을 주기적으로 또는 적어도 1회 제공하는 저장 장치. - 제 19 항에 있어서,

상기 오프-라인 시간에 따라 상기 중단된 리프레쉬 동작의 대상이 되는 메모리 영역이 선택되는 저장 장치. - 제 19 항에 있어서,

상기 메모리 컨트롤러는, 상기 호스트로부터 제공되는 제 1 글로벌 타임과, 상기 저장 장치가 오프-라인(Off-line) 이전에 마지막으로 수행된 리프레쉬 동작이 이력으로부터 제공되는 제 2 글로벌 타임으로부터 상기 오프-라인 시간을 계산하는 저장 장치. - 제 19 항에 있어서,

상기 메모리 컨트롤러는 상기 오프-라인 시간 동안 중단된 리프레쉬 동작을 한꺼번에 실행하는 저장 장치. - 제 19 항에 있어서,

상기 메모리 컨트롤러는 상기 오프-라인 시간 동안 중단된 리프레쉬 동작을 보상 리프레쉬 주기에 따라 분산하여 처리하는 저장 장치.

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020110012009A KR20120091906A (ko) | 2011-02-10 | 2011-02-10 | 데이터 리텐션 동작을 수행하는 사용자 장치, 저장 장치, 그리고 그것의 데이터 리텐션 방법 |

| DE102011056139A DE102011056139A1 (de) | 2011-02-10 | 2011-12-07 | Benutzergerät zum Durchführen eines Datenretentionsvorgangs, sowie Speichervorrichtung und Datenretentionsverfahren |

| JP2011286257A JP2012168927A (ja) | 2011-02-10 | 2011-12-27 | データリテンション動作を実行する使用者装置、データ格納装置、及びそれのデータリテンション方法 |

| CN2011104592866A CN102637154A (zh) | 2011-02-10 | 2011-12-31 | 执行数据保持操作的用户器件、存储器件以及数据保持方法 |

| US13/352,402 US20120210076A1 (en) | 2011-02-10 | 2012-01-18 | User device performing data retention operation, storage device and data retention method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020110012009A KR20120091906A (ko) | 2011-02-10 | 2011-02-10 | 데이터 리텐션 동작을 수행하는 사용자 장치, 저장 장치, 그리고 그것의 데이터 리텐션 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20120091906A true KR20120091906A (ko) | 2012-08-20 |

Family

ID=46579715

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020110012009A KR20120091906A (ko) | 2011-02-10 | 2011-02-10 | 데이터 리텐션 동작을 수행하는 사용자 장치, 저장 장치, 그리고 그것의 데이터 리텐션 방법 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US20120210076A1 (ko) |

| JP (1) | JP2012168927A (ko) |

| KR (1) | KR20120091906A (ko) |

| CN (1) | CN102637154A (ko) |

| DE (1) | DE102011056139A1 (ko) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10572158B2 (en) | 2015-11-20 | 2020-02-25 | Samsung Electroncis Co., Ltd. | Method of operating storage device to recover performance degradation due to retention characteristic and method of operating data processing system including the same |

| KR102408829B1 (ko) * | 2021-11-09 | 2022-06-14 | 삼성전자주식회사 | 리텐션 강화를 위한 스토리지 장치의 구동 방법 및 이를 수행하는 스토리지 장치 |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8966343B2 (en) * | 2012-08-21 | 2015-02-24 | Western Digital Technologies, Inc. | Solid-state drive retention monitor using reference blocks |

| JP2015064860A (ja) | 2013-08-27 | 2015-04-09 | キヤノン株式会社 | 画像形成装置およびその制御方法、並びにプログラム |

| JP2015132937A (ja) * | 2014-01-10 | 2015-07-23 | ソニー株式会社 | 情報処理装置、情報処理方法および記録媒体 |

| CN106098103B (zh) * | 2016-06-03 | 2019-10-18 | 北京兆易创新科技股份有限公司 | 一种非易失性存储器中坏点单元的替换方法 |

| KR102244921B1 (ko) | 2017-09-07 | 2021-04-27 | 삼성전자주식회사 | 저장 장치 및 그 리프레쉬 방법 |

| CN110838314A (zh) * | 2018-08-17 | 2020-02-25 | 北京兆易创新科技股份有限公司 | 一种存储数据的加固方法及装置 |

| KR20200129467A (ko) | 2019-05-08 | 2020-11-18 | 삼성전자주식회사 | 스토리지 컨트롤러 및 이를 포함하는 스토리지 장치 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW521188B (en) * | 2001-08-03 | 2003-02-21 | Via Tech Inc | Automatic updating method for terminal display page and the computer program thereof |

| US20100138588A1 (en) * | 2008-12-02 | 2010-06-03 | Silicon Storage Technology, Inc. | Memory controller and a method of operating an electrically alterable non-volatile memory device |

| KR20110012009A (ko) | 2009-07-29 | 2011-02-09 | 엘지전자 주식회사 | 공기조화기의 전동기 제어장치 |

| US9258201B2 (en) * | 2010-02-23 | 2016-02-09 | Trane International Inc. | Active device management for use in a building automation system |

-

2011

- 2011-02-10 KR KR1020110012009A patent/KR20120091906A/ko not_active Application Discontinuation

- 2011-12-07 DE DE102011056139A patent/DE102011056139A1/de not_active Withdrawn

- 2011-12-27 JP JP2011286257A patent/JP2012168927A/ja not_active Withdrawn

- 2011-12-31 CN CN2011104592866A patent/CN102637154A/zh active Pending

-

2012

- 2012-01-18 US US13/352,402 patent/US20120210076A1/en not_active Abandoned

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10572158B2 (en) | 2015-11-20 | 2020-02-25 | Samsung Electroncis Co., Ltd. | Method of operating storage device to recover performance degradation due to retention characteristic and method of operating data processing system including the same |

| KR102408829B1 (ko) * | 2021-11-09 | 2022-06-14 | 삼성전자주식회사 | 리텐션 강화를 위한 스토리지 장치의 구동 방법 및 이를 수행하는 스토리지 장치 |

Also Published As

| Publication number | Publication date |

|---|---|

| DE102011056139A1 (de) | 2012-08-16 |

| US20120210076A1 (en) | 2012-08-16 |

| JP2012168927A (ja) | 2012-09-06 |

| CN102637154A (zh) | 2012-08-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20120091906A (ko) | 데이터 리텐션 동작을 수행하는 사용자 장치, 저장 장치, 그리고 그것의 데이터 리텐션 방법 | |

| US11216323B2 (en) | Solid state memory system with low power error correction mechanism and method of operation thereof | |

| US9916087B2 (en) | Method and system for throttling bandwidth based on temperature | |

| KR102072829B1 (ko) | 저장 장치 및 그것을 포함하는 데이터 저장 시스템의 글로벌 가비지 컬렉션 방법 | |

| US20170040057A1 (en) | Nonvolatile memory module having backup function | |

| US10649692B2 (en) | Storage device, system including the same and method of operating the same | |

| KR102351660B1 (ko) | 전력 관리 메커니즘을 갖는 솔리드 스테이트 메모리 시스템 및 그것의 동작 방법 | |

| TWI677783B (zh) | 記憶體裝置及用於向該記憶體裝置提供能源資訊的方法及系統 | |

| KR20140044070A (ko) | 버퍼 메모리 장치를 포함하는 데이터 저장 장치 | |

| US10254979B1 (en) | Relocating or aborting a block of data by a host, based on media policies managed by a storage device | |

| US9235509B1 (en) | Write amplification reduction by delaying read access to data written during garbage collection | |

| US11803436B2 (en) | Storage device and storage system including the same | |

| KR20210098717A (ko) | 컨트롤러, 컨트롤러의 동작 방법 및 이를 포함하는 저장 장치 | |

| US20230195338A1 (en) | Memory system for updating firmware when spo occurs and operating method thereof | |

| KR20160007988A (ko) | 런 타임 배드 셀을 관리하는 스토리지 시스템 | |

| KR20200076431A (ko) | 메모리 컨트롤러 및 메모리 시스템의 동작 방법, 및 메모리 시스템 | |

| TW202004505A (zh) | 用於在突然斷電時降低功率消耗之資料儲存方法和資料儲存設備 | |

| US20230359399A1 (en) | Ufs device for transmitting status information through afc frame and operating method thereof | |

| KR20200114052A (ko) | 컨트롤러, 메모리 시스템 및 그것의 동작 방법 | |

| KR20200114212A (ko) | 데이터 저장 장치 및 그것의 동작 방법 | |

| CN115705872A (zh) | 触发对非易失性存储器的刷新 | |

| US20170123687A1 (en) | Operating method for host device and memory system including host device and storage device | |

| KR20210012123A (ko) | 메모리 시스템, 메모리 컨트롤러 및 동작 방법 | |

| US11556268B2 (en) | Cache based flow for a simple copy command | |

| US10515693B1 (en) | Data storage apparatus and operating method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |