KR20110081942A - 기판 전체에 걸쳐 향상된 균일성을 지닌 임베딩된 si/ge물질을 구비한 트랜지스터 - Google Patents

기판 전체에 걸쳐 향상된 균일성을 지닌 임베딩된 si/ge물질을 구비한 트랜지스터 Download PDFInfo

- Publication number

- KR20110081942A KR20110081942A KR1020117005498A KR20117005498A KR20110081942A KR 20110081942 A KR20110081942 A KR 20110081942A KR 1020117005498 A KR1020117005498 A KR 1020117005498A KR 20117005498 A KR20117005498 A KR 20117005498A KR 20110081942 A KR20110081942 A KR 20110081942A

- Authority

- KR

- South Korea

- Prior art keywords

- forming

- gate electrode

- transistor

- semiconductor

- cavities

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000000463 material Substances 0.000 title claims description 34

- 239000000758 substrate Substances 0.000 title claims description 26

- 238000000034 method Methods 0.000 claims abstract description 175

- 239000004065 semiconductor Substances 0.000 claims abstract description 105

- 230000008569 process Effects 0.000 claims abstract description 102

- 229910045601 alloy Inorganic materials 0.000 claims abstract description 40

- 239000000956 alloy Substances 0.000 claims abstract description 40

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 claims abstract description 30

- 238000003631 wet chemical etching Methods 0.000 claims abstract description 25

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims abstract description 24

- 239000000377 silicon dioxide Substances 0.000 claims abstract description 12

- 235000012239 silicon dioxide Nutrition 0.000 claims abstract description 12

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 32

- 239000010703 silicon Substances 0.000 claims description 31

- 229910052710 silicon Inorganic materials 0.000 claims description 24

- 239000007772 electrode material Substances 0.000 claims description 21

- 239000002019 doping agent Substances 0.000 claims description 20

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 claims description 12

- 229910052732 germanium Inorganic materials 0.000 claims description 11

- 230000001965 increasing effect Effects 0.000 claims description 10

- 239000000126 substance Substances 0.000 claims description 10

- 238000005468 ion implantation Methods 0.000 claims description 5

- 230000001939 inductive effect Effects 0.000 claims description 4

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 claims 2

- 238000005530 etching Methods 0.000 abstract description 34

- 239000010410 layer Substances 0.000 description 56

- 238000004519 manufacturing process Methods 0.000 description 29

- 125000006850 spacer group Chemical group 0.000 description 22

- 238000000151 deposition Methods 0.000 description 12

- 230000008021 deposition Effects 0.000 description 11

- 239000002210 silicon-based material Substances 0.000 description 8

- 229910000927 Ge alloy Inorganic materials 0.000 description 7

- 229910000676 Si alloy Inorganic materials 0.000 description 7

- 238000002513 implantation Methods 0.000 description 7

- 238000002955 isolation Methods 0.000 description 7

- 238000012545 processing Methods 0.000 description 7

- 239000002800 charge carrier Substances 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- 230000008901 benefit Effects 0.000 description 4

- 230000007246 mechanism Effects 0.000 description 4

- 238000000059 patterning Methods 0.000 description 4

- 230000009467 reduction Effects 0.000 description 4

- 235000012431 wafers Nutrition 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 230000006978 adaptation Effects 0.000 description 3

- 238000007796 conventional method Methods 0.000 description 3

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 3

- 239000002243 precursor Substances 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- CPELXLSAUQHCOX-UHFFFAOYSA-N Hydrogen bromide Chemical compound Br CPELXLSAUQHCOX-UHFFFAOYSA-N 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- 229910001128 Sn alloy Inorganic materials 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 230000009286 beneficial effect Effects 0.000 description 2

- 229910021419 crystalline silicon Inorganic materials 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 239000007943 implant Substances 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 230000000873 masking effect Effects 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 238000005275 alloying Methods 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 238000000429 assembly Methods 0.000 description 1

- 230000000712 assembly Effects 0.000 description 1

- 238000010923 batch production Methods 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000003575 carbonaceous material Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 229910000042 hydrogen bromide Inorganic materials 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 239000006259 organic additive Substances 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical group [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/01—Manufacture or treatment

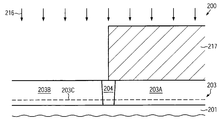

- H10D62/021—Forming source or drain recesses by etching e.g. recessing by etching and then refilling

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/40—Crystalline structures

- H10D62/405—Orientations of crystalline planes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/82—Heterojunctions

- H10D62/822—Heterojunctions comprising only Group IV materials heterojunctions, e.g. Si/Ge heterojunctions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0167—Manufacturing their channels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/017—Manufacturing their source or drain regions, e.g. silicided source or drain regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102008049723A DE102008049723B4 (de) | 2008-09-30 | 2008-09-30 | Transistor mit eingebettetem Si/Ge-Material mit einer besseren substratüberspannenden Gleichmäßigkeit |

| DE102008049723.1 | 2008-09-30 | ||

| US12/562,437 US8183100B2 (en) | 2008-09-30 | 2009-09-18 | Transistor with embedded SI/GE material having enhanced across-substrate uniformity |

| US12/562,437 | 2009-09-18 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20110081942A true KR20110081942A (ko) | 2011-07-15 |

Family

ID=41794956

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020117005498A Withdrawn KR20110081942A (ko) | 2008-09-30 | 2009-09-29 | 기판 전체에 걸쳐 향상된 균일성을 지닌 임베딩된 si/ge물질을 구비한 트랜지스터 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US8183100B2 (enExample) |

| JP (1) | JP5798923B2 (enExample) |

| KR (1) | KR20110081942A (enExample) |

| CN (1) | CN102160159A (enExample) |

| DE (1) | DE102008049723B4 (enExample) |

| WO (1) | WO2010037522A1 (enExample) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102008049723B4 (de) * | 2008-09-30 | 2012-01-26 | Advanced Micro Devices, Inc. | Transistor mit eingebettetem Si/Ge-Material mit einer besseren substratüberspannenden Gleichmäßigkeit |

| US8492234B2 (en) | 2010-06-29 | 2013-07-23 | International Business Machines Corporation | Field effect transistor device |

| US9006052B2 (en) | 2010-10-11 | 2015-04-14 | International Business Machines Corporation | Self aligned device with enhanced stress and methods of manufacture |

| DE102010064282B4 (de) * | 2010-12-28 | 2012-09-06 | GLOBALFOUNDRIES Dresden Module One Ltd. Liability Company & Co. KG | Transistor mit eingebetteten sigma-förmigen sequenziell hergestellten Halbleiterlegierungen |

| US9018065B2 (en) * | 2012-05-08 | 2015-04-28 | Globalfoundries Inc. | Horizontal epitaxy furnace for channel SiGe formation |

| US9054217B2 (en) | 2013-09-17 | 2015-06-09 | Samsung Electronics Co., Ltd. | Method for fabricating semiconductor device having an embedded source/drain |

| CN105161406B (zh) * | 2014-06-12 | 2019-04-26 | 中芯国际集成电路制造(上海)有限公司 | 晶体管及其形成方法 |

| US11217486B2 (en) * | 2018-10-31 | 2022-01-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor device and method |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6376481A (ja) * | 1986-09-19 | 1988-04-06 | Hitachi Ltd | 半導体装置及びその製造方法 |

| US5716218A (en) * | 1991-06-04 | 1998-02-10 | Micron Technology, Inc. | Process for manufacturing an interconnect for testing a semiconductor die |

| US5414276A (en) * | 1993-10-18 | 1995-05-09 | The Regents Of The University Of California | Transistors using crystalline silicon devices on glass |

| US6372618B2 (en) * | 2000-01-06 | 2002-04-16 | Micron Technology, Inc. | Methods of forming semiconductor structures |

| AU2003264342A1 (en) * | 2002-08-28 | 2004-03-19 | National Institute Of Advanced Industrial Science And Technology | Double-gate type mos field effect transistor and production method therefor |

| JP4046014B2 (ja) * | 2003-05-30 | 2008-02-13 | 株式会社デンソー | 構造体の製造方法 |

| US7045407B2 (en) * | 2003-12-30 | 2006-05-16 | Intel Corporation | Amorphous etch stop for the anisotropic etching of substrates |

| US6946350B2 (en) * | 2003-12-31 | 2005-09-20 | Intel Corporation | Controlled faceting of source/drain regions |

| JP4837902B2 (ja) * | 2004-06-24 | 2011-12-14 | 富士通セミコンダクター株式会社 | 半導体装置 |

| US20060091483A1 (en) * | 2004-11-02 | 2006-05-04 | Doczy Mark L | Method for making a semiconductor device with a high-k gate dielectric layer and a silicide gate electrode |

| JP4369359B2 (ja) * | 2004-12-28 | 2009-11-18 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置 |

| US7494858B2 (en) * | 2005-06-30 | 2009-02-24 | Intel Corporation | Transistor with improved tip profile and method of manufacture thereof |

| JP2007019129A (ja) * | 2005-07-06 | 2007-01-25 | Renesas Technology Corp | 半導体装置の製造方法及び半導体装置 |

| DE102005051994B4 (de) * | 2005-10-31 | 2011-12-01 | Globalfoundries Inc. | Verformungsverfahrenstechnik in Transistoren auf Siliziumbasis unter Anwendung eingebetteter Halbleiterschichten mit Atomen mit einem großen kovalenten Radius |

| JP2007157788A (ja) * | 2005-11-30 | 2007-06-21 | Toshiba Corp | 半導体装置 |

| US7691752B2 (en) * | 2007-03-30 | 2010-04-06 | Intel Corporation | Methods of forming improved EPI fill on narrow isolation bounded source/drain regions and structures formed thereby |

| DE102008049723B4 (de) * | 2008-09-30 | 2012-01-26 | Advanced Micro Devices, Inc. | Transistor mit eingebettetem Si/Ge-Material mit einer besseren substratüberspannenden Gleichmäßigkeit |

-

2008

- 2008-09-30 DE DE102008049723A patent/DE102008049723B4/de active Active

-

2009

- 2009-09-18 US US12/562,437 patent/US8183100B2/en active Active

- 2009-09-29 JP JP2011528255A patent/JP5798923B2/ja active Active

- 2009-09-29 WO PCT/EP2009/007001 patent/WO2010037522A1/en not_active Ceased

- 2009-09-29 CN CN2009801362115A patent/CN102160159A/zh active Pending

- 2009-09-29 KR KR1020117005498A patent/KR20110081942A/ko not_active Withdrawn

-

2012

- 2012-04-24 US US13/454,177 patent/US8334569B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| DE102008049723A1 (de) | 2010-04-08 |

| US8183100B2 (en) | 2012-05-22 |

| JP2012504326A (ja) | 2012-02-16 |

| CN102160159A (zh) | 2011-08-17 |

| DE102008049723B4 (de) | 2012-01-26 |

| WO2010037522A1 (en) | 2010-04-08 |

| JP5798923B2 (ja) | 2015-10-21 |

| US20120211810A1 (en) | 2012-08-23 |

| US20100078691A1 (en) | 2010-04-01 |

| US8334569B2 (en) | 2012-12-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101537079B1 (ko) | 점진적으로 만들어진 형태의 구성을 가지는 매립 스트레인 유도 물질을 갖는 트랜지스터 | |

| US7586153B2 (en) | Technique for forming recessed strained drain/source regions in NMOS and PMOS transistors | |

| US8093634B2 (en) | In situ formed drain and source regions in a silicon/germanium containing transistor device | |

| US8906811B2 (en) | Shallow pn junction formed by in situ doping during selective growth of an embedded semiconductor alloy by a cyclic growth/etch deposition process | |

| US8138050B2 (en) | Transistor device comprising an asymmetric embedded semiconductor alloy | |

| US8124467B2 (en) | Reducing silicide resistance in silicon/germanium-containing drain/source regions of transistors | |

| CN101322228B (zh) | 通过倾斜式预非晶化而减少受应变的晶体管中的晶体缺陷的技术 | |

| US20140264386A1 (en) | Performance enhancement in pmos and nmos transistors on the basis of silicon/carbon material | |

| US8334569B2 (en) | Transistor with embedded Si/Ge material having enhanced across-substrate uniformity | |

| US20120292637A1 (en) | Dual Cavity Etch for Embedded Stressor Regions | |

| US7939399B2 (en) | Semiconductor device having a strained semiconductor alloy concentration profile | |

| US9331174B2 (en) | Method for improving device performance using epitaxially grown silicon carbon (SiC) or silicon-germanium (SiGe) | |

| US20060172511A1 (en) | In situ formed halo region in a transistor device | |

| US20130032877A1 (en) | N-channel transistor comprising a high-k metal gate electrode structure and a reduced series resistance by epitaxially formed semiconductor material in the drain and source areas | |

| US7416931B2 (en) | Methods for fabricating a stress enhanced MOS circuit | |

| US20070254444A1 (en) | A semiconductor device having stressed etch stop layers of different intrinsic stress in combination with pn junctions of different design in different device regions | |

| US7951662B2 (en) | Method of fabricating strained silicon transistor | |

| US7608912B2 (en) | Technique for creating different mechanical strain in different CPU regions by forming an etch stop layer having differently modified intrinsic stress | |

| WO2006083546A2 (en) | In situ formed halo region in a transistor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0105 | International application |

Patent event date: 20110308 Patent event code: PA01051R01D Comment text: International Patent Application |

|

| PG1501 | Laying open of application | ||

| PC1203 | Withdrawal of no request for examination | ||

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |