KR20110081942A - 기판 전체에 걸쳐 향상된 균일성을 지닌 임베딩된 si/ge물질을 구비한 트랜지스터 - Google Patents

기판 전체에 걸쳐 향상된 균일성을 지닌 임베딩된 si/ge물질을 구비한 트랜지스터 Download PDFInfo

- Publication number

- KR20110081942A KR20110081942A KR1020117005498A KR20117005498A KR20110081942A KR 20110081942 A KR20110081942 A KR 20110081942A KR 1020117005498 A KR1020117005498 A KR 1020117005498A KR 20117005498 A KR20117005498 A KR 20117005498A KR 20110081942 A KR20110081942 A KR 20110081942A

- Authority

- KR

- South Korea

- Prior art keywords

- forming

- gate electrode

- transistor

- semiconductor

- cavities

- Prior art date

Links

- 239000000463 material Substances 0.000 title claims description 34

- 239000000758 substrate Substances 0.000 title claims description 26

- 238000000034 method Methods 0.000 claims abstract description 175

- 239000004065 semiconductor Substances 0.000 claims abstract description 105

- 230000008569 process Effects 0.000 claims abstract description 102

- 229910045601 alloy Inorganic materials 0.000 claims abstract description 40

- 239000000956 alloy Substances 0.000 claims abstract description 40

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 claims abstract description 30

- 238000003631 wet chemical etching Methods 0.000 claims abstract description 25

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims abstract description 24

- 239000000377 silicon dioxide Substances 0.000 claims abstract description 12

- 235000012239 silicon dioxide Nutrition 0.000 claims abstract description 12

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 32

- 239000010703 silicon Substances 0.000 claims description 31

- 229910052710 silicon Inorganic materials 0.000 claims description 24

- 239000007772 electrode material Substances 0.000 claims description 21

- 239000002019 doping agent Substances 0.000 claims description 20

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 claims description 12

- 229910052732 germanium Inorganic materials 0.000 claims description 11

- 230000001965 increasing effect Effects 0.000 claims description 10

- 239000000126 substance Substances 0.000 claims description 10

- 238000005468 ion implantation Methods 0.000 claims description 5

- 230000001939 inductive effect Effects 0.000 claims description 4

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 claims 2

- 238000005530 etching Methods 0.000 abstract description 34

- 239000010410 layer Substances 0.000 description 56

- 238000004519 manufacturing process Methods 0.000 description 29

- 125000006850 spacer group Chemical group 0.000 description 22

- 238000000151 deposition Methods 0.000 description 12

- 230000008021 deposition Effects 0.000 description 11

- 239000002210 silicon-based material Substances 0.000 description 8

- 229910000927 Ge alloy Inorganic materials 0.000 description 7

- 229910000676 Si alloy Inorganic materials 0.000 description 7

- 238000002513 implantation Methods 0.000 description 7

- 238000002955 isolation Methods 0.000 description 7

- 238000012545 processing Methods 0.000 description 7

- 239000002800 charge carrier Substances 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- 230000008901 benefit Effects 0.000 description 4

- 230000007246 mechanism Effects 0.000 description 4

- 238000000059 patterning Methods 0.000 description 4

- 230000009467 reduction Effects 0.000 description 4

- 235000012431 wafers Nutrition 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 230000006978 adaptation Effects 0.000 description 3

- 238000007796 conventional method Methods 0.000 description 3

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 3

- 239000002243 precursor Substances 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- CPELXLSAUQHCOX-UHFFFAOYSA-N Hydrogen bromide Chemical compound Br CPELXLSAUQHCOX-UHFFFAOYSA-N 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- 229910001128 Sn alloy Inorganic materials 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- 230000009286 beneficial effect Effects 0.000 description 2

- 229910021419 crystalline silicon Inorganic materials 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 239000007943 implant Substances 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 230000000873 masking effect Effects 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 238000005275 alloying Methods 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 238000000429 assembly Methods 0.000 description 1

- 230000000712 assembly Effects 0.000 description 1

- 238000010923 batch production Methods 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000003575 carbonaceous material Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 229910000042 hydrogen bromide Inorganic materials 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 239000006259 organic additive Substances 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical group [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66568—Lateral single gate silicon transistors

- H01L29/66636—Lateral single gate silicon transistors with source or drain recessed by etching or first recessed by etching and then refilled

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

- H01L29/045—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes by their particular orientation of crystalline planes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823807—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the channel structures, e.g. channel implants, halo or pocket implants, or channel materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823814—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the source or drain structures, e.g. specific source or drain implants or silicided source or drain structures or raised source or drain structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic System

- H01L29/161—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic System including two or more of the elements provided for in group H01L29/16, e.g. alloys

- H01L29/165—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic System including two or more of the elements provided for in group H01L29/16, e.g. alloys in different semiconductor regions, e.g. heterojunctions

Abstract

복잡한 반도체 디바이스들에서, 습식 화학적 식각 공정을 기반으로 캐비티들을 형성하는 것에 의해 스트레인 유발 반도체 합금이 채널 영역에 가까지 위치될 수 있다. 상기 습식 화학적 식각 공정은 서로 다른 결정학적 배향들에 대해 이방성 식각 특성을 가질 수 있다. 일 실시예에서, 이방성 식각 특성에 부가하여, 실리콘 이산화물에 대해 높은 식각 선택도를 보여주는 TMAH가 사용될 수 있으며, 이에 의해, 전체 프로세스 가변성을 과도하게 야기하지 않으면서도 채널 영역으로부터의 오프셋을 추가적으로 감소시킬 가능성을 더 제공해주는 극도로 얇은 식각 정지 층들을 가능하게 해준다.

Description

일반적으로, 본 발명은 집적 회로의 제조에 관한 것이며, 보다 구체적으로는, 트랜지스터들의 채널 영역들에서 전하 캐리어 이동도(charge carrier mobility)를 향상시키기 위하여 임베딩된 Si/Ge(실리콘/게르마늄)을 사용함으로써 스트레인된(strained) 채널 영역들을 구비한 트랜지스터들에 관한 것이다.

복잡한 집적 회로의 제작은 다수의 트랜지스터 소자들이 제공되는 것을 필요로하며, 여기서 트랜지스터 소자들은 복잡한 회로들의 주요 회로 소자(dominant circuit element)를 나타낸다. 예를 들어, 현재 사용가능한 복잡한 집적 회로들에는 수십억개의 트랜지스터들이 제공될 수 있다. 일반적으로, 복수의 공정 기법들이 현재 실시되는바, 마이크로프로세서, 저장 칩 등과 같은 복잡한 회로에 대해서는, 동작 속도 및/또는 전력 소모 및/또는 비용 효율 측면에서의 우수한 특성들로 인하여 CMOS 기법이 현재 가장 유망한 기법이다. CMOS 회로에서, CPU, 저장 칩 등과 같은 고도로 복잡한 회로 어셈블리들을 설계하기 위하여 회로 소자들(예를 들어, 인버터 및 기타 로직 게이트들)을 형성하는데 상보형 트랜지스터들(complementary transistors)(즉, p-채널 트랜지스터들 및 n-채널 트랜지스터들)이 사용된다. CMOS 기법을 사용하여 복잡한 집적 회로들을 제작하는 동안, 수백만 개의 트랜지스터들(즉, n-채널 트랜지스터들 및 p-채널 트랜지스터들)이 결정질 반도체 층(crystalline semiconductor layer)을 포함하는 기판 위에 형성된다. MOS 트랜지스터, 또는 일반적으로 전계 효과 트랜지스터는, n-채널 트랜지스터가 고려되든 p-채널 트랜지스터가 고려되든지에 관계없이, 소위 pn 접합을 포함하는바, 상기 pn 접합은 고농도로 도핑된(highly doped) 드레인 영역 및 소스 영역과, 상기 드레인 영역과 상기 소스 영역의 사이에 배치된 역으로 또는 저농도로 도핑된(inversely or weakly doped) 채널 영역과의 인터페이스에 의해 형성된다. 채널 영역의 전도성, 즉, 전도성 채널의 전류 구동 성능(drive current capability)은, 채널 영역에 근접하게 형성된 그리고 얇은 절연 층에 의해 상기 채널 영역으로부터 분리되는 게이트 전극에 의해 제어된다. 적절한 제어 전압을 게이트 전극에 인가함으로써 전도성 채널을 형성할 때, 채널 영역의 전도성은, 도판트 농도, 전하 캐리어들의 이동도, 그리고 트랜지스터 폭 방향에서의 주어진 채널 영역의 확장에 대한, 소스 영역과 드레인 영역 사이의 거리(채널 길이라고도 지칭됨)에 의존한다. 따라서, 채널 길이의 감소 및 이와 관련된 채널 저항률(channel resistivity)의 감소는 집적 회로들의 동작 속도 향상을 달성하기 위한 주요 설계 기준이다.

그러나, MOS 트랜지스터의 채널 길이가 끊임없이 감소됨으로 인하여 얻어지는 이점들을 과도하게 상쇄시키지 않기 위하여, 트랜지스터 치수의 지속적인 축소는 이와 관련된 해결되어야 할 복수의 문제점들을 수반한다. 예를 들어, 요구되는 채널 제어성과 함께 낮은 시트 및 접촉 저항률(sheet and contact resistivity)을 제공하기 위하여, 드레인 및 소스 영역들에는, 측방향(lateral direction)뿐만아니라 수직 방향으로, 고도로 복잡한 도판트 프로파일들이 요구된다. 더우기, 요구되는 채널 제어성(channel controllability)을 유지하기 위하여, 게이트 유전체 물질이 또한 감소된 채널 길이에 맞추어 변경될 수 있다. 그러나, 높은 채널 제어성을 유지하기 위한 몇몇 메커니즘들은 또한 트랜지스터의 채널 영역에서 전하 캐리어 이동도에 부정적인 영향을 가질 수 있으므로, 채널 길이의 감소에 의해 얻어지는 이점들을 부분적으로 상쇄시킨다.

임계 치수(critical dimensions)(즉, 트랜지스터의 게이트 길이)의 지속적인 사이즈 감소는 적응(adaptation) 및 가능하게는 고도로 복잡한 공정 기법들의 새로운 개발을 필요로 하며, 또한 이동도 저하로 인해 성능 이득을 현저하기 못하게 할 수 있기 때문에, 주어진 채널 길이에 대하여 채널 영역에서 전하 캐리어 이동도를 증가시킴으로써 트랜지스터 소자들의 채널 전도성을 향상시킴으로써 적어도 디바이스 스케일링에 관련된 공정 적응들의 상당부분들을 방지 또는 적어도 연기하는 한편 극도로 스케일된 임계 치수들(extremely scaled critical dimensions)을 요구하는 기술 표준으로의 발전과 비슷한 성능 향상을 가능하게 하는 방법이 제시되어 왔다.

전하 캐리어 이동도를 증가시키는 한가지 효율적인 메커니즘은, 예를 들어, 채널 영역 내에 대응하는 스트레인을 생성하기 위하여 채널 영역 부근에 인장성(tensile) 또는 압축성(compressive) 스트레스를 생성함으로써 채널 영역 내의 격자 구조(lattice structure)를 수정하는 것인바, 이는 결과적으로 전자들 또는 정공들(holes) 각각의 이동도가 수정되게 한다. 예를 들어, 활성 실리콘 물질(active silicon material)의 표준 결정학적 구조(crystallographic configuration), 즉, 채널 길이가 <100> 방향으로 정렬된 상태의 (100) 표면 배향(surface orientation), 에서 채널 영역 내에 인장성 스트레인을 생성하는 것은 전자들의 이동도를 증가시키며, 이는 직접적으로 전도성(conductivity)이 증가되게 한다. 반면, 채널 영역 내의 압축성 스트레인은 정공들의 이동도을 증가시키며, 그럼으로써 p-타입 트랜지스터들의 성능을 향상시킬 가능성(potential)을 제공한다. 스트레인된 실리콘은, 잘 확립된 많은 제조 기법들을 여전히 사용할 수 있으면서도, 고가의 반도체 물질들을 요구함이 없이 빠르고 파워풀한 반도체 디바이스들을 제작할 수 있게 해주는 "새로운" 타입의 반도체 물질로 여겨질 수 있기 때문에, 집적 회로 제작에 스트레스 또는 스트레인 엔지니어링을 도입하는 것은 매우 유망한 기법이다.

결과적으로, 예를 들어, 대응하는 스트레인을 발생시킬 수 있는 압축성 응력을 유발하기 위하여 채널 영역 옆에 실리콘/게리마늄 층을 도입하는 것이 제안되어 왔다. Si/Ge 물질을 형성할 때, NMOS 트랜지스터들은 마스킹되는 한편, PMOS 트랜지스터들의 드레인 및 소스 영역들은 선택적으로 리세스되어 캐비티들(cavities)을 형성하고, 후속적으로 에피텍셜 성장에 의해 실리콘/게르마늄 물질이 PMOS 트랜지스터의 캐비티들 내에 선택적으로 형성된다.

상기 기법은 p-채널 트랜지스터들의 성능 이득 및 이에 따른 CMOS 디바이스의 성능 이득의 관점에서 현저한 이점들을 가지지만, 그러나, 다수의 트랜지스터 소자들을 포함하는 진보된 반도체 디바이스들에서, 디바이스 성능의 증가된 가변성(variability)이 관측될 수 있는 것으로 밝혀졌다. 상기 증가된 가변성은, 도 1a 내지 1e를 참조로 보다 자세히 설명될 바와 같이, 특히 최종적으로 달성되는 스트레인의 관점에서 채널 영역으로부터의 실리콘/게르마늄 물질의 오프셋이 감소되어야 할 때, p-채널 트랜지스터들의 드레인 및 소스 영역들 내에 스트레인된 실리콘-게르마늄 합금을 포함시키는 위에서 설명된 기법에 관련된 것이다.

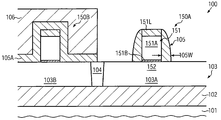

도 1은 p-채널 트랜지스터(150a) 및 n-채널 트랜지스터(150b)를 포함하는 종래의 반도체 디바이스(100)의 단면도를 개략적으로 도시하는바, 여기서, 상술한 바와 같이, 스트레인된 실리콘/게르마늄 합금을 기반으로 상기 트랜지스터(150a)의 성능이 향상될 것이다. 반도체 디바이스(100)는 실리콘 기판과 같은 기판(101)을 포함하며, 상기 기판(101) 위에는 매립 절연 층(buried insulating layer)(102)이 형성되어 있을 수 있다. 또한 결정질 실리콘 층(103)이 매립 절연 층(102) 위에 형성되어, SOI(절연체 위의 실리콘) 구조를 형성한다. SOI 구조는 전체적인 트랜지스터 성능의 관점에서 유익할 수 있는바, 예를 들어, 트랜지스터들(150a, 150b)의 기생 접합 커패시턴스(parasitic junction capacitance)가 벌크 구조(즉, 실리콘 층(103)의 두께가 층(103) 내부로의 트랜지스터들(150a, 150b)의 수직 연장부(vertical extension)보다 현저히 큰 구조)에 비하여 감소될 수 있기 때문이다. 트랜지스터들(150a, 150b)은 각각, 개략적으로 103a, 103b로 표시된 각각의 "활성(active)" 영역들 내부 및 위에 형성될 수 있으며, 여기서 상기 활성 영역들은 쉘로우 트렌치 격리(shallow trench isolation)와 같은 격리 구조(104)에 의해 분리(seperation)될 수 있다. 도시된 제조 단계에서, 트랜지스터들(150a, 150b)은 게이트 전극 구조(151)를 포함하는바, 상기 게이트 전극 구조는, 실제 게이트 전극을 나타내며 게이트 절연 층(151b) 위에 형성되는 전도성 전극 물질(151a)을 포함하는 물질로 이해될 수 있으며, 그럼으로써, 각각의 대응하는 활성 영역들(103a, 103b) 내에 위치된 채널 영역(152)으로부터 게이트 전극 물질(151)을 전기적으로 절연시킨다. 또한, 게이트 전극 구조들(151)은 예를 들어, 실리콘 질화물로 구성된 캡층(151c)을 포함할 수 있다. 또한, 스페이서 구조(105)가 트랜지스터(150a) 내의 게이트 전극 구조(151)의 측벽들 위에 형성되어, 캡층(151c)과 함께 게이트 전극 물질(151)을 캡슐화(encapsulation)할 수 있다. 한편, 마스크층(105a)이 트랜지스터(150b) 위에 형성되어, 대응하는 게이트 전극 물질(151)을 캡슐화하고 또한 활성 영역(103b)을 덮을 수 있다. 또한, 트랜지스터(150a)를 노출시킨 상태로 마스크 층(105a)을 덮기 위하여 레지스트 마스크 등과 같은 마스크(106)가 형성될 수 있다.

도 1a에 도시된 것과 같은 종래의 반도체 디바이스(100)는 하기의 공정 기법을 기반으로 형성될 수 있다.

활성 영역들(103a, 103b)이 격리 구조(104)에 기반하여 정의될 수 있으며, 상기 격리 구조(104)는 잘 확립된 포토리쏘그래피, 식각, 증착 및 평탄화 기법들을 사용하여 형성될 수 있다. 그후, 대응하는 활성 영역들(103a, 103b)에서의 기본적인 도핑 레벨(basic doping level)이, 예를 들어, 적절한 마스킹 기법을 기반으로 수행되는 주입 공정들에 의해 확립될 수 있다. 그후, 게이트 전극 물질(151) 및 게이트 절연 층(151b)을 얻기 위하여 복잡한 리쏘그래피 및 패터닝 방법들을 사용하여 게이트 전극 구조들(151)이 형성되며, 여기서, 또한 캡층(151c)이 패터닝될 수 있다. 그후, 예를 들어, 잘 확립된 저압 CVD(low pressure CVD)(화학적 증기 증착) 기법들에 의해 마스크층(105a)이 증착될 수 있으며, 이에 의해, 식각 정지 라이너로서 가능하게는 실리콘 이산화물 물질과 함께 실리콘 질화물이 형성될 수 있다. 저압 CVD 기법들은, 고도의 제어가능성을 제공하지만, 기판(101)에 걸쳐 특정한 불균일성(certain non-uniformity)을 보여주는바, 그 결과, 기판의 중앙부에 비해 기판의 에지부에서 두께가 증가될 수 있다. 결과적으로, 마스크(106)를 형성하고 전에 증착된 마스크 층(105a)으로부터 스페이서 구조(105)를 형성하기 위하여 디바이스(100)를 이방성 식각 대기(anisotropic etch ambient)에 노출함에 따라, 결과적인 폭(105w)에서 특정 정도의 불균일성이 발생될 수 있으며, 이러한 불균일성은 예를 들어, 결과적으로 기판(101)의 중앙 영역들에 비해 기판(101)의 주변부의 폭이 약간 증가되게 할 수 있다. 스페이서 구조(105)는 이방성 식각 기법들에 의해 활성 영역(103a)에 형성될 캐비티의 측방 오프셋(lateral offset)을 실질적으로 정의할 수 있으므로, 마스크 층(105a)의 증착 및 후속적인 이방성 식각 공정의 수행 중에 발생되는 불균일성에 따라, 대응하는 측방 오프셋이 약간 달라질 수 있다. 한편, 복잡한 애플리케이션들에서, 인접 채널 영역(152) 내의 전체적인 스트레인을 향상시킨다는 관점에서 대응하는 스트레인된 실리콘-게르마늄 합금의 측방 오프셋이 감소될 수 있으며, 이에 따라 스트레인된 실리콘/게르마늄 합금을 채널 영역(152)에 더 가까이 위치시키기 위하여 폭(105w)이 감소될 것이 요구된다. 일반적으로, 채널 영역(152)의 스트레인은 감소된 폭(105w)에 비례하여 증가할 수 있으며, 따라서, 적절하게 작은 폭(105w)을 제공하기 위한 공정 기법들에서, 층(105a)의 증착 및 후속적인 식각 공정에 의해 야기되는 가변성 또한 비례적으로 증가할 수 있고, 그럼으로써, 트랜지스터들(150a)의 결과적인 성능에 대해 고도의 가변성을 야기한다.

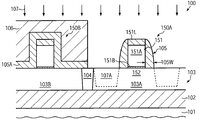

도 1b는 이방성 플라즈마 어시스트 식각 공정(anisotropic plasma assisted etch process)(107) 동안의 반도체 디바이스(100)를 개략적으로 도시하며, 여기서 예를 들어, 브롬화 수소(hydrogen bromide) 등을 기반으로한 적절한 화학제들이 적절한 유기 첨가제들(organic additives)과 함께 사용되어, 적절하게 선택된 플라즈마 조건들과 함께 대응하는 이방성 식각 특성이 얻어질 수 있다. 그러나, 상술한 바와 같이, 특히 측방 오프셋에 있어서 근소한 차(minute difference)조차도 트랜지스터 성능에 대해 상당한 변화를 야기할 수 있는 매우 복잡한 트랜지스터들이 고려되는 경우, 플라즈마 어시스트 식각 공정(107) 동안에 특정 정도의 가변성이 또한 유발되어 전체적인 가변성을 야기할 수 있다. 결과적으로, 가능하게는 각각의 캐비티들(107a)을 형성하기 위해 사용되는 이방성 식각 공정(107)과 함께, 스페이서 구조(105)를 형성하기 위한 선행하는 층(105a)의 증착 및 대응하는 이방성 식각 공정에 의해 야기되는 가변 폭(105w)으로 인하여, 캐비티들의 위치 및 사이즈 또한 대응하는 정도의 가변성을 보여줄 수 있다.

도 1c는 더 진행된 제조 단계에서 반도체 디바이스(100)를 개략적으로 도시한다. 즉, 트랜지스터(105b)가 마스크 층(105)으로 덮여진 상태에서 트랜지스터(150a) 내에 실리콘/게르마늄 합금(109)을 증착시키기 위하여, 캐비티들(107a)(도 1b와 비교)을 형성한 후 마스크(106)(도 1b와 비교)가 제거되고 선택적 에피텍셜 성장 공정이 수행된다. 노출된 결정질 실리콘 표면들 상에 실리콘/게르마늄 물질의 현저한 증착을 얻기 위하여 압력, 온도, 프리커서 유속(flow rates) 등과 같은 대응하는 공정 파라미터들이 적절하게 선택되는 대응하는 선택적 에피택셜 성장 방법들이 잘 확립되어 있으며, 한편 유전체 표면 영역들 상의 대응하는 물질의 증착은 현저히 감소되거나 심지어 무시될 수 있다. 따라서, 실리콘/게르마늄의 자연 격자 상수(natural lattice constant)가 실리콘의 격자 상수보다 크기 때문에 실리콘/게르마늄 물질(109)이 스트레인된 상태에서 성장될 수 있으며, 이에 의해, 인접 채널 영역(152)에 대응하는 압축성 스트레인을 유발할 수 있는 압축성 스트레인된 물질을 얻을 수 있다. 압축성 스트레인의 크기는 전에 형성된 캐비티들의 위치 및 사이즈, 그리고 물질(109) 내의 게르마늄 농도에 의존할 수 있다. 따라서, 물질(109)을 형성하기 위한 선택적 에피택셜 성장 공정 중에 주어진 공정 파라미터들에 대해, 마스크층(105a)을 형성하고, 스페이서 구조(105)를 패터닝하고, 캐비티들(107a)을 형성하기 위한 선행 제조 공정들의 가변성이 결과적으로 기판(101) 전체에 걸쳐 트랜지스터 성능에 대한 특정한 불균일성을 야기할 수 있다.

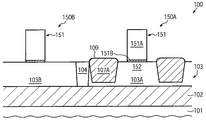

도 1d는 더 진행된 제조 단계에서의 반도체 디바이스(100)를 개략적으로 도시하는바, 여기서 마스크 층(105a), 스페이서 구조(105) 및 캡 층(151c)(도 1a와 비교)이 제거되며, 이는 잘 확립된 선택적 식각 기법들에 의해 달성될 수 있다. 그후, 디바이스 요구조건들에 따라 드레인 및 소스 영역들을 형성하는 것에 의해 추가의 공정이 계속될 수 있다.

도 1e는 기본적인 트랜지스터 구조가 실질적으로 완료된 제조 단계에서의 반도체 디바이스(100)를 개략적으로 도시한다. 도시된 바와 같이, 트랜지스터들(150a, 150b)은 측벽 스페이서 구조(153)를 포함할 수 있으며, 상기 스페이서 구조(153)는, 드레인 및 소스 영역들(154)의 도판트 프로파일의 요구되는 복잡도에 따라, 가능하게는 대응하는 식각 정지 라이너들(153a)과 함께 하나 이상의 스페이서 소자들(153a)을 포함할 수 있다. 스페이서 구조(153)는 잘 확립된 기법들에 따라, 즉, 식각 정지 라이너(153b) 및 스페이서 소자(153a)를 형성하기 위하여 이방성 식각 공정들에 의해 패터닝될 수 있는 대응하는 마스크층을 형성함으로써, 형성될 수 있다. 스페이서 구조(153)를 형성하기 전에, 스페이서 구조(153)를 바탕으로 형성될 수 있는 깊은 드레인 및 소스 영역들(154d)과 함께 드레인 및 소스 영역들(154)을 나타내는 확장 영역(154e)을 정의하기 위하여, 적절한 주입 공정들이 수행될 수 있다. 그후, 디바이스(100)를 어닐링함으로써 도판트들이 활성화되어, 주입 유발 손상(implantation induced damage)을 적어도 어느 정도까지 재결정화(recrystallizing)할 수 있다. 그후, 가능하게는 잘 확립된 공정 기법들에 따라 스트레스된 유전체 물질들에 기반하여, 금속 실리사이드 영역들을 형성하고 대응하는 컨택 구조를 형성하는 것에 의해 추가의 공정이 계속될 수 있다. 위에서 설명된 바와 같이, 복잡한 애플리케이션들에서, 트랜지스터(150a)의 성능은, 실리콘/게르마늄 합금(109)에 의해 제공되는 스트레인 유발 메커니즘에 의해 실질적으로 결정될 수 있으며, 여기서, 특히 채널 영역(152)에서의 실리콘/게르마늄 물질(109)의 요구되는 감소된 측방 오프셋에 대해, 적절하게 높은 정도의 가변성(moderately high degree of variability)이 생산 수율(production yield)을 감소시킬 수 있다. 다른 경우들에서는, 채널 영역(152)으로부터의 대응하는 오프셋이 요구되는 것보다 크게 유지되어야 하기 때문에, 물질(109)에 의해 제공되는 스트레인 유발 메커니즘의 가능성(potential)이 완전히 활용되지 않을 수 있다.

위에서 기술된 현상의 관점에서, 본 발명은 위에서 언급된 하나 이상의 문제점들의 영향들을 방지하거나 적어도 줄임으로써, 에피텍셜하게 성장된 반도체 합금들에 의해 향상된 트랜지스터 성능이 달성되는 반도체 디바이스들 및 그 제조 기법들에 관한 것이다.

일반적으로, 본 발명은 반도체 디바이스들 및 그 제조 기법들을 제공하는바, 이러한 반도체 디바이스들 및 기법들에서는, 높은 결정학적 이방성을 지닌 습식 화학적 식각 공정을 기반으로 채널 영역에 대해 잘 제어된 측방 오프셋(well controlled lateral offset)을 갖는 캐비티들이 트랜지스터 디바이스들의 활성 영역들 내에 형성될 수 있으며, 따라서, 복잡한 스페이서 구조들을 요구함이 없이 측방 오프셋에 대한 정교한 제어가 달성될 수 있다. 본 명세서의 일부 예시적인 양상들에서, 결정학적으로 이방성인 식각 공정은, 실리콘 이산화물에 대해 고도의 선택도를 가지고 실리콘을 식각하기 위한 효과적인 습식 화학제인 테트라 메틸 암모늄 하이드록사이드(TMAH)를 사용함으로써 달성될 수 있으며, 그럼으로써, 매우 안정적이고 재생가능한(reproducible) 습식 식각 공정을 제공하면서도 보호 게이트 전극 구조들에 대해 식각 정지 물질의 두께를 현저히 감소시킬 수 있다. 결과적으로, 습식 식각 공정 자체의 감소된 정도의 가변성 및 높은 식각 선택도 및 양호한 제어가능성으로 인하여, 종래에 스페이서들을 패터닝하고 대응하는 캐비티들을 형성하기 위한 대응하는 플라즈마 어시스트 식각 공정들과 결합된 스페이서 물질의 증착에 의해 야기되는 기판에 걸친 가변성을 실질적으로 겪지 않고, 대응하는 캐비티들의 오프셋이 현저히 감소될 수 있다. 또한, 고도로 제어가능한 식각 공정들을 사용함으로써, 그리고 대응하는 스페이서 물질에 대해 현저한 층 두께(pronounced layer thickness)의 증착을 방지함으로써, 특히 스페이서 물질을 패터닝하고 캐비티들을 얻기 위한 식각 공정들이 일반적으로 단일 웨이퍼 공정들(single wafer processes)로서 수행되는 종래의 기법에 비해, 전체적인 공정 처리량이 현저히 증가할 수 있다.

본 명세서에서 개시되는 한가지 예시적인 방법은, 실리콘-함유 결정질 반도체 영역 위에 형성된 트랜지스터의 게이트 전극 구조의 노출된 표면 영역들 위에 유전체 식각 정지 물질을 형성하는 것을 포함한다. 상기 방법은, 결정질 반도체 영역의 적어도 서로 다른 두개의 결정학적 배향들에서 서로 다른 제거율(removal rates)을 가지는 습식 식각 공정을 수행함으로써 게이트 전극 구조에 인접한 결정질 반도체 영역 내에 캐비티들을 형성하는 것을 더 포함한다. 또한, 상기 방법은, 선택적 에피텍셜 성장 공정을 수행함으로써 적어도 캐비티들 내에 스트레인 유발 반도체 합금을 형성하는 것을 포함한다. 마지막으로, 상기 방법은, 스트레인 유발 반도체 합금의 적어도 일부에 드레인 및 소스 영역들을 형성하는 것을 포함한다.

본 명세서에 개시된 추가의 예시적인 방법은 테트라 메틸 암모늄 하이드록사이드(TMAH)를 기반으로 습식 화학적 식각 공정을 수행함으로서 결정질 반도체 영역의 일부 위에 형성된 트랜지스터의 게이트 전극 구조에 인접한 결정질 반도체 영역 내에 캐비티들을 형성하는 것을 포함한다. 상기 방법은 캐비티들 내에 스트레인 유발 반도체 합금을 형성하는 것 및 게이트 전극 구조에 인접한 반도체 영역 내에 드레인 및 소스 영역들을 형성하는 것을 더 포함한다.

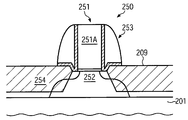

본 명세서에서 개시되는 한가지 예시적인 반도체 디바이스는 기판 위에 형성된 트랜지스터를 포함한다. 트랜지스터는 결정질 반도체 영역 위에 형성되고 게이트 전극 물질을 포함하는 게이트 전극 구조를 포함한다. 또한, 스트레인 유발 반도체 합금이, 대략 30도 이상의 측벽 각도를 가지고 테이퍼지게 하는 식으로 깊이 방향을 따라 신장되도록 결정질 반도체 영역 내에 형성된다. 마지막으로, 트랜지스터는 결정질 반도체 영역 내에, 그리고 적어도 부분적으로 반도체 합금 내에 형성된 드레인 및 소스 영역들을 포함한다.

본 발명의 다양한 실시예들이 첨부된 청구항들에서 정의될 것이며, 도면을 참조로 하기의 상세한 설명에 의해 보다 명확해질 것이다.

도 1a -1e는 복잡한 증착 공정들 및 플라즈마 어시스트 식각 기법들을 바탕으로 실리콘/게르마늄 합금을 형성하는 다양한 제조 단계들 동안 p-채널 트랜지스터를 포함하는 종래의 반도체 디바이스의 단면도를 개략적으로 도시한다.

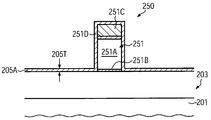

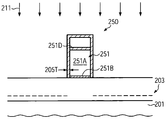

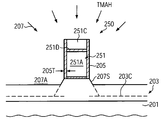

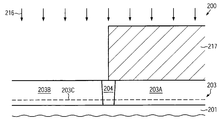

도 2a-2c는 예시적인 실시예들에 따라 습식 식각 공정 기법을 바탕으로 트랜지스터가 캐비티들을 수용하는 다양한 제조 단계들에서의 반도체 디바이스의 단면도들을 개략적으로 도시한다.

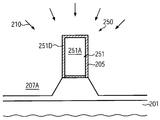

도 2d는 예시적인 실시예들에 따른 습식 화학적 식각 공정 중의 실리콘 물질의 결정학적 구성을 개략적으로 도시한다.

도 2e 및 2f는 예시적인 실시예들에 따라 채널 영역에 근접하게 위치하고 감소된 가변성을 지닌 스트레인 유발 반도체 합금을 형성하는 더 진행된 제조 단계들 동안의 트랜지스터의 단면도들을 개략적으로 도시한다.

도 2g는 서로 다른 트랜지스터들(상기 트랜지스터들 중 하나는 예시적인 실시예들에 따라 반도체 합금을 얻을 수 있음)이 제공되는 반도체 디바이스의 단면도를 개략적으로 도시한다.

도 2h-2j는 추가의 예시적인 실시예들에 따라 습식 화학적 식각 공정에 대한 제어를 향상시키기 위하여 기본 반도체 층 내의 특정 깊이(specified depth)에 종들(species)을 제공하는 다양한 변형예들에 따른 반도체 디바이스의 단면도를 개략적으로 도시한다.

도 1a -1e는 복잡한 증착 공정들 및 플라즈마 어시스트 식각 기법들을 바탕으로 실리콘/게르마늄 합금을 형성하는 다양한 제조 단계들 동안 p-채널 트랜지스터를 포함하는 종래의 반도체 디바이스의 단면도를 개략적으로 도시한다.

도 2a-2c는 예시적인 실시예들에 따라 습식 식각 공정 기법을 바탕으로 트랜지스터가 캐비티들을 수용하는 다양한 제조 단계들에서의 반도체 디바이스의 단면도들을 개략적으로 도시한다.

도 2d는 예시적인 실시예들에 따른 습식 화학적 식각 공정 중의 실리콘 물질의 결정학적 구성을 개략적으로 도시한다.

도 2e 및 2f는 예시적인 실시예들에 따라 채널 영역에 근접하게 위치하고 감소된 가변성을 지닌 스트레인 유발 반도체 합금을 형성하는 더 진행된 제조 단계들 동안의 트랜지스터의 단면도들을 개략적으로 도시한다.

도 2g는 서로 다른 트랜지스터들(상기 트랜지스터들 중 하나는 예시적인 실시예들에 따라 반도체 합금을 얻을 수 있음)이 제공되는 반도체 디바이스의 단면도를 개략적으로 도시한다.

도 2h-2j는 추가의 예시적인 실시예들에 따라 습식 화학적 식각 공정에 대한 제어를 향상시키기 위하여 기본 반도체 층 내의 특정 깊이(specified depth)에 종들(species)을 제공하는 다양한 변형예들에 따른 반도체 디바이스의 단면도를 개략적으로 도시한다.

본 발명이 도면들과 함께 하기의 상세한 설명에 예시된 것과 같은 실시예들을 참조로 설명되지만, 도면들 및 하기의 상세한 설명은 본 발명을 개시된 특정한 예시적 실시예들로 제한하려 의도된 것이 아니며, 오히려 설명된 예시적 실시예들은 본 발명의 다양한 양상들을 단지 예시하기 위한 것이고, 본 발명의 범주는 첨부된 청구항들에 의해 정의되는 것임이 이해되어야 한다.

일반적으로, 본 발명은, 채널 영역 가까이에 대응하는 반도체 합금을 위치시킬 가능성을 제공하면서도, 스트레인된 반도체 합금을 트랜지스터 디바이스들의 채널 영역들에 인접하게 포함시키기 위한 제조 시퀀스 동안에 개선된 균일성이 달성될 수 있는 반도체 디바이스들 및 그 제조 기법들을 제공한다. 이를 위하여, 대응하는 캐비티들을 형성하기 위하여 양호하게 제어가능하며 재생가능한 습식 화학적 식각 기법들이 사용될 수 있으며, 여기서, 습식 화학적 식각 화학제는 패터닝될 반도체 물질의 서로 다른 결정학적 배향들에 대해 내재적인(inherent) "이방성(anisotropic)" 식각 특성을 가질 수 있다. 결과적으로, 일부 예시적인 양상들에서, 기본 반도체 물질(asic semiconductor material)의 결정학적 구조가 적절하게 선택될 수 있으며, 따라서 식각률(etch rate)의 내재적인 차이가 측면 방향(lateral direction)에서 "자기-제약적(self-restricting)" 식각 특성을 제공할 수 있고, 그러므로 식각 공정의 시작시 주어진 초기 측방 오프셋(initial lateral offset)에 대해 개별 기판들에 걸쳐 전체적 균일성이 향상된 상태로 각각의 캐비티들이 얻어질 수 있다. 예를 들어, 일부 예시적인 실시예들에서, 실리콘 물질의 표준 결정학적 배향(standard crystallographic orientation), 즉, 트랜지스터 길이 방향들이 <110> 방향을 따라 배향된 상태의 (100) 표면 배향(surface orientation)이 사용되어, <110>, <100> 방향등과 같은 다른 방향들에 비해 <111> 방향을 따라 현저히 줄어든 식각률의 이점을 취할 수 있다. 본 명세서 전체에 걸쳐서, 대응하는 결정학적 배향들은 물리적으로 등가의 배향들을 나타내는 것으로서 이해되어야 하는바, 즉, (100) 배향은 (010), (001), (-100) 등과 같은 임의의 물리적으로 등가의 배향들을 포괄하는 것으로서 이해되어야 한다. 임의의 다른 결정학적 배향에 대해서도 마찬가지이다. 내재적인 고도의 균일성 및 재생성(reproducibility)을 가진 습식 식각 공정을 바탕으로, 습식 화학적 식각 공정에 의해 얻어지는 대응하는 캐비티들 내에 형성될 반도체 합금의 측방 오프셋을 현저하게 감소시킬 수 있게 하기 위하여 적절한 마스킹 방법들이 또한 제공될 수 있다. 본 명세서에 개시된 일부 예시적인 실시예들에서, 습식 화학적 식각 공정은 TMAH를 기반으로 수행될 수 있는바, 이러한 식각 공정은, 결정학적으로 이방성인 식각 특성에 부가하여 또한 실리콘 및 실리콘 이산화물에 대해 매우 현저한 식각 선택도(pronounced etch selectivity)를 보여줄 수 있으며, 여기서 실리콘 이산화물이 실리콘에 비해 현저하게 줄어든 속도(reduced rate)으로 식각될 수 있다. 따라서, 매우 얇은 실리콘 이산화물 층이라도 게이트 전극 구조를 캡슐화하기 위한 식각 정지 물질로서 효과적으로 사용될 수 있는바, 이는 고도의 균일성을 가지고 대응 두께를 조정할 가능성(potential)을 제공해주어, 감소된 정도의 가변성을 가지고, 스트레인 향상의 측면에서 유익한 매우 작은 측방 오프셋이 또한 달성될 수 있다. 더우기, 일부 예시적인 실시예들에서, 습식 화학적 식각 공정은, 예를 들어, 이온 주입, 선택적 에피텍셜 성장 등에 의해 기본 반도체 층 내에 도입될 수 있는 지시자 종들(indicator species) 또는 식각 정지 종들(etch stop species)을 기반으로 제어될 수 있다. 일부 예시적인 실시예들에서, 효율적인 식각 제어를 제공하기 위하여, n-타입 도판트 종들이 실리콘 물질 내의 지정된 깊이에 위치될 수 있는바, 이는, 예를 들어, TMAH가 n-타입 실리콘 물질에 대해 현저히 감소된 제거율(removal rate)을 가질 수 있기 때문이다. 다른 경우들에서는, 습식 화학적 식각 용액 내에서 검출가능한 주요 지시자 종들(prominent indicator species)이 포함될 수 있으며, 그럼으로써 또한 습식 화학적 식각 공정에 대한 향상된 제어성을 제공해준다.

도 2a 내지 2j를 참조로, 필요한 경우 도 1a 내지 1e를 또한 참조하여, 추가의 예시적인 실시예들이 이제 더 상세히 설명될 것이다.

도 2a는 초기 제조 단게에서의 트랜지스터(250)의 단면도를 개략적으로 도시한다. 트랜지스터(250)는 임의의 타입의 트랜지스터를 나타낼 수 있으며, 상기 트랜지스터(250)의 성능은 특정 타입의 스트레인을 생성하기 위하여 임베딩된 반도체 합금을 제공하는 것에 의해 개선될 것이다. 트랜지스터(250)는 기판(201)을 포함할 수 있으며, 기판 위에는 반도체 영역(203)이 형성된다. 반도체 영역(203)은, 전체적인 디바이스 요구조건들에 따라, 동일한 또는 서로 다른 전도성 타입을 지닌 복수의 트랜지스터들 또는 단일의 트랜지스터를 수용하는 활성 영역(active region)을 나타낼 수 있다. 기판(201) 및 반도체 영역(203)에 대해, 디바이스(100)을 참조로 앞에서 또한 설명된 것과 같은 유사한 기준(criteria)이 적용될 수 있다. 즉, 반도체 영역(203)은 대응하는 실리콘-기반 반도체층의 일부를 나타낼 수 있으며, 이는 대응하는 격리 구조(도시되지 않음)을 제공함으로써 개별적인 활성 영역들로 분리될 수 있다. 또한, 영역(203) 및 기판(201)은, 대응하는 매립 절연층(도시되지 않음)이 영역(203)과 기판(201) 사이에 위치된다면, SOI 구조를 나타낼 수 있다. 다른 경우들에서는, 영역(203) 및 기판(201)은, 디바이스(100)을 참조로 위에서 또한 설명된 것과 같이, 벌크 구조를 정의할 수 있다. 트랜지스터(250)는 게이트 전극 구조(251)를 포함할 수 있으며, 상기 게이트 전극 구조는, 게이트 절연층(251b)과 함께, 다결정 실리콘등과 같은 게이트 전극 물질(251a)을 나타낼 수 있다. 예를 들어, 복잡한 반도체 디바이스들이 고려되는 경우, 게이트 전극 구조(251)는 게이트 길이, 즉, 약 50nm 및 이보다 현저히 적은 게이트 전극 물질(251a)의 수평 신장부(horizontal extension)를 가질 수 있다. 또한, 일부 예시적인 실시예들에서, 캡층(251c)이 게이트 전극 물질(251) 위에 형성될 수 있고, 식각 정지층(251d)이 게이트 전극 물질(251a)와 캡층(251c) 사이에 형성될 수 있다. 예를 들어, 디바이스(100)와 관련하여 앞에서 설명된 것과 같이, 종래의 기법들과의 고도의 호환성이 적절한 것으로 간주될 때, 캡층(251c)은 실리콘 질화물로 구성될 수 있다. 한편, 식각 정지 층(251d)은 실리콘 이산화물로 구성될 수 있다. 또한, 식각 정지 라이너(205a)가 반도체 영역(203) 및 게이트 전극 구조(251) 위에 형성될 수 있다. 일 예시적인 실시예에서, 식각 정지 라이너(205a)는 실리콘 이산화물로 구성될 수 있다.

도 2a에 도시된 것과 같은 트랜지스터 디바이스는 하기의 공정들을 기반으로 형성될 수 있다. 예를 들어, 디바이스(100)에 대해 설명된 바와 같이, 격리 구조들을 기반으로 반도체 영역(203)을 정의한 후, 게이트 전극 구조(251)가 형성될 수 있는바, 이는 앞에서 설명한 바와 같이 잘 확립된 공정 기법들을 기반으로 달성될 수 있고, 여기서 게이트 전극 물질(251a)을 증착한 후, 식각 정지 물질(251d)이 형성될 수 있고, 뒤이어 캡층(251c)이 증착될 수 있다. 그후, 캡층(251c) 및 식각 정지 물질(251d)을 패터닝하기 위하여 패터닝 기법이 사용될 수 있고, 뒤이어 도 2a에 도시된 바와 같이 게이트 전극 물질(251a)을 얻기 위하여, 잘 확립된 실리콘 식각 기법들이 수행된다. 그후, 예를 들어, 잘 확립된 공정 기법들을 사용한 증착에 의해 식각 정지 라이너(205a)가 형성될 수 있는바, 여기서, 영역(203) 내에 더 형성될 캐비티에 대한 요구되는 오프셋을 얻는 측면에서 공정 요구조건들에 따라 두께(205t)가 선택될 수 있다. 예를 들어, 게이트 전극 물질(251)에 대해 대응하는 작은 오프셋이 요구된다면, 두께(205t)는 대략 5nm 이하(예를 들어, 2nm 이하)로 선택될 수 있다. 이러한 목적으로, 저압 CVD 등과 같은 적절한 공정 기법들이 사용될 수 있으며, 여기서 감소된 두께(205t)가 전체적인 기판에 걸쳐 향상된 균일성을 제공할 수 있다. 다른 경우들에는, 층(205a)이 산화 공정(oxidation process)에 의해 형성될 수 있는바, 여기서 층(205a)은 캡층(251c)을 덮지 않을 수 있다. 또한, 이 경우에, 요구되는 두께(205t)를 얻기 위하여 고도로 제어가능한 공정이 달성될 수 있다.

도 2b는 반도체 영역(203)에 대해 그리고 가능하게는 캡층(251c)에 대해 층(205a)의 물질을 선택적으로 제거하도록 된 이방성 식각 공정(211) 동안의 트랜지스터(250)를 개략적으로 도시한다. 실리콘 이산화물에 대한 각각의 고도로 선택적인 플라즈마 어시스트 식각 공정들은 본 기술분야에서 잘 확립되어 있고, 공정(211)을 위해 사용될 것임이 이해될 것이다. 결과적으로, 각각의 "측벽 스페이서들"(205)은, 식각 공정(211)에 의해 야기된 두께의 매우 근소한 감소를 제외하고는 두께(205t)에 실질적으로 대응하는 두께를 가진 게이트 전극 구조들(251)의 측벽들 위에 얻어질 수 있다. 그러나, 감소된 두께(205t)로 인하여, 식각 공정에 관련된 변형들(etch process related variations)이 매우 작을 수 있도록, 공정(211) 대기에 대한 노출이 적절히 짧아질 수 있음이 이해되어야 한다.

도 2c는 습식 화학적 식각 공정(207) 동안의 트랜지스터(250)를 개략적으로 도시하는바, 상기 공정은 수직 방향과 수평 방향에서 서로 다른 식각률(etch rate)을 가질 수 있다. 즉, 공정(207)의 습식 화학적 식각 화학제는 서로 다른 결정학적 배향들에 대해 서로 다른 고유한(intrinsic) 제거율을 가질 수 있고, 따라서, 수직 및 측면 방향에서 다르게 식각될 수 있는바, 이는, 영역(203)의 실리콘 베이스 물질의 결정학적 구성에 따라, 결정질 반도체 영역(203)이 이 방향들에 대해 서로 다른 결정학적 배향들을 가지기 때문이다. 예를 들어, 습식 화학적 식각 화학제는 <111> 결정학적 배향을 따라 감소된 식각률을 가질 수 있고, 이는 결과적으로 식각 프론트(etch front)의 측방 제약(lateral restriction)을 야기할 수 있으며, 그럼으로써, 대응하는 <111> 방향의 공간적 배향(spatial orientation)에 따라 경사지는(inclined) 대응하는 캐비티들(207a)의 측벽들(207s)을 생성한다. 일 예시적인 실시예에서, 공정(207)의 습식 화학적 식각 화학제는 테트라 메틸 암모늄 하이드록사이드(TMAH)를 기반으로 확립될 수 있는바, 상기 TMAH는 또한 레지스트 현상 물질(resist developing material)로서 사용될 수 있으며, 실리콘 물질에 대해 높은 식각률을 가질 수 있고, 여기서 또한 실리콘 이산화물에 대한 높은 식각 선택도가 달성될 수 있다. 결과적으로, 디바이스(250)를 공정(207) 대기에 노출시킴에 따라, 캐비티들(207a)의 오프셋이 실질적으로 폭(205t)에 의해 결정될 수 있도록 스페이서들(205)이 효율적으로 게이트 전극 구조(251)를 보호할 수 있으며, 여기서, 습식 화학적 식각 공정(207)의 진행 중에, 영역(203)의 결정학적 축들(crystallographic axes)의 공간적 배향(spatial orientation)에 따라 고도로 제어가능하고 예측가능한 방식으로 측방 오프셋이 증가할 수 있다. 캡층(251c)이 공정(207)에 대해 특정한 식각 저항(specific etch resistance)을 보이지 않는다면, 식각 정지층(251)이 여전히 게이트 전극 물질(251a)에 대한 무결성(integrity)을 제공해준다. 또한, 일부 예시적인 실시예들에서, 식각 공정(207)을 제어하기 위하여, 즉, 캐비티들(207a)의 깊이를 향상된 균일성을 가지고 조정하기 위하여, 식각 제어 종들(203c)은 특정한 깊이(specified depth)를 중심으로(centered around) 놓일 수 있다. 예를 들어, 식각 제어 종들(203c)은, TMAH 기반의 공정(207)의 습식 화학적 화학제에 노출될 때 현저히 감소된 식각률을 가지는 n-도핑된 실리콘 영역을 얻기 위하여, 비소(arsenic)와 같은 n-타입 도판트 종들의 형태로 제공될 수 있다. 식각 제어 종들(203c)은 추후 보다 자세히 설명될 이온 주입, 에피텍셜 성장 기법들 등에 의해 제공될 수 있다.

도 2d는 <111> 방향을 따른 식각 프론트의 진행이 다른 결정학적 방향들에 따른 진행에 비해 현저히 감소되도록 (111) 평면을 바탕으로 현저한 식각 저항률(pronounced etch resistivity)을 달성할 수 있는 일 예시적인 실시예에 따른 반도체 영역(203)의 결정학적 구조를 개략적으로 도시한다. 도시된 바와 같이, 실리콘 물질의 큐빅 격자 구조의 일부가 도시되며, 여기서 반도체 산업에서 사용되는 표준적인 기본 반도체 웨이퍼들에 따라 (100) 표면층이 제공될 수 있다. 또한, 게이트 전극 구조(251)는 그것의 길이 방향, 즉, 도 2c에서, <110> 방향에 따른 게이트 전극 물질(251a)의 수평 확장 방향으로 위치될 수 있는다. 이 경우에, (111) 평면들은, 대응하는 (110) 평면들에 대해 대략 35도, 26도의 각도를 형성할 수 있으며, 이는 또한 습식 화학적 식각 공정 진행 중의 측벽들(207s)(도 2c와 비교)의 측벽 각도를 실질적으로 나타낼 수 있다. 그러나, 서로 다른 측벽 각도들이 요구되는 경우, 대응하는 식각 화학제의 주어진 이방성 식각 특성에 대해 베이스 물질(203)에 대한 각각의 서로 다른 결정학적 구조들이 선택될 수 있음이 이해되어야 한다. 즉, 각각의 "회전된(rotated)" 결정학적 배향에 대해 대응하는 트랜지스터 성능 이득이 얻어질 수 있는 한, 서로 다른 측벽 각도를 얻기 위하여 베이스 물질(203)의 결정학적 배향이 적절하게 "회전"될 수 있다.

도 2e는 캐비티들(207a)이 특정 깊이까지 아래로 신장된 상태의 트랜지스터(250)를 개략적으로 도시하는바, 상기 깊이는 예를 들어, 식각 제어 종들(203c)(도 2c와 비교)에 의해 결정되거나, 시간 제어 식각 기법(time controlled etch strategy)을 바탕으로 조정될 수 있다. 대응하는 습식 화학적 식각 리액터(wet chemical etch reactor)에서 복수의 기판들이 동시에 처리될 수 있으므로, 고 처리율 식각 공정(high throughput etch process)을 기반으로 캐비티들(207a)이 얻어질 수 있으며, 그럼으로써 일반적으로 단일 기판 공정 기법을 필요로하는 종래의 플라즈마 어시스트 식각 기법들에 비해 현저한 이득을 제공함이 이해되어야 한다.

도시된 바와 같이, 캡층(251c)(도 2c와 비교)이 현저한 식각 저항률(pronounced etch resistivity)을 보이지 않는다면, 선행하는 습식 화학적 식각 공정 중에 식각 정지층(251d)이 노출될 수 있다. 따라서, 식각 정지층(251d)이 한동안 게이트 전극 물질(251)의 무결성을 유지하도록 동작하며, 또한 선택적 에피텍셜 성장 공정(210) 공안에 성장 마스크로서 동작한다. 트랜지스터(250)가 채널 영역(252) 내에 압축성 응력을 필요로하는 트랜지스터를 나타낼 때, 공정(210) 중에실리콘/게르마늄 합금, 실리콘/게르마늄/주석 합금, 실리콘/주석 합금과 같은 적절한 반도체 합금이 증착될 수 있다. 다른 경우들에는, 실리콘/탄소 물질이 공정(210) 동안 증착되어 인장성 스트레스된 반도체 합금(tensile stressed semiconductor alloy)을 제공할 수 있고, 이는 결과적으로 채널 영역(252) 내에 대응하는 인장성 스트레인을 야기할 수 있다. 또한, 적절하게 선택된 공정 파라미터들을 기반으로 수행될 수 있는 선택적 에피택셜 성장 공정 중에, 개별 성분들(individual components)의 분율(fractions)이 조정될 수 있고, 필요하다면, 도판트 종들이 첨가될 수 있으며, 여기서, 필요하다면, 임의의 도판트 종들의 농도 및 대응하는 합금 성분들의 농도가 공정(210) 중에 변화될 수 있다. 고도로 균일하며 제어가능한 캐비티들(207a)의 형성으로 인하여, 공정(210)에 대해 증가된 유연성이 또한 달성될 수 있는바, 이는 앞에서 설명된 바와 같이, 종래의 공정 기법들에 의해 야기되는 증가된 가변성에, 변화하는(varying) 도판트 농도 및/또는 반도체 합금 성분들의 농도에 기반한 디바이스 특성들에 대한 임의의 특정한 변경(adaptation)이 부가(superimpose)될 수 있기 때문이다.

도 2f는 더 진행된 제조 단계에서의 트랜지스터(250)를 개략적으로 도시한다. 도시된 바와 같이, 인접 채널 영역(252) 내에 특정 타입의 스트레인을 유발하도록, 위에서 설명된 합금들과 같은 반도체 합금(209)이 영역(203) 내에 형성될 수 있으며, 여기서, 감소된 측방 오프셋이 스트레인 전달(strain transfer)의 효율성을 증가시켜줄 수 있다. 또한, 드레인 및 소스 영역들(254)이 영역(203), 특히 반도체 합금(209) 내에 정의된다. 또한, 측벽 스페이서 구조(253)가 게이트 전극 구조(251)의 측벽들 위에 형성될 수 있다. 도 2a에 도시된 것과 같은 트랜지스터(250)는 디바이스(100)에 대해 앞에서 설명된 것과 유사한 공정 기법들을 바탕으로 형성될 수 있으나, 여기서, 채널 영역(252)에 대한 반도체 합금(209)의 근접성으로 인하여, 다른 경우 동일한 디바이스 및 프로세스 파라미터들에 대해 향상된 전체 트랜지스터 성능이 얻어질 수 있으며, 한편 전체적인 가변성, 즉, 대응하는 트랜지스터 특성들의 기판에 걸친 균일성(across-substrate uniformity)은 종래의 기법들에 비해 향상될 수 있다.

도 2g는 초기 제조 단계에서 트랜지스터들(250a, 250b)을 포함하는 반도체 디바이스(200)를 개략적으로 도시한다. 도시된 바와 같이, 트랜지스터들(250a, 250b)은 도 2a를 참조로 설명된 것과 같은 유사한 구조를 가진다. 즉, 트랜지스터들(250a, 250b)은 대응하는 활성 영역들(203a, 203b) 위에 형성된 게이트 전극 구조(251)를 포함할 수 있다. 활성 영역들(203a, 203b)은, 디바이스(100)를 참조로 또한 설명된 바와 같이, 격리 구조(204)에 의해 분리될 수 있다. 또한, 도시된 제조 단계에서, 스페이서(205)가 게이트 전극 구조(251)의 측벽들 위에 형성될 수 있으며, 트랜지스터(250b)의 구조(251)는 마스크층(205a)에 의해 덮여질 수 있다. 또한, 트랜지스터(250a)를 노출시킨 상태로 트랜지스터(250b)를 덮기 위하여 레지스트 마스크와 같은 마스크(206)가 제공될 수 있다.

반도체 디바이스(200)를 형성하기 위한 제조 기법과 관련하여, 트랜지스터(250)를 참조로 설명된 것과 같은 대응하는 공정 기법들이 참조될 수 있다. 즉, 마스크층(205A)을 형성한 후, 활성 영역(203b) 위에 마스크층(205A)을 유지한 채로, 레지스트 마스크 또는 임의의 다른 식각 마스크(206)가 형성될 수 있으며 스페이서들(205)를 얻기 위해 사용될 수 있다. 그후, 습식 화학적 식각 공정(207)(도 2b와 비교)에 대한 식각 저항률에 따라 마스크(206)는 제거 또는 유지될 수 있다. 따라서, 마스크(206)가 제거될 것이라면, 마스크층(205a)은 식각 마스크로서 동작할 수 있으며, 또한 후속적인 선택적 에피텍셜 성장 공정 중에 성장 마스크로서 동작할 수 있다. 결과적으로, 적절하게 얇은 층 두께를 지닌 마스크층(205a)이 또한, 트랜지스터(250b)와 같은 디바이스 영역들을 덮기 위해 효과적으로 사용될 수 있으며, 여기서 반도체 합금은 요구되지 않을 수 있다. 트랜지스터(250a) 내에 반도체 합금을 형성한 후, 디바이스(100)와 관련하여 설명된 것과 같이, 잘 확립된 공정 기법들을 바탕으로 추가의 공정이 계속될 수 있다.

도 2h는 초기 제조 단계, 즉, 게이트 전극 구조들(251)을 형성하기 전의 반도체 디바이스(200)를 개략적으로 도시한다. 이 제조 단계에서, 주입 마스크(214)에 의해 활성 영역(203b)을 덮는 한편, 영역(203a)에 대한 기본 도핑 농도가 대응하는 주입 시퀀스(213)에 근거하여 정의될 수 있다. 일 예시적인 실시예에서, 주입 시퀀스(213)은 또한 특정 깊이(203d)에 식각 제어 종들(203c)을 도입하기 위한 주입 단계를 포함할 수 있으며, 상기 깊이(203d)는 추후의 제조 단계에서 영역(203a) 내에 형성될 캐비티들의 요구되는 깊이에 실질적으로 대응한다. 예를 들어, 영역(203a)이 p-채널 트랜지스터의 활성 영역을 나타낸다면, 추가의 n-타입 도판트 종들(203c)은 전체적인 트랜지스터 특성들에 실질적으로 영향을 미치지 않을 수 있다. 다른 예시적인 실시예들에서, 예를 들어, 도 2a를 참조로 도시되고 설명된 바와 같이, 식각 제어 종들(203c)을 도입하기 위한 대응하는 주입 단계는, 게이트 전극 구조(251)를 제공한 후에 수행될 수 있음이 이해되어야 한다.

도 2i는 추가의 예시적인 실시에들에 따른 반도체 디바이스(200)를 개략적으로 도시하는바, 여기서 반도체 영역 또는 층(203)은 에피텍셜 성장 공정(215)에 의해 기판(201) 위에 형성될 수 있으며, 식각 제어 종들(203c)이 성장 공정(215)의 특정 단계 중에 포함될 수 있다. 예를 들어, 식각 제어 종들(203c)을 특정 깊이에 위치시키기 위하여, 대응하는 n-타입 도판트 종들이, 적절한 프리커서 가스의 형태로 공정(215)의 증착 대기에 제공될 수 있다. 그후, n-타입 도판트 프리커서 가스의 공급이 중단될 수 있으며, 이에 의해 대응하는 식각 제어 종들(203c)에 대한 잘 정의된 깊이 및 두께가 제공될 수 있다.

도 2j는 더 진행된 제조 단계에서의 디바이스(200)를 개략적으로 도시하는바, 여기서 층(203)이 그 최종 두께로 제공되며, 격리 구조(204)가 활성 영역들(203a, 203b)을 분리한다. 또한, 식각 제어 종들(203c)의 존재가 결과적으로 활성 영역(203b) 내에서 수정된 전기적 특성들 야기할 수 있다고 가정된다. 이 경우에, 예를 들어, 활성 영역(203b) 내에 기본 도판트 농도를 정의하기 위한 시퀀스 동안에 적절한 주입 공정(216)이 수행될 수 있으며, 여기서, 식각 제어 종들을 보상(compensate)하기 위하여 적절한 정도의 카운터 도핑이 특정 깊이에 도입될 수 있고, 한편, 식각 제어 종들(203c)이 있을것이 요구될 수 있는 활성 영역(203a)을, 대응하는 주입 마스크(217)가 덮을 수 있다.

그후, 상술한 바와 같이, 습식 화학적 식각 공정을 바탕으로 캐비티들을 형성하기 위한 위에서 기술된 공정 시퀀스가 수행될 수 있으며, 여기서 식각 제어 종들(203c)은 결과적인 캐비티들의 깊이 및 이에 따른 사이즈에 대해 향상된 제어가능성을 제공해 줄 수 있다.

결과적으로, 본 발명은 채널 영역에 인접하게 위치될 수 있는 반도체 합금을 바탕으로 개선된 트랜지스터 성능이 달성될 수 있는 반도체 디바이스들 및 그 제조 기법을 제공한다. 이를 위하여, 캐비티들의 측방 오프셋을 정의하고 캐비티들을 형성하기 위한 대응하는 시퀀스 중에 현저히 감소된 가변성을 제공할 수 있는 습식 화학적 식각 공정이 사용될 수 있다. 또한, 스페이서 물질의 현저한 증착(pronounced deposition)이 요구되지 않을 수 있기 때문에, 그리고 습식 화학적 식각 공정이 배치 공정에서 고도의 제어가능성을 가지고 수행될 수 있다는 사실로 인하여, 플라즈마 어시스트 식각 방법들이 단일의 웨이퍼 공정 전략을 요구하는 종래의 기법들에 비해 전체적인 처리량이 현저히 증가될 수 있다.

본 발명에 대한 추가의 수정 및 변형들은 상기 설명의 관점에서 당업자들에게 자명할 것이다. 따라서, 상기 설명은 단지 예시적인 것으로서 이해되어야 하며, 당업자에게 본 발명을 수행하는 일반적인 방식을 제공하기 위한 목적으로 이해되어야 한다. 본 명세서에서 도시되고 설명된 것들은 현재 선호되는 실시예들로서 다루어지는 것임이 이해될 것이다.

Claims (25)

- 실리콘 함유 결정질 반도체 영역(silicon containing crystalline semiconductor region) 위에 형성된 트랜지스터의 게이트 전극 구조의 노출 표면 영역들(exposed surface areas) 위에 유전체 식각 정지 물질을 형성하는 단계와;

상기 결정질 반도체 영역의 적어도 두개의 서로 다른 결정학적 배향들(crystallographic orientations)에서 서로 다른 제거율(removal rates)을 가지는 습식 화학적 식각 공정(wet chemical etch process)을 수행함으로써 상기 게이트 전극 구조에 인접한 상기 결정질 반도체 영역 내에 캐비티들(cavities)을 형성하는 단계와;

선택적 에피텍셜 성장 공정을 수행함으로써 적어도 상기 캐비티들 내에 스트레인 유발 반도체 합금(strain inducing semiconductor alloy)을 형성하는 단계와; 그리고

상기 스트레인 유발 반도체 합금의 적어도 일부 내에 드레인 및 소스 영역들을 형성하는 단계를 포함하는 것을 특징으로 하는 방법. - 제1 항에 있어서, 상기 습식 화학적 식각 공정은 테트라 메틸 암모늄 하이드록사이드(TMAH)에 기반하여 수행되는 것을 특징으로 하는 방법.

- 제1 항에 있어서, 상기 유전체 식각 정지 물질을 형성하는 단계는 상기 게이트 전극 구조의 적어도 측벽 표면들(sidewall surfaces) 위에 실리콘 이산화물층을 형성하는 것을 포함하는 것을 특징으로 하는 방법.

- 제3 항에 있어서, 상기 실리콘 이산화물층의 두께는 대략 5 나노미터 이하인 것을 특징으로 하는 방법.

- 제1 항에 있어서, 상기 결정질 반도체 영역 내의 특정 깊이(specified depth)에 n-타입 도판트 종들을 위치시키는 단계 및 상기 습식 화학적 식각 공정을 제어하기 위하여 상기 n-타입 도판트 종들을 사용하는 단계를 더 포함하는 것을 특징으로 하는 방법.

- 제5 항에 있어서, 상기 n-타입 도판트 종들은 이온 주입 공정을 수행하는 것에 의해 상기 특정 깊이에 위치되는 것을 특징으로 하는 방법.

- 제6 항에 있어서, 상기 이온 주입 공정은 상기 게이트 전극 구조를 형성하기 전에 수행되는 것을 특징으로 하는 방법.

- 제6 항에 있어서, 상기 이온 주입 공정은 상기 게이트 전극 구조를 형성한 후에 수행되는 것을 특징으로 하는 방법.

- 제5 항에 있어서, 상기 결정질 반도체 영역은 에피텍셜 성장 공정에 의해 형성되며, 상기 n-타입 도판트 종들은 상기 에피텍셜 성장 공정 중에 상기 특정 깊이에 위치되는 것을 특징으로 하는 방법.

- 제5 항에 있어서, 상기 반도체 합금은 상기 트랜지스터의 채널 영역 내에 압축성 스트레인(compressive strain)을 유발하기 위하여 형성되는 것을 특징으로 하는 방법.

- 제10 항에 있어서, 상기 반도체 합금은 실리콘 및 게르마늄으로 구성된 것을 특징으로 하는 방법.

- 제10 항에 있어서, 상기 반도체 합금은 주석(tin)을 포함하는 것을 특징으로 하는 방법.

- 테트라 메틸 암모늄 하이드록사이드(TMAH)를 기반으로한 습식 화학적 식각 공정을 수행함으로써 결정질 반도체 영역 일부 위에 형성된 트랜지스터의 게이트 전극 구조에 인접한 상기 결정질 반도체 영역 내에 캐비티들을 형성하는 단계와;

상기 캐비티들 내에 스트레인 유발 반도체 합금을 형성하는 단계와; 그리고

상기 게이트 전극 구조에 인접하게 상기 반도체 영역 내에 드레인 및 소스 영역들을 형성하는 단계를 포함하는 것을 특징으로 하는 방법. - 제13 항에 있어서, 상기 캐비티들을 형성하는 단계는, 상기 반도체 영역 내의 특정 깊이에 n-타입 도판트 종들을 위치시키는 단계 및 상기 습식 화학적 식각 공정을 제어하기 위하여 상기 n-타입 도판트 종들을 사용하는 단계를 더 포함하는 것을 특징으로 하는 방법.

- 제13 항에 있어서, 상기 캐비티들을 형성하기 전에 게이트 전극 물질의 적어도 측벽들 위에 식각 정지 물질을 형성하는 단계를 더 포함하는 것을 특징으로 하는 방법.

- 제15 항에 있어서, 상기 식각 정지 물질은 대략 5 나노미터 이하의 두께를 가지는 것을 특징으로 하는 방법.

- 제13 항에 있어서, 상기 드레인 및 소스 영역들을 형성하는 단계는 상기 캐비티들 내에 반도체 합금을 형성하는 것을 포함하며, 여기서 상기 반도체 합금은 상기 트랜지스터의 채널 영역 내에 압축성 스트레인을 유발하는 것을 특징으로 하는 방법.

- 제17 항에 있어서, 상기 캐비티들을 형성하고 상기 캐비티들 내에 상기 반도체 합금을 형성하는 동안 제2 트랜지스터 위에 마스크층을 제공하는 단계를 더 포함하는 것을 특징으로 하는 방법.

- 제17 항에 있어서, 상기 반도체 합금은 게르마늄과 주석 중 적어도 하나를 포함하는 것을 특징으로 하는 방법.

- 반도체 디바이스로서,

기판 위에 형성된 트랜지스터와, 상기 트랜지스터는 결정질 반도체 영역 위에 형성된 게이트 전극 구조 및 게이트 전극 물질을 포함하고;

대략 30˚이상의 측벽 각도를 가지고 테이퍼지게하는 식(tapered manner)으로 깊이 방향(depth direction)을 따라 신장되도록 상기 결정질 반도체 영역 내에 형성된 스트레인 유발 반도체 영역과; 그리고

상기 결정질 반도체 영역 내에 그리고 적어도 부분적으로 상기 반도체 합금 내에 형성된 드레인 및 소스 영역들을 포함하는 것을 특징으로 하는 반도체 디바이스. - 제20 항에 있어서,

상기 반도체 합금의 바닥부(bottom)에 중심을 두고 증가된 n-타입 도판트 농도를 더 포함하는 것을 특징으로 하는 반도체 디바이스. - 제20 항에 있어서, 상기 게이트 전극 물질로부터의 상기 반도체 합금의 최소 측방 오프셋은 대략 5 나노미터 이하인 것을 특징으로 하는 반도체 디바이스.

- 제22 항에 있어서,

상기 게이트 전극 물질로부터의 상기 반도체 합금의 최소 측방 오프셋은 대략 2 나노미터 이하인 것을 특징으로 하는 반도체 디바이스. - 제20 항에 있어서,

상기 반도체 합금은 상기 트랜지스터의 채널 영역 내에 압축성 스트레인을 유발하는 것을 특징으로 하는 반도체 디바이스. - 제24 항에 있어서,

상기 게이트 전극 물질의 게이트 길이는 대략 50 나노미터 이하인 것을 특징으로 하는 반도체 디바이스.

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102008049723.1 | 2008-09-30 | ||

| DE102008049723A DE102008049723B4 (de) | 2008-09-30 | 2008-09-30 | Transistor mit eingebettetem Si/Ge-Material mit einer besseren substratüberspannenden Gleichmäßigkeit |

| US12/562,437 | 2009-09-18 | ||

| US12/562,437 US8183100B2 (en) | 2008-09-30 | 2009-09-18 | Transistor with embedded SI/GE material having enhanced across-substrate uniformity |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20110081942A true KR20110081942A (ko) | 2011-07-15 |

Family

ID=41794956

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020117005498A KR20110081942A (ko) | 2008-09-30 | 2009-09-29 | 기판 전체에 걸쳐 향상된 균일성을 지닌 임베딩된 si/ge물질을 구비한 트랜지스터 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US8183100B2 (ko) |

| JP (1) | JP5798923B2 (ko) |

| KR (1) | KR20110081942A (ko) |

| CN (1) | CN102160159A (ko) |

| DE (1) | DE102008049723B4 (ko) |

| WO (1) | WO2010037522A1 (ko) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102008049723B4 (de) * | 2008-09-30 | 2012-01-26 | Advanced Micro Devices, Inc. | Transistor mit eingebettetem Si/Ge-Material mit einer besseren substratüberspannenden Gleichmäßigkeit |

| US8492234B2 (en) * | 2010-06-29 | 2013-07-23 | International Business Machines Corporation | Field effect transistor device |

| US9006052B2 (en) | 2010-10-11 | 2015-04-14 | International Business Machines Corporation | Self aligned device with enhanced stress and methods of manufacture |

| DE102010064282B4 (de) * | 2010-12-28 | 2012-09-06 | GLOBALFOUNDRIES Dresden Module One Ltd. Liability Company & Co. KG | Transistor mit eingebetteten sigma-förmigen sequenziell hergestellten Halbleiterlegierungen |

| US9018065B2 (en) * | 2012-05-08 | 2015-04-28 | Globalfoundries Inc. | Horizontal epitaxy furnace for channel SiGe formation |

| US9054217B2 (en) | 2013-09-17 | 2015-06-09 | Samsung Electronics Co., Ltd. | Method for fabricating semiconductor device having an embedded source/drain |

| CN105161406B (zh) * | 2014-06-12 | 2019-04-26 | 中芯国际集成电路制造(上海)有限公司 | 晶体管及其形成方法 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6376481A (ja) * | 1986-09-19 | 1988-04-06 | Hitachi Ltd | 半導体装置及びその製造方法 |

| US5716218A (en) * | 1991-06-04 | 1998-02-10 | Micron Technology, Inc. | Process for manufacturing an interconnect for testing a semiconductor die |

| US5414276A (en) * | 1993-10-18 | 1995-05-09 | The Regents Of The University Of California | Transistors using crystalline silicon devices on glass |

| US6372618B2 (en) * | 2000-01-06 | 2002-04-16 | Micron Technology, Inc. | Methods of forming semiconductor structures |

| JP4355807B2 (ja) * | 2002-08-28 | 2009-11-04 | 独立行政法人産業技術総合研究所 | 二重ゲート型mos電界効果トランジスタ及びその作製方法 |

| JP4046014B2 (ja) * | 2003-05-30 | 2008-02-13 | 株式会社デンソー | 構造体の製造方法 |

| US7045407B2 (en) * | 2003-12-30 | 2006-05-16 | Intel Corporation | Amorphous etch stop for the anisotropic etching of substrates |

| US6946350B2 (en) * | 2003-12-31 | 2005-09-20 | Intel Corporation | Controlled faceting of source/drain regions |

| JP4837902B2 (ja) * | 2004-06-24 | 2011-12-14 | 富士通セミコンダクター株式会社 | 半導体装置 |

| US20060091483A1 (en) * | 2004-11-02 | 2006-05-04 | Doczy Mark L | Method for making a semiconductor device with a high-k gate dielectric layer and a silicide gate electrode |

| JP4369359B2 (ja) * | 2004-12-28 | 2009-11-18 | 富士通マイクロエレクトロニクス株式会社 | 半導体装置 |

| US7494858B2 (en) * | 2005-06-30 | 2009-02-24 | Intel Corporation | Transistor with improved tip profile and method of manufacture thereof |

| JP2007019129A (ja) * | 2005-07-06 | 2007-01-25 | Renesas Technology Corp | 半導体装置の製造方法及び半導体装置 |

| DE102005051994B4 (de) * | 2005-10-31 | 2011-12-01 | Globalfoundries Inc. | Verformungsverfahrenstechnik in Transistoren auf Siliziumbasis unter Anwendung eingebetteter Halbleiterschichten mit Atomen mit einem großen kovalenten Radius |

| JP2007157788A (ja) * | 2005-11-30 | 2007-06-21 | Toshiba Corp | 半導体装置 |

| US7691752B2 (en) * | 2007-03-30 | 2010-04-06 | Intel Corporation | Methods of forming improved EPI fill on narrow isolation bounded source/drain regions and structures formed thereby |

| DE102008049723B4 (de) * | 2008-09-30 | 2012-01-26 | Advanced Micro Devices, Inc. | Transistor mit eingebettetem Si/Ge-Material mit einer besseren substratüberspannenden Gleichmäßigkeit |

-

2008

- 2008-09-30 DE DE102008049723A patent/DE102008049723B4/de active Active

-

2009

- 2009-09-18 US US12/562,437 patent/US8183100B2/en active Active

- 2009-09-29 JP JP2011528255A patent/JP5798923B2/ja active Active

- 2009-09-29 CN CN2009801362115A patent/CN102160159A/zh active Pending

- 2009-09-29 WO PCT/EP2009/007001 patent/WO2010037522A1/en active Application Filing

- 2009-09-29 KR KR1020117005498A patent/KR20110081942A/ko not_active Application Discontinuation

-

2012

- 2012-04-24 US US13/454,177 patent/US8334569B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20100078691A1 (en) | 2010-04-01 |

| US20120211810A1 (en) | 2012-08-23 |

| DE102008049723A1 (de) | 2010-04-08 |

| DE102008049723B4 (de) | 2012-01-26 |

| US8183100B2 (en) | 2012-05-22 |

| JP2012504326A (ja) | 2012-02-16 |

| WO2010037522A1 (en) | 2010-04-08 |

| US8334569B2 (en) | 2012-12-18 |

| JP5798923B2 (ja) | 2015-10-21 |

| CN102160159A (zh) | 2011-08-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8466520B2 (en) | Transistor with an embedded strain-inducing material having a gradually shaped configuration | |

| US7586153B2 (en) | Technique for forming recessed strained drain/source regions in NMOS and PMOS transistors | |

| US8906811B2 (en) | Shallow pn junction formed by in situ doping during selective growth of an embedded semiconductor alloy by a cyclic growth/etch deposition process | |

| US8093634B2 (en) | In situ formed drain and source regions in a silicon/germanium containing transistor device | |

| US8124467B2 (en) | Reducing silicide resistance in silicon/germanium-containing drain/source regions of transistors | |

| US8138050B2 (en) | Transistor device comprising an asymmetric embedded semiconductor alloy | |

| US20140264386A1 (en) | Performance enhancement in pmos and nmos transistors on the basis of silicon/carbon material | |

| US8962420B2 (en) | Semiconductor device comprising a buried poly resistor | |

| KR20080073352A (ko) | 스트레인된 트랜지스터의 결정질 결함들을 경사진 선행비결정화에 의해서 감소시키는 방법 | |

| US20060172511A1 (en) | In situ formed halo region in a transistor device | |

| US8334569B2 (en) | Transistor with embedded Si/Ge material having enhanced across-substrate uniformity | |

| US20120292637A1 (en) | Dual Cavity Etch for Embedded Stressor Regions | |

| US20070254444A1 (en) | A semiconductor device having stressed etch stop layers of different intrinsic stress in combination with pn junctions of different design in different device regions | |

| US7416931B2 (en) | Methods for fabricating a stress enhanced MOS circuit | |

| US7939399B2 (en) | Semiconductor device having a strained semiconductor alloy concentration profile | |

| US9331174B2 (en) | Method for improving device performance using epitaxially grown silicon carbon (SiC) or silicon-germanium (SiGe) | |

| US7608912B2 (en) | Technique for creating different mechanical strain in different CPU regions by forming an etch stop layer having differently modified intrinsic stress | |

| US20130032877A1 (en) | N-channel transistor comprising a high-k metal gate electrode structure and a reduced series resistance by epitaxially formed semiconductor material in the drain and source areas | |

| US7951662B2 (en) | Method of fabricating strained silicon transistor | |

| WO2006083546A2 (en) | In situ formed halo region in a transistor device | |

| US20130175640A1 (en) | Stress enhanced mos transistor and methods for fabrication |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid |