KR20090066317A - 플라즈마 cvd법에 의한 실리콘계 박막의 형성방법 - Google Patents

플라즈마 cvd법에 의한 실리콘계 박막의 형성방법 Download PDFInfo

- Publication number

- KR20090066317A KR20090066317A KR1020097009525A KR20097009525A KR20090066317A KR 20090066317 A KR20090066317 A KR 20090066317A KR 1020097009525 A KR1020097009525 A KR 1020097009525A KR 20097009525 A KR20097009525 A KR 20097009525A KR 20090066317 A KR20090066317 A KR 20090066317A

- Authority

- KR

- South Korea

- Prior art keywords

- film

- thin film

- gas

- silicon

- based thin

- Prior art date

Links

- 239000010409 thin film Substances 0.000 title claims abstract description 134

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 title claims abstract description 89

- 229910052710 silicon Inorganic materials 0.000 title claims abstract description 82

- 239000010703 silicon Substances 0.000 title claims abstract description 78

- 238000000034 method Methods 0.000 title claims abstract description 47

- 238000005268 plasma chemical vapour deposition Methods 0.000 title claims abstract description 17

- 239000010408 film Substances 0.000 claims abstract description 150

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims abstract description 69

- 238000000151 deposition Methods 0.000 claims abstract description 54

- 230000008021 deposition Effects 0.000 claims abstract description 54

- 238000001069 Raman spectroscopy Methods 0.000 claims abstract description 33

- 229910021417 amorphous silicon Inorganic materials 0.000 claims abstract description 16

- 238000010790 dilution Methods 0.000 claims abstract description 14

- 239000012895 dilution Substances 0.000 claims abstract description 14

- 238000011156 evaluation Methods 0.000 claims abstract description 7

- 230000005284 excitation Effects 0.000 claims abstract description 6

- 239000007789 gas Substances 0.000 claims description 145

- 230000015572 biosynthetic process Effects 0.000 claims description 91

- 239000000758 substrate Substances 0.000 claims description 41

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims description 12

- 239000001301 oxygen Substances 0.000 claims description 12

- 229910052760 oxygen Inorganic materials 0.000 claims description 12

- 239000002994 raw material Substances 0.000 claims description 12

- 239000003085 diluting agent Substances 0.000 claims description 10

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 claims description 9

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 7

- 229910052799 carbon Inorganic materials 0.000 claims description 7

- 229910052732 germanium Inorganic materials 0.000 claims description 7

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 claims description 5

- 230000008878 coupling Effects 0.000 claims description 4

- 238000010168 coupling process Methods 0.000 claims description 4

- 238000005859 coupling reaction Methods 0.000 claims description 4

- 230000001939 inductive effect Effects 0.000 claims description 4

- 125000004432 carbon atom Chemical group C* 0.000 claims description 2

- 239000000463 material Substances 0.000 abstract description 7

- 238000012545 processing Methods 0.000 description 18

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 16

- 238000002425 crystallisation Methods 0.000 description 15

- 230000008025 crystallization Effects 0.000 description 15

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 12

- 238000002474 experimental method Methods 0.000 description 11

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 10

- 230000007423 decrease Effects 0.000 description 10

- 230000001965 increasing effect Effects 0.000 description 9

- 229910021419 crystalline silicon Inorganic materials 0.000 description 7

- 239000011521 glass Substances 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 7

- 229910052757 nitrogen Inorganic materials 0.000 description 6

- 230000001737 promoting effect Effects 0.000 description 6

- 239000004065 semiconductor Substances 0.000 description 6

- 238000005259 measurement Methods 0.000 description 5

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 4

- 230000003247 decreasing effect Effects 0.000 description 4

- 230000007547 defect Effects 0.000 description 4

- 229910001873 dinitrogen Inorganic materials 0.000 description 4

- 229910001882 dioxygen Inorganic materials 0.000 description 4

- 238000009616 inductively coupled plasma Methods 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 239000000523 sample Substances 0.000 description 4

- 229910000077 silane Inorganic materials 0.000 description 4

- YZCKVEUIGOORGS-UHFFFAOYSA-N Hydrogen atom Chemical compound [H] YZCKVEUIGOORGS-UHFFFAOYSA-N 0.000 description 3

- 238000003486 chemical etching Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 3

- 239000002245 particle Substances 0.000 description 3

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- 239000003513 alkali Substances 0.000 description 2

- 125000004429 atom Chemical group 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 238000005224 laser annealing Methods 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- HYXIRBXTCCZCQG-UHFFFAOYSA-J [C+4].[F-].[F-].[F-].[F-] Chemical compound [C+4].[F-].[F-].[F-].[F-] HYXIRBXTCCZCQG-UHFFFAOYSA-J 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 238000003745 diagnosis Methods 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 239000012777 electrically insulating material Substances 0.000 description 1

- 229910052986 germanium hydride Inorganic materials 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000010248 power generation Methods 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- 239000012495 reaction gas Substances 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 238000004611 spectroscopical analysis Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000013589 supplement Substances 0.000 description 1

- PPMWWXLUCOODDK-UHFFFAOYSA-N tetrafluorogermane Chemical compound F[Ge](F)(F)F PPMWWXLUCOODDK-UHFFFAOYSA-N 0.000 description 1

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

Images

Classifications

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/44—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating

- C23C16/50—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating using electric discharges

- C23C16/505—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the method of coating using electric discharges using radio frequency discharges

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/22—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of inorganic material, other than metallic material

- C23C16/24—Deposition of silicon only

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02524—Group 14 semiconducting materials

- H01L21/02532—Silicon, silicon germanium, germanium

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/0262—Reduction or decomposition of gaseous compounds, e.g. CVD

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/18—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof

- H01L31/1804—Processes or apparatus specially adapted for the manufacture or treatment of these devices or of parts thereof comprising only elements of Group IV of the Periodic Table

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/547—Monocrystalline silicon PV cells

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- General Physics & Mathematics (AREA)

- Organic Chemistry (AREA)

- General Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Metallurgy (AREA)

- Mechanical Engineering (AREA)

- Materials Engineering (AREA)

- Inorganic Chemistry (AREA)

- Electromagnetism (AREA)

- Plasma & Fusion (AREA)

- Chemical Vapour Deposition (AREA)

- Photovoltaic Devices (AREA)

Abstract

본 발명은, 고주파 여기의 플라즈마 CVD법에 의한 실리콘계 박막의 형성방법에 있어서, 비교적 저온 하에서 저렴하게, 생산성 좋게 결정화도가 높은 다결정 실리콘게 박막을 형성한다. 성막시의 가스압을 0.0095 Pa∼64 Pa의 범위에서, 성막실 내로 도입하는 성막 원료 가스의 도입 유량(Ms)에 대한 희석가스의 도입 유량(Md)의 비(Md/Ms)를 0∼1200의 범위에서, 고주파 전력밀도를 0.0024 W/㎤∼11 W/㎤의 범위에서 각각 선택 결정함과 동시에, 성막시의 플라즈마 포텐셜을 25 V 이하, 플라즈마 중의 전자밀도를 1×1010개/㎤이상으로 유지하여 막을 형성하고, 또한, 그것들 압력 등의 조합을 레이저 라만 산란 분광법에 의한 막 중 실리콘의 결정성 평가에 있어서 아몰퍼스 실리콘 성분에 기인하는 Ia에 대한 결정화 실리콘 성분에 기인하는 Ic의 비(Ic/Ia=결정화도)가 8 이상이 되는 조합으로 하여 다결정 실리콘계 박막을 형성한다.

Description

본 발명은 플라즈마 CVD법에 의한 실리콘계 박막, 특히 다결정 실리콘계 박막의 형성방법에 관한 것이다.

종래, 액정 표시장치에서의 화소에 설치되는 TFT(박막 트랜지스터) 스위치의 재료로서, 또는 각종 집적회로, 태양전지 등의 제작에 실리콘계 박막(대표적으로는 실리콘 박막)이 채용되어 있다.

실리콘 박막은, 대부분의 경우, 실란계 반응가스를 사용한 플라즈마 CVD법에 의해 형성되고, 그 경우, 상기 박막의 대부분은 아몰퍼스 실리콘 박막이다.

아몰퍼스 실리콘 박막은, 피성막 기판의 온도를 비교적 낮게 하여 형성할 수 있고, 평행 평판형의 전극을 사용한 고주파 방전(주파수 13.56 MHz)에 의한 재료가스의 플라즈마 하에 용이하게 대면적으로 형성할 수 있다. 이것으로부터, 지금까지 액정 표시장치의 화소용 스위칭 디바이스, 태양전지 등에 널리 이용되고 있다.

그러나, 실리콘막 이용의 태양전지에서의 발전효율의 더 한층의 향상, 실리콘막 이용의 반도체 디바이스에서의 응답속도 등의 특성의 더 한층의 향상은 이와 같은 아몰퍼스 실리콘막에 구할 수는 없다. 그 때문에 결정성 실리콘 박막(예를 들면 다결정 실리콘 박막)의 이용이 검토되고 있다(예를 들면 일본국 특개2001-313257호 공보 참조).

다결정 실리콘 박막과 같은 결정성 실리콘 박막의 형성방법으로서는, 피성막 기판의 온도를 600℃∼700℃ 이상의 온도로 유지하여 저압 플라즈마 CVD, 열 CVD 등의 CVD법이나, 진공증착법, 스퍼터 증착법 등의 PVD법에 의해 막을 형성하는 방법(예를 들면 일본국 특개평5-234919호 공보, 특개평11-54432호 공보 참조), 각종 CVD법이나 PVD법에 의해 비교적 저온 하에서 아몰퍼스 실리콘 박막을 형성한 후, 후처리로서, 800℃ 정도 이상의 열처리 또는 600℃ 정도에서 장시간에 걸치는 열처리를 실시하는 방법(예를 들면 일본국 특개평5-218368호 공보 참조)이 알려져 있다.

또, 아몰퍼스 실리콘막에 레이저 어닐링처리를 실시하여 상기 막을 결정화시키는 방법도 알려져 있다(예를 들면 일본국 특개평8-124852호 공보, 특개2005-197656호 공보, 특개2004-253646호 공보 참조).

한편, 최근, 막 형성 대상 기판의 대형화에 따라, 넓은 범위에 걸쳐 플라즈마를 안정적으로 형성할 수 있는 방법으로서, 유도결합형 안테나로부터 플라즈마화 대상 가스에 고주파 전력을 인가하여 유도결합형 플라즈마를 생성하고, 상기 플라즈마 하에서 막을 형성하는 것도 주목받고 있다(예를 들면 일본국 특개2004-228354호 공보 참조).

[특허문헌 1]

일본국 특개2001-313257호 공보

[특허문헌 2]

일본국 특개평5-234919호 공보

[특허문헌 3]

일본국 특개평11-54432호 공보

[특허문헌 4]

일본국 특개평5-218368호 공보

[특허문헌 5]

일본국 특개평8-124852호 공보

[특허문헌 6]

일본국 특개2005-197656호 공보

[특허문헌 7]

일본국 특개2004-253646호 공보

[특허문헌 8]

일본국 특개2004-228354호 공보

그러나, 이들 중 기판을 고온에 노출하는 방법에서는, 기판으로서 고온에 견딜 수 있는 고가의 기판을 채용하지 않으면 안되고, 예를 들면 저렴한 저융점 유리 기판(내열온도 500℃ 이하)에 대한 결정성 실리콘 박막의 형성은 곤란하고, 그 때문에, 다결정 실리콘 박막과 같은 결정성 실리콘 박막의 제조비용이 높아진다는 문제가 있다.

또, 레이저 어닐링법에 의할 때에는, 저온 하에서 결정성 실리콘 박막을 얻을 수 있으나, 레이저 조사공정을 필요로 하는 것과, 매우 높은 에너지밀도의 레이저광을 조사하지 않으면 안되는 것 등으로부터, 이 경우도 결정성 실리콘 박막의 제조비용이 높아진다.

또한, 대면적 기판에 대한 막 형성에 적합하다고 생각되고 있는 유도결합형 플라즈마에 의한 실리콘 박막의 형성에 대해서는, 아직 그 형성방법이 충분히 확립되어 있다고는 할 수 없다.

그래서 본 발명은, 비교적 저온 하에서 저렴하고, 생산성 좋게 결정화도가 높은 다결정 실리콘계 박막을 형성할 수 있는 플라즈마 CVD법에 의한 실리콘계 박막의 형성방법을 제공하는 것을 제 1 과제로 한다.

또 본 발명은, 상기 제 1 과제를 해결할 수 있음과 동시에 결함이 적은 양질의 다결정 실리콘계 박막을 형성할 수 있는 플라즈마 CVD법에 의한 실리콘계 박막의 형성방법을 제공하는 것을 제 2 과제로 한다.

본 발명자의 연구에 의하면, 다결정 실리콘계 박막을 TFT(박막 트랜지스터) 스위치의 제작, 또는 각종 집적회로, 태양전지 등의 제작에 반도체막으로서 이용하고자 하는 경우, 그것들 스위치 등의 성능향상을 위해서는, 상기 막은, 레이저 라만 산란 분광법에 의한 막 중 실리콘의 결정성 평가에 있어서 아몰퍼스 실리콘 성분에 기인하는 라만 산란 피크강도(Ia)에 대한 결정화 실리콘 성분에 기인하는 라만 산란 피크강도(Ic)의 비(Ic/Ia = 결정화도)가 높은 쪽이 바람직하고, 구체적으로는, 상기 결정화도가 8 이상이 바람직하고, 10 이상이 더욱 바람직하다. 결정화도(Ic/Ia)=10 는, 실리콘 성분의 결정화의 정도가 100%에 가깝다.

본 발명자는 이와 같은 결정화도 8 이상의 다결정 실리콘계 박막을 형성하도록 연구를 거듭한 바,

(1) 막 형성에는 플라즈마 CVD법을 이용할 수 있는 것, 다시 말하면, 실리콘 원자를 함유하는 성막 원료 가스 또는 상기 실리콘 원자를 함유하는 성막 원료 가스와 이것을 희석하는 희석가스를 성막실 내로 도입하고, 상기 도입 가스를 고주파 여기로 플라즈마화하고, 상기 플라즈마 하에서 상기 성막실 내에 배치된 피성막 기판 상에 실리콘계 박막을 형성하는 플라즈마 CVD법을 이용할 수 있고, 상기 플라즈마 CVD법에 의해 비교적 저온 하에 생산성 좋게 막을 형성할 수 있고, 예를 들면 내열온도 500℃ 이하의 저렴한 저융점 유리 기판(대표적으로는 무알칼리 유리 기판)에 대한 막 형성도 가능하여, 그 만큼 저렴하게 막을 형성할 수 있는 것, 및

(2) 상기 플라즈마 CVD법에 의한 성막시의 성막실 내압은 0.0095 Pa∼64 Pa의 범위에서 선택 결정하는 것이 바람직한 것,

(3) 성막시에 상기 성막실 내로 도입하는 상기 성막 원료 가스의 도입 유량 Ms[sccm]에 대한 상기 희석가스의 도입 유량 Md[sccm]의 비(Md/Ms)는 0∼1200의 범위에서 선택 결정하는 것이 바람직한 것(Md/Ms=0은 희석가스를 사용하지 않은 경우이다.),

(4) 성막시의 고주파 전력밀도를 0.0024 W/㎤∼11 W/㎤의 범위에서 선택 결정하는 것이 바람직한 것,

(5) 성막시의 플라즈마 포텐셜은 25 V 이하로 유지하고, 성막시의 플라즈마중의 전자밀도를 1 × 1010개/㎤ 이상으로 유지하는 것이 바람직한 것,

(6) 상기 여러가지 조건을 만족하여 결정화도 8 이상의 다결정 실리콘계 박막을 형성할 수 있는 것을 발견하였다.

성막시의 성막실 내압은 0.0095 Pa∼64 Pa의 범위에서 선택 결정하는 것이 바람직한 이유는, 0.0095 Pa보다 낮아지면, 플라즈마가 불안정해지거나, 막 형성속도가 저하하기도 하고, 극단적인 경우는 플라즈마의 점등, 유지를 견딜 수 없게 되고, 64 Pa보다 높아지면, 실리콘의 결정성이 저하하여, 결정화도(Ic/Ia)≥8의 다결정 실리콘계 박막의 형성이 곤란해지기 때문이다.

성막시의 성막 원료 가스의 도입 유량 Ms[sccm]에 대한 상기 희석가스의 도입 유량 Md[sccm]의 비(Md/Ms)는 0∼1200의 범위로 설정하는 것이 바람직한 이유는, 비(Md/Ms)가 1200을 넘으면 실리콘의 결정성이 저하하고, 결정화도(Ic/Ia)≥8의 다결정 실리콘계 박막의 형성이 곤란해지는 데다가, 막 형성속도가 저하하기 때문이다.

성막시의 고주파 전력밀도는 0.0024 W/㎤∼11 W/㎤의 범위에서 선택 결정하는 것이 바람직한 이유는, 0.0024 W/㎤보다 작아지면, 플라즈마가 불안정해지거나, 막 형성속도가 저하하고, 극단적인 경우는 플라즈마의 점등, 유지가 곤란해지며, 11 W/㎤보다 커지면, 실리콘의 결정성이 저하하여 결정화도(Ic/Ia)≥8의 다결정 실리콘계 박막의 형성이 곤란해지거나, 막 형성속도가 저하하기 때문이다.

여기서 「고주파 전력밀도[W/㎤]」란, 투입 고주파 전력[W]을 플라즈마생성공간(통상은 성막실)의 체적 [㎤]으로 나눈 것이다.

또, 성막시의 플라즈마 포텐셜을 25 V 이하로 유지하는 것이 바람직한 이유는, 25 V보다 높아지면, 실리콘의 결정화가 저해되기 쉬워지고, 결정화도(Ic/Ia)≥ 8의 다결정 실리콘계 박막의 형성이 곤란해지기 때문이다.

그러나, 너무 낮아지면, 플라즈마의 유지가 곤란해지기 때문에, 그것에는 한정되지 않으나, 대략 10 V 이상으로 하면 된다.

또, 성막시의 플라즈마 중의 전자밀도를 1×1010개/㎤ 이상으로 유지하는 것이 바람직한 이유는, 전자밀도가 1×1010개/㎤보다 작아지면, 막 형성에 기여하는 이온밀도도 저하하여 실리콘의 결정화도가 저하하거나, 막 형성속도가 저하하기도 하여, 결정화도(Ic/Ia)≥8의 다결정 실리콘계 박막의 형성이 곤란해지기 때문이다.

그러나, 너무 지나치게 크면, 막 및 피성막 기판이 비래(飛來)하는 이온 등의 하전입자에 의해 대미지를 받기 쉬워지기 때문에, 결정화도(Ic/Ia)≥8의 달성을 고려하면, 반드시 그것에는 한정되지 않으나, 대략 1.0×1012개/㎤정도 이하로 하면 된다.

또한, 플라즈마 포텐셜의 증감은 플라즈마 중의 전자밀도의 증감에 영향을 준다. 플라즈마 포텐셜이 높아지면, 전자밀도도 커지는 경향이 있고, 플라즈마 포텐셜이 낮아지면, 전자밀도도 작아지는 경향에 있다. 따라서 이들 양자는 결정화도(Ic/Ia)≥8의 달성을 고려하여 선택 결정하지 않으면 안된다.

이와 같은 플라즈마 포텐셜이나 플라즈마의 전자밀도는, 인가하는 고주파 전력의 크기(환언하면 고주파 전력밀도), 고주파의 주파수, 성막압 등 중 적어도 하나를 제어함으로써 조정할 수 있다.

이상의 식견에 의거하여, 본 발명은 상기 제 1 과제를 해결하기 위하여,

실리콘 원자를 함유하는 성막 원료 가스 및 희석가스 중 적어도 상기 성막 원료 가스를 성막실 내로 도입하여, 상기 도입 가스를 고주파 여기로 플라즈마화하고, 상기 플라즈마 하에서 상기 성막실 내에 배치된 피성막 기판 상에 실리콘계 박막을 형성하는 플라즈마 CVD법에 의한 실리콘계 박막의 형성방법이고, 성막시의 성막실 내압을 0.0095 Pa∼64 Pa의 범위에서, 성막시에 상기 성막실 내로 도입하는 상기 성막 원료 가스의 도입 유량 Ms[sccm]에 대한 상기 희석가스의 도입 유량 Md[sccm]의 비(Md/Ms)를 0∼1200의 범위에서, 성막시의 고주파 전력밀도를 0.0024 W/㎤∼11 W/㎤의 범위에서 각각 선택 결정함과 동시에, 성막시의 플라즈마 포텐셜을 25 V 이하로, 성막시의 플라즈마 중의 전자밀도를 1 × 1010개/㎤ 이상으로 유지하여 막을 형성하고,

또한, 상기 선택 결정되는 성막시의 성막실 내압, 성막 원료 가스와 희석가스의 도입 유량비(Md/Ms) 및 고주파 전력밀도 및 상기 유지되어야 할 플라즈마 포텐셜 및 플라즈마 중의 전자밀도의 조합이 레이저 라만 산란 분광법에 의한 막 중 실리콘의 결정성 평가에 있어서 아몰퍼스 실리콘 성분에 기인하는 라만 산란 피크강도(Ia)에 대한 결정화 실리콘 성분에 기인하는 라만 산란 피크강도(Ic)의 비(Ic/Ia= 결정화도)가 8 이상이 되는 다결정 실리콘계 박막이 얻어지는 조합으로 하여 막을 형성함으로써 다결정 실리콘계 박막을 형성하는 플라즈마 CVD법에 의한 실리콘계 박막의 형성방법을 제공한다.

본 발명에 관한 실리콘계 박막의 형성방법에서는, 가스 플라즈마화를 위하여 투입하는 고주파 전력을 효율좋게 이용하여 성막실 내에 고밀도 플라즈마를 형성하고, 또 넓은 범위에 걸쳐 플라즈마를 안정적으로 형성하여 가능한 한 균일한 막을 형성하기 위하여, 상기 성막실 내로의 도입 가스의 고주파 여기에 의한 플라즈마화를 상기 성막실 내에 설치한 유도결합형 안테나로부터 상기 도입 가스로 고주파 전력을 인가함으로써 행하여도 된다.

이와 같이 유도결합형 안테나 성막실 내에 설치할 때는, 상기 안테나를 절연성재료로 피복하는 것이 바람직하다. 안테나를 전기절연성 재료로 피복함으로써, 자기바이어스에 의해 안테나가 플라즈마로부터의 하전입자에 의해 스퍼터링되어, 안테나 유래의 스퍼터 입자가 형성하려고 하는 막 중으로 혼입하는 것을 억제할 수 있다.

이와 같은 절연성재료로서는, 석영 유리나 안테나의 양극 산화 처리에 의한 재료를 예시할 수 있다.

어쨌든, 본 발명에 관한 막을 형성방법에 의해 형성할 수 있는 다결정 실리콘계 박막으로서는, 실리콘으로 이루어지는 다결정 실리콘 박막을 들 수 있으나, 이 외에, 예를 들면, 게르마늄을 함유하는(예를 들면 10원자% 이하의 게르마늄을 함유한다) 다결정 실리콘계 박막이나 탄소를 함유하는(예를 들면 10원자% 이하의 탄소를 함유한다) 다결정 실리콘계 박막도 예시할 수 있다.

어쨌든, 상기 아몰퍼스 실리콘성분에 기인하는 라만 산란 피크강도(Ia)로서 파수 480-1cm에서의 라만 산란강도를 채용할 수 있다. 또, 상기 결정화 실리콘 성분에 기인하는 라만 산란 피크강도(Ic)로서 파수 520-1 cm 또는 그 부근에서의 라만산란 피크강도를 채용할 수 있다.

다결정 실리콘 박막을 형성하는 경우, 상기 실리콘 원자를 함유하는 원료 가스의 예로서, 모노실란(SiH4)가스, 디실란(Si2H6)가스 등의 실란계 가스를 들 수 있고, 희석가스를 사용하는 경우에는, 상기 희석가스로서 수소가스를 예시할 수 있다.

게르마늄을 함유하는 다결정 실리콘계 박막을 형성하는 경우는, 상기 실리콘원자를 함유하는 성막 원료 가스로서, 게르마늄원자도 함유하는 가스를 채용하면 된다.

이와 같은 성막 원료 가스의 구체예로서는, 모노실란(SiH4)가스, 디실란(Si2 H6)가스 등의 실란계 가스에 게르마늄을 함유하는 가스[예를 들면 모노게르만(GeH4)가스, 4불화 게르마늄(GeF4)가스]를 혼합한 가스를 예시할 수 있다.

이 경우도 희석가스를 사용하는 경우에는, 상기 희석가스로서 예를 들면 수소가스를 사용할 수 있다.

탄소를 함유하는 다결정 실리콘계 박막을 형성하는 경우는, 상기 실리콘 원자를 함유하는 성막 원료 가스로서, 탄소 원자도 함유하는 가스를 채용하면 된다.

이와 같은 성막 원료 가스의 구체예로서는, 모노실란(SiH4)가스, 디실란(Si2 H6)가스 등의 실란계 가스에 탄소를 함유하는 가스[예를 들면 메탄(CH4)가스, 4불화탄소(CF4)가스]를 혼합한 가스를 예시할 수 있다.

이 경우도 희석가스를 사용하는 경우에는, 상기 희석가스로서 예를 들면 수소가스를 사용할 수 있다.

그런데, 다결정 실리콘계 박막은, 그 표면이 산소나 질소 등으로 종단 처리되어 있는 것이 바람직하다. 여기서「산소나 질소 등에 의한 종단 처리」란, 다결정 실리콘계 박막의 표면에 산소나, 질소가 결합하여, (Si-0)결합이나, (Si-N)결합, 또는 (Si-0-N)결합 등을 일으키게 하는 것을 말한다.

이와 같은 종단 처리에 의한 산소나 질소의 결합은, 종단 처리 전의 결정성 실리콘 박막 표면에, 예를 들면, 댕글링결합(dangling bond)과 같은 결함이 있어도, 이것을 보충하는 것과 같이 기능하고, 결정성 실리콘 박막 전체로서 실질상 결함이 억제된 양질의 막 상태를 형성한다. 이와 같은 종단 처리가 실시된 결정성 실리콘 박막은 전자 디바이스의 재료로서 이용된 경우, 상기 디바이스에 요구되는 특성이 향상한다. 예를 들면, TFT 재료로서 사용된 경우, TFT 에서의 전자 이동도를 향상시키거나, 0FF 전류를 저감시킬 수 있다. 또, 장시간의 TFT의 사용에서도 전압 전류 특성이 변화되기 어려운 등의 신뢰성이 향상한다.

그래서 본 발명은 상기 제 2 과제를 해결하기 위하여,

상기 본 발명에 관한 실리콘계 박막의 형성방법에 있어서, 상기 다결정 실리콘계 박막을 형성 후에, 산소함유 가스 및 질소함유 가스로부터 선택된 적어도 1종의 종단 처리용 가스에 고주파 전력을 인가함으로써 발생시킨 종단 처리용 플라즈마 하에서 상기 다결정성 실리콘계 박막의 표면을 종단 처리하는 실리콘계 박막의 형성방법도 제공한다.

이와 같은 종단 처리는, 지장이 없으면, 다결정성 실리콘계 박막을 형성 후에, 동일한 성막실 내로 종단 처리용 가스를 도입하여, 상기 가스에 고주파 전력을 인가하여 종단 처리용 플라즈마를 발생시키고, 상기 플라즈마 하에서 다결정성 실리콘계 박막의 표면을 종단 처리하여도 된다.

또, 성막실로부터 독립된 종단 처리실을 준비하고, 상기 종단 처리실에서 종단 처리공정을 실시하여도 된다.

또, 성막실에서 다결정성 실리콘계 박막을 형성한 후, 상기 다결정성 실리콘계 박막이 형성된 기판을 상기 성막실에(직접적으로 또는 물품 반송로봇을 가지는 반송실을 거치는 등으로 하여 간접적으로) 연달아 설치된 종단 처리실로 반입하여, 상기 종단 처리실에서 종단 처리를 실시하여도 된다.

이와 같은 종단 처리실에서의 종단 처리에 있어서, 종단 처리용 가스에 고주파 전력을 인가하는 고주파 방전 전극에 대해서도, 상기와 같은 유도결합 플라즈마를 발생시키는 안테나로 하여도 된다.

종단 처리용 가스로서는, 상기한 바와 같이 산소함유 가스 또는(및) 질소함유 가스를 사용하나, 산소함유 가스로서는, 산소가스나 산화 질소(N20)가스를 예시할 수 있고, 질소함유 가스로서는, 질소가스나 암모니아(NH3)가스를 예시할 수 있다.

이상 설명한 바와 같이 본 발명에 의하면, 비교적 저온 하에서 저렴하고, 생산성 좋게 결정화도가 높은 다결정 실리콘계 박막을 형성할 수 있는 플라즈마 CVD법에 의한 실리콘계 박막의 형성방법을 제공할 수 있다.

또 본 발명에 의하면, 이와 같은 이점을 가지는 실리콘계 박막의 형성방법으로서, 결함이 적은 양질의 다결정 실리콘계 박막을 형성할 수 있는 플라즈마 CVD법에 의한 실리콘계 박막의 형성방법을 제공할 수 있다.

도 1은 본 발명의 다결정 실리콘계 박막의 형성방법에 사용할 수 있는 박막 형성장치의 일례를 나타내는 도,

도 2는 형성된 막의 결정화도(Ic/Ia)와 성막시의 성막실 내압과의 관계를 나타내는 도,

도 3은 형성된 막의 결정화도(Ic/Ia)와 성막시의 가스 도입 유량비와의 관계를 나타내는 도,

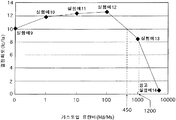

도 4는 형성된 막의 결정화도(Ic/Ia)와 성막시의 고주파 전력밀도와의 관계를 나타내는 도,

도 5는 형성된 막의 결정화도(Ic/Ia)와 성막시의 플라즈마 포텐셜과의 관계를 나타내는 도면이다.

※ 도면의 주요부분에 대한 부호의 설명

1 : 성막실 11 : 성막실(1)의 천정벽

111 : 천정벽(11)에 설치한 전기 절연성 부재

2 : 기판 홀더 21 : 히터

3 : 유도결합형 안테나 31, 32 : 안테나(3)의 끝부

4 : 고주파 전원 41 : 매칭 박스

5 : 배기 펌프 51 : 컨덕턴스 밸브

6 : 성막 원료 가스 공급부 7 : 희석가스 공급부

8 : 종단 처리용 가스 공급부 10 : 플라즈마 진단장치

10a : 랑뮤어(Langmuir) 프로브 10b : 플라즈마 진단부

100 : 압력계

이하 본 발명의 실시형태에 대하여 도면을 참조하여 설명한다.

도 1은 본 발명에 관한 실리콘계 박막(다결정 실리콘계 박막)의 형성방법의 실시에 사용할 수 있는 박막 형성장치의 일례의 구성의 개략을 나타내고 있다.

도 1의 박막 형성장치는, 성막실(1)을 구비하고 있고, 성막실(1) 내의 하부에는 피성막 기판(S)을 유지하는 홀더(2)가 설치되어 있다. 홀더(2)에는 이것에 유지되는 기판(S)을 가열할 수 있는 히터(21)가 내장되어 있다.

성막실(1) 내 상부의, 홀더(2)에 대향하는 영역에 유도결합형 안테나(3)가 배치되어 있다. 안테나(3)는 도립(倒立) 문(門)형상의 것으로, 그 양쪽 끝부(31, 32)는 성막실(1)의 천정벽(11)에 설치한 절연성부재(111)를 관통하여 성막실 밖까지 연장되어 있다. 성막실(1) 내에서의 안테나(3)의 가로방향 폭은 w, 세로방향 길이는 h 이다.

성막실 밖까지 나온 안테나 끝부(31)에는 매칭 박스(41)를 거쳐 출력 가변의 고주파 전원(4)이 접속되어 있다. 다른쪽의 안테나 끝부(32)는 접지되어 있다.

또, 성막실(1)에는 배기량 조정밸브(본 예에서는 컨덕턴스 밸브)(51)를 거쳐 배기 펌프(5)가 접속되어 있다. 또한, 가스 도입관(61)을 거쳐 성막 원료 가스공급부(6)가 접속되어 있음과 동시에, 가스 도입관(71)을 거쳐 희석가스 공급부(7)가 접속되어 있다. 또한, 가스 도입관(81)을 거쳐 종단 처리용 가스 공급부(8)가 접속되어 있다. 가스 공급부(6, 7 및 8)의 각각에는 성막실 내로의 가스 도입량을 조정하기 위한 매스플로우 컨트롤러나 가스원 등이 함유되어 있다.

홀더(2)는 성막실(1)을 거쳐 접지 전위가 된다.

또, 성막실(1)에 대하여 랑뮤어 프로브 이용의 플라즈마 진단장치(10) 및 압력계(100)가 설치되어 있다. 플라즈마 진단장치(10)는 성막실(1) 내로 삽입된 랑뮤어 프로브(10a)와 상기 프로브에서 얻어지는 플라즈마정보에 의거하여 플라즈마 포텐셜 및 플라즈마 중의 전자밀도를 구할 수 있다. 성막실 내 압력은 압력계(100)로 계측할 수 있다.

이상 설명한 박막 형성장치에 의하면, 예를 들면 다음과 같이 하여 다결정 실리콘계 박막을 형성할 수 있고, 또한 상기 막에 대하여 종단 처리를 행할 수 있다.

먼저, 성막실(1) 내의 홀더(2) 상에 피성막 기판(S)를 유지시키고, 필요에 따라 히터(21)로 상기 기판을 가열하고, 배기 펌프(5)를 운전하여 성막실 내 압력을 성막시의 압력보다 낮은 압력까지 배기한다. 이어서, 성막실(1) 내로 성막 원료 가스공급부(6)로부터 실리콘 원자를 함유하는 성막 원료 가스를 도입하고, 또는 가스공급부(6)로부터 실리콘 원자를 함유하는 성막 원료 가스를 도입함과 동시에 희석가스 공급부(7)로부터 희석가스를 도입하고, 컨덕턴스 밸브(51)로 성막실 내 압력을 성막시 압력으로 조정하면서 가변 고주파 전원(4)으로부터 매칭 박스(41)를 거쳐 안테나(3)로 고주파 전력을 공급한다.

그렇게 하면, 상기 안테나로부터 성막실 내 가스에 고주파 전력이 인가되고, 그것에 의하여 상기 가스가 고주파 여기되어 유도결합 플라즈마가 발생하고, 상기 플라즈마 하에서 기판(S) 상에 실리콘계 박막이 형성된다.

이 막 형성에서는, 성막시의 성막실 내압을 0.0095 Pa∼64 Pa의 범위에서, 성막실(1) 내로 도입하는 성막 원료 가스의 도입 유량 Ms[sccm]에 대한 희석가스의 도입 유량 Md[sccm]의 비(Md/Ms)를 0∼1200의 범위에서, 고주파 전력밀도를 0.0024 W/㎤∼11 W/㎤의 범위에서 각각 선택 결정하고, 또한, 성막시의 플라즈마 포텐셜을 25 V 이하로, 성막시의 플라즈마 중의 전자밀도를 1×1010개/㎤ 이상의 범위로 유지하여 막을 형성한다.

또한, 상기 선택 결정되는 성막시의 성막실 내압, 성막 원료 가스와 희석가스의 도입 유량비(Md/Ms) 및 고주파 전력밀도 및 상기 유지되어야 할 플라즈마 포 텐셜 및 플라즈마 중의 전자밀도의 조합이 레이저 라만 산란 분광법에 의한 막 중 실리콘의 결정성 평가에 있어서 아몰퍼스 실리콘 성분에 기인하는 라만 산란 피크강도(Ia)에 대한 결정화 실리콘 성분에 기인하는 라만 산란 피크강도(Ic)의 비(Ic/Ia=결정화도)가 8 이상이 되는, 더욱 바람직하게는 10 이상이 되는 다결정 실리콘계 박막이 얻어지는 조합으로 하여 막을 형성한다.

이와 같이 하여, 기판(S) 상에 다결정 실리콘계 박막을 형성한다.

성막실 내의 압력은 가스 도입량에도 영향을 받지만, 가스 도입량을 일정화한 후, 컨덕턴스 밸브(51)로 조정하는 것이 간단하다. 성막실 내압은 압력계(100)로 파악할 수 있다. 성막실 내로의 각 가스 도입량의 조정 및 도입량 비(Md/Ms)의 조정은 상기 각 가스 공급부의 매스플로우 컨트롤러에 의해 행할 수 있다.

고주파 전력밀도의 조정은 고주파 전원(4)의 출력 조정에 의해 행할 수 있다.

플라즈마 포텐셜 및 전자밀도는 상기 플라즈마 진단장치(10)에 의해 파악할 수 있다.

이 막을 형성함에 있어서, 결정화도(Ic/Ia)가 8 이상, 더욱 바람직하게는 10 이상을 달성하는 성막시의 성막실 내 압력, 가스 도입량 비(Md/Ms), 고주파 전력밀도, 플라즈마 포텐셜 및 전자밀도는 각각 상기 범위에서 결정하는 것이나, 그 방법으로서는, 예를 들면, 성막실 내 압력, 가스 도입량 비(Md/Ms) 및 고주파 전력밀도에 대하여, 상기 플라즈마 진단장치(10)에서 플라즈마 포텐셜이 25 V 이하인 것 및 전자밀도가 1×1010개/㎤ 이상의 범위에 있는 것을 확인할 수 있을 때의 성막실 내압, 가스 도입량 비(Md/Ms) 및 고주파 전력밀도로서, 각각이 상기 범위 내에 있는 것을 선택 결정하는 경우를 들 수 있다.

또는, 결정화도(Ic/Ia)가 8 이상, 더욱 바람직하게는 10 이상을 달성하는 성막시의 성막실 내 압력, 가스 도입량 비(Md/Ms), 고주파 전력밀도, 플라즈마 포텐셜및 전자밀도의 조합에 대하여 미리 실험 등에 의해 구하여 두고, 성막실 내 압력,가스 도입량 비(Md/Ms), 고주파 전력밀도, 플라즈마 포텐셜 및 전자밀도를, 그 조합군에서 선택 결정하여도 된다.

이와 같이 하여 결정화도가 8 이상인 실리콘을 주성분으로 하는 다결정 실리콘계 박막을 형성한 후, 상기 막에 종단 처리를 실시하여도 된다.

예를 들면, 가스공급부(6)(또는 6, 7)로부터 실(1) 내로의 가스도입, 전원(4)으로부터 안테나(3)에 대한 전력 인가를 정지하는 한편, 배기펌프(5)의 운전을 속행하여 성막실(1) 내로부터 잔존 가스를 가능한 한 배출한다.

그 후, 기판 온도를 예를 들면 250℃∼400℃의 범위로 유지하면서, 종단 처리 가스 공급부(8)로부터 종단 처리 가스인 예를 들면 산소가스 또는 질소가스를 50 sccm∼500 sccm의 범위의 유량으로 성막실(1) 내로 도입함과 동시에 성막실 내를 종단 처리를 위한 압력(0.1 Pa∼10 Pa 정도의 범위의 압력)으로 설정하고, 또한 고주파 전원(4)으로부터 매칭 박스(41)를 거쳐 종단 처리용 고주파 전력(예를 들면 13.56 MHz, 0.5 kW∼3 kW 정도의 전력)을 안테나(3)에 인가하여 종단 처리용 가스 를 플라즈마화하고, 상기 플라즈마 하에서 소정의 처리시간(예를 들면 0.5분∼10분정도), 기판(S) 상의 다결정 실리콘계 박막의 표면에 종단 처리를 실시하고, 그것에 의하여 상기 다결정 실리콘계 박막을 더욱 양질의 것으로 하다.

이와 같이 산소 또는 질소로 종단 처리된 다결정 실리콘계 박막을 예를 들면 TFT용 반도체막으로서 사용하면, TFT 전기 특성으로서의 전자 이동도가, 종단 처리하지 않은 경우보다 한층 향상하고, 또한, 0FF 전류가 저감된다.

또한, 산소함유 가스에 의한 종단 처리의 전 또는 후에 질소함유 가스에 의한 종단 처리를 실시하여도 된다.

다음에, 다결정 실리콘계 박막의 예로서 다결정 실리콘 박막을 형성한 실험예에 대하여 설명한다.

실험에 앞서 유도결합형 안테나(3)로서 다음의 것을 준비하고, 실험에서는 그것들 안테나 중 어느 하나를 사용하였다.

안테나 A B C D E F

가로방향 폭(w) 140 mm 120 mm 50 mm 50 mm 50 mm 50 mm

세로방향 길이(h) 110 mm 70 mm 80 mm 65 mm 55 mm 50 mm

형성된 막의 실리콘의 결정화도의 평가는 He-Ne 레이저(파장 632.8 nm)를 사용한 레이저 라만 산란 분광법에 의해 행하고, 막 중 실리콘의 결정성 평가에서 아몰퍼스 실리콘 성분에 기인하는 라만 산란 피크강도(Ia)에 대한 결정화 실리콘 성분에 기인하는 라만 산란 피크강도(Ic)의 비(Ic/Ia= 결정화도)로 행하였다.

또, 여기서는 아몰퍼스 실리콘 성분에 기인하는 라만 산란 피크강도(Ia)로서 파수 480-1㎝에서의 라만 산란강도를 채용하고, 결정화 실리콘 성분에 기인하는 라만 산란 피크강도(Ic)로서 파수 520-1cm 또는 그 부근에서의 라만 산란 피크강도를 채용하였다.

어느 것의 실험에서도, 막 형성에 있어서는 기판(S)으로서 무알칼리 유리 기판을 홀더(2)에 유지시키고, 히터(21)로 상기 기판의 온도를 400℃로 하고, 성막 원료 가스로서 모노실란(SiH4)가스를 사용하며, 희석가스를 사용하는 경우는 상기 가스로서 수소가스(H2)를 사용하고, 당초 성막실(1)로부터 배기 펌프(5)로 배기하여 상기 실 내압을 10-5Pa 오더로 하고, 그 후 각 실험과 같이 상기 실 내로의 가스 도입, 안테나(3)에 대한 주파수 13.56 MHz의 고주파 전력인가 및 플라즈마 점등에 의해 무알칼리 유리 기판 상에 실리콘 박막을 형성하였다.

사용하는 안테나를 상기 안테나 C로 하고, 수소가스의 도입 유량(Md)을 20 sccm의 일정하게 함과 동시에, 모노실란가스의 도입 유량(Ms)을 2 sccm의 일정하게 하고, 따라서 도입 유량비(Md/Ms)를 일정값 10으로 하고, 또한 투입하는 고주파 전력의밀도를 0.01 W/㎤의 일정하게 하고, 성막실 내압을 변화시킨 참고 실험예 1, 실험예 2∼6 및 참고 실험예 7∼8을 이하의 표 1에 정리하여 나타낸다.

또, 형성된 실리콘 박막의 결정화도(Ic/Ia)의 측정결과와 성막시의 성막실 내압과의 관계를 도 2에 나타낸다.

실험예 2∼6에서는 결정화도 8 이상으로 결정화한 실리콘 박막이 형성되었다.

그러나, 참고 실험예 1에서는 플라즈마가 점등하지 않고, 실리콘 박막을 형성할 수 없었다. 이것은 성막압이 너무 낮기 때문에 플라즈마의 점등, 유지에 충분한 가스분자가 실(1) 내에 존재하지 않았기 때문이다.

실험예 6 및 참고 실험예 7, 8에서는 Ic/Ia가 점차로 저하하고, 참고 실험예7, 8에서는 Ic/Ia가 크게 저하되었으나, 이것은 성막압력이 높아짐에 의하여, 실리콘의 결정화에 중요한 역할을 하는 원자형상 수소 라디칼의 생성이 억제되었기 때문이다.

실험예 3, 2에서는 압력이 낮아짐에도 불구하고 Ic/Ia가 저하 경향을 나타내고 있으나, 이것은 원자형상 수소 라디칼의 생성이 촉진되면서도, 결정화 촉진작용과 동시 평행적으로 진행되는 케미컬 에칭적인 대미지 작용이 상회하는 경향이 있었기 때문이다. 또, 동시에 플라즈마 포텐셜이 상승함으로써 플라즈마로부터의 대미지 작용도 증가하였기 때문이다.

도 2에서, 성막시의 성막실 내압을 0.0095 Pa∼64 Pa 정도의 범위의 것으로 하면, Ic/Ia≥8을 달성할 수 있는 것을 알 수 있다. 또, 성막시의 성막실 내압을 0.048 Pa∼32 Pa 정도의 범위의 것으로 하면, 더욱 바람직한 Ic/Ia≥10을 달성할 수 있는 것을 알 수 있다.

다음에, 사용하는 안테나를 상기 안테나 C로 하고, 성막시의 압력을 1.3 Pa의 일정하게 하며, 투입하는 고주파 전력의 밀도를 0.01 W/㎤의 일정하게 하고, 가스 도입 유량비(Md/Ms)를 변화시킨 실험예 9∼13 및 참고 실험예 14를 이하의 표 2에 정리하여 나타낸다.

형성된 실리콘 박막의 결정화도(Ic/Ia)의 측정결과와 성막시의 가스 도입 유량비(Md/Ms)와의 관계를 도 3에 나타낸다.

실험예 9∼13에서는 결정화도 8 이상으로 결정화한 실리콘 박막이 형성되었다.

실험예 9, 10, 11, 12와 Ic/Ia가 증가하는 것은, 수소가스 도입 유량을 증가시킬수록 원자형상 수소 라디칼이 증가하여, 결정화가 촉진되기 때문이다. 실험예 13, 참고 실험예 14와 Ic/Ia가 저하하여 가고, 참고 실험예 14에서는 Ic/Ia가 현저하게 저하한 것은, 원자형상 수소 라디칼이 증가하면서도, 결정화 촉진작용과 동시평행적으로 진행하는 케미컬 에칭적인 대미지 작용이 상회하는 경향이 있었기 때문이다.

또한, 희석가스를 채용하지 않은 실험예 9에서도 결정화도가 높아져 있는 것은, 모노실란가스가 분해되고, 그 결과 수소(H)가 공급되어, 원자형상 수소 라디칼로 되어 있기 때문이다.

도 3에서 성막시의 가스 도입량 비(Md/Ms)를 0∼1200 정도의 범위의 것으로 하면 Ic/Ia≥8를 달성할 수 있는 것을 알 수 있다. 또, 성막시의 가스 도입량 비(Md/Ms)를 0∼450 정도의 범위의 것으로 하면, 더욱 바람직한 Ic/Ia≥10을 달성할 수 있는 것을 알 수 있다.

다음에, 사용하는 안테나를 상기 안테나 C로 하고, 성막시의 압력을 1.3 Pa의 일정하게 하며, 수소가스의 도입량(Md)을 20 sccm의 일정하게 함과 동시에, 모노실란가스의 도입량(Ms)을 2 sccm의 일정하게 하고, 따라서 도입 유량비(Md/Ms)를 일정값 10으로 하며, 투입하는 고주파 전력의 밀도를 변화시킨 참고 실험예 15∼16, 실험예 17∼20 및 참고 실험예 21를 이하의 표 3에 정리하여 나타낸다.

또, 형성된 실리콘 박막의 결정화도(Ic/Ia)의 측정결과와 성막시의 고주파 전력밀도와의 관계를 도 4에 나타낸다.

실험예 17∼20에서는 결정화도 8 이상으로 결정화한 실리콘 박막이 형성되었다.

참고 실험예 15에서는 플라즈마가 점등하지 않고, 실리콘 박막을 형성할 수없었다. 이것은 고주파 전력밀도가 너무 낮기 때문에, 가스를 플라즈마화할 수 없기 때문이다.

참고 실험예 16, 실험예 17, 18과 Ic/Ia가 증가하는 것은, 고주파 전력밀도를 증가할수록 가스의 분해(플라즈마화)가 진행되어, 원자형상 수소 라디칼의 생성이 촉진되기 때문이다.

실험예 19, 20, 참고 실험예 21과 Ic/Ia가 저하하고, 참고 실험예 21에서는 Ic/Ia가 현저하게 저하되어 있으나, 이것은, 원자형상 수소 라디칼이 증가하면서도, 결정화 촉진작용과 동시 평행적으로 진행하는 케미컬 에칭적인 대미지 작용이 상회하는 경향이 있었기 때문이다.

도 4에서, 성막시의 고주파 전력밀도를 0.0024 W/㎤∼11 W/㎤정도의 범위의 것으로 하면, Ic/Ia≥8를 달성할 수 있는 것을 알 수 있다. 또, 성막시의 고주파 전력밀도를 0.0045 W/㎤∼4.1 W/㎤ 정도의 범위의 것으로 하면, 더욱 바람직한 Ic/Ia≥10을 달성할 수 있는 것을 알 수 있다.

다음에, 성막시의 압력을 1.3 Pa의 일정하게 하고, 수소가스의 도입량(Md)을 20 sccm의 일정하게 함과 동시에, 모노실란가스의 도입량(Ms)을 2 sccm의 일정하게 하고, 따라서 도입 유량비(Md/Ms)를 일정값 10으로 하고, 투입하는 고주파 전력밀도를 0.01 W/㎤의 일정하게 하고, 사용하는 안테나를 여러가지 바꾸어 플라즈마 포텐셜 및 전자밀도를 변화시킨 참고 실험예 22∼23, 실험예 24∼25 및 참고 실험예26∼27를 이하의 표 4에 정리하여 나타낸다.

또, 형성된 실리콘 박막의 결정화도(Ic/Ia)의 측정결과와 성막시의 플라즈마 포텐셜과의 관계를 도 5에, 결정화도(Ic/Ia)의 측정결과와 성막시의 전자밀도와의 관계를 도 6에 각각 나타낸다.

실험예 24, 25에서는 결정화도 8 이상으로 결정화한 실리콘 박막이 형성되었다.

그러나, 참고 실험예 26에서는, 평가 가능한 실리콘 박막이 기판 상에 퇴적되어 있지 않았다. 이것은 실질적으로 박막을 형성하는 것이 불가능한 정도로까지 플라즈마 밀도(전자밀도)가 저하하였기 때문이다.

참고 실험예 27에서는, 플라즈마가 점등하거나, 소멸하는 불안정한 상태가 되어, 실리콘 박막을 형성할 수 없었다. 이것은, 플라즈마 포텐셜이 지나치게 저하한 결과, 플라즈마 그 자체의 유지가 곤란하게 되었기 때문이다.

참고 실험예 22, 23에서는, 플라즈마로부터의 대미지에 의해 Ic/Ia가 현저하게 낮아졌다.

도 5에서 성막시의 플라즈마 포텐셜을 25 V 이하의 범위의 것으로 함으로써 Ic/Ia≥8를 달성할 수 있는 것을 알 수 있다. 또, 성막시의 플라즈마 포텐셜을 23 V 정도 이하의 범위의 것으로 하면, 더욱 바람직한 Ic/Ia≥10을 달성할 수 있는 것을 알 수 있다.

어쨌든, 전자밀도의 하한에 대해서는, 이미 설명한 바와 같이 1×1010개/㎤정도 이상이 바람직하다.

이상 설명한 실험예 중, Ic/Ia≥10을 달성한 실험예 3∼5, 9∼12, 17∼19, 24∼25의 각각에서 형성된 다결정 실리콘 박막에 대하여 종단 처리를 실시한 실험예 28, 29에 대하여 설명한다.

실험예 28, 29 중 어느 것에서도, 다결정 실리콘 박막이 형성된 기판(S)을 홀더(2)에 유지시키고, 고주파 전원(4)으로부터 매칭 박스(41)를 거쳐 안테나(3)로 고주파 전력을 인가하였다. 사용한 안테나종은, 실험예 3∼5, 9∼12, 17∼19, 24∼25에서의 다결정 실리콘 박막 형성에 있어서 각각 사용한 안테나종이다. 또, 종단 처리용 가스공급부(8)로서, 산소가스 또는 질소가스를 공급할 수 있는 것을 사용하였다.

실험예 28(산소 종단 처리된 다결정 실리콘 박막의 형성)

기판 온도 : 400℃

산소가스 도입량 : 100 sccm

고주파 전력 : 13.56 MHz 1 kW

종단 처리압 : 0.67 Pa

처리시간 : 1분

실험예 29(질소 종단 처리된 다결정 실리콘 박막의 형성)

기판 온도 : 400℃

질소가스 도입량 : 200 sccm

고주파 전력 : 13.56 MHz lkW

종단 처리압 : 0.67 Pa

처리시간 : 5분

이와 같이 산소 또는 질소로 종단 처리된 다결정 실리콘계 박막을 TFT용 반도체막으로서 사용하면, TFT 전기 특성으로서의 전자 이동도가, 종단 처리하지 않은 경우보다 한층 향상하고, 또, 0FF 전류가 저감하였다.

이상 설명한 종단 처리에서는 성막실(1)을 종단 처리실로서 이용하였으나, 종단 처리실을 따로 설치하고, 그곳에서 종단 처리를 실시하여도 된다. 예를 들면, 성막실(1)에서 다결정성 실리콘계 박막을 형성한 후, 상기 다결정성 실리콘계 박막이 형성된 기판(S)을 성막실(1)에(직접적으로 또는 물품 반송로봇을 가지는 반송실을 거치는 등으로 하여 간접적으로) 연달아 설치된 종단 처리실로 반입하고, 상기 종단 처리실에서 종단 처리를 실시하여도 된다.

이상, 다결정 실리콘 박막의 형성예에 대하여 설명하였으나, 본 발명은, 게르마늄을 함유하는 실리콘을 주성분으로 하는 다결정 실리콘계 박막이나, 탄소를 함유하는 실리콘을 주성분으로 하는 다결정 실리콘계 박막의 형성에도 적용할 수 있다.

이하에 그와 같은 박막형성의 실험예에 대하여 기재하여 둔다.

실험예 30(게르마늄을 함유하는 다결정 실리콘계 박막의 형성)

기판 : 무알칼리 유리 기판

기판 온도 : 400℃

성막 원료 가스 : SiH4(2 sccm) 및 GeH4(0.02 sccm)

희석가스 : 수소가스 20 sccm

가스 도입 유량비 H2/(SiH4 + GeH4) : 9.9

성막압 : 1.3 Pa

고주파 전력밀도 : 0.01 W/㎤

플라즈마 포텐셜 : 19 V

전자밀도 : 4.5×1010개/㎤

안테나종 : C

실험예 31(탄소를 함유하는 다결정 실리콘계 박막의 형성)

기판 : 무알칼리 유리 기판

기판 온도 : 400℃

성막 원료 가스 : SiH4(2 sccm) 및 CH4(0.02 sccm)

희석가스 : 수소가스 20 sccm

가스 도입 유량비 H2/(SiH4 + CH4) : 9.9

성막압 : 1.3 Pa

고주파 전력밀도 : 0.01 W/㎤

플라즈마 포텐셜 : 19 V

전자밀도 : 4.4×1010개/㎤

안테나종 : C

실험예 30에 의하면, 막 중의 게르마늄 함유량은 대략 1 atm%[1 원자%]이었다. 그리고 레이저 라만 산란 분광법에 의한 막 중 실리콘의 결정화도 평가에 있어서, 아몰퍼스 실리콘 성분에 기인하는 파수 480-1 cm 에서의 라만 산란강도(Ia)에 대한 결정화 실리콘 성분에 기인하는 파수 520-1cm 또는 그 부근에서의 라만 산란 피크강도(Ic)의 비(Ic/Ia)가 12.3인 다결정 실리콘계 박막을 확인할 수 있었다.

실험예 31에 의하면, 막 중의 탄소 함유량은 대략 1 atm%[1 원자%]이었다. 그리고 막 중 실리콘의 결정화도 평가에 있어서, 아몰퍼스 실리콘 성분에 기인하는 파수 480-1cm 에서의 라만 산란강도(Ia)에 대한 결정화 실리콘 성분에 기인하는 파수 520-1cm 또는 그 부근에서의 라만 산란 피크강도(Ic)의 비(Ic/Ia)가 12.4인 다결정 실리콘계 박막을 확인할 수 있었다.

또, 실험예 30, 31에서 형성된 막에 상기 실험예 28, 29와 동일한 조건으로 종단 처리를 실시하여, TFT용 반도체막으로서 사용하면, TFT 전기 특성으로서의 전자 이동도가, 종단 처리하지 않은 경우보다 한층 향상하고, 또한 0FF 전류가 저감하였다.

본 발명은, 피성막 기판 상에 TFT(박막 트랜지스터) 스위치의 재료로서, 또는 각종 집적회로, 태양전지 등의 제작에 반도체막으로서 이용할 수 있는 다결정 실리콘계 박막을 형성하는 것에 이용할 수 있다.

Claims (7)

- 실리콘원자를 함유하는 성막 원료 가스 및 희석가스 중 적어도 상기 성막 원료 가스를 성막실 내로 도입하고, 해당 도입 가스를 고주파 여기(勵起)로 플라즈마화하여, 해당 플라즈마 하에서 상기 성막실 내에 배치된 피성막 기판 상에 실리콘계 박막을 형성하는 플라즈마 CVD법에 의한 실리콘계 박막의 형성방법에 있어서,성막시의 성막실 내압을 0.0095 Pa∼64 Pa의 범위에서, 성막시에 상기 성막실 내로 도입하는 상기 성막 원료 가스의 도입 유량 Ms[sccm]에 대한 상기 희석가스의 도입 유량 Md[sccm]의 비(Md/Ms)를 0∼1200의 범위에서, 성막시의 고주파 전력밀도를 0.0024 W/㎤∼11 W/㎤의 범위에서 각각 선택 결정함과 동시에, 성막시의 플라즈마 포텐셜을 25 V 이하로, 성막시의 플라즈마 중의 전자밀도를 1×1010개/㎤이상으로 유지하여 막을 형성하고,또한, 상기 선택 결정되는 성막시의 성막실 내압, 성막 원료 가스와 희석가스의 도입 유량비(Md/Ms), 고주파 전력밀도, 상기 유지되어야 할 플라즈마 포텐셜 및 플라즈마 중의 전자밀도의 조합이 레이저 라만 산란 분광법에 의한 막 중 실리콘의 결정성 평가에 있어서 해당 막 중 아몰퍼스 실리콘 성분에 기인하는 라만산란 피크강도(Ia)에 대한 결정화 실리콘 성분에 기인하는 라만 산란 피크강도(Ic)의 비(Ic/Ia=결정화도)가 8 이상이 되는 다결정 실리콘계 박막이 얻어지는 조합으로 하여 막을 형성함으로써 다결정 실리콘계 박막을 형성하는 것을 특징으로 하는 플 라즈마 CVD법에 의한 실리콘계 박막의 형성방법.

- 제 1항에 있어서,상기 성막실 내로의 도입 가스의 고주파 여기에 의한 플라즈마화를 상기 성막실 내에 설치한 유도결합형 안테나로부터 상기 도입 가스로 고주파 전력을 인가 함으로써 행하는 것을 특징으로 하는 실리콘계 박막의 형성방법.

- 제 1항 또는 제 2항에 있어서,상기 아몰퍼스 실리콘 성분에 기인하는 라만 산란 피크강도(Ia)로서 파수480-1cm 에서의 라만 산란강도를 채용하고, 상기 결정화 실리콘 성분에 기인하는 라만 산란 피크강도(Ic)로서 파수 520-1 cm 또는 그 부근에서의 라만 산란 피크강도를 채용하는 것을 특징으로 하는 실리콘계 박막의 형성방법.

- 제 1항, 제 2항 또는 제 3항 중 어느 한 항에 있어서,상기 실리콘 원자를 함유하는 성막 원료 가스로서 게르마늄 원자도 함유하는 가스를 채용하고, 게르마늄을 함유하는 다결정 실리콘계 박막을 형성하는 것을 특징으로 하는 실리콘계 박막의 형성방법.

- 제 1항, 제 2항 또는 제 3항 중 어느 한 항에 있어서,상기 실리콘 원자를 함유하는 성막 원료 가스로서 탄소 원자도 함유하는 가스를 채용하고, 탄소를 함유하는 다결정 실리콘계 박막을 형성하는 것을 특징으로 하는 실리콘계 박막의 형성방법.

- 제 1항 내지 제 5항 중 어느 한 항에 있어서,상기 다결정 실리콘계 박막을 형성 후에, 산소함유 가스 및 질소함유 가스에서 선택된 적어도 1종의 종단 처리용 가스에 고주파 전력을 인가함으로써 발생시킨 종단 처리용 플라즈마 하에서 상기 다결정 실리콘계 박막의 표면을 종단 처리하는 것을 특징으로 하는 실리콘계 박막의 형성방법.

- 제 6항에 있어서,상기 성막실에서 상기 다결정 실리콘계 박막을 형성 후, 상기 다결정 실리콘계 박막이 형성된 상기 기판을 상기 성막실에 연달아 설치된 종단 처리실로 반입하고, 상기 종단 처리실에서 상기 종단 처리를 실시하는 것을 특징으로 하는 실리콘계 박막의 형성방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006303676A JP2008124111A (ja) | 2006-11-09 | 2006-11-09 | プラズマcvd法によるシリコン系薄膜の形成方法 |

| JPJP-P-2006-303676 | 2006-11-09 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20090066317A true KR20090066317A (ko) | 2009-06-23 |

Family

ID=39364377

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020097009525A KR20090066317A (ko) | 2006-11-09 | 2007-10-29 | 플라즈마 cvd법에 의한 실리콘계 박막의 형성방법 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20100210093A1 (ko) |

| JP (1) | JP2008124111A (ko) |

| KR (1) | KR20090066317A (ko) |

| CN (1) | CN101558473B (ko) |

| TW (1) | TW200932942A (ko) |

| WO (1) | WO2008056557A1 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190135472A (ko) * | 2017-04-27 | 2019-12-06 | 어플라이드 머티어리얼스, 인코포레이티드 | 3d 낸드 적용을 위한 낮은 유전율의 산화물 및 낮은 저항의 op 스택 |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008177419A (ja) * | 2007-01-19 | 2008-07-31 | Nissin Electric Co Ltd | シリコン薄膜形成方法 |

| US8709551B2 (en) * | 2010-03-25 | 2014-04-29 | Novellus Systems, Inc. | Smooth silicon-containing films |

| US9028924B2 (en) | 2010-03-25 | 2015-05-12 | Novellus Systems, Inc. | In-situ deposition of film stacks |

| US8741394B2 (en) | 2010-03-25 | 2014-06-03 | Novellus Systems, Inc. | In-situ deposition of film stacks |

| US9165788B2 (en) | 2012-04-06 | 2015-10-20 | Novellus Systems, Inc. | Post-deposition soft annealing |

| US9117668B2 (en) | 2012-05-23 | 2015-08-25 | Novellus Systems, Inc. | PECVD deposition of smooth silicon films |

| US9388491B2 (en) | 2012-07-23 | 2016-07-12 | Novellus Systems, Inc. | Method for deposition of conformal films with catalysis assisted low temperature CVD |

| US8895415B1 (en) | 2013-05-31 | 2014-11-25 | Novellus Systems, Inc. | Tensile stressed doped amorphous silicon |

| JP2017092142A (ja) * | 2015-11-05 | 2017-05-25 | 東京エレクトロン株式会社 | 被処理体を処理する方法 |

| US20170294289A1 (en) * | 2016-04-11 | 2017-10-12 | Aaron Reinicker | Boron compositions suitable for ion implantation to produce a boron-containing ion beam current |

| JP7028001B2 (ja) * | 2018-03-20 | 2022-03-02 | 日新電機株式会社 | 成膜方法 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0552375B1 (en) * | 1991-07-16 | 2004-06-02 | Seiko Epson Corporation | Method of forming a semiconductor film with a chemical vapor deposition apparatus |

| JPH1027762A (ja) * | 1996-03-18 | 1998-01-27 | Hyundai Electron Ind Co Ltd | 誘導結合形プラズマcvd方法及びこれを用いて生成された非晶質シリコン薄膜,及び、窒化シリコン膜,非晶質薄膜トランジスタ |

| JP3680677B2 (ja) * | 2000-02-08 | 2005-08-10 | セイコーエプソン株式会社 | 半導体素子製造装置および半導体素子の製造方法 |

| JP2001316818A (ja) * | 2000-02-29 | 2001-11-16 | Canon Inc | 膜形成方法及び形成装置、並びにシリコン系膜、起電力素子及びそれを用いた太陽電池、センサー及び撮像素子 |

| JP2003068643A (ja) * | 2001-08-23 | 2003-03-07 | Japan Advanced Inst Of Science & Technology Hokuriku | 結晶性シリコン膜の作製方法及び太陽電池 |

| JP3894862B2 (ja) * | 2002-05-29 | 2007-03-22 | 京セラ株式会社 | Cat−PECVD法 |

| US7186663B2 (en) * | 2004-03-15 | 2007-03-06 | Sharp Laboratories Of America, Inc. | High density plasma process for silicon thin films |

| JP4474596B2 (ja) * | 2003-08-29 | 2010-06-09 | キヤノンアネルバ株式会社 | シリコンナノ結晶構造体の形成方法及び形成装置 |

| JP4434115B2 (ja) * | 2005-09-26 | 2010-03-17 | 日新電機株式会社 | 結晶性シリコン薄膜の形成方法及び装置 |

| JP2007123008A (ja) * | 2005-10-27 | 2007-05-17 | Nissin Electric Co Ltd | プラズマ生成方法及び装置並びにプラズマ処理装置 |

| JP5162108B2 (ja) * | 2005-10-28 | 2013-03-13 | 日新電機株式会社 | プラズマ生成方法及び装置並びにプラズマ処理装置 |

| JP2008177419A (ja) * | 2007-01-19 | 2008-07-31 | Nissin Electric Co Ltd | シリコン薄膜形成方法 |

-

2006

- 2006-11-09 JP JP2006303676A patent/JP2008124111A/ja active Pending

-

2007

- 2007-10-29 CN CN2007800416922A patent/CN101558473B/zh not_active Expired - Fee Related

- 2007-10-29 US US12/513,362 patent/US20100210093A1/en not_active Abandoned

- 2007-10-29 KR KR1020097009525A patent/KR20090066317A/ko not_active Application Discontinuation

- 2007-10-29 WO PCT/JP2007/070994 patent/WO2008056557A1/ja active Application Filing

-

2008

- 2008-01-31 TW TW097103750A patent/TW200932942A/zh unknown

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20190135472A (ko) * | 2017-04-27 | 2019-12-06 | 어플라이드 머티어리얼스, 인코포레이티드 | 3d 낸드 적용을 위한 낮은 유전율의 산화물 및 낮은 저항의 op 스택 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100210093A1 (en) | 2010-08-19 |

| CN101558473A (zh) | 2009-10-14 |

| CN101558473B (zh) | 2012-02-29 |

| WO2008056557A1 (fr) | 2008-05-15 |

| JP2008124111A (ja) | 2008-05-29 |

| TW200932942A (en) | 2009-08-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20090066317A (ko) | 플라즈마 cvd법에 의한 실리콘계 박막의 형성방법 | |

| US7763153B2 (en) | Method and apparatus for forming a crystalline silicon thin film | |

| EP1043762B1 (en) | Polycrystalline silicon thin film forming method and thin film forming apparatus | |

| US6720037B2 (en) | Plasma processing method and apparatus | |

| JP4497068B2 (ja) | シリコンドット形成方法及びシリコンドット形成装置 | |

| JP4258549B2 (ja) | 結晶性シリコン薄膜の形成方法及び装置 | |

| US20100062585A1 (en) | Method for forming silicon thin film | |

| JP3807127B2 (ja) | シリコン系薄膜の形成方法 | |

| WO2013018292A1 (ja) | 成膜方法 | |

| JPH11150283A (ja) | 多結晶シリコン薄膜の製造方法 | |

| JP4133490B2 (ja) | 成膜方法 | |

| JP2010225792A (ja) | 成膜装置及び成膜方法 | |

| Kirimura et al. | Low-temperature microcrystalline silicon film deposited by high-density and low-potential plasma technique using hydrogen radicals | |

| Miyajima et al. | Effect of plasma power on structure of hydrogenated nanocrystalline cubic silicon carbide films deposited by very high frequency plasma-enhanced chemical vapor deposition at a low substrate temperature | |

| JP2011021256A (ja) | ナノ結晶シリコン薄膜の成膜方法及びナノ結晶シリコン薄膜、並びに該薄膜を成膜する成膜装置 | |

| JPH11150284A (ja) | 多結晶シリコン薄膜の製造方法 | |

| Jou et al. | The characteristics of EPI-Si thin film in electron cyclotron resonance plasma examined by an integrated plasma diagnostic sub-system | |

| JP2008182267A (ja) | 基板の製造方法および基板処理装置 | |

| Westendorp et al. | High Deposition Rate Pecvd Processes For Next Generation Tft-Lcds | |

| Hu et al. | CVD Characteristics and mechanism of a-Si: H thin films in electron cyclotron resonance H2-Ar-SiH4 plasma |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |