KR101101552B1 - 세라믹 기판의 리페어 방법 및 이를 이용하여 리페어된 세라믹기판 - Google Patents

세라믹 기판의 리페어 방법 및 이를 이용하여 리페어된 세라믹기판 Download PDFInfo

- Publication number

- KR101101552B1 KR101101552B1 KR1020090085932A KR20090085932A KR101101552B1 KR 101101552 B1 KR101101552 B1 KR 101101552B1 KR 1020090085932 A KR1020090085932 A KR 1020090085932A KR 20090085932 A KR20090085932 A KR 20090085932A KR 101101552 B1 KR101101552 B1 KR 101101552B1

- Authority

- KR

- South Korea

- Prior art keywords

- wiring

- repair

- ceramic substrate

- main wiring

- pattern

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/225—Correcting or repairing of printed circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/0306—Inorganic insulating substrates, e.g. ceramic, glass

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical & Material Sciences (AREA)

- Ceramic Engineering (AREA)

- Inorganic Chemistry (AREA)

- Manufacturing & Machinery (AREA)

- Manufacturing Of Printed Wiring (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

Abstract

Description

Claims (17)

- 적어도 하나의 메인 배선 및 상기 메인 배선 중 손상된 메인 배선을 리페어하는 적어도 하나의 리페어 배선을 구비한 세라믹층을 마련하는 단계;상기 세라믹층에 상기 메인 배선과 상기 리페어 배선이 각각 전기적 접속 가능하도록 제1 도전 패턴을 형성하는 단계;상기 메인 배선의 손상 발생시, 상기 제1 도전 패턴을 제거하는 단계;상기 도전 패턴이 제거된 상기 손상된 메인 배선 상에 절연 부재를 형성하는 단계;상기 세라믹층에 상기 손상된 메인 배선 상에 형성된 절연 부재와 상기 리페어 배선을 연결하도록 리페어 패턴을 형성하는 단계; 및상기 리페어 패턴이 형성된 부분을 제외한 상기 메인 배선 및 상기 리페어 배선 상에 제2 도전 패턴을 형성하는 단계를 포함하며, 상기 제1 도전 패턴을 제거하는 단계는 상기 제1 도전 패턴을 연마하여 상기 손상된 메인 배선을 노출시키는 단계; 및 상기 노출된 메인 배선의 일부 영역을 제거하여 홈부를 형성하는 단계를 포함하는 세라믹 기판의 리페어 방법.

- 제1항에 있어서,전기적 불량 발생시, 상기 손상된 메인 배선에 전달되는 전기적 신호는 상기 리페어 패턴을 통하여 상기 리페어 배선에 전달되도록 리페어되는 것을 특징으로 하는 세라믹 기판의 리페어 방법.

- 삭제

- 제1항에 있어서,상기 홈부는 레이저 식각, 화학적 식각, 펀칭 또는 레이저 드릴링 중 적어도 하나의 방법에 의해 형성되는 것을 특징으로 하는 세라믹 기판의 리페어 방법.

- 제1항에 있어서,상기 절연 부재는 유전체로 구성된 페이스트로 형성되는 것을 특징으로 하는 세라믹 기판의 리페어 방법.

- 제1항에 있어서,상기 제1 및 제2 도전 패턴 및 상기 리페어 패턴은 스크린 프린팅, 포토 리소그래피, 증착, 도금 또는 화학적 식각 중 적어도 하나의 방법에 의해 형성되는 것을 특징으로 하는 세라믹 기판의 리페어 방법.

- 제1항에 있어서,상기 제1 및 제2 도전 패턴 및 상기 리페어 패턴은 은과 상기 은을 도금하는 금, 구리, 구리 합금, 금, 금 합금, 텅스텐 및 텅스텐 합금 중 적어도 어느 하나의 재질로 형성되는 것을 특징으로 하는 세라믹 기판의 리페어 방법.

- 제1항에 있어서,상기 세라믹 기판의 내부 또는 외부에 접지용 배선을 형성하는 단계를 더 포함하는 것을 특징으로 하는 세라믹 기판의 리페어 방법.

- 제8항에 있어서,상기 리페어 배선과 상기 접지용 배선을 연결하는 단계를 더 포함하는 것을 특징으로 하는 세라믹 기판의 리페어 방법.

- 제1항에 있어서,상기 세라믹 기판의 내부 또는 외부에 테스트용 배선을 형성하는 단계를 더 포함하는 것을 특징으로 하는 세라믹 기판의 리페어 방법.

- 제10항에 있어서,전기적 테스트시, 상기 리페어 배선은 상기 테스트용 배선에 연결되는 것을 특징으로 하는 세라믹 기판의 리페어 방법.

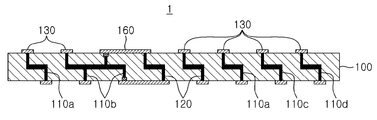

- 적어도 하나의 메인 배선을 구비한 세라믹층;상기 메인 배선과 전기적 접속이 가능하도록 상기 세라믹층에 형성된 도전 패턴;상기 세라믹층에 형성되며, 상기 메인 배선 중 손상된 메인 배선을 리페어하는 적어도 하나의 리페어 배선;상기 손상된 메인 배선의 일부 영역을 제거하여 형성된 홈부에 형성되며, 상기 손상된 메인 배선과 상기 도전 패턴을 절연하는 절연 부재; 및상기 세라믹층에 형성되며, 상기 손상된 메인 배선 상에 형성된 절연 부재와 상기 리페어 배선을 연결하는 리페어 패턴을 포함하는 세라믹 기판.

- 제12항에 있어서,전기적 불량 발생시, 상기 손상된 메인 배선에 전달되는 전기적 신호는 상기 리페어 패턴을 통하여 상기 리페어 배선에 전달되도록 리페어되는 것을 특징으로 하는 세라믹 기판.

- 제12항에 있어서,상기 절연 부재는 유전체로 구성된 페이스트로 이루어지는 것을 특징으로 하는 세라믹 기판.

- 제12항에 있어서,상기 도전 패턴 및 상기 리페어 패턴은 은과 상기 은을 도금하는 금, 구리, 구리 합금, 금, 금 합금, 텅스텐 및 텅스텐 합금 중 적어도 어느 하나의 재질로 이루어지는 것을 특징으로 하는 세라믹 기판.

- 제12항에 있어서,상기 세라믹 기판의 내부 또는 외부에 접지용 배선을 더 포함하는 것을 특징으로 하는 세라믹 기판.

- 제12항에 있어서,상기 세라믹 기판의 내부 또는 외부에 테스트용 배선을 더 포함하는 것을 특징으로 하는 세라믹 기판.

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020090085932A KR101101552B1 (ko) | 2009-09-11 | 2009-09-11 | 세라믹 기판의 리페어 방법 및 이를 이용하여 리페어된 세라믹기판 |

| JP2009286539A JP2011061178A (ja) | 2009-09-11 | 2009-12-17 | セラミック基板のリペア方法及びこれを用いてリペアされたセラミック基板 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020090085932A KR101101552B1 (ko) | 2009-09-11 | 2009-09-11 | 세라믹 기판의 리페어 방법 및 이를 이용하여 리페어된 세라믹기판 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20110028031A KR20110028031A (ko) | 2011-03-17 |

| KR101101552B1 true KR101101552B1 (ko) | 2012-01-02 |

Family

ID=43934546

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020090085932A Expired - Fee Related KR101101552B1 (ko) | 2009-09-11 | 2009-09-11 | 세라믹 기판의 리페어 방법 및 이를 이용하여 리페어된 세라믹기판 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2011061178A (ko) |

| KR (1) | KR101101552B1 (ko) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8692136B2 (en) | 2010-07-13 | 2014-04-08 | Samsung Electro-Mechanics Co., Ltd. | Method of repairing probe card and probe board using the same |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4974048A (en) | 1989-03-10 | 1990-11-27 | The Boeing Company | Integrated circuit having reroutable conductive paths |

| JPH02307254A (ja) * | 1989-05-23 | 1990-12-20 | Fujitsu Ltd | ウエハー上の半導体チップ配線接続方式 |

| KR100683444B1 (ko) * | 2005-12-29 | 2007-02-22 | 주식회사 파이컴 | 프로브 카드의 기판 및 그 기판의 재생 방법 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007335434A (ja) * | 2006-06-12 | 2007-12-27 | Nec Corp | フレキシブル配線基板、回路基板およびフレキシブル配線断線時の修復方法 |

-

2009

- 2009-09-11 KR KR1020090085932A patent/KR101101552B1/ko not_active Expired - Fee Related

- 2009-12-17 JP JP2009286539A patent/JP2011061178A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4974048A (en) | 1989-03-10 | 1990-11-27 | The Boeing Company | Integrated circuit having reroutable conductive paths |

| JPH02307254A (ja) * | 1989-05-23 | 1990-12-20 | Fujitsu Ltd | ウエハー上の半導体チップ配線接続方式 |

| KR100683444B1 (ko) * | 2005-12-29 | 2007-02-22 | 주식회사 파이컴 | 프로브 카드의 기판 및 그 기판의 재생 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011061178A (ja) | 2011-03-24 |

| KR20110028031A (ko) | 2011-03-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101121644B1 (ko) | 프로브 카드용 공간 변환기 및 공간 변환기의 복구 방법 | |

| US6462570B1 (en) | Breakout board using blind vias to eliminate stubs | |

| CN102196662B (zh) | 用于高速总线的测试点设计 | |

| US8692136B2 (en) | Method of repairing probe card and probe board using the same | |

| JP2004226397A (ja) | プリント基板の接触器,プリント基板,および,プリント基板の製造方法 | |

| US12019111B2 (en) | Manufacturing method of a multi-layer for a probe card | |

| CN102365001A (zh) | 一种在同一块板上多种表面处理的制造方法 | |

| US11570908B2 (en) | Designing a printed circuit board (PCB) to detect slivers of conductive material included within vias of the PCB | |

| KR101572089B1 (ko) | 인쇄회로기판 검사방법 | |

| CN103813634A (zh) | 具有埋入式连接杆的电路板及其制造方法 | |

| KR101101552B1 (ko) | 세라믹 기판의 리페어 방법 및 이를 이용하여 리페어된 세라믹기판 | |

| TW201916757A (zh) | 多層線路結構及其製作方法 | |

| JP2013134249A (ja) | プローブカード及びその製造方法 | |

| JP5774332B2 (ja) | プローブカード用セラミック基板及びその製造方法 | |

| JP6199010B2 (ja) | プローブカード | |

| CN109673099B (zh) | 多层线路结构及其制作方法 | |

| JP2012141274A (ja) | プローブカード用セラミック基板及びその製造方法 | |

| KR100979500B1 (ko) | 프로브카드용 기판 | |

| JP5776230B2 (ja) | フリップチップパッケージ用基板の電気検査方法 | |

| KR20100099858A (ko) | 인쇄회로기판의 리페어 방법 | |

| JP2006275579A (ja) | 検査基板および検査装置 | |

| CN101969057B (zh) | 线路基板 | |

| KR101022869B1 (ko) | 이미지센서 모듈용 인쇄회로기판의 제조방법 | |

| JP4544236B2 (ja) | Tabテープ | |

| CN121172016A (zh) | 封装结构、电路板以及封装结构的制作方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| D13-X000 | Search requested |

St.27 status event code: A-1-2-D10-D13-srh-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| D14-X000 | Search report completed |

St.27 status event code: A-1-2-D10-D14-srh-X000 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 20141227 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 20141227 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |