KR100245179B1 - 반도체 기억 장치 - Google Patents

반도체 기억 장치 Download PDFInfo

- Publication number

- KR100245179B1 KR100245179B1 KR1019970010206A KR19970010206A KR100245179B1 KR 100245179 B1 KR100245179 B1 KR 100245179B1 KR 1019970010206 A KR1019970010206 A KR 1019970010206A KR 19970010206 A KR19970010206 A KR 19970010206A KR 100245179 B1 KR100245179 B1 KR 100245179B1

- Authority

- KR

- South Korea

- Prior art keywords

- potential

- transistor

- word

- word driver

- memory device

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/12—Group selection circuits, e.g. for memory block selection, chip selection, array selection

Abstract

본 발명은 반도체 기억 장치에 있어서 워드 선택선을 구동하는 워드 드라이버의 밴드간 터널 전류를 삭감함으로써, 대기시 등의 소비 전류를 삭감하는 것을 목적으로 한다.

반도체 기억 장치는 메모리 셀에 대하여 워드선을 선택 활성화하는 워드 드라이버와, 상기 워드 드라이버의 트랜지스터의 게이트 전압을 제어함으로써 상기 트랜지스터의 밴드간 터널 전류를 억제하는 제어부를 포함하는 것을 특징으로 한다.

Description

본 발명은 일반적으로 반도체 기억 장치에 관한 것으로, 상세하게는 대기시 등의 소비 전류를 삭감하는 반도체 기억 장치에 관한 것이다.

DRAM, SRAM, 플래시 메모리, EPROM 등의 반도체 기억 장치에 있어서, 트랜지스터의 사이즈를 작게하여 집적도를 향상시키기 위해서는 트랜지스터에 주입하는 불순물 농도를 높여 줄 필요가 있다. 이와 같이 불순물 농도를 높게 하면 트랜지스터의 공핍층(空乏層)의 폭이 작아지고, 공핍층에 걸리는 전계가 커진다. 이 결과 특히 PMOS 트랜지스터에 있어서는, 고전압을 게이트에 인가하여 트랜지스터를 오프로 하여도, 공핍층 위치에서 밴드가 심하게 구부러짐으로써 금제대 간격이 좁아지며, 밴드간 터널 전류가 흐르게 된다.

도 9 는 밴드간 터널 전류가 흐르는 것에 의한 영향을 설명하기 위한 도면이다. 도 9 는 반도체 기억 장치의 워드 선택선을 구동하는 워드 드라이버 등에 있어서 이용되는 인버터 회로를 나타내고, 이 인버터 회로는 PMOS 트랜지스터(201) 및 NMOS 트랜지스터(202)를 포함한다. 반도체 기억 장치의 워드 드라이버 등에 있어서는, 예컨대 반도체 기억 장치가 데이타 입출력을 기다리는 대기 상태에 있는 경우, PMOS 트랜지스터(201)의 게이트 G1 및 NMOS 트랜지스터(202)의 게이트 G2 에 고전위(VDD)를 인가한다. 이것에 의해서 PMOS 트랜지스터(201)를 오프로 하여 NMOS 트랜지스터(202)를 온으로 하고, 인버터 회로의 출력을 저전위로 해 둔다.

그러나 상술한 바와같이, 반도체 기억 장치의 집적도 향상에 의해 공핍층에 걸리는 전계가 커지면, 도 9 의 PMOS 트랜지스터(201)에 밴드간 터널 전류 IBT가 흐르게 된다. 이 밴드간 터널 전류 IBT는 PMOS 트랜지스터(201)의 벌크 B 에서 드레인 D 에 흐르는 전류이고, 그 전류량이 작은 경우에는 회로의 동작 자체에는 영향을 미치게 하지 않는다.

반도체 기억 장치에 있어서는, 도 9 와 같은 인버터 회로가 여러가지 부위에서 이용된다. 특히 상술한 바와 같이, 워드 선택선을 구동하는 워드 드라이버 부분에 있어서는, 도 9 의 인버터 회로가 고전압이 인가되는 각 워드선에 대하여 설치되기 때문에, 인버터 1 개당의 밴드간 터널 전류가 큰데다가 그 수는 방대한 것이 된다. 따라서, 반도체 기억 장치가 대기 상태에 있는 경우에, 워드 드라이버의 인버터 회로 전체에 흐르는 밴드간 터널 전류 IBT는 총계하면 무시할 수 없는 것으로 된다.

또한 반도체 기억 장치가 예컨대 데이타 독출 상태에 있는 경우에도, 비선택 메모리 블록에 있어서의 워드 드라이버의 인버터 회로는 저전위 출력 상태로 되어 있다. 따라서, 이들 인버터 회로에 흐르는 밴드간 터널 전류 IBT는 총계하면 무시할 수 없는 값이 된다.

이 밴드간 터널 전류에 의한 소비 전력은 특히 휴대용 기기에 반도체 기억 장치를 장비하였을 때에, 배터리의 소비를 빠르게 하여 바람직스럽지 않다. 휴대용기기에 있어서는, 한정된 배터리 전력을 효율적으로 사용하기 위해서 저소비 전력의 반도체 기억 장치가 필요로 된다.

따라서, 반도체 기억 장치의 밴드간 터널 전류를 삭감함으로써, 대기 상태 등에 있어서의 소비 전류 삭감을 도모할 필요가 있다. 밴드간 터널 전류는 일반적으로, 소스 혹은 드레인과 벌크 사이에 고전압이 인가된 상태로, 오프 상태의 트랜지스터에 있어서 현저한 것이 알려져 있다. 따라서, 소스 혹은 드레인과 벌크 사이의 전압을 낮춤으로써, 밴드간 터널 전류를 억압할 수 있다. 또한 트랜지스터가 온하는 방향으로 게이트 전압을 변화시키면, 밴드간 터널 전류를 억압할 수 있다.

본 발명은 반도체 기억 장치에 있어서, 워드 선택선을 구동하는 워드 드라이버에 있어서의 밴드간 터널 전류를 삭감함으로써, 대기시 등의 소비 전류를 삭감하는 것을 목적으로 한다.

도 1 은 본 발명에 의한 DRAM의 개략 전체 구조를 나타내는 도면.

도 2 는 도 1 의 DRAM 의 X 디코더 및 메모리 코어를 상세하게 나타내는 도면.

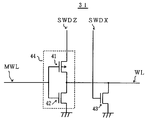

도 3 의 (A)는 도 2 의 메모리 코어 내부의 워드선 배치를 상세하게 나타내는 도면이고, (B)는 (A)의 서브 워드 디코드부를 나타내는 도면.

도 4 는 서브 워드 디코더의 구성을 나타내는 회로도.

도 5 는 메인 워드 디코더와 메인 워드 디코더 구동 회로의 제 1 실시예를 나타내는 회로도.

도 6 의 (A)는 대기시 혹은 비선택 블록에 있어서의 본 발명의 DRAM 의 동작을 설명하는 도면이고, (B)는 선택 블록에 있어서의 본 발명의 DRAM 의 동작을 설명하는 도면.

도 7 은 본 발명의 DRAM 의 동작을 설명하기 위한 타이밍도.

도 8 은 메인 워드 디코더 구동 회로의 제 2 실시예를 나타내는 회로도.

도 9 는 밴드간 터널 전류를 설명하기 위한 도면.

* 도면의 주요부분에 대한 부호의 설명

10 : DRAM

11 : 메모리 코어

12 : Y 디코더

13 : X 디코더

14 : 어드레스 버퍼

15 : 제어 버퍼

16 : 데이타 버퍼

20 : 센스 앰프열

21 : 메인 워드 디코더

22 : 메인 워드 디코더 구동 회로

23 : 메모리 블록

30 : 서브 워드 디코드부

31,32 : 서브 워드 디코더

44 : 워드 드라이버

청구범위 제 1 항의 발명에 있어서는, 반도체 기억 장치는 메모리 셀에 대하여 워드선을 선택 활성화하는 워드 드라이버와, 상기 워드 드라이버의 트랜지스터의 게이트 전압을 제어함으로써 상기 트랜지스터의 밴드간 터널 전류를 억제하는 제어부를 포함하는 것을 특징으로 한다.

상기 발명에 있어서는, 워드 드라이버의 트랜지스터의 게이트 전위를 제어하는 제어부를 설치함으로써, 그 트랜지스터의 밴드간 터널 전류를 억제할 수 있다.

청구범위 제 2 항의 발명에 있어서는, 제 1 항 기재의 반도체 기억 장치에 있어서, 상기 제어부는 상기 워드 드라이버를 분할하는 복수의 그룹의 각각을 독립적으로 제어하는 것을 특징으로 한다.

상기 발명에 있어서는, 제어부는 워드 드라이버의 복수의 그룹의 각각에 대하여 독립적으로 제어할 수 있기 때문에, 각 그룹마다 적절한 제어를 행할 수 있다.

청구범위 제 3 항의 발명에 있어서는, 제 2 항 기재의 반도체 기억 장치에 있어서, 상기 복수의 그룹에 대응하는 상기 메모리 셀로 이루어지는 복수의 메모리 블록을 추가로 포함하며, 상기 제어부는 상기 복수의 메모리 블록의 각각을 독립적으로 제어하는 것을 특징으로 한다.

상기 발명에 있어서는, 제어부는 메모리 블록의 각각에 대하여 독립으로 제어할 수 있기 때문에, 메모리 블록마다 밴드간 터널 전류를 적절히 제어할 수 있다.

청구범위 제 4 항의 발명에 있어서는, 제 1 항 기재의 반도체 기억 장치에 있어서, 상기 제어부는 상기 반도체 장치가 대기중에 상기 밴드간 터널 전류를 억제하는 것을 특징으로 한다.

상기 발명에 있어서는, 반도체 장치가 대기중에 밴드간 터널 전류를 제어함으로써, 대기시의 쓸데없는 전력 소비를 삭감할 수 있다.

청구범위 제 5 항의 발명에 있어서는, 제 2 항 기재의 반도체 기억 장치에 있어서, 상기 제어부는 상기 메모리 블록으로부터 데이타 입출력를 위해 선택된 메모리 블록에 대한 제어와, 상기 선택된 메모리 블록 이외의 메모리 블록에 대한 제어를 다르게 하며, 상기 선택된 메모리 블록 이외의 메모리 블록에 대하여 상기 밴드간 터널 전류를 억제하는 것을 특징으로 한다.

상기 발명에 있어서는, 반도체 기억 장치가 데이타 입출력 동작중이더라도, 비선택의 메모리 블록에 있어서 밴드간 터널 전류를 억제함으로써, 쓸데없는 전력 소비를 삭감할 수 있다.

청구범위 제 6 항의 발명에 있어서는, 제 1 항 기재의 반도체 기억 장치에 있어서, 상기 워드 드라이버는 상기 워드선을 활성화하는 전위와 같은 제 1 전위와, 상기 제 1 전위보다 낮은 제 2 전위와, 접지 전위인 제 3 전위중 어느 하나를 상기 게이트의 전위로서 수신하며, 상기 제어 회로는 상기 제 1 전위를 대신해서 상기 제 2 전위를 상기 워드 드라이버에 공급함으로써 상기 밴드간 터널 전류를 억제하는 것을 특징으로 한다.

상기 발명에 있어서는, 워드선을 활성화하는 전위와 같은 전위가 아니라, 그것보다도 낮은 전위를 워드 드라이버의 트랜지스터에 게이트 전압으로서 공급함으로써, 밴드간 터널 전류를 억압할 수 있다.

청구범위 제 7 항의 발명에 있어서는, 제 6 항 기재의 반도체 기억 장치에 있어서, 상기 워드 드라이버는 상기 제 1 전위와 상기 제 3 전위중 하나를 전원 전압으로 하는 것을 특징으로 한다.

상기 발명에 있어서는, 선택된 워드 드라이버는 워드선을 활성화하는 전위와 같은 전위를 전원 전압으로서 수신함으로써, 워드선에 그 전위를 공급할 수 있다.

청구범위 제 8 항의 발명에 있어서는, 제 4 항 또는 제 5 항 기재의 반도체 기억 장치에 있어서, 상기 워드 드라이버는 상기 워드선을 활성화하는 전위와 같은 제 1 전위와, 상기 제 1 전위보다 낮은 제 2 전위와, 접지 전위인 제 3 전위중 어느 하나를 상기 게이트의 전위로서 수신하며, 상기 제어 회로는 상기 제 1 전위를 대신해서 상기 제 2 전위를 상기 워드 드라이버에 공급함으로써 상기 밴드간 터널 전류를 억제하는 것을 특징으로 한다.

상기 발명에 있어서는, 워드선을 활성화하는 전위와 같은 전위가 아니라, 그것보다도 낮은 전위를 워드 드라이버의 트랜지스터에 게이트 전압으로서 공급함으로써, 밴드간 터널 전류를 억압할 수 있다.

청구범위 제 9 항의 발명에 있어서는, 제 8 항 기재의 반도체 기억 장치에 있어서, 상기 제어 회로는 상기 선택된 메모리 블록의 선택된 상기 워드 드라이버에는 상기 제 3 전위를 공급하고, 상기 선택된 메모리 블록의 비선택의 상기 워드 드라이버에는 상기 제 1 전위를 공급하며, 상기 선택된 메모리 블록 이외의 상기 메모리 블록에 대응하는 상기 워드 드라이버에는 상기 제 2 전위를 공급하는 것을 특징으로 한다.

상기 발명에 있어서는, 비선택의 메모리 블록에 있어서 워드선을 활성화하는 전위보다도 낮은 전위를 워드 드라이버에 공급함으로써, 비선택의 메모리 블록에 있어서의 밴드간 터널 전류를 억압하여 소비 전류의 삭감을 도모할 수 있다.

청구범위 제 10 항의 발명에 있어서는, 제 8 항 기재의 반도체 기억 장치에 있어서, 상기 제어 회로는, 상기 반도체 장치가 대기중에 상기 제 2 전위를 상기 워드 드라이버에 공급함으로써 상기 밴드간 터널 전류를 억제하는 것을 특징으로 한다.

상기 발명에 있어서는, 반도체 장치가 대기중에 워드선을 활성화하는 전위보다도 낮은 전위를 워드 드라이버에 공급함으로써, 밴드간 터널 전류를 억압하여 대기시의 쓸데없는 전력 소비를 삭감할 수 있다.

청구범위 제 11 항의 발명에 있어서는, 제 6 항 기재의 반도체 기억 장치에 있어서, 상기 제어 회로는 상기 제 1 전위를 전원 전압으로 하는 제 1 트랜지스터와, 상기 제 2 전위를 전원 전압으로 하는 제 2 트랜지스터를 포함하며, 상기 제 1 트랜지스터의 게이트 및 상기 제 2 트랜지스터의 게이트에 상보 신호를 입력함으로써 상기 제 1 전위와 상기 제 2 전위중 하나를 선택하는 것을 특징으로 한다.

청구범위 제 12 항의 발명에 있어서는, 제 11 항 기재의 반도체 기억 장치에 있어서, 상기 제어 회로는 상기 상보 신호를 상기 제 1 트랜지스터 및 상기 제 2 트랜지스터의 동작 전압 레벨에 맞추기 위한 레벨 시프터 회로를 추가로 포함하는 것을 특징으로 한다.

청구범위 제 13 항의 발명에 있어서는, 제 6 항 기재의 반도체 기억 장치에 있어서, 상기 제어 회로는 상기 제 1 전위 및 상기 제 2 전위 사이에서 직렬 접속된 P 형 트랜지스터 및 N 형 트랜지스터를 포함하며, 상기 P 형 트랜지스터의 게이트 및 상기 N 형 트랜지스터의 게이트에 공통으로 입력하는 신호에 의해서 상기 제 1 전위와 상기 제 2 전위중 하나를 선택하는 것을 특징으로 한다.

청구범위 제 14 항의 발명에 있어서는, 제 13 항 기재의 반도체 기억 장치에 있어서, 상기 제어 회로는 상기 신호를 상기 P 형 트랜지스터 및 상기 N 형 트랜지스터의 동작 전압 레벨에 맞추기 위한 레벨 시프터 회로를 추가로 포함하는 것을 특징으로 한다.

상기 청구범위 제 11 항 내지 제 14 항의 발명에 있어서는, 워드 드라이버에 공급하는 전위를 제어부에서 용이하게 전환하여 제어할 수 있으므로, 밴드간 터널 전류 억압을 용이하게 행할 수 있다.

이하에 본 발명의 실시예를 첨부의 도면을 이용하여 설명한다.

도 1 은 본 발명을 적용하는 DRAM 의 전체 구성을 개략적으로 나타내는 도면이다. 본 발명의 실시예는 DRAM 을 예로서 설명하였지만, 플래시 메모리 혹은 EPROM 등 각종의 반도체 기억 장치에 적용할 수 있다.

도 1 의 DRAM(10)은 메모리 코어(11), Y 디코더(열 디코더)(12), X 디코더(행 디코더)(13), 어드레스 버퍼(14), 제어 버퍼(15) 및 데이타 버퍼(16)를 포함한다. 메모리 코어(11)는 1 비트의 정보를 기억하는 메모리 셀의 배열 및 워드 선택선이나 열 선택선 등으로 이루어진다.

어드레스 버퍼(14)에 공급된 어드레스 신호는 X 디코더(13) 및 Y 디코더(12)에 공급되어 디코드된다. 어드레스 신호의 디코드 결과에 따라서, Y 디코더(12)는 열 선택선을 선택 활성화하고, X 디코더(13)는 워드 선택선을 선택 활성화한다. 데이타 독출의 경우에는 활성화된 열 및 워드에 대응하는 메모리 셀의 정보가 메모리 코어(11)로부터 독출되고, 데이타 버퍼(16)를 통해 외부로 데이타 신호로서 공급된다. 또한 데이타 기록의 경우에는 외부로부터 공급된 데이타 신호가 데이타 버퍼(16)를 통해 메모리 코어(11)에 공급되며, 활성화된 열 및 워드에 대응하는 메모리 셀에 데이타가 기록된다.

제어 버퍼(15)는 외부로부터 공급되는 제어 신호에 기초하여, 어드레스 버퍼(14) 및 데이타 버퍼(16)를 제어한다. 제어 신호로서는 어드레스 신호 입력을 나타내는 RAS(Row Address Strobe)나 CAS(Col1umn Address Strobe)등이 있다.

도 2 는 본 발명을 적용하는 도 1 의 DRAM(10)에 있어서의 X 디코더(13)의 관련 부분을 나타낸다. 도 2 에 나타낸 바와같이 X 디코더(13)는 복수의 메인 워드 디코더(21)와, 각 메인 워드 디코더(21)에 전원을 공급하는 메인 워드 디코더 구동 회로(22)를 포함한다. 각 메인 워드 디코더(21)로부터는, n 개의 메인 워드선(MWL0∼MWLn)이 메모리 코어(11)내부를 향해 연장되고 있다. 메인 워드선(MWL0∼MWLn)에 직교하여 서브 워드 디코드선(SWD0∼SWD3)이 배치된다. 서브 워드 디코드선(SWD0∼SWD3)도 워드 디코드를 행하는 신호선의 일부로서, X 디코더(13)로부터 공급되는 신호를 전송한다.

메모리 코어(11)는 메모리 셀에 접속되는 비트선(도시 생략)의 신호를 증폭하는 센스 앰프열(20)에 의해서, 복수의 메모리 블록(23)으로 분할된다. 복수의 메모리 블록(23)중의 하나가 선택되어, 선택된 메모리 블록(23)의 메인 워드선(MWL0∼MWLn)중의 1 개가 선택된다. 또 서브 워드 디코드선(SWD0∼SWD3)중의 1 개가 선택되어, 1 개의 워드선(서브 워드선)을 선택함으로써 메모리 셀에 대한 워드선 선택을 행한다. 여기서 메인 워드 디코더(21) 및 메인 워드 디코더 구동 회로(22)는 각 메모리 블록(23)마다 설치되어 있고, 블록마다 독립된 제어를 행할 수 있다.

도 3 의 (A) 및 (B)는 메인 워드선(MWL0∼MWLn)과 서브 워드선의 관계를 나타내는 도면이다. 도 3 의 (A)에는 도 2 의 메인 워드선(MWL0∼MWLn)중에서 4 개(MWL0 내지 MWL3)만이 도시된다. 도 3 의 (A)에 도시된 바와 같이, 메인 워드선(MWL0 내지 MWL3)중 1 개와, 서브 워드 디코드선 (SWD0 및 SWD2 혹은 SWD1 및 SWD3)이 각 서브 워드 디코드부(30)에 공급된다.

도 3 의 (B)는 메인 워드선(MWL0)과 서브 워드 디코드선(SWD0 및 SWD2)을 입력으로 하는 서브 워드 디코드부(30)를 나타낸다. 도 3 의 (B)의 서브 워드 디코드부(30)는 서브 워드 디코더(31,32)를 포함한다. 서브 워드 디코더(31)는 메인 워드선(MWL0)과 서브 워드 디코드선(SWD2)을 입력으로 하여, 양쪽이 선택된 경우에 서브 워드선(WL2)을 고전위로 한다. 또한 서브 워드 디코더(32)는 메인 워드선(MWL0)과 서브 워드 디코드선(SWD0)을 입력으로 하여, 양쪽이 선택된 경우에 서브 워드선(WL0)을 고전위로 한다.

이렇게 하여 메모리 코어(11)의 선택된 메모리 블록(23)에 있어서, 메인 워드선(MWL0∼MWLn)의 1 개와, 서브 워드 디코드선(SWD0∼SWD3)의 1 개를 선택함으로써, 서브 워드선을 선택 활성화할 수 있다.

또한, 도 2 와 도 3 의 (A) 및 (B)에 도시된 워드 디코드 구조는 메인 워드선 및 서브 워드선으로 이루어진 계층화 워드 디코더 방식이라 칭해지는 것이다. 통상 워드선 재료는 폴리실리콘이지만, 폴리실리콘은 배선 재료로서는 저항이 높고 신호 지연이 크기 때문에, 평행하게 배치한 알루미늄 배선과 폴리실리콘의 워드선을 적당한 간격으로 콘택트시켜, 워드선의 저항을 낮추는 일이 행해진다. 그러나 집적도가 증가하면 배선 간격이 좁아지고, 알루미늄 배선을 폴리실리콘 배선과 같은 피치로 패터닝하는 것이 곤란해진다. 계층화 워드 디코더 방식은, 이러한 문제점을 극복하기 위해서 채용되는 것으로, 폴리실리콘으로 이루어지는 워드선을 지연이 허락되는 정도까지 분할하여 서브 워드선으로 하고, 메인 워드선에는 알루미늄 배선을 이용하는 것으로 지연을 없애는 것이다.

이하 본 발명의 실시예는 이 계층화 워드 디코더 방식을 예로 들어 설명하지만, 계층화 구조가 아닌 워드 디코더 방식에도 동일하게 본 발명을 적용할 수 있는 것은 말할 필요도 없다.

도 4 는 도 3 의 (A)의 서브 워드 디코더(31)(또는 32)의 구체적 회로도를 도시한다. 도 4 의 서브 워드 디코더(31)(또는 32)는 PMOS 트랜지스터(41)와 NMOS 트랜지스터(42,43)를 포함한다. 여기서 PMOS 트랜지스터(41)와 NMOS 트랜지스터(42)가 워드 드라이버(44)를 구성한다. 도 4 에 있어서는 메인 워드선(MWL0∼MWLn)중의 임의의 1 개를 메인 워드선(MWL)으로서 나타낸다. 또한 한쌍의 서브 워드 디코드선(SWDZ 및 SWDX)이 설치되어 있는 것으로 한다. 또, 대응하는 서브 워드선을 서브 워드선(WL)으로서 기재한다.

메인 워드선(MWL)은 저전위인 경우에 그 메인 워드선(MWL)이 선택된 것을 나타낸다. 도 4 에 있어서는 메인 워드선(MWL)이 선택되고 또한 서브 워드 디코드선(SWDZ)가 고전위이고 서브 워드 디코드선(SWDX)가 저전위인 경우에, 대응하는 서브 워드선(WL)이 선택되어 고전위가 된다. 즉, 메인 워드선(MWL)이 저전위이고 서브 워드 디코드선(SWDX)가 저전위인 경우, PMOS 트랜지스터(41)가 도통, NMOS 트랜지스터(42,43)가 비도통이 되며, 서브 워드선(WL)이 서브 워드 디코드선(SWDZ)와 동일한 고전위가 된다.

또 도 4 에 있어서 NMOS 트랜지스터(43)는 메인 워드선(MWL)이 선택되어 저전위이더라도, 서브 워드 디코더(31)가 선택되지 않은 경우, 즉 서브 워드 디코드선(SWDZ 및 SWDX)이 저전위 및 고전위인 경우에, 서브 워드선(WL)을 저전위로 하기 위해 설치된다.

도 9 의 인버터 회로에서 설명한 것과 동일하게, 도 4 에 있어서 워드 드라이버(44)의 PMOS 트랜지스터(41)가 오프인 경우, 밴드간 터널 전류가 흘러 버리면 쓸데없는 전류가 소비되게 된다. 그래서 본 발명에 있어서는, 도 4 의 워드 드라이버(44)를 선택하는 메인 워드선(MWL)의 전위를 제어하여, 대기시 및 메모리 블록 비선택시에 메인 워드선(MWL)의 전위를 낮춤으로써, 밴드간 터널 전류를 억압한다.

도 5 는 본 발명에 의한 메인 워드 디코더 구동 회로(22)와 메인 워드 디코더(21)의 제 1 실시예를 나타낸다. 도 4 의 메인 워드 디코더 구동 회로(22)와 메인 워드 디코더(21)는 대기시 및 메모리 블록 비선택시에 메인 워드 디코더(21)의 출력인 메인 워드선(MWL)의 전위를 낮추도록 제어한다. 이것에 의해서 도 4 의 워드 드라이버(44)에 있어서의 밴드간 터널 전류를 억압하는 것이다. 즉, 워드 드라이버(44)의 PMOS 트랜지스터(41)의 게이트 전위를 낮춤으로써, PMOS 트랜지스터(41)의 벌크로부터 소스 및 드레인에 흐르는 밴드간 터널 전류를 억압할 수 있다.

종래는, 선택된 메인 워드선(MWL)에는 접지 전위(vss)가 공급되고, 그 이외의 모든 메인 워드선(MWL)에는 DRAM(l0)의 일반적인 내부 동작 전압(vii)보다도 높은 전위(svii)가 공급된다. 전위(vii)보다도 높은 전위(svii)가 메인 워드선 MWL에 필요한 이유는 다음과 같다. 즉, 메모리 셀의 셀 트랜지스터가 NMOS 이기 때문에, 메모리 셀에 하이-데이타 즉 vii 를 기록하기 위해서는 셀 트랜지스터의 게이트에 (vii+vth+α)의 전압을 인가할 필요가 있다. 여기서 vth 는 셀 트랜지스터의 임계치 전압이며, α 는 메모리 셀에 고속으로 데이타를 기록하기 위한 오버드라이브분의 전압이다. 따라서, 서브 워드선(WL)(도 4 참조)에는 DRAM(10)의 일반적인 내부 동작 전압(vii)보다도 높은 전위(svii)(=vii+vth+α)를 인가할 필요가 있다. 이 때문에 서브 워드 디코드선(SWDZ)은 선택된 메모리 블록(23)의 선택된 워드 디코더(44)에 대하여 전위 svii 를 공급한다. 그러나 선택 메모리 블록(23)에 있어서는, 서브 워드 디코드선(SWDZ)이 전위 svii 이지만 선택되지 않은 워드 디코더(44)가 존재한다. 이 경우에 비선택 워드 디코더(44)의 PMOS 트랜지스터(41)(도 4 참조)를 완전히 오프하기 위해서는 메인 워드선(MWL)에는 전위 svii 를 제공할 필요가 있다. 이것이 종래에 있어서는, 메인 워드선(MWL)에 공급되는 전위가 선택 메인 워드선 이외에는 svii 이었던 이유이다.

본 발명에 있어서는 대기시 및 비선택 메모리 블록(23)에 대해서는 메인 워드선(MWL)에 공급하는 전위를 전위 svii 로부터 낮추어 예컨대 전위 vii 로 한다. 또한 종래와 같이, 선택 메모리 블록(23)의 비선택 메인 워드선(MWL)에는 전위 svii 를 공급하고, 선택 메인 워드선 MWL 에는 접지 전위 vss 를 공급한다. 또 대기시 및 비선택 메모리 블록(23)에 있어서의 메인 워드선(MWL)의 전위는 vii 가 아니어도 좋고, svii 보다 낮은 적당한 전위가 좋다.

도 5 의 메인 워드 디코더 구동 회로(22)는 NAND 회로(51), 인버터(52), PMOS 트랜지스터(53,54), NMOS 트랜지스터(55,56) 및 PMOS 트랜지스터(57,58)를 포함한다.

NAND 회로(51)에는 메모리 블록(23)의 선택/비선택을 나타내는 신호와, DRAM(10)의 비대기/대기를 나타내는 신호가 공급된다. 메모리 블록(23)의 선택/비선택을 나타내는 신호는 X 디코더(13)의 다른 부분으로부터 공급된다. 또한 DRAM(10)의 비대기/대기를 나타내는 신호로서는, 도 1 의 제어 버퍼(15)로부터 공급되는 RAS 신호 등을 이용할 수 있다. NAND 회로(51)는 비대기로서 메모리 블록(23)이 선택된 경우에만 로우를 출력한다. 즉, 대기 상태의 경우 또는 비선택의 경우는 하이를 출력한다.

비대기로서 메모리 블록(23)이 선택된 경우, NMOS 트랜지스터(55,56)는 오프 및 온이 되며, PMOS 트랜지스터(53,54) 및 NMOS 트랜지스터(55,56)로 이루어지는 레벨 시프터 회로의 노드 N2 는 로우가 된다. 따라서 PMOS 트랜지스터(58)가 온이 되고, 전압 svii 가 메인 워드 디코더 구동 전압 VMWL 로서, 메인 워드 디코더(21)에 공급된다.

대기 상태의 경우 또는 메모리 블록(23)이 비선택인 경우에는 NMOS 트랜지스터(55,56)는 온 및 오프가 되며, PMOS 트랜지스터(53,54) 및 NMOS 트랜지스터(55,56)로 이루어지는 레벨 시프터 회로의 노드 N1 은 로우가 된다. 따라서 PMOS 트랜지스터(57)가 온이 되고, 전압 Vii 가 메인 워드 디코더 구동 전압 VMWL 로서, 메인 워드 디코더(21)에 공급된다.

또 상기 레벨 시프터 회로는 NAND 회로(51) 및 인버터(52)의 출력이 DRAM 의 내부 동작 전압 vii 에 기초하는 것이기 때문에, 이 출력의 전압을 PMOS 트랜지스터(57,58)의 동작 전압 레벨에까지 높이기 위해서 이용되는 것이다.

메인 워드 디코더(21)는 NAND 회로(61), 인버터(62), PMOS 트랜지스터(63,64), NMOS 트랜지스터(65,66), 또 PMOS 트랜지스터(67) 및 NMOS 트랜지스터(68)를 포함한다.

NAND 회로(61)에는 X 디코더(13)의 다른 부분으로부터 메인 워드선 선택 신호가 공급된다. 메인 워드선 MWL 이 선택될 때, NAND 회로(61)의 출력은 로우가 되며, 비선택인 경우는 하이가 된다.

메인 워드선 MWL 이 선택된 경우, NMOS 트랜지스터(65,66)는 오프 및 온이 되며, PMOS 트랜지스터(63,64) 및 NMOS 트랜지스터(65,66)으로 이루어지는 레벨 시프터 회로의 노드 N3 은 하이가 된다. 따라서 PMOS 트랜지스터(67) 및 NMOS 트랜지스터(68)가 각각 오프 및 온이 되어, 접지 전위(전위 vss)가 메인 워드선 MWL 에 공급된다.

메인 워드선 MWL 이 비선택의 경우에는, NMOS 트랜지스터(65,66)는 온 및 오프가 되고, PMOS 트랜지스터(64,64) 및 NMOS 트랜지스터(65,66)로 이루어지는 레벨 시프터 회로의 노드 N3 은 로우가 된다. 따라서 PMOS 트랜지스터(67) 및 NMOS 트랜지스터(68)가 각각 온 및 오프로 되어, 메인 워드 디코더 구동 전압 VMWL 이 메인 워드선 MWL 에 공급된다.

이 메인 워드 디코더 구동 전압 VMWL 은 상술한 바와 같이, 대기시 및 메모리 블록 비선택시는 전위 vii 이고, 메모리 블록 선택시는 svii 이다.

또 선택/비선택 신호, 비대기/대기 신호, 및 메인 워드선 선택 신호는 종래 기술의 범위내이므로, 그 생성등에 관한 상세한 설명은 생략한다.

이와 같이 본 발명의 제 1 실시예에 있어서는 메인 워드 디코더 구동 회로(22)와 메인 워드 디코더(21)는 대기시 및 메모리 블록 비선택시에 메인 워드 디코더(21)의 출력인 메인 워드선 MWL 의 전위를 svii 에서 vii 로 낮추도록 제어한다. 이것에 의해서 도 4 의 워드 드라이버(44)에 있어서의 밴드간 터널 전류를 억압할 수 있다.

도 6 의 (A) 및 (B)는 본 발명에 의한 메인 워드선 전위 제어를 설명하기 위한 도면이다. 도 6 의 (A) 및 (B)에 있어서, 도 4 및 도 5 와 동일한 구성 요소는 동일한 번호로 참조된다. 상술한 바와 같이, 본 발명에 의한 메인 워드선 MWL 의 전위의 제어는 크게 분류하여 대기 상태 및 메모리 블록(23)이 비선택인 경우와, 메모리 블록(23)이 선택된 경우로 나눌 수 있다.

도 6 의 (A)는 대기 상태 및 메모리 블록 비선택인 경우를 나타낸다. 본 발명에 있어서는, 대기 상태 및 메모리 블록 비선택인 경우에는, 메인 워드선 MWL 에는 전위 vii 를 공급한다. 도 6 의 (A)에 있어서, 메인 워드 디코더 구동 회로(22)의 PMOS 트랜지스터(57)가 온되어, 전위 vii 가 메인 워드 디코더(21)에 공급된다. 이 경우는 대기 상태 혹은 메모리 블록 비선택이기 때문에, 메인 워드 디코더(21)에 있어서는 PMOS 트랜지스터(67)가 온되어, 메인 워드 디코더 구동 회로(22)로부터의 전위 vii 가 메인 워드선 MWL 에 공급된다.

각 메인 워드선 MWL 은 한쌍의 서브 워드 디코더(31,31')에 입력된다. 서브 워드 디코더(31)에는 2 개의 서브 워드 디코드선 SWDZ 및 SWDX 로 이루어지는 서브 워드 디코드선 SWD2 이 입력된다. 서브 워드 디코더(31')에는 2 개의 서브 워드 디코드선 SWDZ 및 SWDX 로 이루어지는 서브 워드 디코드선 SWD0 이 입력된다. 이 경우는 대기 상태 혹은 메모리 블록 비선택이기 때문에, 서브 워드 디코드선 SWDZ 및 SWDX 에는 접지 전위 vss 가 공급된다. 각 메인 워드선 MWL 은 전위 vii 이기 때문에, 서브 워드 디코더(31,31')의 NMOS 트랜지스터(42)가 도통되며, 각 서브 워드선 WL 에는 접지 전위 vss 가 나타난다.

각 메인 워드선 MWL 에는 종래의 메인 워드선 전위 svii 보다도 낮은 전위 vii 가 공급되어 있으므로, 서브 워드 디코더(31,31')의 PMOS 트랜지스터(41)의 게이트 전위는 종래에 비하여 낮은 것이 된다. 따라서 PMOS 트랜지스터(41)의 밴드간 터널 전류를 삭감하여 소비 전류 삭감을 도모할 수 있다.

도 6 의 (B)는 메모리 블록(23)이 선택된 경우를 나타낸다. 본 발명에 있어서는, 메모리 블록 선택의 경우에는, 선택된 메인 워드선 MWL 에는 전위 vss 를 공급하고, 그 이외의 메인 워드선 MWL 에는 전위 svii 를 공급한다. 이것은 종래 기술과 동일한 전위 분배이다. 도 6 의 (B)에 있어서, 메인 워드 디코더 구동 회로(22)의 PMOS 트랜지스터(58)가 온되어, 전위 svii 가 메인 워드 디코더(21)에 공급된다. 이 경우는 메모리 블록이 선택된 경우이기 때문에, 선택된 메인 워드선 MWL 에 대해서는, 메인 워드 디코더(21)의 NMOS 트랜지스터(68)가 온되어 전위 vss 가 공급된다. 선택되지 않은 메인 워드선 MWL 에 대해서는 PMOS 트랜지스터(67)가 온되어, 메인 워드 디코더 구동 회로(22)로부터의 전위 svii 가 공급된다.

각 메인 워드선 MWL 은 한쌍의 서브 워드 디코더(31,31')에 입력된다. 서브 워드 디코더(31)에는 2 개의 서브 워드 디코드선 SWDZ 및 SWDX 로 이루어지는 서브 워드 디코드선 SWD2 가 입력된다. 서브 워드 디코더(31')에는 2 개의 서브 워드 디코드선 SWDZ 및 SWDX 로 이루어지는 서브 워드 디코드선 SWD0 이 입력된다. 도 6 의 (B)에 있어서, 서브 워드 디코더(31)를 선택하기 위해서, 서브 워드 디코드선 SWD2 의 SWDX 를 전위 vss 로 설정하고 또 SWDZ 를 전위 svii 로 설정한다. 또한 서브 워드 디코더(31')를 비선택으로 하기 위해서, 서브 워드 디코드선 SWD0 의 SWDX 를 전위 svii 로 설정하며 또 SWDZ 를 전위 vss 로 설정한다. 이렇게 하여 서브 워드 디코더(31) 및 서브 워드 디코더(31')를 각각, 선택 및 비선택으로 한다.

전위 svii 인 비선택 메인 워드선 MWL 에 대응하는 서브 워드 디코더(31,31')의 양쪽에 있어서는, NMOS 트랜지스터(42)가 온이되므로, 서브 워드선 WL 은 접지 전위 vss 가 된다.

전위 vss 인 선택 메인 워드선 MWL 에 대응하는 선택된 서브 워드 디코더(31)에 있어서는, PMOS 트랜지스터(41)가 도통되므로, 서브 워드선 WL 에는 전위 svii 가 나타난다. 그것에 대하여, 전위 vss 인 선택 메인 워드선 MWL 에 대응하는 비선택된 서브 워드 디코더(31')에 있어서는, NMOS 트랜지스터(43)가 도통되므로, 서브 워드선 WL 에는 접지 전위 vss 가 나타난다.

도 7 은 메인 워드 디코더 구동 회로(22)가 출력하는 메인 워드 디코더 구동 전압 VMWL 과, 메인 워드 디코더(21)가 출력하는 메인 워드선 MWL 의 전위를 나타내는 타이밍도이다. 도 7 에 있어서, /RAS(여기서 "/"는 신호의 반전을 나타낸다)는 독출 혹은 기록시의 어드레스 입력 명령(Row Address Strobe)이다.

타이밍도의 개시시에 있어서, /RAS가 하이일 때에는 DRAM(10)은 대기 상태에 있다. 대기 상태에 있어서, 메인 워드 디코더 구동 전압 VMWL 과 메인 워드선 MWL 은 모두 전위 vii 이다. 따라서 도 4 의 워드 드라이버(44)의 PMOS 트랜지스터(41)의 게이트에 공급되는 전위는 vii 이고, 밴드간 터널 전류가 억압된 상태로 되어 있다.

데이타 독출 혹은 기록시에는, /RAS 는 로우로 변화된다.

우선 비선택의 메모리 블록에 있어서는, 메인 워드 디코더 구동 전압 VMWL 및 메인 워드선 MWL 은 모두 전위 vii 인 상태이다. 따라서 도 4 의 워드 드라이버(44)의 PMOS 트랜지스터(41)의 게이트에 공급되는 전위는 vii 이며, 밴드간 터널 전류가 억압된 상태로 되어 있다.

선택 메모리 블록에 대해서는 아래와 같이 된다. 메인 워드 디코더 구동 전압 VMWL 은 전위 svii 가 된다. 비선택된 메인 워드선 MWL 은 메인 워드 디코더 구동 전압 VMWL 과 동일한 전위 svii 가 된다. 선택된 메인 워드선 MWL 은 접지 전위 vss 가 된다.

이와 같이 본 발명에 따르면, 대기 상태에 있어서 밴드간 터널 전류를 삭감하여 전력 소비량을 감소시킬 수 있는 동시에, 메모리 동작중이더라도 비선택의 메모리 블록에 대해서는 밴드간 터널 전류를 감소시킴으로써, 저소비 전력화를 도모할 수 있다.

상술한 설명은 특정한 실시예를 이용하여 설명되었지만, 본 발명은 여러가지 형태로 실시할 수 있는 것은 분명하다.

도 8 은 메인 워드 디코더 구동 회로(22)의 제 2 실시예를 나타낸다. 도 8 에 있어서, 도 5 와 동일한 구성 요소는 동일한 번호로 참조되며, 그 설명은 생략된다.

도 8 의 메인 워드 디코더 구동 회로(22A)에 있어서는, 도 5 의 PMOS 트랜지스터(57,58)를 대신해서, PMOS 트랜지스터(71) 및 NMOS 트랜지스터(72)가 직렬 접속된 회로가 이용된다.

이 메인 워드 디코더 구동 회로(22A)에 있어서는, 비대기 상태에서 메모리 블록이 선택되면, 노드 N2 가 로우가 되고, PMOS 트랜지스터(71)가 도통되어 전위 svii 가 메인 워드 디코더 구동 전압 VMWL 로서 출력된다. 그 이외의 경우에는 노드 N2 가 하이가 되므로, NMOS 트랜지스터(72)가 도통되어, 전위 vii 가 메인 워드 디코더 구동 전압 VMWL 로서 출력된다.

즉 제 2 실시예인 메인 워드 디코더 구동 회로(22A)는 제 1 실시예의 경우와 동일한 메인 워드 디코더 구동 전압 VMWL 을 제공할 수 있다.

본 발명은 실시예에 기초하여 설명되었지만, 상술한 실시예에 한정되지 않으며, 여러가지 변형이나 수정을 특허청구의 범위내에서 행할 수 있다.

청구범위 제 1 항의 발명에 있어서는, 워드 드라이버의 트랜지스터의 게이트 전위를 제어하는 제어부를 설치함으로써, 그 트랜지스터의 밴드간 터널 전류를 억제할 수 있다.

청구범위 제 2 항의 발명에 있어서는, 제어부는 워드 드라이버의 복수의 그룹의 각각에 대하여 독립적으로 제어를 행할 수 있기 때문에, 각 그룹마다 적절한 제어를 행할 수 있다.

청구범위 제 3 항의 발명에 있어서는, 제어부는 메모리 블록의 각각에 대하여 독립적으로 제어를 행할 수 있기 때문에, 메모리 블록마다 밴드간 터널 전류를 적절히 제어할 수 있다.

청구범위 제 4 항의 발명에 있어서는, 반도체 장치가 대기중에 밴드간 터널 전류를 제어함으로써, 대기시의 쓸데없는 전력 소비를 삭감할 수 있다.

청구범위 제 5 항의 발명에 있어서는, 반도체 기억 장치가 데이타 입출력 동작중이더라도, 비선택의 메모리 블록에 있어서 밴드간 터널 전류를 억제함으로써, 쓸데없는 전력 소비를 삭감할 수 있다.

청구범위 제 6 항의 발명에 있어서는, 워드선을 활성화하는 전위와 같은 전위가 아니라, 그것 보다도 낮은 전위를 워드 드라이버의 트랜지스터에 게이트 전압으로서 공급함으로써, 밴드간 터널 전류를 억압할 수 있다.

청구범위 제 7 항의 발명에 있어서는, 선택된 워드 드라이버는 워드선을 활성화하는 전위와 같은 전위를 전원 전압으로서 수신함으로써, 워드선에 그 전위를 공급할 수 있다.

청구범위 제 8 항의 발명에 있어서는, 워드선을 활성화하는 전위와 같은 전위가 아니라, 그것 보다도 낮은 전위를 워드 드라이버의 트랜지스터에 게이트 전압으로서 공급함으로써, 밴드간 터널 전류를 억압할 수 있다.

청구범위 제 9 항의 발명에 있어서는, 비선택된 메모리 블록에 있어서 워드선을 활성화하는 전위보다도 낮은 전위를 워드 드라이버에 공급함으로써, 비선택된 메모리 블록에 있어서의 밴드간 터널 전류를 억압하여 소비 전류의 삭감을 도모할 수 있다.

청구범위 제 10 항의 발명에 있어서는, 반도체 장치가 대기중에 워드선을 활성화하는 전위보다도 낮은 전위를 워드 드라이버에 공급함으로써, 밴드간 터널 전류를 억압하여 대기시의 쓸데없는 전력 소비를 삭감할 수 있다.

상기 청구범위 제 11 항 내지 제 14 항의 발명에 있어서는, 워드 드라이버에 공급하는 전위를 제어부에서 용이하게 전환하여 제어할 수 있으므로, 밴드간 터널 전류 억압을 용이하게 행할 수 있다.

Claims (14)

- 메모리 셀에 대하여 워드선을 선택 활성화하는 워드 드라이버와,상기 워드 드라이버의 트랜지스터의 게이트 전압을 제어함으로써 상기 트랜지스터의 밴드간 터널 전류를 억제하는 제어부를 포함하는 것을 특징으로 하는 반도체 기억 장치.

- 제 1 항에 있어서, 상기 제어부는 상기 워드 드라이버를 분할하는 복수의 그룹의 각각을 독립적으로 제어하는 것을 특징으로 하는 반도체 기억 장치.

- 제 2 항에 있어서, 상기 복수의 그룹에 대응하는 상기 메모리 셀로 이루어지는 복수의 메모리 블록을 추가로 포함하고, 상기 제어부는 상기 복수의 메모리 블록의 각각을 독립적으로 제어하는 것을 특징으로 하는 반도체 기억 장치.

- 제 1 항에 있어서, 상기 제어부는 상기 반도체 장치가 대기중에 상기 밴드간 터널 전류를 억제하는 것을 특징으로 하는 반도체 기억 장치.

- 제 2 항에 있어서, 상기 제어부는 상기 메모리 블록으로부터 데이타 입출력을 위해 선택된 메모리 블록에 대한 제어와, 상기 선택된 메모리 블록이외의 상기 메모리 블록에 대한 제어를 다르게 하고, 상기 선택된 메모리 블록이외의 상기 메모리 블록에 대하여 상기 밴드간 터널 전류를 억제하는 것을 특징으로 하는 반도체 기억 장치.

- 제 1 항에 있어서, 상기 워드 드라이버는, 상기 워드선을 활성화하는 전위와 같은 제 1 전위와, 상기 제 1 전위보다 낮은 제 2 전위와, 접지 전위인 제 3 전위중 어느 하나를 상기 게이트의 전위로서 수신하며, 상기 제어 회로는 상기 제 1 전위를 대신해서 상기 제 2 전위를 상기 워드 드라이버에 공급함으로써 상기 밴드간 터널 전류를 억제하는 것을 특징으로 하는 반도체 기억 장치.

- 제 6 항에 있어서, 상기 워드 드라이버는 상기 제 1 전위와 상기 제 3 전위중 하나를 전원 전압으로 하는 것을 특징으로 하는 반도체 기억 장치.

- 제 4 항 또는 제 5 항에 있어서, 상기 워드 드라이버는 상기 워드선을 활성화하는 전위와 같은 제 1 전위와, 상기 제 1 전위보다 낮은 제 2 전위와, 접지 전위인 제 3 전위중 어느 하나를 상기 게이트의 전위로서 수신하며, 상기 제어 회로는 상기 제 1 전위를 대신해서 상기 제 2 전위를 상기 워드 드라이버에 공급함으로써 상기 밴드간 터널 전류를 억제하는 것을 특징으로 하는 반도체 기억 장치.

- 제 8 항에 있어서, 상기 제어 회로는 상기 선택된 메모리 블록의 선택된 상기 워드 드라이버에는 상기 제 3 전위를 공급하고, 상기 선택된 메모리 블록의 비선택된 상기 워드 드라이버에는 상기 제 1 전위를 공급하며, 상기 선택된 메모리 블록이외의 상기 메모리 블록에 대응하는 상기 워드 드라이버에는 상기 제 2 전위를 공급하는 것을 특징으로 하는 반도체 기억 장치.

- 제 8 항에 있어서, 상기 제어 회로는 상기 반도체 장치가 대기중에 상기 제 2 전위를 상기 워드 드라이버에 공급함으로써 상기 밴드간 터널 전류를 억제하는 것을 특징으로 하는 반도체 기억 장치.

- 제 6 항에 있어서, 상기 제어 회로는 상기 제 1 전위를 전원 전압으로 하는 제 1 트랜지스터와, 상기 제 2 전위를 전원 전압으로 하는 제 2 트랜지스터를 포함하고, 상기 제 1 트랜지스터의 게이트 및 상기 제 2 트랜지스터의 게이트에 상보 신호를 입력함으로써 상기 제 1 전위와 상기 제 2 전위중 하나를 선택하는 것을 특징으로 하는 반도체 기억 장치.

- 제 11 항에 있어서, 상기 제어 회로는 상기 상보 신호를 상기 제 1 트랜지스터 및 상기 제 2 트랜지스터의 동작 전압 레벨에 맞추기 위한 레벨 시프터 회로를 추가로 포함하는 것을 특징으로 하는 반도체 기억 장치.

- 제 6 항에 있어서, 상기 제어 회로는 상기 제 1 전위 및 상기 제 2 전위 사이에서 직렬 접속된 P 형 트랜지스터 및 N 형 트랜지스터를 포함하며, 상기 P 형 트랜지스터의 게이트 및 상기 N 형 트랜지스터의 게이트에 공통으로 입력하는 신호에 의해서 상기 제 1 전위와 상기 제 2 전위중 하나를 선택하는 것을 특징으로 하는 반도체 기억 장치.

- 제 13 항에 있어서, 상기 제어 회로는 상기 신호를 상기 P 형 트랜지스터 및 상기 N 형 트랜지스터의 동작 전압 레벨에 맞추기 위한 레벨 시프터 회로를 추가로 포함하는 것을 특징으로 하는 반도체 기억 장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP8267277A JPH10112181A (ja) | 1996-10-08 | 1996-10-08 | 半導体記憶装置 |

| JP96-267277 | 1996-10-08 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR19980032066A KR19980032066A (ko) | 1998-07-25 |

| KR100245179B1 true KR100245179B1 (ko) | 2000-02-15 |

Family

ID=17442609

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970010206A KR100245179B1 (ko) | 1996-10-08 | 1997-03-25 | 반도체 기억 장치 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US5982701A (ko) |

| JP (1) | JPH10112181A (ko) |

| KR (1) | KR100245179B1 (ko) |

| TW (1) | TW325571B (ko) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20000045361A (ko) * | 1998-12-30 | 2000-07-15 | 김영환 | 워드라인 구동장치 |

| US6198670B1 (en) * | 1999-06-22 | 2001-03-06 | Micron Technology, Inc. | Bias generator for a four transistor load less memory cell |

| JP3948183B2 (ja) * | 2000-02-24 | 2007-07-25 | 富士通株式会社 | 半導体記憶装置 |

| KR100655279B1 (ko) * | 2000-12-14 | 2006-12-08 | 삼성전자주식회사 | 불휘발성 반도체 메모리 장치 |

| US6785186B2 (en) * | 2002-08-21 | 2004-08-31 | Micron Technology, Inc. | Design of an high speed xdecoder driving a large wordline load consuming less switching current for use in high speed syncflash memory |

| US7301849B2 (en) * | 2003-07-11 | 2007-11-27 | Texas Instruments Incorporated | System for reducing row periphery power consumption in memory devices |

| JP5151106B2 (ja) * | 2006-09-27 | 2013-02-27 | 富士通セミコンダクター株式会社 | 半導体メモリおよびシステム |

| JP2008135099A (ja) | 2006-11-27 | 2008-06-12 | Elpida Memory Inc | 半導体記憶装置 |

| JP4962206B2 (ja) * | 2007-08-10 | 2012-06-27 | 富士通セミコンダクター株式会社 | 半導体記憶装置及びワードデコーダ制御方法 |

| KR100968155B1 (ko) * | 2008-10-02 | 2010-07-06 | 주식회사 하이닉스반도체 | 반도체 메모리 장치 |

| FR2959057B1 (fr) * | 2010-04-20 | 2012-07-20 | St Microelectronics Crolles 2 | Dispositif de memoire vive dynamique avec circuiterie amelioree de commande des lignes de mots. |

| KR20160149845A (ko) * | 2015-06-19 | 2016-12-28 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR940008722B1 (ko) * | 1991-12-04 | 1994-09-26 | 삼성전자 주식회사 | 반도체 메모리 장치의 워드라인 드라이버 배열방법 |

| JPH0684354A (ja) * | 1992-05-26 | 1994-03-25 | Nec Corp | 行デコーダ回路 |

| JP2842181B2 (ja) * | 1993-11-04 | 1998-12-24 | 日本電気株式会社 | 半導体メモリ装置 |

| JP3636233B2 (ja) * | 1995-12-27 | 2005-04-06 | 富士通株式会社 | ワードドライバ回路及びそれを利用したメモリ回路 |

-

1996

- 1996-10-08 JP JP8267277A patent/JPH10112181A/ja active Pending

-

1997

- 1997-03-21 US US08/822,981 patent/US5982701A/en not_active Expired - Lifetime

- 1997-03-25 KR KR1019970010206A patent/KR100245179B1/ko not_active IP Right Cessation

- 1997-04-11 TW TW086104683A patent/TW325571B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| JPH10112181A (ja) | 1998-04-28 |

| US5982701A (en) | 1999-11-09 |

| KR19980032066A (ko) | 1998-07-25 |

| TW325571B (en) | 1998-01-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6826074B2 (en) | Semiconductor memory device | |

| US5337281A (en) | Non-volatile semiconductor memory device in which data can be erased on a block basis and method of erasing data on a block basis in non-volatile semiconductor memory device | |

| KR101488166B1 (ko) | 정적 메모리 장치 및 라이트 어시시트 기능을 구비하는에스램 | |

| US7313050B2 (en) | Word-line driver for memory devices | |

| US8164938B2 (en) | Semiconductor memory device | |

| KR100245179B1 (ko) | 반도체 기억 장치 | |

| US7099197B2 (en) | Semiconductor memory device | |

| US7417916B2 (en) | Methods of reducing coupling noise between wordlines | |

| US20020006069A1 (en) | Semiconductor memory device with reduced standby current | |

| US5818790A (en) | Method for driving word lines in semiconductor memory device | |

| JP4649260B2 (ja) | 半導体記憶装置 | |

| KR100945804B1 (ko) | 반도체 메모리 장치 | |

| US7221611B2 (en) | Semiconductor memory device for low power consumption | |

| US6269046B1 (en) | Semiconductor memory device having improved decoders for decoding row and column address signals | |

| US6909654B2 (en) | Bit line pre-charge circuit of semiconductor memory device | |

| US6859388B1 (en) | Circuit for write field disturbance cancellation in an MRAM and method of operation | |

| US5995414A (en) | Non-volatile semiconductor memory device | |

| KR100769492B1 (ko) | 반도체 집적 회로 | |

| US7684268B2 (en) | Semiconductor memory device | |

| US6473347B2 (en) | Semiconductor device having memory with effective precharging scheme | |

| US20230078117A1 (en) | Apparatuses including and methods for memory subword driver circuits with reduced gate induced drain leakage | |

| JP2005222659A (ja) | 半導体記憶装置 | |

| KR100557938B1 (ko) | 워드라인 드라이버 회로 | |

| JP2001202778A (ja) | 半導体記憶装置 | |

| JP3162783B2 (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20121114 Year of fee payment: 14 |

|

| FPAY | Annual fee payment |

Payment date: 20131031 Year of fee payment: 15 |

|

| FPAY | Annual fee payment |

Payment date: 20141103 Year of fee payment: 16 |

|

| FPAY | Annual fee payment |

Payment date: 20151030 Year of fee payment: 17 |

|

| FPAY | Annual fee payment |

Payment date: 20161028 Year of fee payment: 18 |

|

| EXPY | Expiration of term |