JP7635677B2 - 電気光学装置および電子機器 - Google Patents

電気光学装置および電子機器 Download PDFInfo

- Publication number

- JP7635677B2 JP7635677B2 JP2021147452A JP2021147452A JP7635677B2 JP 7635677 B2 JP7635677 B2 JP 7635677B2 JP 2021147452 A JP2021147452 A JP 2021147452A JP 2021147452 A JP2021147452 A JP 2021147452A JP 7635677 B2 JP7635677 B2 JP 7635677B2

- Authority

- JP

- Japan

- Prior art keywords

- electro

- diode

- optical device

- temperature detection

- wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000001514 detection method Methods 0.000 claims description 180

- 239000004065 semiconductor Substances 0.000 claims description 48

- 239000004973 liquid crystal related substance Substances 0.000 claims description 25

- 230000000295 complement effect Effects 0.000 claims description 3

- 239000000758 substrate Substances 0.000 description 84

- 230000003071 parasitic effect Effects 0.000 description 38

- 238000010586 diagram Methods 0.000 description 36

- 230000000694 effects Effects 0.000 description 12

- 101100191136 Arabidopsis thaliana PCMP-A2 gene Proteins 0.000 description 11

- 101100510617 Caenorhabditis elegans sel-8 gene Proteins 0.000 description 11

- 101100422768 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) SUL2 gene Proteins 0.000 description 11

- 101100048260 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) UBX2 gene Proteins 0.000 description 11

- 238000007689 inspection Methods 0.000 description 8

- 230000004048 modification Effects 0.000 description 8

- 238000012986 modification Methods 0.000 description 8

- 230000000052 comparative effect Effects 0.000 description 7

- 230000003287 optical effect Effects 0.000 description 7

- 239000000565 sealant Substances 0.000 description 7

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 7

- 238000003860 storage Methods 0.000 description 7

- 238000004364 calculation method Methods 0.000 description 6

- 230000007423 decrease Effects 0.000 description 5

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- 230000003068 static effect Effects 0.000 description 5

- 101100421135 Caenorhabditis elegans sel-5 gene Proteins 0.000 description 4

- -1 SEL3 Proteins 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 4

- 238000004519 manufacturing process Methods 0.000 description 4

- 230000000087 stabilizing effect Effects 0.000 description 4

- 238000012795 verification Methods 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 238000013461 design Methods 0.000 description 3

- 230000006866 deterioration Effects 0.000 description 3

- 230000005611 electricity Effects 0.000 description 3

- 238000007667 floating Methods 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 239000000463 material Substances 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 230000000149 penetrating effect Effects 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 229920005591 polysilicon Polymers 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 230000035945 sensitivity Effects 0.000 description 3

- 238000000926 separation method Methods 0.000 description 3

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 238000000034 method Methods 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 239000003566 sealing material Substances 0.000 description 2

- 238000004904 shortening Methods 0.000 description 2

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 2

- 229910021342 tungsten silicide Inorganic materials 0.000 description 2

- 239000004988 Nematic liquid crystal Substances 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 239000011324 bead Substances 0.000 description 1

- 238000009529 body temperature measurement Methods 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 229910052593 corundum Inorganic materials 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 239000003365 glass fiber Substances 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 238000005192 partition Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 238000003786 synthesis reaction Methods 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 229910001845 yogo sapphire Inorganic materials 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Landscapes

- Liquid Crystal (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

Description

いは表面側とは第1基板の基板本体が位置する側とは反対側(対向基板および液晶層が位置する側)を意味し、下層側とは第1基板の基板本体が位置する側を意味する。第2基板に形成される層の配置を説明する際、上層側あるいは表面側とは対向基板の基板本体が位置する側とは反対側(第1基板および液晶層が位置する側)を意味し、下層側とは第2基板の基板本体が位置する側を意味する。また、本発明において、「平面視」とは第1基板10または第2基板20に対する法線方向からみた様子を意味する。

1-1.電気光学装置100の具体的構成

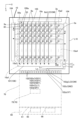

図1は、本発明の実施形態1に係る電気光学装置100の構成例を示す平面図である。図2は、図1に示す電気光学装置100の断面を模式的に示す説明図である。図1および図2に示す電気光学装置100は液晶装置であり、液晶パネルからなる電気光学パネル100pを有している。電気光学装置100では、第1基板10と第2基板20とが所定の隙間を介してシール材107によって貼り合わされており、シール材107は第2基板20の外縁に沿うように枠状に設けられている。シール材107は、光硬化樹脂や熱硬化性樹脂等からなる接着剤であり、両基板間の距離を所定値とするためのグラスファイバー、あるいはガラスビーズ等のギャップ材107aが配合されている。電気光学装置100において、第1基板10と第2基板20との間のうち、シール材107によって囲まれた領域内には、液晶層からなる電気光学層50が設けられている。シール材107には、液晶注入口として利用される途切れ部分107cが形成されており、かかる途切れ部分107cは、液晶材料の注入後、封止材108によって塞がれている。なお、液晶材料を滴下法で封入する場合は、途切れ部分107cは形成されない。第1基板10および第2基板20はいずれも四角形であり、電気光学装置100の略中央には、表示領域10aが四角形の領域として設けられている。かかる形状に対応して、シール材107も略四角形に設けられ、表示領域10aの外側は四角枠状の外周領域10cになっている。

図3は、図2に示す第1基板10の電気的構成を示す回路ブロック図である。図3において、第1基板10は、略中央領域に複数の画素100aがマトリクス状に配列された表

示領域10aを備えている。第1基板10において、表示領域10aの内側には、走査線駆動回路104からX方向に延在する複数本の走査線3a、およびデータ線駆動回路101からY方向に延在する複数本のデータ線6aが設けられており、走査線3aとデータ線6aとの交差に対応して画素100aが構成される。複数本のデータ線6aは、表示領域10aの第2辺10a2側に配置した検査回路105が電気的に接続している。複数の画素100aの各々には、Nチャネル型トランジスターからなる画素トランジスター30、および画素トランジスター30に電気的に接続された画素電極9aが形成される。画素トランジスター30のソース領域にはデータ線6aが電気的に接続され、画素トランジスター30のゲートには走査線3aが電気的に接続され、画素トランジスター30のドレイン領域には、画素電極9aが電気的に接続されている。データ線駆動回路101によってデータ線6aには画像信号VIDが供給され、走査線3aには走査信号Gが供給される。

図4は、図3に示すデータ線駆動回路101等の説明図である。図5は、図1に示す電気光学装置100において画像表示を行う際のタイミングチャートである。図4に示すように、第1基板10において、表示領域10aの第1辺10a1側にはデータ線駆動回路101が配置される。データ線駆動回路101はデマルチプレクサを含み、デマルチプレクサはサンプル・ホールド回路としての選択回路101aを含む。選択回路101aからはデータ線6aがY方向、すなわち表示領域10aの第2辺10a2側へ向かって延在している。選択回路101aは、データ線6aと画像信号配線6jとの電気的な接続を制御するトランジスター30eを備える。本実施形態において、デマルチプレクサは、例えば、8個のトランジスター30eを備える。トランジスター30eはNチャネル型トランジスターである。従って、FHD規格であれば1920/8=240であるから、240個のデマルチプレクサを備える。かかるデータ線駆動回路101は、図3に示す駆動用IC75から端子102および画像信号配線6jを経由した画像信号VIDを各データ線6a

に供給する。その際、選択回路101aのトランジスター30eは、駆動用IC75の制御回路76から制御信号線6iを介して供給される選択信号SEL1、SEL2、…SEL8に基づいて、画像信号VIDを各データ線6aに時分割的に供給する。

おけるプッシュダウン電圧を考慮して共通電位LCCOMの調整が行われるが、実施例の説明上は無視しても支障はない。

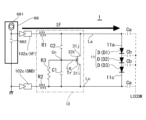

図6は、図3に示す温度検出回路1の説明図である。図6には、温度検出回路1によって温度を検出する際の回路構成を示してある。

静電容量は、例えば、0.1μFである。

子102aから静電気によるサージ電流が侵入すると、第1抵抗素子R1によって電圧変動が抑制されながら、第1容量素子C1と第2容量素子C2との接続ノードCnの電位であるトランジスターTrのゲート電極33tの電位が上昇する。このため、トランジスターTrがオン状態となるので、サージ電流は、トランジスターTrおよびカソード配線Lcを介してカソード端子102cに流れる。その際、第1抵抗素子R1は、アノード端子102aから侵入するサージ電流を緩和し、第2抵抗素子R2は、カソード端子102cから侵入するサージ電流を緩和する。また、トランジスターTrがオンとなる期間は、第1容量素子C1、第2容量素子C2、抵抗素子R3、およびトランジスターTrのゲート容量等で決まる。放電後は、抵抗素子R3によって、トランジスターTrのゲート・ソース間電圧は0Vに復帰する。よって、温度検出素子11に流れるサージ電流は、静電保護回路12によって抑制されるので、温度検出素子11を保護することができる。

図7は、図6に示す温度検出素子11等の断面を模式的に示す説明図である。図7に示すように、第1基板10において、基板本体10wにはシリコン酸化膜等からなる透光性の絶縁層41が形成され、絶縁層41の表面側に、半導体層31aを備えた画素トランジスター30が形成されている。基板本体10wと絶縁層41との間には、半導体層31a等と平面視で重なるように遮光層(図示せず)が形成されることがある。なお、図面での判別を容易にするためにゲート絶縁層32は画素トランジスター30のみに描いている。

bに電気的に接続されている。図示を省略するが、共通電位配線8aは、保持容量55の一方の電極に電気的に接続され、保持容量55の他方の電極は、中継電極6b、8dに電気的に接続されている。また、共通電位配線8aは図1の配線6gにも電気的に接続される。

図8は、本発明の実施形態1に対する比較例の説明図である。図9は、プリチャージと温度検出回路1の出力電圧VFとの関係の一例を示す図である。図10は、図6に示す温度検出素子11に寄生する容量Cbが出力電圧VFに与える影響を示すグラフである。詳細には、図10は、温度検出素子11と共通電位配線8aとの間の寄生容量Cbの静電容量と温度検出回路1の出力電圧VFとの関係を示してある。図10において、寄生容量Cbは、温度検出素子11のダイオードDの電極6e1を含む中継部P1と共通電位配線8aとの間に寄生する容量、および電極6e2を含む中継部P2と共通電位配線8aとの間に寄生する容量である。なお、電極6e1と電気的に接続されているダイオードDの一方の極は、電極6e1と同一のノードである。同様にして、電極6e2と電気的に接続されているダイオードDの一方の極は、電極6e2と同一のノードである。

Dの電極6e1、6e2と共通電位配線8aとの間に大きな静電容量を有する寄生容量が存在しないので、中継部P1、P2と共通電位配線8aとの間に大きな静電容量を有する寄生容量Cbが存在しない。それ故、以下に説明するように、プリチャージによって、共通電位配線8aの電位にスパイクノイズが発生した際、比較例では、共通電位配線8aの電位変化が寄生容量Cbを介して温度検出素子11の出力電圧VFに影響を及ぼすのに対し、実施形態1では、上記の影響が発生しにくい。

1水平走査期間=3μsec

ノイズの電圧=-1.5V

ノイズの電圧の下降時間=100nsec

ノイズの電圧の上昇時間=300nsec

図11は、本発明の実施形態2に係る電気光学装置100の説明図である。図11には、本発明の実施形態2に係る電気光学装置100の温度検出素子11の近傍の平面構成を示してある。図12は、図11に示す温度検出素子11等の断面を模式的に示す説明図である。なお、本形態の基本的な構成は実施形態1と同様であるため、共通する部分は、同一の符号を付してそれらの説明を省略する。

きるので、電気光学層50の劣化を抑制している。

図13は、本発明の実施形態2の変形例に係る電気光学装置100の説明図である。図13には、本発明の実施形態2の変形例に係る電気光学装置100の温度検出素子11等の断面を模式的に示してある。なお、本形態の基本的な構成は実施形態1、2と同様であるため、共通する部分は、同一の符号を付してそれらの説明を省略する。

印加されている導電層7e0間の距離は、絶縁層44の厚さによって大きくなっている。その結果、温度検出素子11のダイオードDの中継部P1、P2と導電層7e0との間に形成される寄生容量を小さくできる。それ故、プリチャージを実施した際、共通電位配線8aにスパイクノイズが発生した場合でも、温度検出回路1の出力電圧VFの変動を抑制することができる。よって、電気光学装置100における温度検出精度が高いので、電気光学装置100では適正に温度制御を実施することができる等、実施形態2と同様な効果を奏する。

図14は、本発明の実施形態3に係る電気光学装置100の説明図である。図14には、本発明の実施形態3に係る電気光学装置100の温度検出素子11の近傍の平面構成を示してある。図15は、図14に示す温度検出素子11の断面図である。なお、本形態の基本的な構成は実施形態1、2と同様であるため、共通する部分は、同一の符号を付してそれらの説明を省略する。なお、図14および図15では、構成が分かりやすいように、温度検出素子11において、直列に電気的に接続するダイオードDの数は3としている。

W1>W2

沿うように、グランド電位GND電位とされるカソード配線Lcを第1方向Eに延在させる。つまり、中継部P1、P2について、カソード配線Lcを図示しない配線に対するシールドとして利用してもよい。その際、カソード配線Lcについては、電気光学パネル100pのグランド電位GND電位配線とは別系統にすれば、カソード配線Lcはノイズが小さい定電位配線になるので、シールド効果が高い。

図16は、本発明の実施形態3の変形例1に係る電気光学装置100の説明図である。図16には、本発明の実施形態3の変形例1に係る電気光学装置100温度検出素子11近傍の平面構成を示してある。なお、本形態の基本的な構成は実施形態3と同様であるため、共通する部分は、同一の符号を付してそれらの説明を省略する。なお、図16では、構成が分かりやすいように、温度検出素子11において、直列に電気的に接続するダイオードの数は3とし、共通電位配線8aの一部の図示を省略してある。

W1>W2

ジスターを備える。また、走査線駆動回路104のインバーター回路104aも、選択回路101aと同様、Nチャネル型トランジスター30n2とPチャネル型トランジスター30p2とを備える。ここで、回路長の短縮のために、Nチャネル型トランジスター30n1を構成する半導体層とPチャネル型トランジスター30p1を構成する半導体層との間隔S1、およびNチャネル型トランジスター30n2を構成する半導体層とPチャネル型トランジスター30p2を構成する半導体層との間隔S2はいずれも狭く設定されている。同様の処置は検査回路105でも行われ得る。このように構成すると電気光学パネル100pの表示領域10a外側の周辺回路領域を小さくできるから電気光学パネル100pを小型化できる。その結果、電気光学パネル100pを安価に製造できる。本形態では、以下に示すように、ダイオードDにおける間隔S0は、Nチャネル型トランジスター30n1とPチャネル型トランジスター30p1との間隔S1、およびNチャネル型トランジスター30n2とPチャネル型トランジスター30p2との間隔S2以下に設定されている。

S0≦S1、S2

S0≦S3

図17は、本発明の実施形態3の変形例2に係る電気光学装置100の説明図である。図17には、本発明の実施形態3の変形例2に係る電気光学装置100の温度検出素子11近傍の平面構成を示してある。なお、本形態の基本的な構成は実施形態3と同様であるため、共通する部分は、同一の符号を付してそれらの説明を省略する。なお、図17では、構成が分かりやすいように、温度検出素子11において、直列に電気的に接続するダイオードDの数は3としてある。

W1>W2

図18は、本発明の実施形態4に係る電気光学装置100の奇数フレームにおけるプリチャージの説明図である。図19は、本発明の実施形態4に係る電気光学装置100の偶数フレームにおけるプリチャージの説明図である。なお、本形態の基本的な構成は実施形態1と同様であるため、共通する部分は、同一の符号を付してそれらの説明を省略する。

図20は、本発明の実施形態5に係る電気光学装置100のプリチャージの説明図である。なお、本形態の基本的な構成は実施形態1と同様であるため、共通する部分は、同一の符号を付してそれらの説明を省略する。

上記実施形態3、4、5では、電気光学装置100において、共通電位配線8aに開口部8a0を設けることによって温度検出素子11と共通電位配線8aとの間の寄生容量Cbを低減し、加えてプリチャージの実施方法の構成によって温度検出回路1の出力電圧VFの変動を抑制した。但し、共通電位配線8aに開口部8a0が設けられていない電気光学装置100に実施形態3、4、5に適用してもよい。すなわち、共通電位配線8aが温度検出素子11に平面視で重なっている電気光学装置100に実施形態3、4、5に適用することによって、温度検出素子11へのノイズの影響を抑制し、温度検出回路1の出力電圧VFの変動を抑制してもよい。

実施形態1、2、3、4、5では配線として共通電位配線8aを例示したが、他の配線にも適用できる。例えば、グランド電位GND配線でも、プリチャージを実施する際に同様に大きなノイズが重畳され得ることから、温度検出素子11とグランド電位GND配線との間の寄生容量を低減するために、実施形態1、2、3、4、5の構成を適用してもよい。また、交流信号が供給される配線に本発明を適用してもよい。また、プリチャージは検査回路105をプリチャージ回路に置き換えて実施するようにしてもよい。

図21は、本発明を適用した投射型表示装置1000の構成例を示すブロック図である。図22は、図21に示す光路シフト素子110の説明図である。なお、図21には、偏光板等の図示を省略してある。図21に示す投射型表示装置1000は、本発明が適用される電子機器の一例であり、照明装置190、分離光学系170、3個の電気光学装置100R、100G、100B、および投射光学系160を備えている。電気光学装置100R、100G、100Bは各々、図1~図20を参照して説明した電気光学装置100からなる。

投射型表示装置については、光源部として、各色の光を出射するLED光源等を用い、かかるLED光源から出射された色光を各々、別の液晶装置に供給するように構成してもよい。

8a0…開口部、8a1…仮想線、8e…遮光層、9a…画素電極、9b…ダミー画素電極、10…第1基板、10a…表示領域、11…温度検出素子、11a…アノード、11c…カソード、12…静電保護回路、20…第2基板、21…共通電極、29…見切り、30…画素トランジスター、30n1、30n2…Nチャネル型トランジスター、30p1、30p2…Pチャネル型トランジスター、31a、31h…半導体層、50…電気光学層、60…上位回路、65…画像制御回路、66…温度検出用駆動回路、70…配線基板、75…駆動用IC、76…制御回路、100、100B、100G、100R…電気光学装置、100a…画素、100p…電気光学パネル、101…データ線駆動回路、101a…選択回路、102a…アノード端子、102c…カソード端子、104…走査線駆動回路、104a…インバーター回路、106…プリチャージ回路、110…光路シフト素子、160…投射光学系、161…ダイクロイックプリズム、162…投射レンズ系、180…スクリーン、190…照明装置、1000…投射型表示装置、D…ダイオード、C1…第1容量素子、C2…第2容量素子、D1…第1ダイオード、D2…第2ダイオード、D3…第3ダイオード、E…第1方向、F…第2方向、P1、P2…中継部、R1…第1抵抗素子、R2…第2抵抗素子、R3…抵抗素子、W1…パターン幅、W2…電極幅、Ca、Cb…寄生容量、Ha1、Hb1…第1水平走査期間、Ha2、Hb2…第2水平走査期間、La…アノード配線、Lc…カソード配線、Cn…接続ノード

Claims (13)

- 表示領域の外側に開口部が設けられた配線と、

表示領域の外側で平面視において前記開口部の内側に設けられた温度検出素子と、

を備えることを特徴とする電気光学装置。 - 請求項1に記載の電気光学装置において、

平面視で前記開口部の内側に、前記配線と同一層の島状の遮光層が前記配線から離隔して設けられていることを特徴とする電気光学装置。 - 請求項1または2に記載の電気光学装置において、

前記表示領域に複数のデータ線を備え、

前記複数のデータ線は各々、平面視で前記配線と重なる部分を有することを特徴とする電気光学装置。 - 請求項3に記載の電気光学装置において、

前記配線は、定電位が印加されることを特徴とする電気光学装置。 - 請求項4に記載の電気光学装置において、

液晶層と、

前記液晶層と前記配線との間で共通電位が印加された導電層と、

を備えることを特徴とする電気光学装置。 - 請求項1から5までの何れか一項に記載の電気光学装置において、

前記温度検出素子は、第1ダイオードと、第2ダイオードと、前記第1ダイオードと前記第2ダイオードとを直列に電気的に接続する電極と、を有し、

前記第1ダイオードと前記第2ダイオードとは第1方向に沿って配置され、

前記電極は、前記第1方向と交差する第2方向に沿う方向の幅が、前記第1ダイオードを構成する半導体層および前記第2ダイオードを構成する半導体層の前記第2方向に沿う方向の幅よりも狭い部分を有することを特徴とする電気光学装置。 - 請求項1から5までの何れか一項に記載の電気光学装置において、

前記表示領域の外側にNチャネル型トランジスターおよびPチャネル型トランジスターを有する相補型トランジスターを備え、

前記温度検出素子は、第1ダイオードと、第2ダイオードと、前記第1ダイオードと前記第2ダイオードとを直列に電気的に接続する電極と、を有し、

前記第1ダイオードを構成する半導体層と前記第2ダイオードを構成する半導体層との間隔は、前記Nチャネル型トランジスターを構成する半導体層と前記Pチャネル型トランジスターを構成する半導体層との間隔以下であることを特徴とする電気光学装置。 - 請求項1から5までの何れか一項に記載の電気光学装置において、

前記表示領域の外側に、交流信号が供給される信号配線を備え、

前記温度検出素子は、第1ダイオードと、第2ダイオードと、前記第1ダイオードと前記第2ダイオードとを直列に電気的に接続する電極と、を有し、

前記第1ダイオードと前記第2ダイオードとは第1方向に沿って配置され、

前記第1ダイオードに電気的に接続されたカソード配線は、平面視において、前記第1ダイオードおよび前記第2ダイオードと、前記信号配線との間を前記第1方向に沿って延在していることを特徴とする電気光学装置。 - 請求項1から5までの何れか一項に記載の電気光学装置において、

前記表示領域の外側に、交流信号が供給される信号配線を備え、

前記温度検出素子は、第1ダイオードと、第2ダイオードと、前記第1ダイオードと前記第2ダイオードとを直列に電気的に接続する電極と、を有し、

前記第1ダイオードと前記第2ダイオードとは第1方向に沿って配置され、

前記信号配線は、前記第1方向と交差する第2方向に沿って延在していることを特徴とする電気光学装置。 - 請求項3から5までのいずれか一項に記載の電気光学装置において、

前記複数のデータ線を選択する選択回路と、

プリチャージ期間において、水平走査期間ごとに前記選択回路を制御する制御回路と、

を備えることを特徴とする電気光学装置。 - 請求項10に記載の電気光学装置において、

前記複数の水平走査期間には、前記複数のデータ線の一部にプリチャージ信号を供給する第1水平走査期間と、前記複数のデータ線のうち、前記一部と異なる他の一部のデータ線に前記プリチャージ信号を供給する第2水平走査期間と、が含まれていることを特徴とする電気光学装置。 - 請求項10に記載の電気光学装置において、

前記複数の水平走査期間には、前記複数のデータ線の全てにプリチャージ信号を供給する第1水平走査期間と、前記複数のデータ線の全てにプリチャージ信号を供給しない第2水平走査期間と、が含まれていることを特徴とする電気光学装置。 - 請求項1から12までの何れか一項に記載の電気光学装置を備えることを特徴とする電子機器。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021147452A JP7635677B2 (ja) | 2021-09-10 | 2021-09-10 | 電気光学装置および電子機器 |

| JP2025014794A JP7790602B2 (ja) | 2021-09-10 | 2025-01-31 | 電気光学装置および電子機器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021147452A JP7635677B2 (ja) | 2021-09-10 | 2021-09-10 | 電気光学装置および電子機器 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2025014794A Division JP7790602B2 (ja) | 2021-09-10 | 2025-01-31 | 電気光学装置および電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2023040469A JP2023040469A (ja) | 2023-03-23 |

| JP7635677B2 true JP7635677B2 (ja) | 2025-02-26 |

Family

ID=85632542

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021147452A Active JP7635677B2 (ja) | 2021-09-10 | 2021-09-10 | 電気光学装置および電子機器 |

| JP2025014794A Active JP7790602B2 (ja) | 2021-09-10 | 2025-01-31 | 電気光学装置および電子機器 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2025014794A Active JP7790602B2 (ja) | 2021-09-10 | 2025-01-31 | 電気光学装置および電子機器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (2) | JP7635677B2 (ja) |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001013511A (ja) | 1999-06-29 | 2001-01-19 | Victor Co Of Japan Ltd | 液晶表示装置 |

| JP2010073810A (ja) | 2008-09-17 | 2010-04-02 | Casio Computer Co Ltd | 薄膜センサ装置 |

| JP2015152609A (ja) | 2014-02-10 | 2015-08-24 | セイコーエプソン株式会社 | 電気光学装置および電気光学装置の駆動方法 |

| JP2017167425A (ja) | 2016-03-17 | 2017-09-21 | セイコーエプソン株式会社 | 電気光学装置、電気光学装置の制御方法および電子機器 |

| JP2018194717A (ja) | 2017-05-19 | 2018-12-06 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| JP2021018367A (ja) | 2019-07-23 | 2021-02-15 | セイコーエプソン株式会社 | 電気光学パネル、電気光学装置および電子機器 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01306820A (ja) * | 1988-06-03 | 1989-12-11 | Hitachi Ltd | 液晶表示装置 |

| JP3339248B2 (ja) * | 1995-03-14 | 2002-10-28 | ソニー株式会社 | 表示装置 |

| JP3229792B2 (ja) * | 1995-11-17 | 2001-11-19 | 三洋電機株式会社 | 液晶表示装置 |

| JPH10171369A (ja) * | 1996-12-16 | 1998-06-26 | Sharp Corp | 映像用伝送路及び画像表示装置 |

| JP3633255B2 (ja) * | 1998-01-09 | 2005-03-30 | セイコーエプソン株式会社 | 電気光学装置の駆動回路、電気光学装置及び電子機器 |

| JP2008046384A (ja) | 2006-08-17 | 2008-02-28 | Sony Corp | 画像表示装置 |

| JP2009288714A (ja) | 2008-05-30 | 2009-12-10 | Sony Corp | 液晶表示パネル及びそれを備えた電子機器 |

| US20100001943A1 (en) | 2008-07-07 | 2010-01-07 | Himax Display, Inc. | Heating system for display panel and display panel using the same |

-

2021

- 2021-09-10 JP JP2021147452A patent/JP7635677B2/ja active Active

-

2025

- 2025-01-31 JP JP2025014794A patent/JP7790602B2/ja active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001013511A (ja) | 1999-06-29 | 2001-01-19 | Victor Co Of Japan Ltd | 液晶表示装置 |

| JP2010073810A (ja) | 2008-09-17 | 2010-04-02 | Casio Computer Co Ltd | 薄膜センサ装置 |

| JP2015152609A (ja) | 2014-02-10 | 2015-08-24 | セイコーエプソン株式会社 | 電気光学装置および電気光学装置の駆動方法 |

| JP2017167425A (ja) | 2016-03-17 | 2017-09-21 | セイコーエプソン株式会社 | 電気光学装置、電気光学装置の制御方法および電子機器 |

| JP2018194717A (ja) | 2017-05-19 | 2018-12-06 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

| JP2021018367A (ja) | 2019-07-23 | 2021-02-15 | セイコーエプソン株式会社 | 電気光学パネル、電気光学装置および電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2025061999A (ja) | 2025-04-11 |

| JP2023040469A (ja) | 2023-03-23 |

| JP7790602B2 (ja) | 2025-12-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10901442B2 (en) | Active-matrix substrate, display panel and display device including the same | |

| US10453869B2 (en) | Display apparatus | |

| JP5834733B2 (ja) | 電気光学装置、電子機器 | |

| US10319316B2 (en) | Electro-optical device including a plurality of scanning lines | |

| US12222614B2 (en) | Electro-optical device and electronic apparatus | |

| WO2015052940A1 (en) | Static electricity protection circuit, electro-optical apparatus, and electronic equipment | |

| JP7635677B2 (ja) | 電気光学装置および電子機器 | |

| US11804156B2 (en) | Electro-optical device and electronic apparatus | |

| JP7673590B2 (ja) | 電気光学装置および電子機器 | |

| JP7739855B2 (ja) | 電気光学装置および電子機器 | |

| JP7732284B2 (ja) | 電気光学装置および電子機器 | |

| US12436433B2 (en) | Electro-optical device comprising an electrostatic protection circuit provided at a wiring substrate and electronic apparatus | |

| JP7800026B2 (ja) | 電気光学装置および電子機器 | |

| JP2014163952A (ja) | 電気光学装置用基板、電気光学装置用基板の製造方法、電気光学装置、電子機器 | |

| JP5286782B2 (ja) | 電気光学装置用基板及び電気光学装置、並びに電子機器 | |

| JP2016042189A (ja) | 電気光学装置、電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20240315 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20240703 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20241211 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20241217 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20241226 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20250114 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20250127 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7635677 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |