JP7626257B2 - キャパシタ - Google Patents

キャパシタ Download PDFInfo

- Publication number

- JP7626257B2 JP7626257B2 JP2023577919A JP2023577919A JP7626257B2 JP 7626257 B2 JP7626257 B2 JP 7626257B2 JP 2023577919 A JP2023577919 A JP 2023577919A JP 2023577919 A JP2023577919 A JP 2023577919A JP 7626257 B2 JP7626257 B2 JP 7626257B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- dielectric layer

- cross

- occupation ratio

- fibrous conductive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G11/00—Hybrid capacitors, i.e. capacitors having different positive and negative electrodes; Electric double-layer [EDL] capacitors; Processes for the manufacture thereof or of parts thereof

- H01G11/22—Electrodes

- H01G11/30—Electrodes characterised by their material

- H01G11/32—Carbon-based

- H01G11/36—Nanostructures, e.g. nanofibres, nanotubes or fullerenes

-

- C—CHEMISTRY; METALLURGY

- C01—INORGANIC CHEMISTRY

- C01B—NON-METALLIC ELEMENTS; COMPOUNDS THEREOF; METALLOIDS OR COMPOUNDS THEREOF NOT COVERED BY SUBCLASS C01C

- C01B32/00—Carbon; Compounds thereof

- C01B32/15—Nano-sized carbon materials

- C01B32/158—Carbon nanotubes

- C01B32/168—After-treatment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G11/00—Hybrid capacitors, i.e. capacitors having different positive and negative electrodes; Electric double-layer [EDL] capacitors; Processes for the manufacture thereof or of parts thereof

- H01G11/22—Electrodes

- H01G11/24—Electrodes characterised by structural features of the materials making up or comprised in the electrodes, e.g. form, surface area or porosity; characterised by the structural features of powders or particles used therefor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G11/00—Hybrid capacitors, i.e. capacitors having different positive and negative electrodes; Electric double-layer [EDL] capacitors; Processes for the manufacture thereof or of parts thereof

- H01G11/22—Electrodes

- H01G11/30—Electrodes characterised by their material

- H01G11/32—Carbon-based

- H01G11/40—Fibres

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/005—Electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/005—Electrodes

- H01G4/008—Selection of materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/005—Electrodes

- H01G4/012—Form of non-self-supporting electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/30—Stacked capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/33—Thin- or thick-film capacitors (thin- or thick-film circuits; capacitors without a potential-jump or surface barrier specially adapted for integrated circuits, details thereof, multistep manufacturing processes therefor)

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Materials Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Nanotechnology (AREA)

- Crystallography & Structural Chemistry (AREA)

- Organic Chemistry (AREA)

- Inorganic Chemistry (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

Description

導電性を有する基板と、

前記基板上に配置され、かつ、前記基板と電気的に接続されている複数のファイバー状導電性部材と、

前記ファイバー状導電性部材の表面を被覆する誘電体層と、

前記誘電体層の表面を被覆する導電体層と、を備え、

複数の前記ファイバー状導電性部材、前記誘電体層、前記導電体層、および前記誘電体層と前記導電体層とにより被覆された複数の前記ファイバー状導電性部材の間に形成された空間は、複合バルク部材を構成し、

前記基板の厚さ方向に沿った1つの断面において、

前記ファイバー状導電性部材が最大高さHmaxを有し、

前記複合バルク部材は、前記複合バルク部材の外縁から前記最大高さHmaxの2倍までの領域を占める一方側および他方側の外周領域と、一方側および他方側の前記外周領域に挟まれた中央領域と、を有し、

一方側および他方側の少なくとも一方の前記外周領域が、前記中央領域における前記ファイバー状導電性部材および前記誘電体層の合計の面積占有割合S11に比べて、前記ファイバー状導電性部材および前記誘電体層の合計の面積占有割合S21が高い部分を含む、キャパシタが提供される。

導電性を有する基板と、

前記基板上に配置され、かつ、前記基板と電気的に接続されている複数のファイバー状導電性部材と、

前記ファイバー状導電性部材の表面を被覆する誘電体層と、

前記誘電体層の表面を被覆する導電体層と、を備え、

複数の前記ファイバー状導電性部材、前記誘電体層、前記導電体層、および前記誘電体層と前記導電体層とにより被覆された複数の前記ファイバー状導電性部材の間に形成された空間は、複合バルク部材を構成し、

前記基板の厚さ方向に沿った1つの断面において、

前記ファイバー状導電性部材が最大高さHmaxを有し、

前記複合バルク部材は、前記複合バルク部材の外縁から前記最大高さHmaxの2倍までの領域を占める一方側および他方側の外周領域と、一方側および他方側の前記外周領域に挟まれた中央領域と、を有し、

一方側および他方側の少なくとも一方の前記外周領域が、前記中央領域における前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S12に比べて、前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S22が高い部分を含む、キャパシタが提供される。

導電性を有する基板と、

前記基板上に配置され、かつ、前記基板と電気的に接続されている複数のファイバー状導電性部材と、

前記ファイバー状導電性部材の表面を被覆する誘電体層と、

前記誘電体層の表面を被覆する導電体層と、を備え、

複数の前記ファイバー状導電性部材、前記誘電体層、前記導電体層、および前記誘電体層と前記導電体層とにより被覆された複数の前記ファイバー状導電性部材の間に形成された空間は、複合バルク部材を構成し、

前記基板の厚さ方向に沿った1つの断面において、前記ファイバー状導電性部材は最大高さHmaxを有し、

前記基板の面内方向に対して平行な1つの断面において、

前記複合バルク部材は、前記複合バルク部材の外縁から前記最大高さHmaxの2倍までの領域を占める外周領域と、前記外周領域に囲まれた中央領域とを有し、

前記外周領域が、前記中央領域における前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S13に比べて、前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S23が高い部分を含む、キャパシタが提供される。

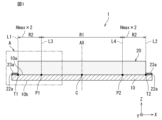

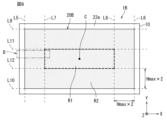

図1は、実施形態1におけるキャパシタの概略断面模式図である。図1は、基板10の厚さ方向に沿った断面を示す。図1では、便宜上、基板10と複合バルク部材20の外形とを示しており、ファイバー状導電性部材21、誘電体層22、導電体層23および空間24を省略している。図2は、図1のA部の拡大図である。図2において、誘電体層22および導電体層23で順次被覆されたファイバー状導電性部材21が模式的に示されている。便宜上、図2において、基板10、ファイバー状導電性部材21、誘電体層22および導電体層23の一部のみが示されている。図3は、図1の基板面内方向に沿った概略断面模式図である。

キャパシタ1は、導電性を有する基板10と、基板10上に配置され、かつ、基板10と電気的に接続されている複数のファイバー状導電性部材21と、ファイバー状導電性部材21の表面を被覆する誘電体層22と、誘電体層22の表面を被覆する導電体層23と、を備える。キャパシタ1は、導電体層23と接触する導電部材(図示省略)を有し得る。複数のファイバー状導電性部材21、誘電体層22、導電体層23、および誘電体層22と導電体層23とにより被覆された複数のファイバー状導電性部材の間に形成された空間24は、複合バルク部材20を構成している。空間24は、樹脂などの充填材によって埋められていてよい。導電部材については、後述する。

複合バルク部材20は、複数のファイバー状導電性部材21(以下、導電ファイバー21と称する。)、誘電体層22、導電体層23、および誘電体層22と導電体層23とにより被覆された複数の導電ファイバー21(以下、単に被覆された導電ファイバー21とも称する。)の間に形成された空間24により構成されている。

複合バルク部材20は、キャパシタ1の厚さ方向の断面(例えば、XZ断面)から決定することができる。上記の通り、複合バルク部材20は、誘電体部分22aおよび導電体部分23aを含まないため、これを除外するように決定される。

最大高さHmaxは、例えば、上記のXZ断面(No.1)のSEM画像から決定される。導電ファイバー21の、基板10の表面10aからZ方向に最も離れている端部を特定し、この端部と表面10aとの間のZ方向の距離が、最大高さHmaxである。

図1に示すように、XZ断面において、外周領域R2は、中央領域R1を挟んでX方向の一方側および他方側(以下、左側および右側とも称する。)の2か所に配置されている。一方側および他方側の外周領域R2は、中央領域R1を介して対向している。

外周領域R2は、上記のXZ断面(No.1)のSEM画像と最大高さHmaxとを用いて決定される。SEM画像において、接点T1およびT2から、中心軸AXに向かって(図示するように接点T1およびT2が基板10の表面10a上にある場合は、中心Cに向かって)、最大高さHmaxの2倍の距離にある点(P1およびP2)をプロットする。点P1を含み、かつZ方向に延びる第3直線L3より左側の領域が、一方側の外周領域R2である。点P2を含み、かつZ方向に延びる第4直線L4より右側の領域が、他方側の外周領域R2である。第3直線L3と第4直線L4とで挟まれた領域が中央領域R1である。

面積占有割合S11は、厚さ方向の断面(例えば、XZ断面)における中央領域R1の任意の一部分に占める、導電ファイバー21および誘電体層22の合計の面積占有割合である。面積占有割合S21は、上記と同じ厚さ方向の断面の外周領域R2の任意の一部分に占める、導電ファイバー21および誘電体層22の合計の面積占有割合である。外周領域R2の一部分において、面積占有割合S21が面積占有割合S11より低い場合であっても、当該厚さ方向の断面における外周領域R2の他の部分の面積占有割合S21が、面積占有割合S11より高ければよい。

面積占有割合S11,S21は、上記のXZ断面(No.1)のSEM画像を用いて、次のようにして算出される。SEM画像において、複合バルク部材20、外周領域R2および中央領域R1は特定されている。複合バルク部材20において、導電ファイバー21、誘電体層22、導電体層23、および充填樹脂(空間24)は区別されている。

上記で使用されたXZ断面(No.1)のSEM画像が、基板10の厚さ方向の断面のSEM画像であるか否かは、観察されている基板10の厚さおよび幅によって確認することができる。SEM画像から測定される基板10の厚さが、本来の基板の厚さより大きい場合、当該断面は、厚さ方向の断面ではないと判断できる。「本来の基板の厚さより大きい」とは、SEM画像における基板10の厚さが、本来の基板10の厚さより5%以上大きいことを意味する。また、SEM画像から測定される基板10の幅が、本来の基板の幅(基板の中心を通る直線と基板の両端部との2つの交点間の距離)より小さい場合にも、当該断面は、厚さ方向の断面ではないと判断できる。「本来の基板の幅より小さい」とは、SEM画像における基板10の幅が、本来の基板10の幅より5%以上小さいことを意味する。

≪導電ファイバー≫

本開示において、導電ファイバー21は、その長手方向寸法(長さ)が該長手方向に垂直な断面最大寸法に比して(好ましくは著しく)大きいもの、概略的には細長い糸状のもの、であれば特に限定されない。

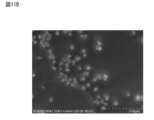

導電ファイバー21の平均数密度は、面積占有割合S11,S21の算出に使用された試料を用いて算出できる。まず、上記試料の、基板10の表面10aからの高さHが最大高さHmaxの20%以下(典型的には、10%以下)となる第1位置におけるXY断面を、研磨により露出させる。このとき、誘電体部分22aまたは導電体部分23aを切断するXY断面を得てもよく、切断しないXY断面を得てもよい。得られるXY断面には、複合バルク部材20のXY断面の一部(半分以下であり得る)が示されているが、当該XY断面の残部も、得られるXY断面の一部と同様の構成を有していると考えて差し支えない。

基板10は、互いに対向する2つの主面(表面10aおよび裏面10b)を有し、例えば板状(基板)、箔状、フィルム状、ブロック状などの形態であり得る。

誘電体層22を構成する誘電性材料としては、適宜選択され得る。例えば、二酸化シリコン、酸化アルミニウム、窒化シリコン、酸化タンタル、酸化ハフニウム、チタン酸バリウム、ジルコン酸チタン酸鉛が挙げられる。これらは単独で用いてもよく、2種以上を(例えば積層して)用いてもよい。

導電体層23を構成する導電性材料としては、例えば、金属、導電性高分子(導電性を有するおよび/または導電性が付与された高分子材料であり、有機導電性材料とも称される)が挙げられる。これらは単独で用いてもよく、2種以上を用いてもよい。導電体層23は、導電性材料が異なる複数の層の積層体であってもよい。

被覆された導電ファイバー21同士の間には、空間24が形成されている。外周領域R1における面積占有割合S21を高くすることにより、この空間24が小さくなって、複合バルク部材20の機械的強度が高まる。

キャパシタ1は、導電体層23と接触する導電部材を有し得る。導電部材は、導電体層23と電気的に接続されており、電極をキャパシタ1の外部に引き出す役割を果たす。

本実施形態のキャパシタ1は、例えば、以下を含む製造方法によって得ることができる:

(a)基板10の表面10aに、中央部よりも外縁部の付着量が多くなるように触媒を付着させること、

(b)触媒を核として、基板10の表面10aに複数の導電ファイバー21を成長させて、当該基板10と一方の端部にて直接接合している複数の導電ファイバー21により構成される、フォレストを準備すること、

(c)複数の導電ファイバー21の表面を被覆する誘電体層22(および存在する場合には誘電体部分22a、以下同様)を、ゾルゲル法により形成すること、および

(d)誘電体層22の表面を被覆する導電体層23(および存在する場合には導電体部分23a、以下同様)を形成すること。

以下、工程(a)~(d)についてより詳細に説明する。

まず、基板10の表面10aに触媒を付着させる。垂直配向カーボンナノチューブ(VACNT、導電ファイバー21)は、この触媒を核にして成長する。基板10の表面10aの中央部よりも外縁部の付着量が多くなるように触媒を付着させることにより、得られるフォレストの縁側に、VACNTの密な部分を設けることができる。

工程(b)

次に、触媒を核として、基板10の表面10aに複数のVACNTを成長させる。これにより、基板10と一方の端部にて直接接合している複数のVACNTにより構成される、フォレストが得られる。

続いて、少なくともVACNTの表面を被覆する誘電体層22を、ゾルゲル法により形成する。

続いて、誘電体層22の表面を被覆する導電体層23を形成する。

図4は、実施形態1の変形例1におけるキャパシタの概略断面模式図である。図4は、図1に対応する断面である。図5は、図4のB部の拡大図であり、図2に対応している。

キャパシタ1Aは、例えば、以下を含む製造方法によって得ることができる:

(a’)基板10の表面10aに配置され、かつ、当該基板10と一方の端部にて直接接合している複数のVACNT(導電ファイバー21)により構成される、フォレストを準備すること、

(b’)フォレストの外側にあるVACNTを、中央に向けて傾斜させること、

(c)複数のVACNTの表面を被覆する誘電体層22を、ゾルゲル法により形成すること、および

(d)誘電体層22の表面を被覆する導電体層23を形成すること。

得られたフォレストの縁にあるVACNTを、中央に向けて傾斜させる。

フォレストを適切な溶媒に浸漬することで、フォレストの縁にあるVACNTを、中央に向けて傾斜させることができる。フォレストを適切な溶媒に浸漬すると、特にフォレストの外側にあるVACNT同士が凝集し易くなる。一方、フォレストの中央付近にあるVACNTは直立状態が維持され易い。その結果、縁にあるVACNTが中央に向かって傾斜する。

実施形態2は、実施形態1とは、面積占有割合を算出する際に用いられる要素が相違する。具体的には、面積占有割合を算出する際、導電ファイバー21および誘電体層22の面積に加えて、導電体層23の面積を用いる。その他の構成は、実施形態1と同様であり、実施形態1と同一の符号を付してその説明を省略する。実施形態2は、実施形態1と同じ図1~3を用いて説明される。

変形例2は、実施形態2とは、複合バルク部材の外形が相違する。この相違する構成は、実施形態1とその変形例1との間の相違と同様である。変形例2は、変形例1と同じ図4および5を用いて説明される。

実施形態3は、実施形態1とは、面積占有割合を算出する際に用いられる要素および断面が相違する。この相違する構成を以下に説明する。その他の構成は、実施形態1と同様であり、実施形態1と同一の符号を付してその説明を省略する。

複合バルク部材20Bを構成する導電ファイバー21は、最大高さHmaxを有する。複合バルク部材20Bは、XY断面において、複合バルク部材20Bの外縁から最大高さHmaxの2倍までの範囲の外周領域R2と、外周領域R2に囲まれた中央領域R1とを有する。

最大高さHmaxは、実施形態1と同様して得られたXZ断面のSEM画像から、実施形態1と同様にして決定される。

XY断面において、外周領域R2は、中央領域R1の周囲を取り囲むように配置されている。

中央領域R1および外周領域R2は、最大高さHmaxを決定する際に使用された試料を用いて、実施形態1において平均数密度N1およびN2を算出するために行った、中央領域R1および外周領域R2の決定と同様の方法により、決定される。この方法に関し、図3が参照できる。上記試料には、キャパシタ1BのXZ断面と、XY断面の半分とが露出している。

対向している外周領域R2は、同様に、最大高さHmaxを決定する際に使用された試料のXY断面から決定できる。このXY断面には、複合バルク部材20BのXY断面の一部(半分以下であり得る)が示されているが、当該XY断面の残部も、得られるXY断面の一部と同様の構成を有していると考えて差し支えない。当該XY断面は図3に模式的に示されている。図3と図6とは対応しており、図3において、切断によって除去された複合バルク部材20BのXY断面の残部を補足した一例が、図6である。対向している外周領域R2は、図6を用いて決定してよい。

上記の試料のXY断面をSEMで観察する。SEM画像において、複合バルク部材20B、中央領域R1および外周領域R2はすでに特定されている。

変形例3は、実施形態3とは、複合バルク部材の外形が相違する。この相違する構成は、実施形態1とその変形例1との間の相違と同様である。その他の構成は、実施形態1と同様であり、実施形態1と同一の符号を付してその説明を省略する。

(製造例1)

変形例1,2および3に係る複合バルク部材を有するキャパシタを製造した。

Si基板10の表面上に触媒を塗布し、VACNTを成長させて、フォレスト200を得た。

フォレスト200が設けられた基板10を、ドデシル硫酸ナトリウム、アンモニアおよびエタノールを含む原料液に浸漬した。浸漬は以下のようにして実施した。まず、液温が室温(23℃±3℃)の原料液に、基板10と原料液の液面との成す角度が概ね90度になるように、フォレスト200が設けられた基板10を投入した。投入速度は5mm/秒とした。その後、基板10を引き上げて、乾燥させた。

上記のフォレスト200に誘電体層22を形成した。詳細には、3-アミノプロピルトリエトキシシランとエタノールとを混合した原料混合液に、基板10上のVACNTを浸漬し、25℃にて1.5時間、300rpmで撹拌しながら維持した後、基板10を引き上げた。最後に乾燥して、基板10上の複数のCNT(導電ファイバー21)の表面を覆う誘電体層22(SiO2)を形成した。

次いで、PEDOT(ポリエチレンジオキシチオフェン)およびPSS(ポリスチレンスルホン酸)を含む分散液に上記の基板10を浸漬して、誘電体層22上に、導電体層23(PEDOT/PSSの複合体)を形成した。このようにして、キャパシタを得た。

導電性を有する基板と、

前記基板上に配置され、かつ、前記基板と電気的に接続されている複数のファイバー状導電性部材と、

前記ファイバー状導電性部材の表面を被覆する誘電体層と、

前記誘電体層の表面を被覆する導電体層と、を備え、

複数の前記ファイバー状導電性部材、前記誘電体層、前記導電体層、および前記誘電体層と前記導電体層とにより被覆された複数の前記ファイバー状導電性部材の間に形成された空間は、複合バルク部材を構成し、

前記基板の厚さ方向に沿った1つの断面において、

前記ファイバー状導電性部材が最大高さHmaxを有し、

前記複合バルク部材は、前記複合バルク部材の外縁から前記最大高さHmaxの2倍までの領域を占める一方側および他方側の外周領域と、一方側および他方側の前記外周領域に挟まれた中央領域と、を有し、

一方側および他方側の少なくとも一方の前記外周領域が、前記中央領域における前記ファイバー状導電性部材および前記誘電体層の合計の面積占有割合S11に比べて、前記ファイバー状導電性部材および前記誘電体層の合計の面積占有割合S21が高い部分を含む、キャパシタ。

<2>

前記基板の厚さ方向に沿った1つの断面において、

一方側および他方側の前記外周領域がいずれも、前記面積占有割合S11に比べて、前記面積占有割合S21が高い部分を含む、<1>に記載のキャパシタ。

<3>

前記基板の厚さ方向に沿った複数の断面のそれぞれにおいて、

一方側および他方側の少なくとも一方の前記外周領域が、前記面積占有割合S11に比べて、前記面積占有割合S21が高い部分を含む、<1>または<2>に記載のキャパシタ。

<4>

導電性を有する基板と、

前記基板上に配置され、かつ、前記基板と電気的に接続されている複数のファイバー状導電性部材と、

前記ファイバー状導電性部材の表面を被覆する誘電体層と、

前記誘電体層の表面を被覆する導電体層と、を備え、

複数の前記ファイバー状導電性部材、前記誘電体層、前記導電体層、および前記誘電体層と前記導電体層とにより被覆された複数の前記ファイバー状導電性部材の間に形成された空間は、複合バルク部材を構成し、

前記基板の厚さ方向に沿った1つの断面において、

前記ファイバー状導電性部材が最大高さHmaxを有し、

前記複合バルク部材は、前記複合バルク部材の外縁から前記最大高さHmaxの2倍までの領域を占める一方側および他方側の外周領域と、一方側および他方側の前記外周領域に挟まれた中央領域と、を有し、

一方側および他方側の少なくとも一方の前記外周領域が、前記中央領域における前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S12に比べて、前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S22が高い部分を含む、キャパシタ。

<5>

前記基板の厚さ方向に沿った1つの断面において、

一方側および他方側の前記外周領域がいずれも、前記面積占有割合S12に比べて、前記面積占有割合S22が高い部分を含む、<4>に記載のキャパシタ。

<6>

前記基板の厚さ方向に沿った複数の断面のそれぞれにおいて、

一方側および他方側の少なくとも一方の前記外周領域が、前記面積占有割合S12に比べて、前記面積占有割合S22が高い部分を含む、<4>または<5>に記載のキャパシタ。

<7>

導電性を有する基板と、

前記基板上に配置され、かつ、前記基板と電気的に接続されている複数のファイバー状導電性部材と、

前記ファイバー状導電性部材の表面を被覆する誘電体層と、

前記誘電体層の表面を被覆する導電体層と、を備え、

複数の前記ファイバー状導電性部材、前記誘電体層、前記導電体層、および前記誘電体層と前記導電体層とにより被覆された複数の前記ファイバー状導電性部材の間に形成された空間は、複合バルク部材を構成し、

前記基板の厚さ方向に沿った1つの断面において、前記ファイバー状導電性部材は最大高さHmaxを有し、

前記基板の面内方向に対して平行な1つの断面において、

前記複合バルク部材は、前記複合バルク部材の外縁から前記最大高さHmaxの2倍までの領域を占める外周領域と、前記外周領域に囲まれた中央領域とを有し、

前記外周領域が、前記中央領域における前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S13に比べて、前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S23が高い部分を含む、キャパシタ。

<8>

前記基板の面内方向に対して平行な1つの断面において、

前記外周領域のうち、前記中央領域を介して対向する一方側および他方側の部分がいずれも、前記面積占有割合S13に比べて、前記面積占有割合S23が高い部分を含む、<7>に記載のキャパシタ。

<9>

前記基板の面内方向に対して平行な複数の断面のそれぞれにおいて、

前記外周領域が、前記面積占有割合S13に比べて、前記面積占有割合S23が高い部分を含む、<7>または<8>に記載のキャパシタ。

<10>

前記誘電体層の厚さが、10nm以上である、<1>~<9>のいずれかに記載のキャパシタ。

<11>

前記外周領域における複数の前記ファイバー状導電性部材の平均数密度N2が、108本/cm2以上である、<1>~<10>のいずれかに記載のキャパシタ。

<12>

複数の前記ファイバー状導電性部材の平均長さが、50μm以上である、<1>~<11>のいずれかに記載のキャパシタ。

<13>

前記中央領域における複数の前記ファイバー状導電性部材の平均数密度N1に対する、前記外周領域における複数の前記ファイバー状導電性部材の平均数密度N2の比N2/N1が、2以上である、<1>~<12>のいずれかに記載のキャパシタ。

<14>

前記ファイバー状導電性部材が、カーボンナノチューブである、<1>~<13>のいずれかに記載のキャパシタ。

10 基板

10a 表面

10b 裏面

20,20A,20B 複合バルク部材

21 ファイバー状導電性部材(導電ファイバー)

22 誘電体層

22a 誘電体部分

23 導電体層

23a 導電体部分

24 空間

200 フォレスト

C 基板の中心

AX 中心軸

R1 中央領域

R2 外周領域

L1,L2,L5,L6,L9.L10 誘電体層と誘電体部分との境界

L3,L4,L7,L8,L11,L12 中央領域R1と外周領域R2との境界

T1 第1直線L1と複合バルク部材と接点

T2 第2直線L2と複合バルク部材と接点

P1 接点T1から中心軸AXに向かって最大高さHmaxの2倍の距離にある点

P2 接点T2から中心軸AXに向かって最大高さHmaxの2倍の距離にある点

Claims (14)

- 導電性を有する基板と、

前記基板上に配置され、かつ、前記基板と電気的に接続されている複数のファイバー状導電性部材と、

前記ファイバー状導電性部材の表面を被覆する誘電体層と、

前記誘電体層の表面を被覆する導電体層と、を備え、

複数の前記ファイバー状導電性部材、前記誘電体層、前記導電体層、および前記誘電体層と前記導電体層とにより被覆された複数の前記ファイバー状導電性部材の間に形成された空間は、複合バルク部材を構成し、

前記基板の厚さ方向に沿った1つの断面において、

前記ファイバー状導電性部材が最大高さHmaxを有し、

前記複合バルク部材は、前記複合バルク部材の外縁から前記最大高さHmaxの2倍までの領域を占める一方側および他方側の外周領域と、一方側および他方側の前記外周領域に挟まれた中央領域と、を有し、

一方側および他方側の少なくとも一方の前記外周領域が、前記中央領域における前記ファイバー状導電性部材および前記誘電体層の合計の面積占有割合S11に比べて、前記ファイバー状導電性部材および前記誘電体層の合計の面積占有割合S21が高い部分を含む、キャパシタ。 - 前記基板の厚さ方向に沿った1つの断面において、

一方側および他方側の前記外周領域がいずれも、前記面積占有割合S11に比べて、前記面積占有割合S21が高い部分を含む、請求項1に記載のキャパシタ。 - 前記基板の厚さ方向に沿った複数の断面のそれぞれにおいて、

一方側および他方側の少なくとも一方の前記外周領域が、前記面積占有割合S11に比べて、前記面積占有割合S21が高い部分を含む、請求項1または2に記載のキャパシタ。 - 導電性を有する基板と、

前記基板上に配置され、かつ、前記基板と電気的に接続されている複数のファイバー状導電性部材と、

前記ファイバー状導電性部材の表面を被覆する誘電体層と、

前記誘電体層の表面を被覆する導電体層と、を備え、

複数の前記ファイバー状導電性部材、前記誘電体層、前記導電体層、および前記誘電体層と前記導電体層とにより被覆された複数の前記ファイバー状導電性部材の間に形成された空間は、複合バルク部材を構成し、

前記基板の厚さ方向に沿った1つの断面において、

前記ファイバー状導電性部材が最大高さHmaxを有し、

前記複合バルク部材は、前記複合バルク部材の外縁から前記最大高さHmaxの2倍までの領域を占める一方側および他方側の外周領域と、一方側および他方側の前記外周領域に挟まれた中央領域と、を有し、

一方側および他方側の少なくとも一方の前記外周領域が、前記中央領域における前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S12に比べて、前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S22が高い部分を含む、キャパシタ。 - 前記基板の厚さ方向に沿った1つの断面において、

一方側および他方側の前記外周領域がいずれも、前記面積占有割合S12に比べて、前記面積占有割合S22が高い部分を含む、請求項4に記載のキャパシタ。 - 前記基板の厚さ方向に沿った複数の断面のそれぞれにおいて、

一方側および他方側の少なくとも一方の前記外周領域が、前記面積占有割合S12に比べて、前記面積占有割合S22が高い部分を含む、請求項4または5に記載のキャパシタ。 - 導電性を有する基板と、

前記基板上に配置され、かつ、前記基板と電気的に接続されている複数のファイバー状導電性部材と、

前記ファイバー状導電性部材の表面を被覆する誘電体層と、

前記誘電体層の表面を被覆する導電体層と、を備え、

複数の前記ファイバー状導電性部材、前記誘電体層、前記導電体層、および前記誘電体層と前記導電体層とにより被覆された複数の前記ファイバー状導電性部材の間に形成された空間は、複合バルク部材を構成し、

前記基板の厚さ方向に沿った1つの断面において、前記ファイバー状導電性部材は最大高さHmaxを有し、

前記基板の面内方向に対して平行な1つの断面において、

前記複合バルク部材は、前記複合バルク部材の外縁から前記最大高さHmaxの2倍までの領域を占める外周領域と、前記外周領域に囲まれた中央領域とを有し、

前記外周領域が、前記中央領域における前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S13に比べて、前記ファイバー状導電性部材、前記誘電体層および前記導電体層の合計の面積占有割合S23が高い部分を含む、キャパシタ。 - 前記基板の面内方向に対して平行な1つの断面において、

前記外周領域のうち、前記中央領域を介して対向する一方側および他方側の部分がいずれも、前記面積占有割合S13に比べて、前記面積占有割合S23が高い部分を含む、請求項7に記載のキャパシタ。 - 前記基板の面内方向に対して平行な複数の断面のそれぞれにおいて、

前記外周領域が、前記面積占有割合S13に比べて、前記面積占有割合S23が高い部分を含む、請求項7または8に記載のキャパシタ。 - 前記誘電体層の厚さが、10nm以上である、請求項1、4または7に記載のキャパシタ。

- 前記外周領域における複数の前記ファイバー状導電性部材の平均数密度N2が、108本/cm2以上である、請求項1、4または7に記載のキャパシタ。

- 複数の前記ファイバー状導電性部材の平均長さが、50μm以上である、請求項1、4または7に記載のキャパシタ。

- 前記中央領域における複数の前記ファイバー状導電性部材の平均数密度N1に対する、前記外周領域における複数の前記ファイバー状導電性部材の平均数密度N2の比N2/N1が、2以上である、請求項1、4または7に記載のキャパシタ。

- 前記ファイバー状導電性部材が、カーボンナノチューブである、請求項1、4または7に記載のキャパシタ。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2022175701 | 2022-11-01 | ||

| JP2022175701 | 2022-11-01 | ||

| PCT/JP2023/026071 WO2024095537A1 (ja) | 2022-11-01 | 2023-07-14 | キャパシタ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JPWO2024095537A1 JPWO2024095537A1 (ja) | 2024-05-10 |

| JPWO2024095537A5 JPWO2024095537A5 (ja) | 2024-09-26 |

| JP7626257B2 true JP7626257B2 (ja) | 2025-02-04 |

Family

ID=90930181

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2023577919A Active JP7626257B2 (ja) | 2022-11-01 | 2023-07-14 | キャパシタ |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20250201493A1 (ja) |

| JP (1) | JP7626257B2 (ja) |

| CN (1) | CN120019725A (ja) |

| WO (1) | WO2024095537A1 (ja) |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050219788A1 (en) | 2004-03-18 | 2005-10-06 | Nanosys, Inc. | Nanofiber surface based capacitors |

| WO2019058922A1 (ja) | 2017-09-19 | 2019-03-28 | 株式会社村田製作所 | キャパシタ |

| US20210074477A1 (en) | 2018-05-18 | 2021-03-11 | Murata Manufacturing Co., Ltd. | Integrated energy storage component |

| WO2021059570A1 (ja) | 2019-09-25 | 2021-04-01 | 株式会社村田製作所 | ナノ構造集合体およびその製造方法 |

| WO2021229871A1 (ja) | 2020-05-12 | 2021-11-18 | 株式会社村田製作所 | 構造体 |

-

2023

- 2023-07-14 WO PCT/JP2023/026071 patent/WO2024095537A1/ja not_active Ceased

- 2023-07-14 JP JP2023577919A patent/JP7626257B2/ja active Active

- 2023-07-14 CN CN202380073651.0A patent/CN120019725A/zh not_active Withdrawn

-

2025

- 2025-03-03 US US19/068,170 patent/US20250201493A1/en active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20050219788A1 (en) | 2004-03-18 | 2005-10-06 | Nanosys, Inc. | Nanofiber surface based capacitors |

| WO2019058922A1 (ja) | 2017-09-19 | 2019-03-28 | 株式会社村田製作所 | キャパシタ |

| US20210074477A1 (en) | 2018-05-18 | 2021-03-11 | Murata Manufacturing Co., Ltd. | Integrated energy storage component |

| WO2021059570A1 (ja) | 2019-09-25 | 2021-04-01 | 株式会社村田製作所 | ナノ構造集合体およびその製造方法 |

| WO2021229871A1 (ja) | 2020-05-12 | 2021-11-18 | 株式会社村田製作所 | 構造体 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN120019725A (zh) | 2025-05-16 |

| JPWO2024095537A1 (ja) | 2024-05-10 |

| US20250201493A1 (en) | 2025-06-19 |

| WO2024095537A1 (ja) | 2024-05-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102290618B1 (ko) | 나노와이어 클러스터 형성 방법 | |

| JP2013524504A (ja) | 電荷蓄積デバイス、電荷蓄積デバイスを製造する方法、電荷蓄積デバイスの導電構造を形成する方法、電荷蓄積デバイスを利用する移動型電子デバイス、及び、電荷蓄積デバイスを含むマイクロ電子デバイス | |

| US11393629B2 (en) | Multilayer ceramic electronic component including an external electrode having a graphene platelet | |

| CN106463618A (zh) | 电容器及其制造方法 | |

| JP2014535124A (ja) | エネルギー貯蔵デバイスのエネルギー密度及び達成可能な電力出力を増やす方法 | |

| US20160118157A1 (en) | Carbon nanotube composite conductors | |

| KR20140138701A (ko) | 세장형 몸체들을 갖는 전도성 엘리먼트들의 어레이를 포함하는 마이크로스케일 및 나노스케일 커패시터들 | |

| US20130224394A1 (en) | Method for producing a capacitor including an array of nanocapacitors | |

| US11749463B2 (en) | Capacitor and method for manufacturing the same | |

| US12362104B2 (en) | Capacitor | |

| US8287604B2 (en) | High energy density storage material device using nanochannel structure | |

| EP1976351A2 (en) | Wiring structure and method of forming the same | |

| JP7626257B2 (ja) | キャパシタ | |

| JP7652330B2 (ja) | キャパシタ | |

| US11869719B2 (en) | Composite capacitor | |

| US20230005663A1 (en) | Structural body | |

| JP7652339B2 (ja) | キャパシタおよびキャパシタの製造方法 | |

| CN115472433A (zh) | 具有明确限定的绝缘区域的高密度电容性器件 | |

| JP2024051956A (ja) | キャパシタ | |

| TW202322154A (zh) | 一種線性阻變元件及製備方法 | |

| JP7485082B2 (ja) | キャパシタ | |

| CN109585179B (zh) | 气凝胶电容器及制造该气凝胶电容器的方法 | |

| JP2017130669A (ja) | エネルギー貯蔵デバイスのエネルギー密度及び達成可能な電力出力を増やす方法 | |

| CN102782784B (zh) | 来自低维度金属体系的复合材料的高电介质电容率材料 | |

| TWI505534B (zh) | 蓄電裝置、其製造方法、為其製造導電結構之方法、使用其之行動電子裝置、與含其之微電子裝置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20231218 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20231218 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20241224 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20250106 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7626257 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |