JP7553458B2 - 異方性化学エッチングのための大面積測定及び処理制御 - Google Patents

異方性化学エッチングのための大面積測定及び処理制御 Download PDFInfo

- Publication number

- JP7553458B2 JP7553458B2 JP2021549891A JP2021549891A JP7553458B2 JP 7553458 B2 JP7553458 B2 JP 7553458B2 JP 2021549891 A JP2021549891 A JP 2021549891A JP 2021549891 A JP2021549891 A JP 2021549891A JP 7553458 B2 JP7553458 B2 JP 7553458B2

- Authority

- JP

- Japan

- Prior art keywords

- catalyst

- etching

- cice

- etch

- silicon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Classifications

-

- H10P72/0422—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/05—Making the transistor

- H10B12/056—Making the transistor the transistor being a FinFET

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/014—Manufacture or treatment of FETs having zero-dimensional [0D] or one-dimensional [1D] channels, e.g. quantum wire FETs, single-electron transistors [SET] or Coulomb blockade transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/024—Manufacture or treatment of FETs having insulated gates [IGFET] of fin field-effect transistors [FinFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/40—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels

- H10D30/43—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels having 1D charge carrier gas channels, e.g. quantum wire FETs or transistors having 1D quantum-confined channels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/62—Fin field-effect transistors [FinFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/117—Shapes of semiconductor bodies

- H10D62/118—Nanostructure semiconductor bodies

- H10D62/119—Nanowire, nanosheet or nanotube semiconductor bodies

- H10D62/121—Nanowire, nanosheet or nanotube semiconductor bodies oriented parallel to substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/117—Shapes of semiconductor bodies

- H10D62/118—Nanostructure semiconductor bodies

- H10D62/119—Nanowire, nanosheet or nanotube semiconductor bodies

- H10D62/122—Nanowire, nanosheet or nanotube semiconductor bodies oriented at angles to substrates, e.g. perpendicular to substrates

-

- H10P50/242—

-

- H10P50/266—

-

- H10P50/267—

-

- H10P72/0411—

-

- H10P74/203—

-

- H10P74/207—

-

- H10P76/202—

-

- H10P76/403—

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y40/00—Manufacture or treatment of nanostructures

-

- H10P50/644—

-

- H10P50/667—

-

- H10P74/238—

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Weting (AREA)

- Chemical & Material Sciences (AREA)

- General Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Plasma & Fusion (AREA)

- Inorganic Chemistry (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- ing And Chemical Polishing (AREA)

- Sampling And Sample Adjustment (AREA)

Description

本出願は、2019年2月25日に出願された米国仮出願第62/810,070号の優先権を主張するものであり、これは、全ての目的のためにその全体が参照により本明細書に組み込まれる。

本技術の種々の実施形態は、一般に、半導体デバイスアーキテクチャ及び製造技術に関する。より具体的には、本技術のいくつかの実施形態は、異方性化学エッチングのための大面積測定及び処理制御に関する。

本技術の様々な実施形態は、CICEについてパターン化し、触媒をエッチングするために、技術標準処理を用いている。触媒のための処理ウィンドウも、電界を用いて拡張される。検出及び回避処理エクスカーションの方法も列挙されている。

CICEを用いて、バルク物質のナノ構造又は超格子などの物質の交互層を作成することができる。バルク材料のCICEは、finFETやナノワイヤ・センサーのような装置で使用することができる。超格子ナノ構造は、3DのNANDフラッシュメモリ装置及びナノシートトランジスタに応用されている。超格子は、時間的に変化する電場を有するバルク半導体基板上、又はドーピング濃度、物質、ドーパントの種類などが異なる半導体物質の交互の層を有する基板上でCICEを実施することによって作成することができる。定義された形態を有するこれらのナノ構造は、以下に記載されるように、多くの用途に使用され得る。

エッチング深さ、多孔質層厚さ、異方性ならびにエッチングされた構造のエッチング方向は、ウェハ全体にわたって均一でなければならない。均一性を確保するために、CICE処理の様々な構成要素を制御しなければならない。例えば、いくつかの実施形態では、エッチング液濃度は、(a)導電率測定及び/又は(b)屈折率測定の2つの技法を使用して、エッチング液濃度を監視及び制御することによって行うことができる。導電率測定において、フッ化水素酸(HF)は、濃度と導電率との間に線形依存性を有する。屈折率測定では、光学測定システムが、溶液と接触する光学窓を用いて反射型の幾何学的形状を介して屈折率(Rl)を測定し、かくして濁度、回折及び吸収を回避するであろう。さらに、ウェハ全体にわたるエッチング液濃度の均一性を確保するために、ウェハ表面全体にわたるエッチング液の均一な分布のためにディフューザを使用することができ、エッチング液を撹拌するために撹拌機を使用することができ、空気圧ポンプを使用してエッチング中にエッチング液を再循環させることができ、及び/又はウェハチャックを使用してウェハをスピンさせることができる。

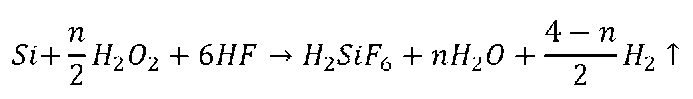

ウェハの両側の電解質は、エッチング液と同じである必要はない。ウェハの前面では、電解質はCICEエッチング液と同じであり、即ち、電解質は、所望の材料(例えば、フッ化物種であるHF、NH4F、緩衝HF、H2SO4、H2O)、酸化剤(H2O2、V2O5、KMn04、溶存酸素など)、アルコール(エタノール、イソプロピルアルコール、エチレングリコール)、エッチング均一性を調節するための材料(界面活性剤、可溶性ポリマー、ジメチルスルホキシド-DMSO)、溶媒(DI水、DMSOなど)、及び緩衝溶液のうちの一以上を含む。

CICE処理の決定的な側面は、エッチング深さの均一性と制御である。CICE中に形成される任意の多孔質層と同様に、エッチ深さは、走査電子顕微鏡(SEM)、透過型電子顕微鏡(TEM)、原子間力顕微鏡(AFM)、光学散乱測定、偏光解析法、小角X線散乱測定、焦点走査光学顕微鏡(TSOM)、ヘリウムイオン顕微鏡、陽子顕微鏡などの多くの破壊的及び非破壊的方法を用いて測定し、特性評価することができる。

基板ドーピング及びドーパント濃度は、CICEでエッチングされた構造の形態を最適化するように選択される。基板は、最適化されたドーピングを有するシリコンの層を含んでもよく、又は基板全体が最適化されたドーピング濃度であってもよい。一実施形態では、基板はドープされていないシリコンである。別の実施形態では、基板は、0.01~0.1Ω・cmの抵抗率を有するリン(P)ドーパントで適度にドープされたn型シリコンである。他の実施形態は、リン及び/又はヒ素ドーパントを有する低濃度ドープn型シリコン、低濃度ドープ、中濃度ドープ、高濃度ドープ、又は縮退ドープされたホウ素ドーパントを有するp型シリコンを含む。リンを軽くドープしたもの、適度にドープしたもの、重くドープしたもの、又は縮退ドープしたものであるリン(P)ドーパントを有するn型シリコン。

CICEは、蒸気状態のエッチング液を用いて行うことができる。気相ベースのCICEのための装置は、局所基板温度の制御のためのサーマルチャックと、エッチング液気相の各成分の気相圧のモニタリングのための手段とを含み得る。電界は、プラズマの形成で印加されてもよい。いくつかの実施形態では、パルスH2O2気相及びHF気相、パルスH2O2液体及びHF液体、パルスH2O2気相及びHF液体、又はパルスH2O2気相及びHF液体を使用することができる。H2O2、プラズマ及びフッ化物イオンの流れ/圧力は、多孔度を交互に変えるために交互にすることができる。多孔質層にはより強い酸化剤を使用し、非多孔質層にはより弱い酸化剤を使用する。気相ベースのCICEのための装置は、気相-HFのような気相エッチングツールに類似している。光学的計測法と共に局所温度制御を備えたサーマルチャックを使用して、気相ベースCICEのためのエッチング深さ変動を制御することができる。

CICEを行うために、Ni、Co、Feなどの磁性材料を触媒に使用することができる。CICEエッチング液に対するそれらの耐性に基づいて、金属は、独立型触媒として使用されてもよく、又はPd、Pt、Au、Ruなどの他の触媒材料に包まれてもよい。磁場を用いて、エッチングが進行するにつれて触媒パターンを方向付けることができ、エッチング深さの変化量を防止することができ、又はエッチング停止方法として機能することができる。

触媒材料のウェハスケールのパターン化は、CICE処理の本質的な側面である。プラズマエッチングや化学エッチングのような典型的なパターン形成方法は、CICEで使用される触媒には適用されない。触媒材料は、典型的には貴金属であり、プラズマエッチングのための揮発性副生成物を形成しない。加えて、そのような金属の化学エッチングは、リソグラフィパターン及び基板材料を侵す可能性がある。様々な実施形態は、触媒パターンを生成するための代替方法を提供する。

触媒材料はシリコン中の深いレベルの欠陥を防ぐためにCMOS互換であるべきである。AuやCuなどの金属を高温で加工すると深準位欠陥が現れる。CICEは室温から低温の処理であるので、このような欠陥の影響は最小限である。触媒は、Au、Ag、Pt、Pd、Ru、Ir、Rh、W、Co、Cu、Al、RuO2、IrO2、TiN、TaN、グラフェン等のうちの一以上とすることができる。CICE処理に対する触媒の効果は、その触媒特性及びエッチング液溶液に対する安定性に基づいて変化する。AuとAgは高い異方性と制御可能な形態(空隙率、細孔サイズ、細孔配向)を実証したが、それらはCMOS互換性がない。Pt及びPdは、匹敵するCICE処理結果を示す。CMOS互換触媒の使用は、CICEによる装置の製造可能性を確保する第一段階である。さらに、CMOS適合性触媒については、堆積及びパターニングは、高い収率を有さなければならない。

触媒として使用される貴金属及び遷移金属は、材料の堆積、フィーチャを規定するためのリソグラフィ、及びリソグラフィパターンを所望の材料に転写するためのプラズマエッチングを含む、従来のCMOSパターニング方法によってパターニングすることができない。これは、触媒が典型的にはプラズマエッチングに必要な揮発性化合物を形成しないからである。さらに、イオンミリング及びプラズマエッチングからの残渣は、フィーチャ内に金属を再堆積させ、デバイスの故障をもたらす可能性がある。

Pt又はPdのような触媒金属の選択的原子層堆積(ALD)は、金属がシリコンと直接接触する領域にのみ堆積されることを確実にするために使用することができる。ネイティブシリコン酸化物を用いて、堆積領域とリソグラフィレジストフィーチャとの間の表面エネルギ勾配を向上することができる。図4は、本技術のいくつかの実施形態による、選択されたALDを使用して触媒をパターン化する際に使用することができる一組の工程の一例を示す処理400を含む。

原子層エッチング

リソグラフィ後に材料をエッチング除去することに基づいて、触媒材料をパターン化可能である。例えば、白金は、210℃を超える温度でPtCl2を形成するためにCl2によるプラズマエッチングを使用してエッチングすることができ、その理由は、PtCl2は、これらの温度で揮発性であり、したがって、堆積及びリソグラフィの後に金属をエッチングする実行可能な方法として使用することができるからである。従来のプラズマエッチングは、触媒材料のいくつかに対して揮発性化合物を生成しないことがあるが、原子層エッチング(ALE)などの他の方法を、リソグラフィされたパターンを破壊しない穏やかなエッチング処理に使用することができる。特に、使用することができる20nm未満のフィーチャサイズについては、ALEを使用することができる。図7は、いくつかの実施形態による、ALEを使用する触媒のパターン化の例を示す処理700を含む。

リフトオフ

触媒は、リフトオフ処理を用いてパターン化することもできる。図8は、処理800を含み、いくつかの実施形態によるリフトオフを使用した触媒のパターン化の例を示す。図8に示す実施形態では、以下のステップが用いられる。処理ステップ805では、リフトオフ層(例えば、PVA、スピンオンガラス、ポリイミドなど)の基板上への堆積を行うことができる。いくつかの実施態様において、基板は、Siウェハであってもよい。Siウェハは、用途に応じて、エピタキシャルドープシリコン層、SiGe層、又は他のタイプの層を含む様々な層を含むことができる。処理ステップ810では、触媒領域がリソグラフィによって画定される。このリソグラフィは、フォトリソグラフィ、インプリントリソグラフィ、EUVリソグラフィ、Litho-Etch-Litho-Etch(LELE)又は他の適用適宜リソグラフィ方法を含むことができる。処理ステップ815に続き、リソグラフィレジストが現像されて、光リソグラフィが可能になる。また、残存層厚のデスカムも発生する可能性がある。リフトオフ層へのパターン転写は、リフトオフ層プロファイルにアンダーカットが存在するように、シリコン基板を露出させるために行うことができる。アンダーカットは、シリコン系のプラズマエッチングを用いてシリコン基板内に形成することもできる。リソグラフィレジストが基板上の適所に置かれると、処理ステップ820において、電子ビーム蒸着、熱蒸着、又は他の適切な方法を利用することによって、触媒材料を方向性をもって堆積させることができる。処理ステップ825において、触媒材料が堆積された後、シリコン基板と直接接触していない領域における触媒材料のリフトオフが起こり得る。いくつかの実施形態では、リフトオフ層を除去するためにウェットエッチングを使用することができる。ステップ830では、CICEが実行され、完了すると、ステップ835で触媒材料を除去することができる。

CICE処理は、触媒材料がシリコンと接触している領域においてのみ、シリコンのような半導体にエッチングされる。この特性は、リフトオフなしにエッチングを実行するために使用することができる。触媒は、リソグラフィ領域及び基板の上部に堆積させることができるが、リフトオフを必要とせずに、基板と接触する領域のみがCICEによってエッチングされる。しかしながら、レジスト、窒化ケイ素、クロム、酸化アルミニウム等のようなリソグラフィされた物質上の触媒もまた、酸化剤還元反応を触媒し、エッチング液の濃度を中断させることがある。これは、追加の触媒作用を考慮してCICEエッチング液を最適化することによって克服することができる。

別の堆積方法は、リソグラフィ後の電着又は無電解堆積によるものであり、金属は、レジスト又は絶縁材料によって覆われていない基板の領域にのみ堆積される。この処理は、Siウェハのような基板を得ることを含み得る。Siウェハは、エピタキシャルドープシリコン層、SiGe層、又は他のタイプの層のような、付加的な応用ベースの層を含むことができる。いったん得られると、表面に電気伝導率を向上するための薄い(10nm以下の)金属層の堆積が起こり得る。金属層は、Ti、TiN、Ta、TaN、W、又は他の特定用途金属もしくは金属化合物のうちの一以上を含むことができる。金属層が堆積されると、PMMA、ポリイミド、又は他の絶縁材料などの追加の絶縁層を堆積することができる。次いで、触媒領域は、リソグラフィ(例えば、フォトリソグラフィ、インプリントリソグラフィ、EUVリソグラフィ、Litho-Etch-Litho-Etch等)を介して画定され得る。次いで、光リソグラフィ用にリソグラフィレジストを開発することができる。あるいは、インプリントリソグラフィのための残留層の厚さの減少が生じてもよい。いったん達成されると、絶縁層へのパターン転写は、金属薄膜(存在する場合)及び/又はシリコン基板を露出するために行われ得る。一旦露出されると、絶縁層材料によって覆われていない領域における触媒金属の選択的電着又は無電解堆積が起こり得る。

触媒除去

CICE処理が完了した後、エッチング液材料は、高アスペクト比構造から完全に洗浄されなければならない。これは、液体の温度を上昇させて、DI水又は低表面張力液体、例えばイソプロピルアルコール又はエタノールなどのリンス媒体との置換を促進することによって行うことができる。これに続いて、エッチングされた高アスペクト比構造の底部にある触媒材料は、エッチングされた構造に影響を及ぼすことなく除去されなければならない。例えば、白金は、シリコン、シリコン酸化物、SiGe、多孔質シリコン、多孔質シリコン酸化物などに影響を与えずにエッチングされなければならない。従って、王水のようなウェットエッチング液は機能しない。プラズマエッチングは、深部及び/又は高いアスペクト比のトレンチの底部に到達する可能性は低く、壊れやすいエッチング構造の横方向エッチングを引き起こす可能性がある。また、プラズマエッチングは、エッチングされた材を再堆積させてもよい。従って、触媒金属を選択的に効果的に除去するためには、原子層エッチング(ALE)が必要である。

高アスペクト比フィーチャの底部への、及び底部からのエッチング液反応物及び生成物のラントスポーツは、CICE中の均一なエッチング、並びにALEを用いたCICE後の触媒材料の除去の両方にとって重要である。ALEの最大アスペクト比と最小フィーチャ寸法は、CICEのアプリケーションに依存する。例えば、1:100のアスペクト比及び10nm未満のフィンハーフピッチを有するfinFET、又は、1:500のアスペクト比及び30nmのフィーチャサイズを有する3DのNANDフラッシュデバイスは、高アスペクト比構造の底部からのエッチング液材料の輸送を可能とするために、追加の処理機能を要求してよい。これは、一以上の方法により達成可能である。例えば、ガス及び/又は基板の温度は上昇される。ガス又は基板の温度がいったん上昇すると、特に100より大きいアスペクト比のサブ50nm孔について、輸送を向上するために、大きな「アクセス孔」が生成される。一実施形態では、アクセス孔によって占有される面積が所望のデバイスの面積の1%を超えないように、エッチングガスの垂直輸送を可能にするために、ミクロンスケールのホールが10ミクロンピッチでパターン化される。他の触媒領域への横方向の輸送は、横方向の多孔質層を使用することによって、及び/又は連結された触媒メッシュ設計を利用することによって達成される。

触媒材料が最終デバイスに関与しない用途では、触媒は、エッチングを使用して除去することができ、又は触媒を絶縁材料内に埋め込んで、触媒がデバイスの性能に影響を及ぼさないことを保証することができる。これは、CICEを使用して、アプリケーションに必要とされるよりも大きな深さにエッチングすることによって達成することができる。次に、過剰な深さを利用して、触媒を隔離する絶縁層を形成する。

3DのNANDなどの用途では、いくつかの実施形態では、多孔質Si又は酸化多孔質Siの交互層を、シリコン層に対して選択的に除去しなければならない。これは、HF気相又はHFとH2O2の溶液を用いて、又はSiO2のALEを用いて行うことができる。いくつかの実施形態では、シリコンの交互層は、タングステン層又は酸化シリコン層に対して選択的に除去されなければならない。これは、SiのALE、TMAH、KOH、EDP、又は他の選択的シリコンエッチング液を使用するエッチングを使用して実行することができる。

CICEのために使用される触媒材料は、触媒活性、粒径、CICEエッチング液に対する耐薬品性、CICE後にパターン化され除去される能力等のような、CICEのための所望のエッチング特性を作り出すように設計された異種材料の合金であってもよい。組合せスパッタ系を用いて合金を堆積することができる。合金は、Au、Ag、Pt、Pd、Ru、Ir、W、TiN、RuO2、IrO2などの活性CICE材料及びMo、C、Cr、金属酸化物、半導体酸化物及び窒化物などの不活性又はエッチング遅延材料を含むであろう。

ナノ構造体の崩壊は、天井及び/又は低い表面エネルギ被覆を用いて、崩壊前のフィーチャ部の臨界高さを増加させることによって防止することができる。天井加工は、プラズマエッチング又はSiSEでフィーチャを短く安定した高さまでエッチングし、天井を堆積させ、SiSE処理を継続することによって行われる。「天井」は、L/2のような短い柱の長さに沿った高さであってもよく、ここでLは短い安定した柱の高さである。これは、フィーチャが更にエッチングされ、短い柱の上部に天井を有するものよりも最大アスペクト比を大きく延長するにつれて、付加的な支持を与える。これは、高アスペクト比ピラーに構造的安定性を与え、崩壊を防止する。

図17は、本技術の種々の実施形態による、シリコン超格子集積スキーム17010の一例を示す。以下に示される導体層は、層の「迷路」部分内の誘電体材料に起因して、増加した抵抗を受ける可能性がある。

文脈がそうでないことを明確に要求しない限り、明細書及び特許請求の範囲を通じて、単語「備える(comprise)」、「備える(comprising)」などは、排他的又は網羅的な意味ではなく、包括的な意味で解釈されるべきであり、つまり、「含むが、限定されない」という意味である。ここで使用されるように、文言「接続された」、「結合された」又はそれらの任意の変形は、2つ以上の要素間の直接又は間接の任意の接続又は結合を意味し、要素間の結合又は接続は、物理的、論理的又はそれらの組み合わせが可能である。加えて、単語「ここで」、「上記」、「以下」及び同様の単語が本明細書で使用される場合、本出願全体を参照し、本出願の任意の特定の部分ではない。上記詳細な説明において単数又は複数で用いられた単語は、文脈が許せば、複数又は単数を含んでよい。単語「又は」は、2以上のアイテムのリストを参照するとき、以下の解釈の全てを包含する:このリスト内のアイテムのいずれか、リスト内のアイテム全て、及び、リスト内のアイテムの任意の組合せ。

Claims (9)

- 触媒影響化学エッチングのための装置であって、

半導体ウェハを収容する処理チャンバと、

前記半導体ウェハ上の一以上の位置の環境特性を制御するように構成された一以上のアクチュエータと、

を備え、

前記触媒影響化学エッチングの現在の状態は、前記半導体ウェハの前面及び背面の一以上の光学的計測法を用いて決定され、

前記触媒影響化学エッチングは、リソグラフィ構造でパターン化された前記半導体ウェハ上で行われ、

前記半導体ウェハの表面は、前記リソグラフィ構造がない領域が曝露され、

前記半導体ウェハ及び前記触媒は、当該装置においてエッチング液にさらされ、

前記触媒は、前記触媒が前記曝露された半導体ウェハの表面の上に堆積された範囲において、前記触媒のみにエッチングが引き起こされる

ことを特徴とする装置。 - 前記一以上のアクチュエータは、温度を制御するように構成されており、

前記一以上のアクチュエータは、溶液を局所的に加熱するために、サーマルチャック、マイクロミラー及び電極の一以上を有する

ことを特徴とする請求項1に記載の装置。 - 前記環境特性は、温度、蒸気圧、電解、エッチング液濃度、エッチング液組成及び照明を含むことを特徴とする請求項1に記載の装置。

- 前記エッチング液は、蒸気状態であることを特徴とする請求項1に記載の装置。

- 前記エッチング液は、液体状態であることを特徴とする請求項1に記載の装置。

- 前記処理チャンバは、前記半導体ウェハの片側又は両側の電極を有することを特徴とする請求項1に記載の装置。

- 前記電極は、前記半導体ウェハの片側又は両側への光を伝搬可能に設計されていることを特徴とする請求項6に記載の装置。

- 前記触媒影響化学エッチングの前記現在の状態は、その場で決定されることを特徴とする請求項1に記載の装置。

- 当該装置は、前記エッチング液を除去するためのすすぎ場を更に備えることを特徴とする請求項1に記載の装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201962810070P | 2019-02-25 | 2019-02-25 | |

| US62/810,070 | 2019-02-25 | ||

| PCT/US2020/019543 WO2020176425A1 (en) | 2019-02-25 | 2020-02-24 | Large area metrology and process control for anisotropic chemical etching |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2022523520A JP2022523520A (ja) | 2022-04-25 |

| JPWO2020176425A5 JPWO2020176425A5 (ja) | 2023-03-06 |

| JP7553458B2 true JP7553458B2 (ja) | 2024-09-18 |

Family

ID=72238704

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021549891A Active JP7553458B2 (ja) | 2019-02-25 | 2020-02-24 | 異方性化学エッチングのための大面積測定及び処理制御 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US20220139717A1 (ja) |

| EP (1) | EP3931863A4 (ja) |

| JP (1) | JP7553458B2 (ja) |

| KR (2) | KR20250128384A (ja) |

| SG (1) | SG11202109293XA (ja) |

| TW (2) | TWI759693B (ja) |

| WO (1) | WO2020176425A1 (ja) |

Families Citing this family (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102731166B1 (ko) | 2018-12-20 | 2024-11-18 | 램 리써치 코포레이션 | 레지스트들의 건식 현상 (dry development) |

| TWI869221B (zh) | 2019-06-26 | 2025-01-01 | 美商蘭姆研究公司 | 利用鹵化物化學品的光阻顯影 |

| EP3780070A1 (en) * | 2019-08-14 | 2021-02-17 | Paul Scherrer Institut | System and etching method for fabricating photonic device elements |

| US11314168B2 (en) | 2020-01-15 | 2022-04-26 | Lam Research Corporation | Underlayer for photoresist adhesion and dose reduction |

| CN115004110A (zh) | 2020-07-07 | 2022-09-02 | 朗姆研究公司 | 用于图案化辐射光致抗蚀剂图案化的集成干燥工艺 |

| US12094691B2 (en) * | 2020-09-30 | 2024-09-17 | Taiwan Semiconductor Manufacturing Co., Ltd. | Etch apparatus for compensating shifted overlayers |

| CN116583932A (zh) * | 2020-10-29 | 2023-08-11 | 德克萨斯大学系统董事会 | 用于受催化剂影响的化学蚀刻的设备和工艺技术 |

| KR20250057101A (ko) | 2020-11-13 | 2025-04-28 | 램 리써치 코포레이션 | 포토레지스트의 건식 제거를 위한 프로세스 툴 |

| KR102870727B1 (ko) * | 2020-12-07 | 2025-10-16 | 삼성전자주식회사 | 반도체 소자 |

| US12406852B2 (en) | 2021-01-21 | 2025-09-02 | Lam Research Corporation | Profile optimization for high aspect ratio memory using an etch front metal catalyst |

| US20220301887A1 (en) * | 2021-03-16 | 2022-09-22 | Applied Materials, Inc. | Ruthenium etching process |

| WO2022216727A1 (en) * | 2021-04-05 | 2022-10-13 | The Board of Trustees of the Leland Stanford Junior University Office of the General Counsel | Ultrahigh aspect ratio nanoporous and nanotextured microstructures with exceptionally high surface area prepared using nanopore-mediated metal-assisted chemical etching |

| CN114229787B (zh) * | 2022-02-23 | 2022-07-08 | 绍兴中芯集成电路制造股份有限公司 | 改善深硅刻蚀晶圆硅柱缺陷的方法、结构及半导体器件 |

| CN114671622B (zh) * | 2022-03-09 | 2024-07-26 | 许昌恒昊光学科技有限公司 | 仿岩石层理交错堆积效果的玻璃蚀刻液及玻璃制作工艺 |

| US20250259852A1 (en) * | 2022-04-07 | 2025-08-14 | Board Of Regents, The University Of Texas System | Tool and processes for electrochemical etching |

| KR102619817B1 (ko) * | 2022-05-19 | 2024-01-02 | 세메스 주식회사 | 반도체 소자의 형성 방법 및 반도체 소자의 형성을 위한 기판 처리 시스템 |

| KR102725782B1 (ko) * | 2022-07-01 | 2024-11-05 | 램 리써치 코포레이션 | 에칭 정지 억제 (etch stop deterrence) 를 위한 금속 옥사이드 기반 포토레지스트의 순환적 현상 |

| CN115360496B (zh) * | 2022-08-30 | 2023-09-29 | 合肥工业大学 | 基于金属辅助化学刻蚀的太赫兹高度差腔体器件的制备方法 |

| CN115424953B (zh) * | 2022-09-21 | 2025-05-02 | 浙江大学 | 一种宽禁带半导体亚表面损伤层厚度的检测方法、装置 |

| KR102808277B1 (ko) * | 2022-09-26 | 2025-05-15 | 세메스 주식회사 | 반도체 소자의 형성 방법 및 반도체 소자의 형성을 위한 기판 처리 시스템 |

| WO2024074929A1 (en) | 2022-10-03 | 2024-04-11 | Rasirc, Inc. | Hydrogen peroxide plasma etch of ashable hard mask |

| WO2024187084A1 (en) * | 2023-03-08 | 2024-09-12 | Board Of Regents, The University Of Texas System | Integrated micro and nanoscale metal assisted chemical etch process with a uniform and clean etch front |

| JP7769144B2 (ja) | 2023-03-17 | 2025-11-12 | ラム リサーチ コーポレーション | Euvパターニングのための乾式現像およびエッチングプロセスの単一プロセスチャンバへの統合 |

| US20240404832A1 (en) * | 2023-06-02 | 2024-12-05 | Taiwan Semiconductor Manufacturing Company Ltd | Wet tool kit for forming semiconductor structure and cmos image sensor employing same |

| WO2025064959A1 (en) * | 2023-09-22 | 2025-03-27 | Mattiq, Inc. | Tunable electron transparent substrates for high-resolution characterization |

| WO2025249178A1 (ja) * | 2024-05-29 | 2025-12-04 | 東京エレクトロン株式会社 | 基板処理方法 |

Citations (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001503571A (ja) | 1997-03-26 | 2001-03-13 | エフエスアイ インターナショナル インコーポレイテッド | 改良されたhfエッチ加工性能のためのイネーブル化化学物質の直接蒸気送達 |

| JP2007200954A (ja) | 2006-01-24 | 2007-08-09 | Osaka Univ | 表面加工方法及び装置 |

| US20100248449A1 (en) | 2009-03-31 | 2010-09-30 | Georgia Tech Research Corporation | Metal-Assisted Chemical Etching of Substrates |

| US20140120723A1 (en) | 2012-10-26 | 2014-05-01 | Xinyu Fu | Methods for depositing fluorine/carbon-free conformal tungsten |

| US20150123249A1 (en) | 2014-01-16 | 2015-05-07 | National Institute Of Standards And Technology | Article with gradient property and processes for selective etching |

| WO2015159973A1 (ja) | 2014-04-18 | 2015-10-22 | 株式会社荏原製作所 | 基板処理装置、基板処理システム、および基板処理方法 |

| JP2015221940A (ja) | 2014-05-09 | 2015-12-10 | ラム リサーチ コーポレーションLam Research Corporation | 塩化タングステン前駆体を使用してタングステンおよび窒化タングステン薄膜を準備する方法 |

| JP2016213385A (ja) | 2015-05-12 | 2016-12-15 | 株式会社東芝 | 半導体チップの製造方法 |

| JP2017028127A (ja) | 2015-07-23 | 2017-02-02 | 株式会社荏原製作所 | 基板処理装置、基板処理システム、および基板処理方法 |

| US20170243751A1 (en) | 2016-02-24 | 2017-08-24 | The Board Of Trustees Of The University Of Illinois | Self-Anchored Catalyst Metal-Assisted Chemical Etching |

| JP2017186595A (ja) | 2016-04-04 | 2017-10-12 | 東京エレクトロン株式会社 | タングステン膜の成膜方法 |

| JP2017222928A (ja) | 2016-05-31 | 2017-12-21 | 東京エレクトロン株式会社 | 表面処理による選択的堆積 |

| JP2018043173A (ja) | 2016-09-12 | 2018-03-22 | 株式会社Screenホールディングス | 犠牲膜形成方法、基板処理方法および基板処理装置 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6246991A (ja) * | 1985-08-21 | 1987-02-28 | Hitachi Ltd | 単結晶成長装置の融液対流制御法 |

| JPH07302896A (ja) * | 1994-04-28 | 1995-11-14 | Ngk Insulators Ltd | 半導体装置およびその製造方法 |

| US6569775B1 (en) * | 1999-03-30 | 2003-05-27 | Applied Materials, Inc. | Method for enhancing plasma processing performance |

| US7265382B2 (en) * | 2002-11-12 | 2007-09-04 | Applied Materials, Inc. | Method and apparatus employing integrated metrology for improved dielectric etch efficiency |

| JP2004327561A (ja) * | 2003-04-22 | 2004-11-18 | Ebara Corp | 基板処理方法及び基板処理装置 |

| US20050148198A1 (en) * | 2004-01-05 | 2005-07-07 | Technion Research & Development Foundation Ltd. | Texturing a semiconductor material using negative potential dissolution (NPD) |

| US7324193B2 (en) * | 2006-03-30 | 2008-01-29 | Tokyo Electron Limited | Measuring a damaged structure formed on a wafer using optical metrology |

| US7927469B2 (en) * | 2006-08-25 | 2011-04-19 | Semitool, Inc. | Electro-chemical processor |

| US7444198B2 (en) * | 2006-12-15 | 2008-10-28 | Applied Materials, Inc. | Determining physical property of substrate |

| US8734661B2 (en) * | 2007-10-15 | 2014-05-27 | Ebara Corporation | Flattening method and flattening apparatus |

| US8951430B2 (en) * | 2012-04-18 | 2015-02-10 | The Board Of Trustees Of The University Of Illinois | Metal assisted chemical etching to produce III-V semiconductor nanostructures |

| US20150376798A1 (en) * | 2013-03-14 | 2015-12-31 | The Board Of Trustees Of The Leland Stanford Junior University | High aspect ratio dense pattern-programmable nanostructures utilizing metal assisted chemical etching |

| US10032681B2 (en) * | 2016-03-02 | 2018-07-24 | Lam Research Corporation | Etch metric sensitivity for endpoint detection |

| US10347497B2 (en) * | 2016-09-23 | 2019-07-09 | The Board Of Trustees Of The University Of Illinois | Catalyst-assisted chemical etching with a vapor-phase etchant |

| SG11202005030XA (en) * | 2017-11-28 | 2020-06-29 | Univ Texas | Catalyst influenced pattern transfer technology |

-

2020

- 2020-02-24 JP JP2021549891A patent/JP7553458B2/ja active Active

- 2020-02-24 SG SG11202109293XA patent/SG11202109293XA/en unknown

- 2020-02-24 US US17/433,777 patent/US20220139717A1/en not_active Abandoned

- 2020-02-24 EP EP20762134.3A patent/EP3931863A4/en active Pending

- 2020-02-24 WO PCT/US2020/019543 patent/WO2020176425A1/en not_active Ceased

- 2020-02-24 KR KR1020257026816A patent/KR20250128384A/ko active Pending

- 2020-02-24 KR KR1020217030604A patent/KR102846785B1/ko active Active

- 2020-02-25 TW TW109105957A patent/TWI759693B/zh active

- 2020-02-25 TW TW111106278A patent/TWI815315B/zh active

Patent Citations (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001503571A (ja) | 1997-03-26 | 2001-03-13 | エフエスアイ インターナショナル インコーポレイテッド | 改良されたhfエッチ加工性能のためのイネーブル化化学物質の直接蒸気送達 |

| JP2007200954A (ja) | 2006-01-24 | 2007-08-09 | Osaka Univ | 表面加工方法及び装置 |

| US20100248449A1 (en) | 2009-03-31 | 2010-09-30 | Georgia Tech Research Corporation | Metal-Assisted Chemical Etching of Substrates |

| US20140120723A1 (en) | 2012-10-26 | 2014-05-01 | Xinyu Fu | Methods for depositing fluorine/carbon-free conformal tungsten |

| US20150123249A1 (en) | 2014-01-16 | 2015-05-07 | National Institute Of Standards And Technology | Article with gradient property and processes for selective etching |

| WO2015159973A1 (ja) | 2014-04-18 | 2015-10-22 | 株式会社荏原製作所 | 基板処理装置、基板処理システム、および基板処理方法 |

| JP2015221940A (ja) | 2014-05-09 | 2015-12-10 | ラム リサーチ コーポレーションLam Research Corporation | 塩化タングステン前駆体を使用してタングステンおよび窒化タングステン薄膜を準備する方法 |

| JP2016213385A (ja) | 2015-05-12 | 2016-12-15 | 株式会社東芝 | 半導体チップの製造方法 |

| JP2017028127A (ja) | 2015-07-23 | 2017-02-02 | 株式会社荏原製作所 | 基板処理装置、基板処理システム、および基板処理方法 |

| US20170243751A1 (en) | 2016-02-24 | 2017-08-24 | The Board Of Trustees Of The University Of Illinois | Self-Anchored Catalyst Metal-Assisted Chemical Etching |

| JP2017186595A (ja) | 2016-04-04 | 2017-10-12 | 東京エレクトロン株式会社 | タングステン膜の成膜方法 |

| JP2017222928A (ja) | 2016-05-31 | 2017-12-21 | 東京エレクトロン株式会社 | 表面処理による選択的堆積 |

| JP2018043173A (ja) | 2016-09-12 | 2018-03-22 | 株式会社Screenホールディングス | 犠牲膜形成方法、基板処理方法および基板処理装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20220139717A1 (en) | 2022-05-05 |

| TW202105559A (zh) | 2021-02-01 |

| TWI759693B (zh) | 2022-04-01 |

| TW202226423A (zh) | 2022-07-01 |

| SG11202109293XA (en) | 2021-09-29 |

| WO2020176425A1 (en) | 2020-09-03 |

| TWI815315B (zh) | 2023-09-11 |

| EP3931863A4 (en) | 2023-04-26 |

| JP2022523520A (ja) | 2022-04-25 |

| EP3931863A1 (en) | 2022-01-05 |

| KR20250128384A (ko) | 2025-08-27 |

| KR20210142118A (ko) | 2021-11-24 |

| KR102846785B1 (ko) | 2025-08-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7553458B2 (ja) | 異方性化学エッチングのための大面積測定及び処理制御 | |

| JP7655989B2 (ja) | 触媒促進パターン転写技術 | |

| US8980656B2 (en) | Method of forming an array of high aspect ratio semiconductor nanostructures | |

| US8193095B2 (en) | Method for forming silicon trench | |

| TWI501043B (zh) | 在基板上形成圖案的方法 | |

| US9595471B2 (en) | Conductive element structure and method | |

| US20160133478A1 (en) | Methods for etching substrate and semiconductor devices | |

| EP3153463A1 (en) | Method for producing a pillar structure in a semiconductor layer | |

| Mallavarapu et al. | Scalable fabrication and metrology of silicon nanowire arrays made by metal assisted chemical etch | |

| Lee et al. | Silicon etching using Copper–Metal-Assisted chemical etching: unveiling the role of Cu2O in microscale structure fabrication | |

| TWI862793B (zh) | 使用原子層蝕刻以形成半導體特徵部 | |

| CN110350029B (zh) | 晶体管及其制造方法 | |

| Adam et al. | Material engineering for nano structure formation: fabrication and characterization | |

| Castaneda | Effect of thermal oxide film on scalable fabrication of silicon nanowire arrays using Metal Assisted Chemical Etching | |

| US20250218861A1 (en) | Semiconductor device with catalytic conductive layer and method for fabricating the same | |

| Dreeskornfeld et al. | Comparison of trimming techniques for sub-lithographic silicon structures | |

| Banerjee et al. | Akhila Mallavarapu |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20211104 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230222 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240220 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20240221 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240520 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20240806 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20240905 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7553458 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |