JP7401050B2 - バス制御回路 - Google Patents

バス制御回路 Download PDFInfo

- Publication number

- JP7401050B2 JP7401050B2 JP2018174191A JP2018174191A JP7401050B2 JP 7401050 B2 JP7401050 B2 JP 7401050B2 JP 2018174191 A JP2018174191 A JP 2018174191A JP 2018174191 A JP2018174191 A JP 2018174191A JP 7401050 B2 JP7401050 B2 JP 7401050B2

- Authority

- JP

- Japan

- Prior art keywords

- bus

- information

- transfer

- route

- switch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000011144 upstream manufacturing Methods 0.000 claims description 4

- 101710176296 Switch 2 Proteins 0.000 description 14

- 238000010586 diagram Methods 0.000 description 12

- 238000000034 method Methods 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- 230000006870 function Effects 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 230000006399 behavior Effects 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 230000001934 delay Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/36—Handling requests for interconnection or transfer for access to common bus or bus system

- G06F13/368—Handling requests for interconnection or transfer for access to common bus or bus system with decentralised access control

- G06F13/374—Handling requests for interconnection or transfer for access to common bus or bus system with decentralised access control using a self-select method with individual priority code comparator

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/382—Information transfer, e.g. on bus using universal interface adapter

- G06F13/385—Information transfer, e.g. on bus using universal interface adapter for adaptation of a particular data processing system to different peripheral devices

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/36—Handling requests for interconnection or transfer for access to common bus or bus system

- G06F13/362—Handling requests for interconnection or transfer for access to common bus or bus system with centralised access control

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/10—Program control for peripheral devices

- G06F13/12—Program control for peripheral devices using hardware independent of the central processor, e.g. channel or peripheral processor

- G06F13/124—Program control for peripheral devices using hardware independent of the central processor, e.g. channel or peripheral processor where hardware is a sequential transfer control unit, e.g. microprocessor, peripheral processor or state-machine

- G06F13/126—Program control for peripheral devices using hardware independent of the central processor, e.g. channel or peripheral processor where hardware is a sequential transfer control unit, e.g. microprocessor, peripheral processor or state-machine and has means for transferring I/O instructions and statuses between control unit and main processor

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/1668—Details of memory controller

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/16—Handling requests for interconnection or transfer for access to memory bus

- G06F13/18—Handling requests for interconnection or transfer for access to memory bus based on priority control

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/36—Handling requests for interconnection or transfer for access to common bus or bus system

- G06F13/368—Handling requests for interconnection or transfer for access to common bus or bus system with decentralised access control

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/40—Bus structure

- G06F13/4004—Coupling between buses

- G06F13/4022—Coupling between buses using switching circuits, e.g. switching matrix, connection or expansion network

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F5/00—Methods or arrangements for data conversion without changing the order or content of the data handled

- G06F5/06—Methods or arrangements for data conversion without changing the order or content of the data handled for changing the speed of data flow, i.e. speed regularising or timing, e.g. delay lines, FIFO buffers; over- or underrun control therefor

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Mathematical Physics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Bus Control (AREA)

Description

複数のバスマスタとスレーブモジュールとのバスの接続を制御するバス制御回路であって、

前記複数のバスマスタに接続され、前記複数のバスマスタそれぞれからのバス転送要求信号を受信し、予め設定された優先順位に従ってバス転送要求信号を発行した前記複数のバスマスタの内の1つに対するバス権を付与することを示す調停結果信号を出力する単一の調停回路と、

複数のバススイッチとを有し、

前記複数のバススイッチそれぞれは、

複数のバス転送信号を受信するための複数の入力端子、および、前記複数の入力端子のうちの1つバス転送信号を下流に伝達するための出力端子とを有する選択回路と、

前記調停回路が出力する前記調停結果信号を受信し、当該調停結果信号に基づいて前記選択回路に対して前記複数の入力端子のいずれか1つを選択するよう制御する制御回路とを有し、

前記複数のバススイッチの少なくともいずれか1つが有する前記複数の入力端子に、上流のバススイッチの出力端子および前記複数のバスマスタの少なくともいずれか1つが接続され、

最下流に位置するバススイッチが有する前記選択回路の出力端子に前記スレーブモジュールが接続されることを特徴とする。

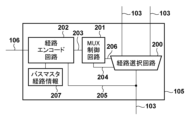

図1は、第1の実施形態におけるバス制御回路を搭載するバスシステムの構成図である。図1に例示するバスシステムは8つのバスマスタモジュール101と、1つのスレーブモジュール102で構成されるバスシステムである。なお、バスマスタモジュール、スレーブモジュールの数に特に制限はなく、あくまで例示であると理解されたい。

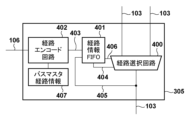

図3は第2の実施形態を示すバスシステムの構成図である。図3に例示するバスシステムは8つのバスマスタモジュール101と1つのスレーブモジュール102で構成されるバスシステムである。バスマスタモジュール101はバス転送要求信号104とバス転送信号103を出力する。

第1、第2の実施形態は、バスマスタモジュールからバススレーブモジュールへの経路でアドレス情報とデータ情報を同一経路で伝達する構成を示しているが、アドレス情報とデータ情報を独立に転送する構成にも適用可能である。すなわち、アドレス情報バスとデータ情報バスが独立に構成される形式に適用可能である。本構成では、バスマスタモジュール101はバス転送要求信号104とともにバス転送方向情報を調停回路100(又は300)に通知する。調停回路100(又は300)は調停結果信号106とともに、当該転送のバス転送方向情報をバススイッチ回路105(又は305)に伝達される。バススイッチ回路はアドレス情報を伝達するバススイッチとデータ情報を伝達するバススイッチが独立して構成される。データ情報を伝達するバススイッチは、調停結果信号106とともに伝達されるバス転送方向情報を参照し、書き込み転送である場合のみバススイッチの経路情報に変換することにより実現される。

Claims (5)

- 複数のバスマスタとスレーブモジュールとのバスの接続を制御するバス制御回路であって、

前記複数のバスマスタに接続され、前記複数のバスマスタそれぞれからのバス転送要求信号を受信し、予め設定された優先順位に従ってバス転送要求信号を発行した前記複数のバスマスタの内の1つに対するバス権を付与することを示す調停結果信号を出力する単一の調停回路と、

複数のバススイッチとを有し、

前記複数のバススイッチそれぞれは、

複数のバス転送信号を受信するための複数の入力端子、および、前記複数の入力端子のうちの1つバス転送信号を下流に伝達するための出力端子とを有する選択回路と、

前記調停回路が出力する前記調停結果信号を受信し、当該調停結果信号に基づいて前記選択回路に対して前記複数の入力端子のいずれか1つを選択するよう制御する制御回路とを有し、

前記複数のバススイッチの少なくともいずれか1つが有する前記複数の入力端子に、上流のバススイッチの出力端子および前記複数のバスマスタの少なくともいずれか1つが接続され、

最下流に位置するバススイッチが有する前記選択回路の出力端子に前記スレーブモジュールが接続される

ことを特徴とするバス制御回路。 - 前記制御回路は、前記調停結果信号をバススイッチの経路情報に変換し、切替選択信号として保持するメモリを有することを特徴とする請求項1に記載のバス制御回路。

- 前記制御回路が有する前記メモリは、前記単一の調停回路が前記調停結果信号を出力したサイクルにおいて前記切替選択信号をFIFO形式で保持し、前記制御回路は、前記切替選択信号を保持された順に用いて、前記選択回路に対して前記複数の入力端子のいずれか1つを選択し、前記調停結果信号に対応するバス転送要求信号の最終転送がなされたサイクルで、前記調停結果信号に対応する前記切替選択信号を削除するよう制御することを特徴とする請求項2に記載のバス制御回路。

- 前記バススイッチは、アドレス情報バスを伝達するスイッチと、データ情報バスを伝達するスイッチを有することを特徴とする請求項1乃至3のいずれか1項に記載のバス制御回路。

- 前記調停回路は、前記複数のバスマスタから、前記バス転送要求信号とともにバス転送方向を示す情報を更に受信し、バス権を与えるとして決定したバスマスタからのバス転送方向を示す情報を前記調停結果信号とともに出力し、

前記制御回路は、前記バス転送方向を示す情報を参照し、前記調停結果信号を、バススイッチの経路情報に変換し、切替選択信号として保持するメモリを有することを特徴とする請求項1乃至4のいずれか1項に記載のバス制御回路。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018174191A JP7401050B2 (ja) | 2018-09-18 | 2018-09-18 | バス制御回路 |

| EP19193097.3A EP3627331B1 (en) | 2018-09-18 | 2019-08-22 | Bus control circuit |

| US16/561,328 US10872051B2 (en) | 2018-09-18 | 2019-09-05 | Bus control circuit |

| KR1020190111857A KR102549085B1 (ko) | 2018-09-18 | 2019-09-10 | 버스 제어회로 |

| CN201910880361.2A CN110908936B (zh) | 2018-09-18 | 2019-09-18 | 总线控制电路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018174191A JP7401050B2 (ja) | 2018-09-18 | 2018-09-18 | バス制御回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2020046876A JP2020046876A (ja) | 2020-03-26 |

| JP2020046876A5 JP2020046876A5 (ja) | 2021-10-21 |

| JP7401050B2 true JP7401050B2 (ja) | 2023-12-19 |

Family

ID=67734547

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018174191A Active JP7401050B2 (ja) | 2018-09-18 | 2018-09-18 | バス制御回路 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10872051B2 (ja) |

| EP (1) | EP3627331B1 (ja) |

| JP (1) | JP7401050B2 (ja) |

| KR (1) | KR102549085B1 (ja) |

| CN (1) | CN110908936B (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN111752875A (zh) * | 2020-06-22 | 2020-10-09 | 深圳鲲云信息科技有限公司 | 一种模块间通信方法及系统 |

| CN113158260B (zh) * | 2021-03-30 | 2023-03-31 | 西南电子技术研究所(中国电子科技集团公司第十研究所) | SoC芯片内部数据分级防护电路 |

| CN113507283B (zh) * | 2021-07-02 | 2024-10-15 | 北京青鸟环宇消防系统软件服务有限公司 | 无极性总线隔离开关 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005062946A (ja) | 2003-08-12 | 2005-03-10 | Fuji Xerox Co Ltd | メモリ制御装置 |

| JP2008117068A (ja) | 2006-11-01 | 2008-05-22 | Denso Corp | 情報処理システム |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5887134A (en) * | 1997-06-30 | 1999-03-23 | Sun Microsystems | System and method for preserving message order while employing both programmed I/O and DMA operations |

| US6243829B1 (en) * | 1998-05-27 | 2001-06-05 | Hewlett-Packard Company | Memory controller supporting redundant synchronous memories |

| US6323755B1 (en) * | 1998-08-19 | 2001-11-27 | International Business Machines Corporation | Dynamic bus locking in a cross bar switch |

| US6842104B1 (en) * | 1999-03-19 | 2005-01-11 | Matsushita Electric Industrial Co., Ltd. | System lsi and a cross-bus switch apparatus achieved in a plurality of circuits in which two or more pairs of a source apparatus and a destination apparatus are connected simultaneously and buses are wired without concentration |

| US7376811B2 (en) * | 2001-11-06 | 2008-05-20 | Netxen, Inc. | Method and apparatus for performing computations and operations on data using data steering |

| KR100618817B1 (ko) * | 2003-12-17 | 2006-08-31 | 삼성전자주식회사 | 소비 전력을 절감시키는 amba 버스 구조 시스템 및 그방법 |

| US7395361B2 (en) * | 2005-08-19 | 2008-07-01 | Qualcomm Incorporated | Apparatus and methods for weighted bus arbitration among a plurality of master devices based on transfer direction and/or consumed bandwidth |

| US7302510B2 (en) * | 2005-09-29 | 2007-11-27 | International Business Machines Corporation | Fair hierarchical arbiter |

| US20080059674A1 (en) * | 2006-09-01 | 2008-03-06 | Jiaxiang Shi | Apparatus and method for chained arbitration of a plurality of inputs |

| US20080082707A1 (en) * | 2006-09-29 | 2008-04-03 | Synfora, Inc. | Non-blocking bus controller for a pipelined, variable latency, hierarchical bus with point-to-point first-in first-out ordering |

| US7734856B2 (en) * | 2007-08-22 | 2010-06-08 | Lantiq Deutschland Gmbh | Method for operating a plurality of arbiters and arbiter system |

| JP5035469B2 (ja) * | 2009-03-31 | 2012-09-26 | 富士通株式会社 | データ転送回路及びデータ転送方法 |

| JP2010282405A (ja) | 2009-06-04 | 2010-12-16 | Renesas Electronics Corp | データ処理システム |

| US8972821B2 (en) * | 2010-12-23 | 2015-03-03 | Texas Instruments Incorporated | Encode and multiplex, register, and decode and error correction circuitry |

| JP5776306B2 (ja) * | 2011-04-25 | 2015-09-09 | 富士ゼロックス株式会社 | 画像データ処理装置及びプログラム |

| US9117022B1 (en) * | 2011-10-07 | 2015-08-25 | Altera Corporation | Hierarchical arbitration |

| US8874680B1 (en) * | 2011-11-03 | 2014-10-28 | Netapp, Inc. | Interconnect delivery process |

| US9176911B2 (en) * | 2012-12-11 | 2015-11-03 | Intel Corporation | Explicit flow control for implicit memory registration |

| CN106301337B (zh) * | 2015-05-13 | 2019-12-06 | 恩智浦有限公司 | 双向通信的方法和系统 |

| GB2557225A (en) * | 2016-11-30 | 2018-06-20 | Nordic Semiconductor Asa | Interconnect system |

-

2018

- 2018-09-18 JP JP2018174191A patent/JP7401050B2/ja active Active

-

2019

- 2019-08-22 EP EP19193097.3A patent/EP3627331B1/en active Active

- 2019-09-05 US US16/561,328 patent/US10872051B2/en active Active

- 2019-09-10 KR KR1020190111857A patent/KR102549085B1/ko active IP Right Grant

- 2019-09-18 CN CN201910880361.2A patent/CN110908936B/zh active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005062946A (ja) | 2003-08-12 | 2005-03-10 | Fuji Xerox Co Ltd | メモリ制御装置 |

| JP2008117068A (ja) | 2006-11-01 | 2008-05-22 | Denso Corp | 情報処理システム |

Also Published As

| Publication number | Publication date |

|---|---|

| KR102549085B1 (ko) | 2023-06-29 |

| CN110908936B (zh) | 2023-09-05 |

| CN110908936A (zh) | 2020-03-24 |

| JP2020046876A (ja) | 2020-03-26 |

| EP3627331B1 (en) | 2024-01-03 |

| KR20200032642A (ko) | 2020-03-26 |

| US20200089635A1 (en) | 2020-03-19 |

| EP3627331A1 (en) | 2020-03-25 |

| US10872051B2 (en) | 2020-12-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP1239374B1 (en) | Shared program memory for use in multicore DSP devices | |

| EP1775897B1 (en) | Interleaving in a NoC (Network on Chip) employing the AXI protocol | |

| JP7401050B2 (ja) | バス制御回路 | |

| US20050188144A1 (en) | Protocol conversion and arbitration circuit, system having the same, and method for converting and arbitrating signals | |

| JP3807250B2 (ja) | クラスタシステム、コンピュータ及びプログラム | |

| EP2312457B1 (en) | Data processing apparatus, data processing method and computer-readable medium | |

| KR101699784B1 (ko) | 버스 시스템 및 그것의 동작 방법 | |

| US8583845B2 (en) | Multi-processor system and controlling method thereof | |

| JPH0981508A (ja) | 通信方法及び装置 | |

| JP2008310832A (ja) | 高レベル・データ・リンク・コントローラから多数個のディジタル信号プロセッサ・コアに信号を分配するための装置と方法 | |

| US9003092B2 (en) | System on chip bus system and a method of operating the bus system | |

| KR20020008955A (ko) | 버스 시스템 및 그 실행 순서 조정방법 | |

| US8352695B2 (en) | Selectable access rates in a memory and memory communication system | |

| US6801978B2 (en) | Crossbar system with increased throughput | |

| US7032061B2 (en) | Multimaster bus system | |

| US7519848B2 (en) | Data transfer apparatus | |

| US20030093594A1 (en) | Apparatus and method for controlling block signal flow in a multi digital signal processor configuration from a shared peripheral direct memory controller to high level data link controller | |

| US10032119B1 (en) | Ordering system that employs chained ticket release bitmap block functions | |

| US6499080B1 (en) | Post write buffer for a dual clock system | |

| KR100737904B1 (ko) | 마스터/슬레이브 디바이스간의 인터페이스 장치 및 그 방법 | |

| KR20000033265A (ko) | 칩 내장형 버스를 인터페이스하기 위한 장치 및 방법 | |

| JPH09128327A (ja) | バス調停回路 | |

| JPH10289191A (ja) | データ転送装置およびデータ転送システム | |

| JPH09231188A (ja) | マルチクラスタ情報処理システム | |

| JPH05265671A (ja) | ポート自動切換装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20210103 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210113 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210906 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210906 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20220428 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220523 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220721 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20221205 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230303 |

|

| C60 | Trial request (containing other claim documents, opposition documents) |

Free format text: JAPANESE INTERMEDIATE CODE: C60 Effective date: 20230303 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20230313 |

|

| C21 | Notice of transfer of a case for reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C21 Effective date: 20230317 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20230519 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20231124 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 7401050 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |