JP7232001B2 - 撮像素子及びその制御方法、プログラム、記憶媒体 - Google Patents

撮像素子及びその制御方法、プログラム、記憶媒体 Download PDFInfo

- Publication number

- JP7232001B2 JP7232001B2 JP2018158571A JP2018158571A JP7232001B2 JP 7232001 B2 JP7232001 B2 JP 7232001B2 JP 2018158571 A JP2018158571 A JP 2018158571A JP 2018158571 A JP2018158571 A JP 2018158571A JP 7232001 B2 JP7232001 B2 JP 7232001B2

- Authority

- JP

- Japan

- Prior art keywords

- pixels

- output

- imaging device

- value

- counting means

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

図1は、本発明の第1の実施形態における撮像素子300の構成を示す図である。撮像素子300は、単位画素100が2次元状に多数配置されているが、説明を分かりやすくするために、図1では3個×3個の単位画素100が配列されているものとして説明する。

第1の実施形態では、各単位画素の記憶素子であるフリップフロップ間をシフトレジスタのように配置し、カウンタ同士を接続することにより、配線及び制御線を簡略化する構成について説明した。しかしながら、全ての単位画素のカウンタ同士を接続する構成にしなければ効果がないわけではない。第2の実施形態では、一部の単位画素間のカウンタ同士を接続する構成とした場合の撮像素子の構造について説明する。

第1及び第2の実施形態では、初期値データRESET_VALUEを一律な固定値の0とし、計数を開始する前にロードする方法について説明した。しかしながら、初期値は固定値とする必要はない。例えばあらかじめ各画素単位に初期値を個別に設定することにより、画素値のOBクランプ補正や画素ごとのリミッタ処理に活用することが可能となる。

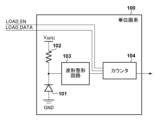

出力CNT00の値は、時刻t805までの撮像期間の間、APD101に光子が1個入射するごとに1ずつ増加する。出力CNT01からCNT22においても対応する画素のAPD101の変化によって同様の処理が行われる。

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサーがプログラムを読出し実行する処理でも実現可能である。また、1以上の機能を実現する回路(例えば、ASIC)によっても実現可能である。

Claims (9)

- 光を受光する受光部と、該受光部に入射した光子の数を計数する計数手段と、をそれぞれ有する複数の画素と、

前記画素の信号の初期値を生成する初期化信号生成手段と、

を備え、

前記複数の画素の少なくとも一部の画素について、該少なくとも一部の画素のそれぞれが有する前記計数手段同士が接続され、接続された複数の計数手段のうちの最初の計数手段に前記初期化信号生成手段が接続されていることを特徴とする撮像素子。 - 前記計数手段は、前記受光部が光子の入射に伴って発生する電荷に基づいてパルスを発生する発生手段と、該発生手段が発生したパルスを計数するカウンタとを有することを特徴とする請求項1に記載の撮像素子。

- 前記計数手段は、前記画素からの信号の読み出し制御、もしくは前記画素のリセット制御において、シフトレジスタ動作を行うことを特徴とする請求項1または2に記載の撮像素子。

- 前記初期化信号生成手段は、一律の固定値を出力することを特徴とする請求項1乃至3のいずれか1項に記載の撮像素子。

- 前記初期化信号生成手段は、画素ごとに個別の値を出力することを特徴とする請求項1乃至3のいずれか1項に記載の撮像素子。

- 前記撮像素子の偶数行の画素に対応する計数手段同士が接続され、奇数行の画素に対応する計数手段同士が接続されることを特徴とする請求項1乃至5のいずれか1項に記載の撮像素子。

- 前記撮像素子の偶数列の画素に対応する計数手段同士が接続され、奇数列の画素に対応する計数手段同士が接続されることを特徴とする請求項1乃至5のいずれか1項に記載の撮像素子。

- 前記受光部は、1つのマイクロレンズの下に射出瞳を分割する少なくとも2つの副画素を有することを特徴とする請求項1乃至5のいずれか1項に記載の撮像素子。

- 前記複数の画素のうちの間引いて読み出される画素に対応したそれぞれの計数手段同士が接続されることを特徴とする請求項1乃至5のいずれか1項に記載の撮像素子。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018158571A JP7232001B2 (ja) | 2018-08-27 | 2018-08-27 | 撮像素子及びその制御方法、プログラム、記憶媒体 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018158571A JP7232001B2 (ja) | 2018-08-27 | 2018-08-27 | 撮像素子及びその制御方法、プログラム、記憶媒体 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2020036092A JP2020036092A (ja) | 2020-03-05 |

| JP2020036092A5 JP2020036092A5 (ja) | 2021-09-24 |

| JP7232001B2 true JP7232001B2 (ja) | 2023-03-02 |

Family

ID=69668759

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018158571A Active JP7232001B2 (ja) | 2018-08-27 | 2018-08-27 | 撮像素子及びその制御方法、プログラム、記憶媒体 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP7232001B2 (ja) |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001502424A (ja) | 1996-10-15 | 2001-02-20 | シマゲ オユ | 放射線撮像のための撮像素子 |

-

2018

- 2018-08-27 JP JP2018158571A patent/JP7232001B2/ja active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001502424A (ja) | 1996-10-15 | 2001-02-20 | シマゲ オユ | 放射線撮像のための撮像素子 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2020036092A (ja) | 2020-03-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11457168B2 (en) | Image sensor and image capturing apparatus | |

| US9369650B2 (en) | Imaging device and camera system with photosensitive conversion element | |

| US8259206B1 (en) | Solid-state imaging apparatus | |

| JP5304410B2 (ja) | Ad変換装置、固体撮像素子、およびカメラシステム | |

| US8111309B2 (en) | Solid-state image pickup device and signal processing method using solid-state image pickup device | |

| US9723237B2 (en) | Imaging device and camera system with photosensitive conversion element | |

| US8203634B2 (en) | Physical quantity detecting device, solid-state imaging device, and imaging apparatus | |

| JP2013070240A5 (ja) | ||

| KR20070099479A (ko) | 물리량 분포 검출 장치 및 촬상 장치 | |

| JP2011205512A5 (ja) | ||

| US8665354B2 (en) | Solid-state image pickup device | |

| CN111133750A (zh) | 图像传感器和摄像设备 | |

| JP2015056902A (ja) | Cmos固体撮像素子及び圧縮センシング方法 | |

| US9448109B2 (en) | Analog-to-digital conversion circuit, imaging apparatus and imaging system | |

| JP2019140537A (ja) | 固体撮像素子、撮像装置及び撮像方法 | |

| JP5400428B2 (ja) | 撮像装置、撮像素子およびその駆動方法 | |

| JP7232001B2 (ja) | 撮像素子及びその制御方法、プログラム、記憶媒体 | |

| KR101512810B1 (ko) | 오버샘플링을 통한 비닝을 지원하는 이미지 센서의 구동 회로 및 방법 | |

| JP7292135B2 (ja) | 撮像素子及び撮像装置 | |

| JP2012175690A (ja) | 固体撮像素子 | |

| JP7277242B2 (ja) | 撮像装置およびその制御方法 | |

| JP7344045B2 (ja) | 撮像素子 | |

| KR101738694B1 (ko) | 엑스선 이미지 센서 시스템용 병렬 처리 독출 회로 및 독출 방법 | |

| JP2020170970A (ja) | 撮像装置およびその制御方法 | |

| JP2016010050A (ja) | 画素回路およびこれを搭載した撮像装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20210103 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210113 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210812 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210812 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20220721 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220801 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220928 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230120 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230217 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 7232001 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |