JP7217153B2 - 情報処理装置、時刻同期方法、及び時刻同期プログラム - Google Patents

情報処理装置、時刻同期方法、及び時刻同期プログラム Download PDFInfo

- Publication number

- JP7217153B2 JP7217153B2 JP2019002774A JP2019002774A JP7217153B2 JP 7217153 B2 JP7217153 B2 JP 7217153B2 JP 2019002774 A JP2019002774 A JP 2019002774A JP 2019002774 A JP2019002774 A JP 2019002774A JP 7217153 B2 JP7217153 B2 JP 7217153B2

- Authority

- JP

- Japan

- Prior art keywords

- time

- information

- difference

- system time

- sensor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04L—TRANSMISSION OF DIGITAL INFORMATION, e.g. TELEGRAPHIC COMMUNICATION

- H04L7/00—Arrangements for synchronising receiver with transmitter

- H04L7/04—Speed or phase control by synchronisation signals

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q9/00—Arrangements in telecontrol or telemetry systems for selectively calling a substation from a main station, in which substation desired apparatus is selected for applying a control signal thereto or for obtaining measured values therefrom

- H04Q9/04—Arrangements for synchronous operation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04J—MULTIPLEX COMMUNICATION

- H04J3/00—Time-division multiplex systems

- H04J3/02—Details

- H04J3/06—Synchronising arrangements

- H04J3/0635—Clock or time synchronisation in a network

- H04J3/0638—Clock or time synchronisation among nodes; Internode synchronisation

- H04J3/0658—Clock or time synchronisation among packet nodes

- H04J3/0661—Clock or time synchronisation among packet nodes using timestamps

- H04J3/0664—Clock or time synchronisation among packet nodes using timestamps unidirectional timestamps

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N21/00—Selective content distribution, e.g. interactive television or video on demand [VOD]

- H04N21/20—Servers specifically adapted for the distribution of content, e.g. VOD servers; Operations thereof

- H04N21/21—Server components or server architectures

- H04N21/218—Source of audio or video content, e.g. local disk arrays

- H04N21/2187—Live feed

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N21/00—Selective content distribution, e.g. interactive television or video on demand [VOD]

- H04N21/20—Servers specifically adapted for the distribution of content, e.g. VOD servers; Operations thereof

- H04N21/23—Processing of content or additional data; Elementary server operations; Server middleware

- H04N21/242—Synchronization processes, e.g. processing of PCR [Program Clock References]

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04Q—SELECTING

- H04Q2209/00—Arrangements in telecontrol or telemetry systems

- H04Q2209/80—Arrangements in the sub-station, i.e. sensing device

- H04Q2209/84—Measuring functions

- H04Q2209/845—Measuring functions where the measuring is synchronized between sensing devices

Landscapes

- Engineering & Computer Science (AREA)

- Computer Networks & Wireless Communication (AREA)

- Signal Processing (AREA)

- Synchronisation In Digital Transmission Systems (AREA)

- Telephonic Communication Services (AREA)

- Electric Clocks (AREA)

- Selective Calling Equipment (AREA)

Description

図2は、データにタイムスタンプを付加するFPGAの第1の比較例を示している。図2のFPGA201は、割り込みコントローラ211、MMIO(Memory-mapped Input Output)レジスタ212、及び検出部213を含む。

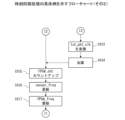

FPGA_freq

=Sub出力/(current_time-last_time) (1)

カウンタ1203 00000

レジスタ1204 10000

current_time 15:00:10

last_time 15:00:05

FPGA_freq=10000/(10-5)=2000[Hz] (2)

カウンタ1203 00000

レジスタ1204 11000

current_time 15:00:16

last_time 15:00:10

FPGA_freq=11000/(16-10)=1833[Hz] (3)

sensor_freq

={(sensor_cur_clk-sensor_last_clk)

/(FPGA_cur_clk-FPGA_last_clk)}

*FPGA_freq (4)

sensor_cnt=1010

FPGA_cur_clk=2050

FPGA_freq=2000

sensor_cnt=1050

FPGA_cur_clk=2071

FPGA_last_clk=2050

sensor_cur_clk=1050

sensor_last_clk=1010

FPGA_freq=2000

sensor_freq

={(1050-1010)/(2071-2050)}*2000

=3810[Hz] (5)

sensor_cnt=1150

FPGA_cur_clk=2125

FPGA_last_clk=2071

sensor_cur_clk=1150

sensor_last_clk=1050

FPGA_freq=2000

sensor_freq

={(1150-1050)/(2125-2071)}*2000

=3704[Hz] (6)

Real_time

=(cur_pkt_cnt-1st_pkt_cnt)/sensor_freq

+1st_pkt_clk/FPGA_freq+OS_time

(7)

1st_pkt_clk=0

first_pktflag=0

FPGA_freq=2000

sensor_freq=4000

sensor_cnt=1010

1st_pkt_clk=50

first_pktflag=1

1st_pkt_cnt=1010

cur_pkt_cnt=1010

FPGA_freq=2000

sensor_freq=4000

Real_time

=(1010-1010)/4000+50/2000+15:00:05

=15:00:05:025 (8)

sensor_cnt=1050

1st_pkt_clk=50

first_pktflag=1

1st_pkt_cnt=1010

cur_pkt_cnt=1050

FPGA_freq=2000

sensor_freq=3810

Real_time

=(1050-1010)/3810+50/2000+15:00:05

=15:00:05:035 (9)

sensor_cnt=1150

1st_pkt_clk=50

first_pktflag=1

1st_pkt_cnt=1010

cur_pkt_cnt=1150

FPGA_freq=2000

sensor_freq=3704

Real_time

=(1150-1010)/3704+50/2000+15:00:05

=15:00:05:063 (10)

(付記1)

第1システム時刻を記憶する記憶部と、

前記記憶部に前記第1システム時刻が書き込まれた後に、情報取得装置から、前記情報取得装置が取得した第1情報と、前記第1情報の取得時刻を示す第1時刻情報とを受信し、前記第1情報と前記第1時刻情報とを受信した後に、前記情報取得装置から、第2情報と前記第2情報の取得時刻を示す第2時刻情報とを受信する受信部と、

前記第1システム時刻に基づいて、前記受信部が前記第1情報と前記第1時刻情報とを受信した受信時刻を、第2システム時刻に変換する受信時刻変換部と、

前記第2システム時刻と前記第1時刻情報とに基づいて、前記第2時刻情報を第3システム時刻に変換する時刻情報変換部と、

前記第2システム時刻を前記第1情報に付加し、前記第3システム時刻を前記第2情報に付加する付加部と、

を備えることを特徴とする情報処理装置。

(付記2)

前記時刻情報変換部は、

前記第2時刻情報と前記第1時刻情報との差分を生成する減算部と、

前記第2時刻情報と前記第1時刻情報との差分から、前記第3システム時刻と前記第2システム時刻との差分を計算する第1差分計算部と、

前記第3システム時刻と前記第2システム時刻との差分を前記第2システム時刻に加算することで、前記第3システム時刻を求める第1加算部と、

を含むことを特徴とする付記1記載の情報処理装置。

(付記3)

前記第2時刻情報と前記第1時刻情報との差分と、クロック信号と、前記クロック信号の周波数とを用いて、前記情報取得装置において取得時刻を生成するタイミング信号の周波数を計算する第1周波数計算部をさらに備え、

前記受信時刻変換部は、前記受信部が前記第1情報と前記第1時刻情報とを受信したときに、前記クロック信号に基づいて特定された時刻を、前記受信時刻として用い、

前記第1差分計算部は、前記第2時刻情報と前記第1時刻情報との差分と、前記タイミング信号の周波数とを用いて、前記第3システム時刻と前記第2システム時刻との差分を計算することを特徴とする付記2記載の情報処理装置。

(付記4)

前記受信時刻変換部は、

前記受信時刻と前記クロック信号の周波数とを用いて、前記第2システム時刻と前記第1システム時刻との差分を計算する第2差分計算部と、

前記第2システム時刻と前記第1システム時刻との差分を前記第1システム時刻に加算することで、前記第2システム時刻を求める第2加算部と、

を含むことを特徴とする付記3記載の情報処理装置。

(付記5)

前記第1システム時刻と前記クロック信号とを用いて、前記クロック信号の周波数を計算する第2周波数計算部をさらに備えることを特徴とする付記4記載の情報処理装置。

(付記6)

前記受信部は、前記記憶部に前記第1システム時刻が書き込まれた後に、複数の情報取得装置のうちいずれかの情報取得装置から、前記いずれかの情報取得装置が取得した第1情報と第1時刻情報とを受信し、前記第1情報と前記第1時刻情報とを受信した後に、前記いずれかの情報取得装置から、第2情報と第2時刻情報とを受信し、

前記付加部は、前記第2システム時刻を前記いずれかの情報取得装置から受信した第1情報に付加し、前記第3システム時刻を前記いずれかの情報取得装置から受信した第2情報に付加することを特徴とする付記1乃至5のいずれか1項に記載の情報処理装置。

(付記7)

情報処理装置によって実行される時刻同期方法であって、

前記情報処理装置が、

第1システム時刻が記憶部に書き込まれた後に、情報取得装置から、前記情報取得装置が取得した第1情報と、前記第1情報の取得時刻を示す第1時刻情報とを受信し、

前記第1情報と前記第1時刻情報とを受信した後に、前記情報取得装置から、第2情報と前記第2情報の取得時刻を示す第2時刻情報とを受信し、

前記第1システム時刻に基づいて、前記第1情報と前記第1時刻情報とを受信した受信時刻を、第2システム時刻に変換し、

前記第2システム時刻と前記第1時刻情報とに基づいて、前記第2時刻情報を第3システム時刻に変換し、

前記第2システム時刻を前記第1情報に付加し、

前記第3システム時刻を前記第2情報に付加する、

ことを特徴とする時刻同期方法。

(付記8)

前記情報処理装置は、

前記第2時刻情報と前記第1時刻情報との差分を生成し、

前記第2時刻情報と前記第1時刻情報との差分から、前記第3システム時刻と前記第2システム時刻との差分を計算し、

前記第3システム時刻と前記第2システム時刻との差分を前記第2システム時刻に加算することで、前記第3システム時刻を求めることを特徴とする付記7記載の時刻同期方法。

(付記9)

前記情報処理装置は、

前記第2時刻情報と前記第1時刻情報との差分と、クロック信号と、前記クロック信号の周波数とを用いて、前記情報取得装置において取得時刻を生成するタイミング信号の周波数を計算し、

前記第1情報と前記第1時刻情報とを受信したときに、前記クロック信号に基づいて特定された時刻を、前記受信時刻として用い、

前記第2時刻情報と前記第1時刻情報との差分と、前記タイミング信号の周波数とを用いて、前記第3システム時刻と前記第2システム時刻との差分を計算することを特徴とする付記8記載の時刻同期方法。

(付記10)

前記情報処理装置は、

前記受信時刻と前記クロック信号の周波数とを用いて、前記第2システム時刻と前記第1システム時刻との差分を計算し、

前記第2システム時刻と前記第1システム時刻との差分を前記第1システム時刻に加算することで、前記第2システム時刻を求めることを特徴とする付記9記載の時刻同期方法。

(付記11)

第1システム時刻が記憶部に書き込まれた後に、情報取得装置から、前記情報取得装置が取得した第1情報と、前記第1情報の取得時刻を示す第1時刻情報とを受信し、

前記第1情報と前記第1時刻情報とを受信した後に、前記情報取得装置から、第2情報と前記第2情報の取得時刻を示す第2時刻情報とを受信し、

前記第1システム時刻に基づいて、前記第1情報と前記第1時刻情報とを受信した受信時刻を、第2システム時刻に変換し、

前記第2システム時刻と前記第1時刻情報とに基づいて、前記第2時刻情報を第3システム時刻に変換し、

前記第2システム時刻を前記第1情報に付加し、

前記第3システム時刻を前記第2情報に付加する、

処理をコンピュータに実行させるための時刻同期プログラム。

(付記12)

前記コンピュータは、

前記第2時刻情報と前記第1時刻情報との差分を生成し、

前記第2時刻情報と前記第1時刻情報との差分から、前記第3システム時刻と前記第2システム時刻との差分を計算し、

前記第3システム時刻と前記第2システム時刻との差分を前記第2システム時刻に加算することで、前記第3システム時刻を求めることを特徴とする付記11記載の時刻同期プログラム。

(付記13)

前記コンピュータは、

前記第2時刻情報と前記第1時刻情報との差分と、クロック信号と、前記クロック信号の周波数とを用いて、前記情報取得装置において取得時刻を生成するタイミング信号の周波数を計算し、

前記第1情報と前記第1時刻情報とを受信したときに、前記クロック信号に基づいて特定された時刻を、前記受信時刻として用い、

前記第2時刻情報と前記第1時刻情報との差分と、前記タイミング信号の周波数とを用いて、前記第3システム時刻と前記第2システム時刻との差分を計算することを特徴とする付記12記載の時刻同期プログラム。

(付記14)

前記コンピュータは、

前記受信時刻と前記クロック信号の周波数とを用いて、前記第2システム時刻と前記第1システム時刻との差分を計算し、

前記第2システム時刻と前記第1システム時刻との差分を前記第1システム時刻に加算することで、前記第2システム時刻を求めることを特徴とする付記13記載の時刻同期プログラム。

102-1、102-2 センサ

121-1~121-4、122-1~122-4 データ

111、201、301 FPGA

202 OS

211 割り込みコントローラ

212、311 MMIOレジスタ

213 検出部

221 OS時刻

312 加算部

402、602-1~602-N 情報取得装置

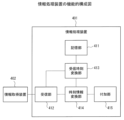

411 記憶部

412、621 受信部

413 受信時刻変換部

414 時刻情報変換部

415、625 付加部

603 通信ネットワーク

611 CPU

612 メモリ

613 時刻同期部

622-1~622-N 第1周波数計算部

623 第2周波数計算部

624-1~624-N 変換部

701 センサモジュール

711 圧力センサ

712、812 水晶振動子

713、813 ADコンバータ

714、814、904、1203、1301 カウンタ

715、815、901、1201 書き込み回路

716、816 データバッファ

717 I2Cバスマスタ

721 情報

801 ビデオモジュール

811 撮像装置

821 画像情報

902 判定回路

903 セレクタ

905~911、1204~1206、1302~1304 レジスタ

912、1207、1208、1305、1306 減算器

913、914、1209、1307、1308 DSP

915、916 加算器

1101、1102 タイムフレーム

1111、1112、1701 OS時刻の差分

1202 ロード回路

1210、1309 統計値計算回路

1801 CPU

1802 メモリ

1803 インタフェース

Claims (6)

- 第1システム時刻を記憶する記憶部と、

前記記憶部に前記第1システム時刻が書き込まれた後に、情報取得装置から、前記情報取得装置が取得した第1情報と、前記第1情報の取得時刻を示す第1時刻情報とを受信し、前記第1情報と前記第1時刻情報とを受信した後に、前記情報取得装置から、第2情報と前記第2情報の取得時刻を示す第2時刻情報とを受信する受信部と、

前記第2時刻情報と前記第1時刻情報との差分と、クロック信号と、前記クロック信号の周波数とを用いて、前記情報取得装置において取得時刻を生成するタイミング信号の周波数を計算する第1周波数計算部と、

前記受信部が前記第1情報と前記第1時刻情報とを受信したときに、前記クロック信号に基づいて特定された時刻を、前記受信部が前記第1情報と前記第1時刻情報とを受信した受信時刻として用い、前記第1システム時刻に基づいて、前記受信時刻を第2システム時刻に変換する受信時刻変換部と、

前記第2システム時刻と前記第1時刻情報とに基づいて、前記第2時刻情報を第3システム時刻に変換する時刻情報変換部と、

前記第2システム時刻を前記第1情報に付加し、前記第3システム時刻を前記第2情報に付加する付加部と、

を備え、

前記時刻情報変換部は、

前記第2時刻情報と前記第1時刻情報との差分を生成する減算部と、

前記第2時刻情報と前記第1時刻情報との差分と、前記タイミング信号の周波数とを用いて、前記第3システム時刻と前記第2システム時刻との差分を計算する第1差分計算部と、

前記第3システム時刻と前記第2システム時刻との差分を前記第2システム時刻に加算することで、前記第3システム時刻を求める第1加算部と、

を含むことを特徴とする情報処理装置。 - 前記受信時刻変換部は、

前記受信時刻と前記クロック信号の周波数とを用いて、前記第2システム時刻と前記第1システム時刻との差分を計算する第2差分計算部と、

前記第2システム時刻と前記第1システム時刻との差分を前記第1システム時刻に加算することで、前記第2システム時刻を求める第2加算部と、

を含むことを特徴とする請求項1記載の情報処理装置。 - 前記第1システム時刻と前記クロック信号とを用いて、前記クロック信号の周波数を計算する第2周波数計算部をさらに備えることを特徴とする請求項2記載の情報処理装置。

- 前記受信部は、前記記憶部に前記第1システム時刻が書き込まれた後に、複数の情報取得装置のうちいずれかの情報取得装置から、前記いずれかの情報取得装置が取得した第1情報と第1時刻情報とを受信し、前記第1情報と前記第1時刻情報とを受信した後に、前記いずれかの情報取得装置から、第2情報と第2時刻情報とを受信し、

前記付加部は、前記第2システム時刻を前記いずれかの情報取得装置から受信した第1情報に付加し、前記第3システム時刻を前記いずれかの情報取得装置から受信した第2情報に付加することを特徴とする請求項1乃至3のいずれか1項に記載の情報処理装置。 - 情報処理装置によって実行される時刻同期方法であって、

前記情報処理装置が、

第1システム時刻が記憶部に書き込まれた後に、情報取得装置から、前記情報取得装置が取得した第1情報と、前記第1情報の取得時刻を示す第1時刻情報とを受信し、

前記第1情報と前記第1時刻情報とを受信した後に、前記情報取得装置から、第2情報と前記第2情報の取得時刻を示す第2時刻情報とを受信し、

前記第2時刻情報と前記第1時刻情報との差分と、クロック信号と、前記クロック信号の周波数とを用いて、前記情報取得装置において取得時刻を生成するタイミング信号の周波数を計算し、

前記第1情報と前記第1時刻情報とを受信したときに、前記クロック信号に基づいて特定された時刻を、前記第1情報と前記第1時刻情報とを受信した受信時刻として用い、前記第1システム時刻に基づいて、前記受信時刻を第2システム時刻に変換し、

前記第2時刻情報と前記第1時刻情報との差分と、前記タイミング信号の周波数とを用いて、前記第3システム時刻と前記第2システム時刻との差分を計算し、

前記第3システム時刻と前記第2システム時刻との差分を前記第2システム時刻に加算することで、第3システム時刻を求め、

前記第2システム時刻を前記第1情報に付加し、

前記第3システム時刻を前記第2情報に付加する、

ことを特徴とする時刻同期方法。 - 第1システム時刻が記憶部に書き込まれた後に、情報取得装置から、前記情報取得装置が取得した第1情報と、前記第1情報の取得時刻を示す第1時刻情報とを受信し、

前記第1情報と前記第1時刻情報とを受信した後に、前記情報取得装置から、第2情報と前記第2情報の取得時刻を示す第2時刻情報とを受信し、

前記第2時刻情報と前記第1時刻情報との差分と、クロック信号と、前記クロック信号の周波数とを用いて、前記情報取得装置において取得時刻を生成するタイミング信号の周波数を計算し、

前記第1情報と前記第1時刻情報とを受信したときに、前記クロック信号に基づいて特定された時刻を、前記第1情報と前記第1時刻情報とを受信した受信時刻として用い、前記第1システム時刻に基づいて、前記受信時刻を第2システム時刻に変換し、

前記第2時刻情報と前記第1時刻情報との差分と、前記タイミング信号の周波数とを用いて、前記第3システム時刻と前記第2システム時刻との差分を計算し、

前記第3システム時刻と前記第2システム時刻との差分を前記第2システム時刻に加算することで、第3システム時刻を求め、

前記第2システム時刻を前記第1情報に付加し、

前記第3システム時刻を前記第2情報に付加する、

処理をコンピュータに実行させるための時刻同期プログラム。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019002774A JP7217153B2 (ja) | 2019-01-10 | 2019-01-10 | 情報処理装置、時刻同期方法、及び時刻同期プログラム |

| EP19210588.0A EP3681171B1 (en) | 2019-01-10 | 2019-11-21 | Information processing apparatus, time synchronization method, and time synchronization program |

| US16/693,456 US10771232B2 (en) | 2019-01-10 | 2019-11-25 | Information processing apparatus, time synchronization method, and computer-readable recording medium recording time synchronization program |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019002774A JP7217153B2 (ja) | 2019-01-10 | 2019-01-10 | 情報処理装置、時刻同期方法、及び時刻同期プログラム |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2020112412A JP2020112412A (ja) | 2020-07-27 |

| JP7217153B2 true JP7217153B2 (ja) | 2023-02-02 |

Family

ID=68762408

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019002774A Active JP7217153B2 (ja) | 2019-01-10 | 2019-01-10 | 情報処理装置、時刻同期方法、及び時刻同期プログラム |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US10771232B2 (ja) |

| EP (1) | EP3681171B1 (ja) |

| JP (1) | JP7217153B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP3594815A4 (en) * | 2017-03-09 | 2021-03-24 | Pioneer Corporation | INFORMATION PROCESSING DEVICE, INFORMATION PROCESSING METHOD, COMPUTER PROGRAM AND RECORDING MEDIUM |

| CN113259037B (zh) * | 2021-03-30 | 2022-12-23 | 杭州涂鸦信息技术有限公司 | 基于传感器时间同步系统的时间同步方法、介质及装置 |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008209995A (ja) | 2007-02-23 | 2008-09-11 | Mitsubishi Electric Corp | 分散計測システムおよびその方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7835366B2 (en) * | 2005-11-01 | 2010-11-16 | Ciena Corporation | Three-way message exchange clock synchronization |

| KR20090032306A (ko) * | 2007-09-27 | 2009-04-01 | 한국전자통신연구원 | 네트워크상의 타임 동기화 시스템 및 방법 |

| JP5369814B2 (ja) * | 2009-03-26 | 2013-12-18 | ソニー株式会社 | 受信装置および受信装置の時刻修正方法 |

| CN102111258A (zh) * | 2009-12-25 | 2011-06-29 | 华为技术有限公司 | 时钟同步方法、设备和系统 |

| WO2012111112A1 (ja) * | 2011-02-16 | 2012-08-23 | 富士通株式会社 | 情報処理装置、時刻設定方法、および時刻設定プログラム |

| US9426763B2 (en) * | 2013-04-17 | 2016-08-23 | Qualcomm Incorporated | Systems and methods for synchronizing timing between wireless networking devices |

| JP6183016B2 (ja) | 2013-07-10 | 2017-08-23 | 住友電気工業株式会社 | センサ情報処理装置、センサ情報処理方法およびセンサ情報処理プログラム |

| US20170041688A1 (en) * | 2013-11-12 | 2017-02-09 | Qualcomm Incorporated | Apparatus and methods for timestamping in a system synchronizing controller and sensors |

| CN106162860B (zh) * | 2015-04-27 | 2020-01-03 | 华为技术有限公司 | 一种时间同步的方法及系统、网络设备 |

| US10349368B2 (en) * | 2016-06-30 | 2019-07-09 | Imagination Technologies Limited | Reference synchronisation |

| JP6649517B2 (ja) | 2017-02-17 | 2020-02-19 | 日本電信電話株式会社 | センシングシステムおよびタイムスタンプ補正方法 |

-

2019

- 2019-01-10 JP JP2019002774A patent/JP7217153B2/ja active Active

- 2019-11-21 EP EP19210588.0A patent/EP3681171B1/en active Active

- 2019-11-25 US US16/693,456 patent/US10771232B2/en active Active

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008209995A (ja) | 2007-02-23 | 2008-09-11 | Mitsubishi Electric Corp | 分散計測システムおよびその方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP3681171A1 (en) | 2020-07-15 |

| US10771232B2 (en) | 2020-09-08 |

| JP2020112412A (ja) | 2020-07-27 |

| US20200228305A1 (en) | 2020-07-16 |

| EP3681171B1 (en) | 2023-07-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10051158B2 (en) | Control apparatus for image pickup apparatus | |

| JP7217153B2 (ja) | 情報処理装置、時刻同期方法、及び時刻同期プログラム | |

| TWI640165B (zh) | 感測器時鐘估計方法及其裝置 | |

| JP2010190635A (ja) | スレーブ装置、スレーブ装置の時刻同期化方法、マスタ装置および電子機器システム | |

| TW201802700A (zh) | 用於控制同步資料流之系統及方法 | |

| CN115361084B (zh) | 一种同步时钟的方法、装置、设备及介质 | |

| JP2015056039A (ja) | 制御装置、制御システムおよび制御方法 | |

| US6895009B1 (en) | Method of generating timestamps for isochronous data | |

| KR100828216B1 (ko) | 멀티미디어 신호 동기화 장치, 컴퓨터 시스템, 신호 동기화 장치 및 방법 | |

| JP4247759B2 (ja) | 被験者情報伝送システム及び被験者情報同期方法 | |

| JP2002064788A (ja) | データストリーム処理装置および方法、並びにプログラム格納媒体 | |

| US10809760B1 (en) | Headset clock synchronization | |

| CN107690053B (zh) | 一种确定视频流的时间轴的方法以及系统 | |

| CN107392983B (zh) | 一种录制动画的方法及系统 | |

| CN113847980A (zh) | 时间序列传感器数据处理设备和方法 | |

| CN109933418B (zh) | 一种时间戳同步方法、电子设备及异构设备 | |

| CN115451954B (zh) | 一种捷联惯导与外部时钟同步的延时补偿方法 | |

| CN113448723B (zh) | 影像感测系统控制方法以及影像感测系统 | |

| JP7265403B2 (ja) | ネットワーク遅延計測方法及び装置並びにプログラム | |

| TWI748892B (zh) | 時脈同步系統及操作時脈同步系統的方法 | |

| JP5423071B2 (ja) | データ転送装置及び撮像装置 | |

| EP4539471A1 (en) | Media transmission system, sending device, sending system, reception device, and reception system | |

| US20240153036A1 (en) | Medical image processing system, medical image processing method, and program | |

| CN114257781B (zh) | 双倍速率动态随机存储器读写控制方法、装置和系统 | |

| WO2024166271A1 (ja) | 判定装置及び判定方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20211007 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20220720 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220823 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20221018 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20221018 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230110 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230123 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7217153 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |