JP7034739B2 - 窒化物半導体基板およびその製造方法 - Google Patents

窒化物半導体基板およびその製造方法 Download PDFInfo

- Publication number

- JP7034739B2 JP7034739B2 JP2018011099A JP2018011099A JP7034739B2 JP 7034739 B2 JP7034739 B2 JP 7034739B2 JP 2018011099 A JP2018011099 A JP 2018011099A JP 2018011099 A JP2018011099 A JP 2018011099A JP 7034739 B2 JP7034739 B2 JP 7034739B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- gan

- raw material

- nitride semiconductor

- semiconductor substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Junction Field-Effect Transistors (AREA)

Description

前記第二の層がIn a2 Al b2 Ga c2 N(a2=0、0<b2≦1、0≦c2<1、b2+c2=1)の組成を有する電子供給層であり、前記キャップ層がGaN層であり、前記第三の層がGa j Si 1-j N(0<j<1)層であることを特徴とする。

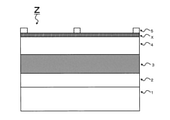

図2に示す窒化物半導体基板Zは、本発明の好適な一態様であり、下地基板1、バッファ層2、第一の層(電子走行層)3、キャップ層C、第二の層(電子供給層)4、第三の層Xおよび電極5を含む。

なお、本発明で示す図はすべて、説明のために形状を模式的に簡素化かつ強調したものであり、細部の形状、寸法、および比率は実際と異なる。また、本発明を説明するのに不要と考えられるその他の構成については、記載を割愛する。

また、第一の層3および第二の層4に含まれる不純物についても、その許容量に限界はない。なお、不純物は、例えば、炭素、リン、マグネシウム、ケイ素、鉄、酸素および水素などである。

この第三の層Xは、広義には保護層としての役割を担っており、本発明でも、特に、電子供給層が大気雰囲気に暴露されることによる不具合を回避する作用を備えている。

上記のとおり、第三の層Xは、第二の層4との界面における電子の挙動に影響を与えるものであり、それ自体があまり厚いと、格子定数の差による応力の影響が無視できなくなる。しかし1nm未満では、本発明の効果が十分得られないだけでなく、形成すること自体が困難である。

直径6インチ、厚さ675μm、p型で比抵抗0.002Ωcm、面方位(111)のシリコン単結晶基板を準備した。これを公知の基板洗浄方法で清浄化した後、MOCVD装置内にセットして、昇温し、装置内をキャリアガスで置換後、1000℃×15分、水素100%雰囲気で熱処理を行い、シリコン単結晶表面の自然酸化膜を除去した。

電子供給層上に、キャップ層としてGaN層を1nm、続いて、第三の層を4nm成膜した。第三の層の成膜では、シラン(SiH4)、NH3およびTMGaを同時に3秒間供給した後、TMGaの供給のみを止め、さらに5秒間、SiH4およびNH3を供給して、GajSi1-jN(0<j<1)層を形成した。GajSi1-jNの厚さは約1nm、j値は約0.5であった。

TMGaの供給は行わず、第三の層の成膜時間を調整した以外は、実施例1と同様にして、キャップ層の形成、および厚さ約4nmでSiN層の形成を行った。

実施例1および比較例1の窒化物半導体基板について、移動度とキャリア濃度を評価した。すなわち、これらの窒化物半導体基板の表面に電極を形成し、Hall効果を測定した。Hall効果の測定は、Van der Pauw法を採用し、測定装置はACCENT製HL5500PCを用いて実施した。また、この電極を用いてシート抵抗も測定した。

結果を以下に示す。

2 バッファ層

3 第一の層(電子走行層)

4 第二の層(電子供給層)

X 第三の層

5 電極

6 SiN保護膜

C キャップ層

Claims (2)

- Ina1Alb1Gac1N(0≦a1≦1、0≦b1≦1、0≦c1≦1、a1+b1+c1=1)の組成を有する第一の層と、

前記第一の層上に形成され、Ina2Alb2Gac2N(0≦a2≦1、0≦b2≦1、0≦c2≦1、a2+b2+c2=1)の組成を有し、かつ、前記第一の層とは異なるバンドギャップを有する第二の層と、

前記第二の層上に形成され、AjB1-jN(Aは13族元素、Bは13族元素または14族元素、A≠B、0<j<1)の組成を有する第三の層と、

前記第二の層と前記第三の層との間に、13族窒化物からなるキャップ層を有し、

前記第一の層がGaNからなる電子走行層であり、

前記第二の層がIn a2 Al b2 Ga c2 N(a2=0、0<b2≦1、0≦c2<1、b2+c2=1)の組成を有する電子供給層であり、

前記キャップ層がGaN層であり、

前記第三の層がGa j Si 1-j N(0<j<1)層であることを特徴とする窒化物半導体基板。 - 第一の層として、電子走行層であるGaN層と、

第二の層として、電子供給層であるIna2Alb2Gac2N(a2=0、0<b2≦1、0≦c2<1、b2+c2=1)層と、

キャップ層としてGaN層と、

第三の層として、GajSi1-jN(0<j<1)層と

をこの順に有し、有機金属気相成長法により窒化物半導体基板を製造する方法であって、

第一の層を積層後、前記第一の層上に第二の層を連続して積層する第1ステップと、

第1ステップの後、前記第二の層上にキャップ層を形成する第2ステップと、

第2ステップ終了直後に、Ga原料ガスとSi原料ガスとN原料ガスとを3秒以下の時間で供給し、第三の層を積層する第3ステップと、

第3ステップの後、前記Ga原料ガスの供給を停止し、前記Si原料ガスと前記N原料ガスとを供給する第4ステップと、

を備えることを特徴とする窒化物半導体基板の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP18157146.4A EP3364463A3 (en) | 2017-02-20 | 2018-02-16 | Nitride semiconductor substrate and method for manufactuing the same |

| US15/900,202 US10593790B2 (en) | 2017-02-20 | 2018-02-20 | Nitride semiconductor substrate and method for manufacturing the same |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017028846 | 2017-02-20 | ||

| JP2017028846 | 2017-02-20 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018137432A JP2018137432A (ja) | 2018-08-30 |

| JP7034739B2 true JP7034739B2 (ja) | 2022-03-14 |

Family

ID=63367073

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018011099A Active JP7034739B2 (ja) | 2017-02-20 | 2018-01-26 | 窒化物半導体基板およびその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP7034739B2 (ja) |

| TW (1) | TWI669820B (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI730516B (zh) * | 2018-12-12 | 2021-06-11 | 日商闊斯泰股份有限公司 | 氮化物半導體基板以及氮化物半導體裝置 |

| CN116759505B (zh) * | 2023-08-23 | 2023-11-17 | 江西兆驰半导体有限公司 | 基于硅衬底的led外延片及其制备方法、led |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013229458A (ja) | 2012-04-26 | 2013-11-07 | Mitsubishi Electric Corp | ヘテロ接合電界効果型トランジスタおよびその製造方法 |

| JP2013243275A (ja) | 2012-05-22 | 2013-12-05 | Pawdec:Kk | GaN系半導体素子およびその製造方法 |

| JP2014170934A (ja) | 2013-02-28 | 2014-09-18 | Power Integrations Inc | ヘテロ構造パワートランジスタおよびヘテロ構造半導体装置を作製する方法 |

| US20150187925A1 (en) | 2013-12-30 | 2015-07-02 | Enkris Semiconductor, Inc. | Enhancement-mode device |

| JP2015177069A (ja) | 2014-03-14 | 2015-10-05 | 株式会社東芝 | 半導体装置 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB201112330D0 (en) * | 2011-07-18 | 2011-08-31 | Epigan Nv | Method for growing III-V epitaxial layers and semiconductor structure |

| GB201203161D0 (en) * | 2012-02-23 | 2012-04-11 | Epigan Nv | A device comprising a III-N layer stack with improved passivation layer and associated manufacturing method |

-

2018

- 2018-01-26 JP JP2018011099A patent/JP7034739B2/ja active Active

- 2018-02-09 TW TW107102527A patent/TWI669820B/zh active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013229458A (ja) | 2012-04-26 | 2013-11-07 | Mitsubishi Electric Corp | ヘテロ接合電界効果型トランジスタおよびその製造方法 |

| JP2013243275A (ja) | 2012-05-22 | 2013-12-05 | Pawdec:Kk | GaN系半導体素子およびその製造方法 |

| JP2014170934A (ja) | 2013-02-28 | 2014-09-18 | Power Integrations Inc | ヘテロ構造パワートランジスタおよびヘテロ構造半導体装置を作製する方法 |

| US20150187925A1 (en) | 2013-12-30 | 2015-07-02 | Enkris Semiconductor, Inc. | Enhancement-mode device |

| JP2015177069A (ja) | 2014-03-14 | 2015-10-05 | 株式会社東芝 | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI669820B (zh) | 2019-08-21 |

| TW201838188A (zh) | 2018-10-16 |

| JP2018137432A (ja) | 2018-08-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10211296B2 (en) | P-doping of group-III-nitride buffer layer structure on a heterosubstrate | |

| JP4530171B2 (ja) | 半導体装置 | |

| KR101321625B1 (ko) | 전자 디바이스용 에피택셜 기판 및 그 제조방법 | |

| JP4381380B2 (ja) | 半導体装置及びその製造方法 | |

| JP6152124B2 (ja) | 半導体装置の製造方法 | |

| US20100243989A1 (en) | Semiconductor device | |

| US20140048770A1 (en) | Nitride semiconductor wafer, nitride semiconductor device, and method for growing nitride semiconductor crystal | |

| JP5788296B2 (ja) | 窒化物半導体基板及びその製造方法 | |

| US10483354B2 (en) | Nitride semiconductor device | |

| US9401402B2 (en) | Nitride semiconductor device and nitride semiconductor substrate | |

| JP6173493B2 (ja) | 半導体素子用のエピタキシャル基板およびその製造方法 | |

| JP2012151422A (ja) | 半導体ウエーハ及び半導体素子及びその製造方法 | |

| JP7034739B2 (ja) | 窒化物半導体基板およびその製造方法 | |

| JP2015103665A (ja) | 窒化物半導体エピタキシャルウエハおよび窒化物半導体 | |

| JP4682541B2 (ja) | 半導体の結晶成長方法 | |

| JP2011258782A (ja) | 窒化物半導体基板 | |

| US10593790B2 (en) | Nitride semiconductor substrate and method for manufacturing the same | |

| JP6416705B2 (ja) | 電界効果トランジスタおよびその製造方法 | |

| TWI728498B (zh) | 氮化物半導體基板 | |

| JP2017092369A (ja) | Iii族窒化物半導体デバイス用基板およびその製造方法 | |

| JP2021044596A (ja) | 窒化物半導体積層物、半導体装置、および窒化物半導体積層物の製造方法 | |

| WO2015005083A1 (ja) | 窒化物半導体積層基板、窒化物半導体装置および窒化物半導体積層基板の製造方法 | |

| CN106783955A (zh) | 含有氮镓铝和氮镓铟的插入层的半导体器件及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20201106 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210930 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20211005 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20211126 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20220301 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20220302 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7034739 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |