JP6915744B2 - 抵抗変化素子及びその製造方法、記憶装置 - Google Patents

抵抗変化素子及びその製造方法、記憶装置 Download PDFInfo

- Publication number

- JP6915744B2 JP6915744B2 JP2020508810A JP2020508810A JP6915744B2 JP 6915744 B2 JP6915744 B2 JP 6915744B2 JP 2020508810 A JP2020508810 A JP 2020508810A JP 2020508810 A JP2020508810 A JP 2020508810A JP 6915744 B2 JP6915744 B2 JP 6915744B2

- Authority

- JP

- Japan

- Prior art keywords

- ion

- layer

- resistance

- resistance change

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/883—Oxides or nitrides

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/54—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using elements simulating biological cells, e.g. neuron

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0007—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising metal oxide memory material, e.g. perovskites

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/003—Cell access

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/004—Reading or sensing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01C—RESISTORS

- H01C13/00—Resistors not provided for elsewhere

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/80—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/011—Manufacture or treatment of multistable switching devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

- H10N70/24—Multistable switching devices, e.g. memristors based on migration or redistribution of ionic species, e.g. anions, vacancies

- H10N70/245—Multistable switching devices, e.g. memristors based on migration or redistribution of ionic species, e.g. anions, vacancies the species being metal cations, e.g. programmable metallization cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

- H10N70/253—Multistable switching devices, e.g. memristors having three or more electrodes, e.g. transistor-like devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/841—Electrodes

- H10N70/8416—Electrodes adapted for supplying ionic species

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/883—Oxides or nitrides

- H10N70/8836—Complex metal oxides, e.g. perovskites, spinels

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/004—Reading or sensing circuits or methods

- G11C2013/0045—Read using current through the cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0069—Writing or programming circuits or methods

- G11C2013/009—Write using potential difference applied between cell electrodes

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/77—Array wherein the memory element being directly connected to the bit lines and word lines without any access device being used

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- General Health & Medical Sciences (AREA)

- Life Sciences & Earth Sciences (AREA)

- Biomedical Technology (AREA)

- Health & Medical Sciences (AREA)

- Molecular Biology (AREA)

- Neurology (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Adjustable Resistors (AREA)

- Secondary Cells (AREA)

Description

しかしながら、抵抗変化層やイオン吸蔵放出層に用いる材料を適切に選択しないと、書き込み時に印加する電圧が大きくなり、書き込み時に必要な電気エネルギが大きくなってしまうことがわかった。

1つの態様では、抵抗変化素子の製造方法は、少なくとも1種類のイオンを吸蔵及び放出でき、少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層を形成する工程と、少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層を形成する工程と、抵抗変化層とイオン吸蔵放出層との間で、少なくとも1種類のイオンを伝導するイオン伝導層を形成する工程とを含み、抵抗変化層を形成する工程及びイオン吸蔵放出層を形成する工程において、構成元素が同一であって且つ組成比が同じである抵抗変化層及びイオン吸蔵放出層をそれぞれ形成する。

本実施形態にかかる抵抗変化素子は、正極活物質層と負極活物質層の間で電解質層(固体電解質層)を通ってイオンが移動することで充電、放電を行なう二次電池の構成を適用した抵抗変化素子である。なお、二次電池を固体二次電池、全固体二次電池、固体電池、全固体電池又はイオン電池ともいう。

本実施形態では、抵抗変化層3は、イオン電池に用いられる正極活物質からなる正極活物質層であり、イオン伝導層4は、イオン電池に用いられる固体電解質からなる固体電解質層であり、イオン吸蔵放出層5は、イオン電池に用いられる負極活物質からなる負極活物質層である。

なお、ここでは、イオン伝導層4は、この少なくとも1種類のイオンを伝導し、電子を伝導しないイオン伝導層である。

また、抵抗変化層3の中のイオンの量(濃度)を連続的に変化させ、その抵抗を連続的に変化させることもできるため、多くの抵抗値を記憶することができる多値抵抗変化素子を実現することも可能である。

特に、本実施形態では、抵抗変化層3とイオン吸蔵放出層5は、構成元素が同一である。つまり、抵抗変化層3とイオン吸蔵放出層5に、構成元素が同一である材料、即ち、同一材料が用いられている。

例えば、伝導イオンをLiイオンとし、抵抗変化層3にLi4Ti5O12を用い、イオン吸蔵放出層5にLi7Ti5O12を用いる場合、Li以外の元素の組成比がともにTi:O=5:12で同じであるため、抵抗変化層3とイオン吸蔵放出層5は、同一材料が用いられていると言える。

つまり、抵抗変化層3とイオン吸蔵放出層5は、伝導イオンとなる元素の量(濃度)が異なっていても良いし、伝導イオンとなる元素の量(濃度)が同一であっても良い。

このように、同一材料とは、抵抗変化層3とイオン吸蔵放出層5で、伝導イオンとなる元素以外の元素の組成比が同じであれば良いことになる。

このようにして抵抗変化層3とイオン吸蔵放出層5を同一材料で構成することで、抵抗値(重み値;メモリ値;データ;情報)の書き込み時(書き換え時)の必要エネルギを低減することができる。

Li4Ti5O12は、次の反応式のように、リチウムの挿入脱離反応を起こすことができる。

Li4Ti5O12+3Li++3e⇔Li7Ti5O12

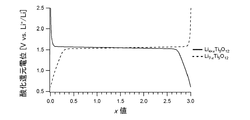

この挿入脱離は、Ti4+/3+の酸化還元を伴い、その電位は約1.5V(vs.Li+/Li)、即ち、リチウムの酸化還元電位を0Vとすると、Ti4+/3+の酸化還元電位は1.5Vである。

抵抗変化層3におけるLi4Ti5O12の物質量とイオン吸蔵放出層5におけるLi7Ti5O12の物質量が等しいと仮定すると、充放電過程における抵抗変化層3とイオン吸蔵放出層5の組成は、x(0≦x≦3)を用いて、それぞれ、Li4+xTi5O12、Li7−xTi5O12と表すことができる。

図2に示すように、xの値が0.3〜2.7の範囲において、Li4+xTi5O12を用いた抵抗変化層3とLi7−xTi5O12を用いたイオン吸蔵放出層5の双方の層の持つ電位の差は、約0.1V未満(<0.1V)になっている。

このように、抵抗変化層3とイオン吸蔵放出層5を同一材料で構成することで、これらの層の電位差を低減できるため、書き込み時に印加する電圧を低減でき、書き込み時に必要な電気エネルギを低減することが可能である。

このうち、伝導イオンをLiイオン(リチウムイオン)とする場合、抵抗変化層3とイオン吸蔵放出層5は、例えば、Li4+xTi5O12(0≦x≦3)、Li3+xV2(PO4)3(−2≦x≦2)、Li3+xFe2(PO4)3(0≦x≦2)、Li1+xVP2O7(−1≦x≦1)、Li1+xFeP2O7(0≦x≦1)、LixMnO2(0≦x≦1)、LixTiO2(0≦x≦1)などの材料からなるものとし、構成元素が同一であるものとすれば良い。また、イオン伝導層4は、例えば、LiPON、Li9Al3(P2O7)3(PO4)2、Li3zLa2/3−zTiO3(0≦z≦1/6)、Li7La3Zr2O12などの材料からなるものとすれば良い。

特に、抵抗変化層3とイオン吸蔵放出層5には、平均的な電子移動伝導度が高いLi4+xTi5O12(0≦x≦3)を用いるのが最も好ましい。

例えば、抵抗変化層3及びイオン吸蔵放出層5は、構成元素が同一であり、同一の組成式であるLi4+xTi5O12(0≦x≦3)で表される組成を有することが好ましい。つまり、抵抗変化層3及びイオン吸蔵放出層5に、構成元素が同一であり、同一の組成式であるLi4+xTi5O12(0≦x≦3)で表される材料(同一材料)を用いることが好ましい。

つまり、初期状態においてLi4+xTi5O12(x=0)で表される組成を有する抵抗変化層3及びイオン吸蔵放出層5の少なくとも一方を、xの値が0<x≦3となるように調整されているものとすることが好ましい。

つまり、抵抗変化層3及びイオン吸蔵放出層5にLi4+xTi5O12(0≦x≦3)で表される材料を用いる場合、x=0の状態が熱力学的に安定な状態であるため、初期状態では抵抗変化層3、イオン吸蔵放出層5はともにx=0の状態で成膜される。

一方、Li4+xTi5O12(0≦x≦3)で表される材料は、x<0の状態を取ることができないため、抵抗変化層3、イオン吸蔵放出層5がともにx=0の状態になっていると、両者間でLiイオンの授受を行なうことができない。

ここで、調整は以下の方法で行なうことができる。

成膜したLi4Ti5O12の上に金属リチウムを成膜する。

Li4Ti5O12+yLi→Li4+yTi5O12

なお、この反応は室温で放置しておくだけでも進行するが、高温状態(例えば約30℃〜約80℃)に置くことで当該反応を促進させることも可能である。

このようにして抵抗変化層3及びイオン吸蔵放出層5の少なくとも一方をxの値が0<x≦3となるように調整する場合、例えば、抵抗変化層3は上述の調整を行なわずにLi4Ti5O12からなるものとし、イオン吸蔵放出層5は上述の調整を行なってLi7Ti5O12からなるものとすれば良い。また、例えば、抵抗変化層3は上述の調整を行なってLi5Ti5O12からなるものとし、イオン吸蔵放出層5も上述の調整を行なってLi5Ti5O12からなるものとしても良い。また、例えば、抵抗変化層3は上述の調整を行なってLi7Ti5O12からなるものとし、イオン吸蔵放出層5は上述の調整を行なわずにLi4Ti5O12からなるものとしても良い。

ここで、xの値が同じになっている場合には、抵抗変化層3とイオン吸蔵放出層5は、伝導イオンとなる元素の組成比が同一になっていることになる。また、xの値が異なるものとなっている場合には、抵抗変化層3とイオン吸蔵放出層5は、伝導イオンとなる元素の組成比が異なっていることになる。いずれの場合も、抵抗変化層3とイオン吸蔵放出層5は、伝導イオンとなる元素以外の元素の組成比は同じである。

つまり、初期状態においてZnxMnO2(x=0)で表される組成を有する抵抗変化層3及びイオン吸蔵放出層5の少なくとも一方を、xの値が0<x≦0.5となるように調整されているものとすることが好ましい。

つまり、抵抗変化層3及びイオン吸蔵放出層5にZnxMnO2(0≦x≦0.5)で表される材料を用いる場合、x=0の状態が熱力学的に安定な状態であるため、初期状態では抵抗変化層3、イオン吸蔵放出層5はともにx=0の状態で成膜される。

一方、ZnxMnO2(0≦x≦0.5)で表される材料は、x<0の状態を取ることができないため、抵抗変化層3、イオン吸蔵放出層5がともにx=0の状態になっていると、両者間でZnイオンの授受を行なうことができない。

ここで、調整は以下の方法で行なうことができる。

成膜したMnO2の上に金属亜鉛を成膜する。

MnO2+yZn→ZnyMnO2

なお、この反応は室温で放置しておくだけでも進行するが、高温状態(例えば約30℃〜約80℃)に置くことで当該反応を促進させることも可能である。

このようにして抵抗変化層3及びイオン吸蔵放出層5の少なくとも一方をxの値が0<x≦0.5となるように調整する場合、例えば、抵抗変化層3は上述の調整を行なわずにMnO2からなるものとし、イオン吸蔵放出層5は上述の調整を行なってZn0.5MnO2からなるものとすれば良い。また、例えば、抵抗変化層3は上述の調整を行なってZn0.3MnO2からなるものとし、イオン吸蔵放出層5も上述の調整を行なってZn0.3MnO2からなるものとしても良い。また、例えば、抵抗変化層3は上述の調整を行なってZn0.5MnO2からなるものとし、イオン吸蔵放出層5は上述の調整を行なわずにMnO2からなるものとしても良い。

ここで、xの値が同じになっている場合には、抵抗変化層3とイオン吸蔵放出層5は、伝導イオンとなる元素の組成比が同一になっていることになる。また、xの値が異なるものとなっている場合には、抵抗変化層3とイオン吸蔵放出層5は、伝導イオンとなる元素の組成比が異なっていることになる。いずれの場合も、抵抗変化層3とイオン吸蔵放出層5は、伝導イオンとなる元素以外の元素の組成比は同じである。

つまり、抵抗変化層3及びイオン吸蔵放出層5に、ZnxTiO2(0≦x≦0.5)で表される材料を用いる場合、x=0の状態が熱力学的に安定な状態であるため、初期状態では抵抗変化層3、イオン吸蔵放出層5はともにx=0の状態で成膜される。一方、これらの材料は、x<0の状態を取ることができないため、抵抗変化層3、イオン吸蔵放出層5がともにx=0の状態になっていると、両者間でZnイオンの授受を行なうことができない。このため、両者間でZnイオンの授受を行なうことができるように、抵抗変化層3、イオン吸蔵放出層5の少なくとも一方のxの値を化学的に調整することが好ましい。

ここで、伝導イオンを他のイオンとする場合、抵抗変化層3、イオン吸蔵放出層5、イオン伝導層4には、以下のような材料を用いれば良い。

つまり、伝導イオンをNaイオン(ナトリウムイオン)とする場合、抵抗変化層3とイオン吸蔵放出層5は、例えば、Na1+xTi2(PO4)3(0≦x≦2),Na2+xTi3O7(0≦x≦3),Na3+xV2(PO4)3(−2≦x≦2),Na3-zV2-zZrz(PO4)3,NaxMnO2(0≦x≦1),NaxTiO2(0≦x≦1)などの材料からなるものとし、構成元素が同一であるものとすれば良い。また、イオン伝導層4は、例えば、Na3PO4,Na3Zr2(SiO4)2PO4,Na3.3Sc0.3Zr1.7(SiO4)2(PO4),Na+−β”−Al2O3などの材料からなるものとすれば良い。

本実施形態にかかる抵抗変化素子の製造方法は、少なくとも1種類のイオンを吸蔵、放出でき、少なくとも1種類のイオンの量に応じて抵抗が変化する抵抗変化層3を形成する工程と、少なくとも1種類のイオンを吸蔵、放出できるイオン吸蔵放出層5を形成する工程と、抵抗変化層とイオン吸蔵放出層との間で、少なくとも1種類のイオンを伝導するイオン伝導層4を形成する工程と、を含む。

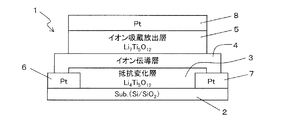

ところで、具体的な構成例としては、例えば図1に示すように、例えばSiO2膜(シリコン酸化膜;絶縁膜)を備えるSi基板などの基板2上に、例えばLi4+xTi5O12(x=0)、即ち、Li4Ti5O12で表される組成を有する抵抗変化層3、例えばLiPONからなるイオン伝導層4、例えばLi4+xTi5O12(x=3)、即ち、Li7Ti5O12で表される組成を有するイオン吸蔵放出層5を順に積層し、抵抗変化層3の両側に、例えばPtからなる第1電極6及び第2電極7を設け、イオン吸蔵放出層5上に、例えばPtからなる第3電極8を設ければ良い。

また、第1電極6及び第2電極7の少なくとも一方(ここでは第2電極7)及び第3電極8は、抵抗値(重み値;メモリ値;データ;情報)の書き込み(書き換え)に用いられる。このため、第1電極6及び第2電極7の少なくとも一方(ここでは第2電極7)及び第3電極8を、第1書込電極及び第2書込電極、又は、第1引出電極及び第2引出電極ともいう。

例えばSiO2膜を備えるSi基板などの基板2上に、第1電極6及び第2電極7、抵抗変化層3、イオン伝導層4、イオン吸蔵放出層5を成膜する。

つまり、例えばSiO2膜を備えるSi基板などの基板2上に、第1電極6及び第2電極7が抵抗変化層3に電気的に接続され、抵抗変化層3、イオン伝導層4、イオン吸蔵放出層5が順に積層されるように、第1電極6及び第2電極7、抵抗変化層3、イオン伝導層4、イオン吸蔵放出層5を成膜する。

なお、ここでは、第1電極6及び第2電極7の少なくとも一方(ここでは第2電極7)は、読出電極と書込電極を兼ねているが、これに限られるものではなく、第1電極6及び第2電極7を読出電極とし、これらとは別に書込電極としての第4電極を設けても良い。この場合、第4電極は、抵抗変化層3に電気的に接続されるように、抵抗変化層3、イオン伝導層4及びイオン吸蔵放出層5を挟んで第3電極8の反対側に設ければ良い。

ところで、上述のように構成される抵抗変化素子1では、以下のようにして、抵抗値(重み値;メモリ値;データ;情報)の書き込み(書き換え)と読み出し(読み取り)を行なうことができる。

Ioutput=Vinput/R

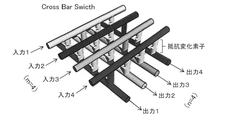

また、このように構成される抵抗変化素子1を用いて、例えば機械学習用のニューラルネットワークを作製することができる。

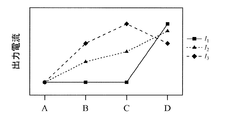

ここで、各入力ワイヤ10A、10Bから電圧Vi(1≦i≦m)を入力すると、各出力ワイヤ11A〜11Cから応答電流Ij(1≦j≦n)が出力される。

つまり、各抵抗変化素子R11〜Rmn(ここではR11、R12、R13、R21、R22、R23)に直流電源S11〜Smn(ここではS11、S12、S13、S21、S22、S23)によって電圧を印加して、各抵抗変化素子R11〜Rmn(ここではR11、R12、R13、R21、R22、R23)の持つ抵抗値を変化させることで、各出力ワイヤ11A〜11Cから出力される応答電流Ijを変化させることができる。

この場合、抵抗変化素子1に接続されている入力ワイヤ10及び出力ワイヤ11は、抵抗変化素子1から抵抗値(重み値;メモリ値;データ;情報)を読み出すための読出回路12として機能する。

このため、記憶装置9は、上述のように構成される抵抗変化素子1と、抵抗変化素子1に接続され、抵抗変化素子1へ情報の書き込みを行なう書込回路13と、抵抗変化素子1に接続され、抵抗変化素子1から情報の読み出しを行なう読出回路12とを備えることになる。

ディープラーニングは、多層のニューラルネットワークを用いた機械学習手法であり、現在、画像認識、音声認識などの分野に応用されている。

ここで言う「ニューラルネットワーク」は、データ入出力の役割を持つ人工ニューロンがシナプス結合により形成したネットワークを表す。

そして、シナプス結合の強度は、入力データの各要素を出力データに反映する際の重み値wと対応付けられる。

コンピュータ内で当該重み値付けを行なうために、その重み値をメモリに記憶させておく方法がある。

しかしながら、毎回、その重み値を読み出すことになり、処理速度低下、消費電力増大の招くことになる。

そこで、例えば図4に示すように、クロスバー構造でニューラルネットワークを模したデバイス(シナプスデバイス)が提案されている。

これは、入力側のナノワイヤ群(入力ワイヤ;m本;ここではm=4)、出力側のナノワイヤ群(出力ワイヤ;n本;ここではn=4)と、個々の入力ワイヤ−出力ワイヤ間に備えられる抵抗変化素子(m×n個)で構成されている。

つまり、抵抗変化素子の持つ抵抗値Rをもって重み値wを記憶することができる。この場合、一つのRについて一つのwが対応する。

実際には、入力ワイヤに電圧Vinputで入力した場合に、抵抗値Rの大小が、出力される応答電流Ioutputに反映される(次式参照)。

Ioutput=Vinput/R

この抵抗変化素子は、重み値を記憶するために不揮発性でなければならない。

このような抵抗変化素子が対応できる重み値の数は、例えば「0」と「1」の2値よりも「0」、「1」、「2」、…のような多値の方が、同じ規模のシナプスデバイスでより高精度の予測を可能とする。また、同様に、同じ精度の機械学習をより小規模のシナプスデバイスで遂行することが可能になる。

そこで、例えばリチウムイオン電池などで用いられている正極材料が、多値化が可能な材料(メモリ材料)として注目されている。

例えば、非特許文献1には、抵抗変化層の材料としてLixCoO2を用いた例が挙げられている。

このような抵抗変化素子では、抵抗変化層の中のリチウム量を制御するために、抵抗変化層のほかにイオン伝導層やイオン吸蔵放出層を設ける。

この場合、抵抗変化層とイオン吸蔵放出層の間に電気エネルギEappを与え、抵抗変化層中のリチウムイオン濃度を変化させることで、抵抗変化層の持つ抵抗値(重み値)を変えることができる。

Eapp=VappIapptapp

ここで、Vappは印加電圧、Iappは印加電流、tappは印加時間である。Vappは、この全固体電池が持つ開回路電圧Vbatteryと、イオン伝導層内の伝導速度に影響を与える過電圧Voverpotentialを用いて、以下の式の様に表現できる。

Vapp=Vbattery+Voverpotential

しかしながら、抵抗変化層やイオン吸蔵放出層に用いる材料を適切に選択しないと、Vbatteryが大きくなることで、書き込み時に印加する電圧Vappが大きくなり、書き込み時に必要な電気エネルギが大きくなってしまうことがわかった。

このように、抵抗変化層が持つ抵抗値を書き換えるには、全固体電池が持つ電圧に匹敵する電圧を印加する必要があるため、必要電圧を低減するためには、全固体電池が持つ電圧を低減することが必要である。

つまり、抵抗変化層、イオン吸蔵放出層を適切に選択することで、Vbattery、およびVappを低減することができる。

これは、抵抗値に相当する重み値wを書き込む(書き換える)のに必要なエネルギEappを低減し、さらには機械学習を遂行するのに必要な電力の低減にも寄与する。

したがって、本実施形態にかかる抵抗変化素子及びその製造方法、記憶装置は、書き込み時に印加する電圧を低減し、書き込み時に必要な電気エネルギを低減することができるという効果を有する。

例えば、以下のようにして抵抗変化素子1を作製し、その効果を確認したところ、Voverpotentialを0.1V未満とした場合、抵抗値(重み値)の書き込み(書き換え)に必要な電気エネルギを、例えば非特許文献1に記載されているものと比較して約3%以下に低減できることが確認できた。

つまり、まず、SiO2膜を備えるSi基板(SiO2/Si基板)2上に、第1電極6及び第2電極7としてのPt電極(例えば膜厚約50nm)、Li4Ti5O12で表される組成を有する抵抗変化層3(例えば厚さ約100nm)、LiPONで表される組成を有するイオン伝導層4(例えば厚さ約500nm)、Li4Ti5O12で表される組成を有するイオン吸蔵放出層5(厚さ約100nm)の順に成膜する。

ここで、金属リチウムの量はLi4Ti5O12に対して3当量相当とする。この時点で、次式のように、イオン吸蔵放出層5と金属リチウムが反応し、イオン吸蔵放出層5はLi7Ti5O12で表される組成を有するものとなる。

Li4Ti5O12+3Li→Li7Ti5O12

そして、Li7Ti5O12で表される組成を有するイオン吸蔵放出層5上に、第3電極8としてのPt電極を成膜する。

次に、このようにして作製した抵抗変化素子1の効果を確認した。

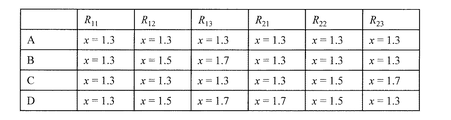

ここでは、一対の書込電極である第2電極7と第3電極8の間に、例えば約0.1V未満の電圧を印加して、抵抗変化層3を構成するLi4+xTi5O12のxの値を約1.3、約1.5、約1.7の3つの状態に変化させ、それぞれの状態で一対の読出電極である第1電極6と第2電極7の間に、例えば約10mVの電圧を印加して、これに応じて流れる電流値を測定した。

そして、Li4+xTi5O12で表される組成を有する抵抗変化層3中のxの値をx=1.3、x=1.5、x=1.7と変化させた状態でそれぞれ観測される電流値Ix=1.3、Ix=1.5、Ix=1.7を測定したところ、約0.52μA、約0.60μA、約0.67μAであり、有意差のある違いが表れた。

そして、x=1.3、x=1.5、x=1.7の間で状態を変化させる際に必要な電圧は約0.1V未満であるため、抵抗値(重み値)の書き込み(書き換え)に必要な電気エネルギを、例えば非特許文献1に記載されているものと比較して約3%以下に低減できることが確認できた。

次に、第2具体例として、以下のようにして、抵抗変化層3及びイオン吸蔵放出層5にZnxMnO2(0≦x≦0.5)で表される材料を用いた抵抗変化素子1を作製し、その効果を確認した。

ここで、金属亜鉛の量はMnO2に対して0.5当量相当とする。そして、約40℃〜約60℃の環境下に置き、しばらくすると、次式のように、イオン吸蔵放出層5と金属亜鉛が反応し、イオン吸蔵放出層5はZnxMnO2(x=0.5)、即ち、Zn0.5MnO2で表される組成を有するものとなる。

MnO2+0.5Zn→Zn0.5MnO2

そして、Zn0.5MnO2で表される組成を有するイオン吸蔵放出層5上に、第3電極8としてのPt電極を成膜する。

次に、このようにして作製した抵抗変化素子1の効果を確認した。

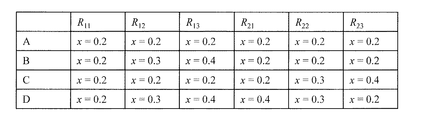

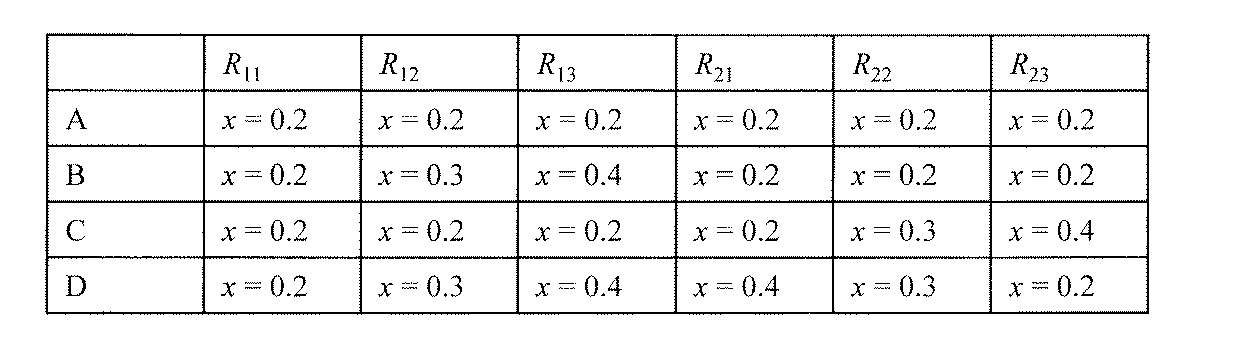

ここでは、一対の書込電極である第2電極7と第3電極8の間に、例えば約0.1V未満の電圧を印加して、抵抗変化層3を構成するZnxMnO2のxの値を約0.2、約0.3、約0.4の3つの状態に変化させ、それぞれの状態で一対の読出電極である第1電極6と第2電極7の間に、例えば約10mVの電圧を印加して、これに応じて流れる電流値を測定した。

そして、ZnxMnO2で表される組成を有する抵抗変化層3中のxの値をx=0.2、x=0.3、x=0.4と変化させた状態でそれぞれ観測される電流値Ix=1.3、Ix=1.5、Ix=1.7を測定したところ、有意差のある違いが表れた。

そして、x=0.2、x=0.3、x=0.4の間で状態を変化させる際に必要な電圧は約0.1V未満であるため、抵抗値(重み値)の書き込み(書き換え)に必要な電気エネルギを、例えば非特許文献1に記載されているものと比較して約3%以下に低減できることが確認できた。

次に、上述のようにして作製した抵抗変化素子1(例えば図1参照)を用い、ニューラルネットワーク9を作製し(例えば図3参照)、その効果を確認した。

次に、上述の第2具体例の抵抗変化素子1、即ち、抵抗変化層3及びイオン吸蔵放出層5にZnxMnO2で表される材料を用いて作製した抵抗変化素子(例えば図1参照)を用い、同様に、2つの入力端子(入力ワイヤ)10A、10B、3つの出力端子(出力ワイヤ)11A〜11C、6つの抵抗変化素子R11、R12、R13、R21、R22、R23、6つの直流電源S11、S12、S13、S21、S22、S23を備えるニューラルネットワーク9を作製した(例えば図3参照)。

このように、上述のようにして作製した抵抗変化素子1を用いたニューラルネットワーク9が多値メモリとして機能することが確認できた。また、多値メモリの効果を利用して、2値しか取れないメモリと比較して、より少ない素子数でより多様な出力電流を検出できることが確認できた。

2 基板

3 抵抗変化層

4 イオン伝導層

5 イオン吸蔵放出層

6 第1電極(読出電極、入力電極)

7 第2電極(読出電極、出力電極、書込電極、引出電極)

8 第3電極(書込電極、引出電極)

9 ニューラルネットワーク(記憶装置)

10、10A、10B 入力ワイヤ(入力端子)

11、11A〜11C 出力ワイヤ(出力端子)

12 読出回路

13 書込回路

R11〜Rmn、R11、R12、R13、R21、R22、R23 抵抗変化素子

S11〜Smn、S11、S12、S13、S21、S22、S23 直流電源

Claims (20)

- 少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層とを備え、

前記抵抗変化層と前記イオン吸蔵放出層は、構成元素が同一であって且つ組成比が同じであることを特徴とする抵抗変化素子。 - 少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層とを備え、

前記抵抗変化層と前記イオン吸蔵放出層は、構成元素が同一であり、

前記少なくとも1種類のイオンは、Liイオン、Znイオン、Naイオン、Kイオン、Mgイオン、Alイオン、Agイオン、Cuイオンのいずれかであることを特徴とする抵抗変化素子。 - 少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層とを備え、

前記抵抗変化層と前記イオン吸蔵放出層は、構成元素が同一であり、

前記少なくとも1種類のイオンは、Liイオンであることを特徴とする抵抗変化素子。 - 前記抵抗変化層及び前記イオン吸蔵放出層は、Li4+xTi5O12(0≦x≦3)で表される組成を有することを特徴とする、請求項3に記載の抵抗変化素子。

- 前記抵抗変化層及び前記イオン吸蔵放出層の少なくとも一方は、xの値が0<x≦3となるように調整されていることを特徴とする、請求項4に記載の抵抗変化素子。

- 少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層とを備え、

前記抵抗変化層と前記イオン吸蔵放出層は、構成元素が同一であり、

前記少なくとも1種類のイオンは、Znイオンであることを特徴とする抵抗変化素子。 - 前記抵抗変化層及び前記イオン吸蔵放出層は、ZnxMnO2(0≦x≦0.5)で表される組成を有することを特徴とする、請求項6に記載の抵抗変化素子。

- 前記抵抗変化層及び前記イオン吸蔵放出層の少なくとも一方は、xの値が0<x≦0.5となるように調整されていることを特徴とする、請求項7に記載の抵抗変化素子。

- 抵抗変化素子と、

前記抵抗変化素子に接続され、前記抵抗変化素子へ情報の書き込みを行なう書込回路と、

前記抵抗変化素子に接続され、前記抵抗変化素子から情報の読み出しを行なう読出回路とを備え、

前記抵抗変化素子は、

少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層とを備え、

前記抵抗変化層と前記イオン吸蔵放出層は、構成元素が同一であって且つ組成比が同じであることを特徴とする記憶装置。 - 抵抗変化素子と、

前記抵抗変化素子に接続され、前記抵抗変化素子へ情報の書き込みを行なう書込回路と、

前記抵抗変化素子に接続され、前記抵抗変化素子から情報の読み出しを行なう読出回路とを備え、

前記抵抗変化素子は、

少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層とを備え、

前記抵抗変化層と前記イオン吸蔵放出層は、構成元素が同一であり、

前記少なくとも1種類のイオンは、Liイオン、Znイオン、Naイオン、Kイオン、Mgイオン、Alイオン、Agイオン、Cuイオンのいずれかであることを特徴とする記憶装置。 - 抵抗変化素子と、

前記抵抗変化素子に接続され、前記抵抗変化素子へ情報の書き込みを行なう書込回路と、

前記抵抗変化素子に接続され、前記抵抗変化素子から情報の読み出しを行なう読出回路とを備え、

前記抵抗変化素子は、

少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層とを備え、

前記抵抗変化層と前記イオン吸蔵放出層は、構成元素が同一であり、

前記少なくとも1種類のイオンは、Liイオンであり、

前記抵抗変化層及び前記イオン吸蔵放出層は、Li4+xTi5O12(0≦x≦3)で表される組成を有することを特徴とする記憶装置。 - 抵抗変化素子と、

前記抵抗変化素子に接続され、前記抵抗変化素子へ情報の書き込みを行なう書込回路と、

前記抵抗変化素子に接続され、前記抵抗変化素子から情報の読み出しを行なう読出回路とを備え、

前記抵抗変化素子は、

少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層とを備え、

前記抵抗変化層と前記イオン吸蔵放出層は、構成元素が同一であり、

前記少なくとも1種類のイオンは、Znイオンであり、

前記抵抗変化層及び前記イオン吸蔵放出層は、ZnxMnO2(0≦x≦0.5)で表される組成を有することを特徴とする記憶装置。 - 少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層を形成する工程と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層を形成する工程と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層を形成する工程とを含み、

前記抵抗変化層を形成する工程及び前記イオン吸蔵放出層を形成する工程において、構成元素が同一であって且つ組成比が同じである前記抵抗変化層及び前記イオン吸蔵放出層をそれぞれ形成することを特徴とする抵抗変化素子の製造方法。 - 少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層を形成する工程と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層を形成する工程と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層を形成する工程とを含み、

前記抵抗変化層を形成する工程及び前記イオン吸蔵放出層を形成する工程において、構成元素が同一である前記抵抗変化層及び前記イオン吸蔵放出層をそれぞれ形成し、

前記少なくとも1種類のイオンは、Liイオン、Znイオン、Naイオン、Kイオン、Mgイオン、Alイオン、Agイオン、Cuイオンのいずれかであることを特徴とする抵抗変化素子の製造方法。 - 少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層を形成する工程と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層を形成する工程と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層を形成する工程とを含み、

前記抵抗変化層を形成する工程及び前記イオン吸蔵放出層を形成する工程において、構成元素が同一である前記抵抗変化層及び前記イオン吸蔵放出層をそれぞれ形成し、

前記少なくとも1種類のイオンは、Liイオンであることを特徴とする抵抗変化素子の製造方法。 - 前記抵抗変化層及び前記イオン吸蔵放出層は、Li 4+x Ti 5 O 12 (0≦x≦3)で表される組成を有することを特徴とする、請求項15に記載の抵抗変化素子の製造方法。

- 前記抵抗変化層及び前記イオン吸蔵放出層の少なくとも一方は、xの値が0<x≦3となるように調整されていることを特徴とする、請求項16に記載の抵抗変化素子の製造方法。

- 少なくとも1種類のイオンを吸蔵及び放出でき、前記少なくとも1種類のイオンの濃度に応じて抵抗が変化する抵抗変化層を形成する工程と、

前記少なくとも1種類のイオンを吸蔵及び放出できるイオン吸蔵放出層を形成する工程と、

前記抵抗変化層と前記イオン吸蔵放出層との間で、前記少なくとも1種類のイオンを伝導するイオン伝導層を形成する工程とを含み、

前記抵抗変化層を形成する工程及び前記イオン吸蔵放出層を形成する工程において、構成元素が同一である前記抵抗変化層及び前記イオン吸蔵放出層をそれぞれ形成し、

前記少なくとも1種類のイオンは、Znイオンであることを特徴とする抵抗変化素子の製造方法。 - 前記抵抗変化層及び前記イオン吸蔵放出層は、Zn x MnO 2 (0≦x≦0.5)で表される組成を有することを特徴とする、請求項18に記載の抵抗変化素子の製造方法。

- 前記抵抗変化層及び前記イオン吸蔵放出層の少なくとも一方は、xの値が0<x≦0.5となるように調整されていることを特徴とする、請求項19に記載の抵抗変化素子の製造方法。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2018/013706 WO2019187032A1 (ja) | 2018-03-30 | 2018-03-30 | 抵抗変化素子及びその製造方法、記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2019187032A1 JPWO2019187032A1 (ja) | 2021-01-14 |

| JP6915744B2 true JP6915744B2 (ja) | 2021-08-04 |

Family

ID=68061282

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020508810A Expired - Fee Related JP6915744B2 (ja) | 2018-03-30 | 2018-03-30 | 抵抗変化素子及びその製造方法、記憶装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20200411760A1 (ja) |

| JP (1) | JP6915744B2 (ja) |

| WO (1) | WO2019187032A1 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10943169B2 (en) * | 2017-03-07 | 2021-03-09 | International Business Machines Corporation | Battery-based neural network weights |

| WO2020138975A1 (ko) * | 2018-12-26 | 2020-07-02 | 한양대학교 에리카산학협력단 | 메모리 소자 및 그 제조 방법 |

| US11250315B2 (en) * | 2019-10-29 | 2022-02-15 | International Business Machines Corporation | Electrochemical device of variable electrical conductance |

| JP7578283B2 (ja) * | 2021-04-30 | 2024-11-06 | 国立研究開発法人物質・材料研究機構 | 変化信号部を強調するマルチチャネル電子素子、それを用いた回路およびその使用方法 |

| US20230079071A1 (en) * | 2021-09-15 | 2023-03-16 | Kabushiki Kaisha Toshiba | Variable resistance element, storage device, and neural network apparatus |

| JP2023043142A (ja) * | 2021-09-15 | 2023-03-28 | 株式会社東芝 | 抵抗変化素子、記憶装置およびニューラルネットワーク装置 |

| CN115050841A (zh) * | 2022-05-19 | 2022-09-13 | 中国科学院物理研究所 | 基于锌离子脱嵌调节电阻的三端电化学器件 |

| JP7830388B2 (ja) * | 2023-07-21 | 2026-03-16 | 株式会社東芝 | 抵抗変化素子、記憶装置、及びニューラルネットワーク装置 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4839700A (en) * | 1987-12-16 | 1989-06-13 | California Institute Of Technology | Solid-state non-volatile electronically programmable reversible variable resistance device |

| JPH0770731B2 (ja) * | 1990-11-22 | 1995-07-31 | 松下電器産業株式会社 | 電気可塑性素子 |

| US7494742B2 (en) * | 2004-01-06 | 2009-02-24 | Cymbet Corporation | Layered barrier structure having one or more definable layers and method |

| US7354793B2 (en) * | 2004-08-12 | 2008-04-08 | Micron Technology, Inc. | Method of forming a PCRAM device incorporating a resistance-variable chalocogenide element |

| JP2006120702A (ja) * | 2004-10-19 | 2006-05-11 | Matsushita Electric Ind Co Ltd | 可変抵抗素子および半導体装置 |

| JP5227544B2 (ja) * | 2007-07-12 | 2013-07-03 | 株式会社日立製作所 | 半導体装置 |

| US8441060B2 (en) * | 2008-10-01 | 2013-05-14 | Panasonic Corporation | Nonvolatile memory element and nonvolatile memory device incorporating nonvolatile memory element |

| KR20130126325A (ko) * | 2012-05-11 | 2013-11-20 | 에스케이하이닉스 주식회사 | 가변 저항 메모리 장치 및 그 제조 방법 |

| US9425237B2 (en) * | 2014-03-11 | 2016-08-23 | Crossbar, Inc. | Selector device for two-terminal memory |

| JP6572063B2 (ja) * | 2015-08-26 | 2019-09-04 | 富士フイルム株式会社 | 全固体二次電池、全固体二次電池用電極シート及びこれらの製造方法 |

| US9553263B1 (en) * | 2015-11-06 | 2017-01-24 | Micron Technology, Inc. | Resistive memory elements including buffer materials, and related memory cells, memory devices, electronic systems |

| KR102485485B1 (ko) * | 2016-01-08 | 2023-01-06 | 에스케이하이닉스 주식회사 | 스위칭 소자 및 이를 포함하는 저항 변화 메모리 장치 |

| US10943169B2 (en) * | 2017-03-07 | 2021-03-09 | International Business Machines Corporation | Battery-based neural network weights |

| US10079341B1 (en) * | 2017-03-13 | 2018-09-18 | International Business Machines Corporation | Three-terminal non-volatile multi-state memory for cognitive computing applications |

| US10944053B2 (en) * | 2018-03-28 | 2021-03-09 | University Of Cincinnati | Systems and methods for gated-insulator reconfigurable non-volatile memory devices |

-

2018

- 2018-03-30 WO PCT/JP2018/013706 patent/WO2019187032A1/ja not_active Ceased

- 2018-03-30 JP JP2020508810A patent/JP6915744B2/ja not_active Expired - Fee Related

-

2020

- 2020-09-11 US US17/017,746 patent/US20200411760A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| JPWO2019187032A1 (ja) | 2021-01-14 |

| US20200411760A1 (en) | 2020-12-31 |

| WO2019187032A1 (ja) | 2019-10-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6915744B2 (ja) | 抵抗変化素子及びその製造方法、記憶装置 | |

| US20190214082A1 (en) | High speed thin film two terminal resistive memory | |

| CN106654009A (zh) | 一种忆阻器及其应用 | |

| Banerjee et al. | Variability improvement of tio x/al2o3 bilayer nonvolatile resistive switching devices by interfacial band engineering with an ultrathin al2o3 dielectric material | |

| CN104051545B (zh) | 基于pn异质结构的忆阻器及其制备方法 | |

| Lee et al. | Two-terminal structured synaptic device using ionic electrochemical reaction mechanism for neuromorphic system | |

| JP2013016529A5 (ja) | ||

| CN104756246B (zh) | 具有基于阳离子的导电氧化物元件的低电压嵌入式存储器 | |

| Ismail et al. | Unveiling the potential of HfO2/WS2 bilayer films: robust analog switching and synaptic emulation for advanced memory and neuromorphic computing | |

| CN106299114A (zh) | 一种忆阻器 | |

| WO2019210156A1 (en) | Resistive switching devices using cation intercalation | |

| US10586591B2 (en) | High speed thin film two terminal resistive memory | |

| Kim et al. | Transition of short-term to long-term memory of Cu/TaOx/CNT conductive bridge random access memory for neuromorphic engineering | |

| US9685610B2 (en) | Method for producing a resistive random access memory | |

| JP7116377B2 (ja) | 2つのメタ安定相の間の可逆介在イオン移動に基づくメモリスタ・デバイス | |

| US20100108975A1 (en) | Non-volatile memory cell formation | |

| US10777267B2 (en) | High speed thin film two terminal resistive memory | |

| JP7047579B2 (ja) | 抵抗変化素子及びその製造方法、記憶装置 | |

| CN112018236A (zh) | 一种基于pzt的忆阻器件、其制备方法及其应用 | |

| Kozicki et al. | Programmable metallization cells in memory and switching applications | |

| CN112687794B (zh) | 一种具有自修复能力的柔性忆阻器及制备方法 | |

| Rahaman et al. | Comparison of resistive switching characteristics using copper and aluminum electrodes on GeOx/W cross-point memories | |

| JP2019165161A (ja) | 抵抗変化素子及びその製造方法、記憶装置 | |

| Valov et al. | (Keynote) atomic scale and Interface interactions in redox-based resistive switching memories | |

| Li et al. | Redox transistors based on TiO2 for analogue neuromorphic computing |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200514 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210330 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210517 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210615 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210628 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6915744 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |