JP6889872B2 - 半導体素子の駆動回路、半導体素子の駆動方法、およびモータ制御装置 - Google Patents

半導体素子の駆動回路、半導体素子の駆動方法、およびモータ制御装置 Download PDFInfo

- Publication number

- JP6889872B2 JP6889872B2 JP2019568522A JP2019568522A JP6889872B2 JP 6889872 B2 JP6889872 B2 JP 6889872B2 JP 2019568522 A JP2019568522 A JP 2019568522A JP 2019568522 A JP2019568522 A JP 2019568522A JP 6889872 B2 JP6889872 B2 JP 6889872B2

- Authority

- JP

- Japan

- Prior art keywords

- speed

- control

- voltage

- switching

- semiconductor element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02P—CONTROL OR REGULATION OF ELECTRIC MOTORS, ELECTRIC GENERATORS OR DYNAMO-ELECTRIC CONVERTERS; CONTROLLING TRANSFORMERS, REACTORS OR CHOKE COILS

- H02P23/00—Arrangements or methods for the control of AC motors characterised by a control method other than vector control

- H02P23/20—Controlling the acceleration or deceleration

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/08—Circuits specially adapted for the generation of control voltages for semiconductor devices incorporated in static converters

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02P—CONTROL OR REGULATION OF ELECTRIC MOTORS, ELECTRIC GENERATORS OR DYNAMO-ELECTRIC CONVERTERS; CONTROLLING TRANSFORMERS, REACTORS OR CHOKE COILS

- H02P23/00—Arrangements or methods for the control of AC motors characterised by a control method other than vector control

- H02P23/03—Arrangements or methods for the control of AC motors characterised by a control method other than vector control specially adapted for very low speeds

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02P—CONTROL OR REGULATION OF ELECTRIC MOTORS, ELECTRIC GENERATORS OR DYNAMO-ELECTRIC CONVERTERS; CONTROLLING TRANSFORMERS, REACTORS OR CHOKE COILS

- H02P27/00—Arrangements or methods for the control of AC motors characterised by the kind of supply voltage

- H02P27/04—Arrangements or methods for the control of AC motors characterised by the kind of supply voltage using variable-frequency supply voltage, e.g. inverter or converter supply voltage

- H02P27/06—Arrangements or methods for the control of AC motors characterised by the kind of supply voltage using variable-frequency supply voltage, e.g. inverter or converter supply voltage using DC to AC converters or inverters

- H02P27/08—Arrangements or methods for the control of AC motors characterised by the kind of supply voltage using variable-frequency supply voltage, e.g. inverter or converter supply voltage using DC to AC converters or inverters with pulse width modulation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/04—Modifications for accelerating switching

- H03K17/041—Modifications for accelerating switching without feedback from the output circuit to the control circuit

- H03K17/04106—Modifications for accelerating switching without feedback from the output circuit to the control circuit in field-effect transistor switches

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/04—Modifications for accelerating switching

- H03K17/042—Modifications for accelerating switching by feedback from the output circuit to the control circuit

- H03K17/04206—Modifications for accelerating switching by feedback from the output circuit to the control circuit in field-effect transistor switches

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/16—Modifications for eliminating interference voltages or currents

- H03K17/161—Modifications for eliminating interference voltages or currents in field-effect transistor switches

- H03K17/165—Modifications for eliminating interference voltages or currents in field-effect transistor switches by feedback from the output circuit to the control circuit

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0003—Details of control, feedback or regulation circuits

- H02M1/0029—Circuits or arrangements for limiting the slope of switching signals, e.g. slew rate

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0048—Circuits or arrangements for reducing losses

- H02M1/0054—Transistor switching losses

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B70/00—Technologies for an efficient end-user side electric power management and consumption

- Y02B70/10—Technologies improving the efficiency by using switched-mode power supplies [SMPS], i.e. efficient power electronics conversion e.g. power factor correction or reduction of losses in power supplies or efficient standby modes

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Power Conversion In General (AREA)

- Inverter Devices (AREA)

Description

まず、図1を参照しつつ、本実施形態の半導体素子の駆動回路の制御構成の一例について説明する。

次に、上記図1で示した本実施形態の駆動回路1の具体的な実装例である回路図を図2に示す。この図2において、上記駆動電圧切替部2は、いわゆるプッシュプル回路21で構成されており、制御信号がHレベルである場合には駆動電圧を+Vcc電位で出力し、制御信号がLレベルである場合には駆動電圧を0電位で出力する。

上述したようにMOSFET(この場合は主回路MOSFET100)などの半導体素子は、主回路における大電流の通電と遮断を切り替えるスイッチング素子に用いられる。このような半導体素子は、ゲート端子Gmとソース端子Sm間に付加するゲート電圧(制御電圧)の高さとその付加時間に応じて他のソース端子Smとドレイン端子Dmの間における主電流(つまり主回路MOSFET100のドレイン電流)の流通状態(通電、遮断)と通電量、及び主端子間電圧(つまり主回路MOSFET100のドレイン電圧)が変化する。そして例えばインバータ等の電力変換装置への適用を想定した場合は、モータ端子に発生するサージの回避などを理由として、主端子間電圧の増減変化期間を所定時間以上に確保する規格が規定されている。

まず、主回路MOSFET100の時系列制御特性とスイッチングロスについて詳細に説明するために、図3に示すような比較例の駆動回路91を適用した場合について説明する。この図3に示す比較例の駆動回路91においては、上記図2に示した本実施形態の駆動回路1と比較して各タイミング調整回路61,62と、各増速制御用MOSFET41,42と、各加算器43,44と、通電検出部7と、通電切替回路81を備えていない点で相違している。つまり、比較例の駆動回路91は、駆動電圧切替部2のプッシュプル回路21が制御信号に応じて切り替えて出力する+Vcc電位と0電位の各駆動電圧を、それぞれ低速制御部3であるゲート抵抗31の電流制限によりゲート電圧が低速で増減変化するよう主回路MOSFET100のゲート端子Gmに入力するだけの構成となる。このような比較例の駆動回路91で主回路MOSFET100をターンON制御した場合のシーケンスタイムチャートを図4に、ターンOFF制御した場合のシーケンスタイムチャートを図5にそれぞれ示す。

以下、本実施形態の駆動回路1が備える増速制御の機能について説明する。まず図6は、上記図2に示した本実施形態の駆動回路1のうちターンON制御に対応して機能する部分だけを抜き出した部分回路図を示し、図7はそのターンONシーケンスのタイムチャートを示している。

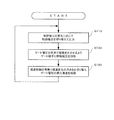

本実施形態の駆動回路1による制御フローを図10に示す。この図10に示すフローチャートは、上記図1に示した駆動回路1による主回路MOSFET100の駆動方法を、当該駆動回路1における各部の機能で逐次処理したとみなした場合の処理手順を示したものである。

以上説明したように、本実施形態の半導体素子の駆動回路1は、制御信号の変化に応じて出力する駆動電圧を切り替える駆動電圧切替部2と、主回路MOSFET100のゲート電圧を低速で増減変化させるようそのゲート端子Gmにゲート電圧を印加させる低速制御部3と、低速制御部3によるゲート電圧の変化速度を増速させる増速制御部4と、増速制御部4による増速制御の有無と増速変化の大きさを切り替える増速切替部5と、を有している。

上記実施形態で説明したように、通電検出部7は、主回路MOSFET100が接続する主回路において主電流の通電量が増減変化した際に、その潜在インダクタンス成分によって当該主回路に生じる変化量に応じた電圧を検出する回路で構成してもよい。しかしながら、主回路MOSFET100のモジュールパッケージ内の回路配線では、主電流の増減変化状態を検出するのに必要な潜在インダクタンスが得られない場合がある。この場合には、主回路MOSFET100のモジュールパッケージの外部において主回路に相当する主電流通電配線に対して通電検出部7を配置することが考えられる。以下においては、そのように主回路MOSFET100のモジュールパッケージの外部に配置する場合の通電検出部7の実装構成例について説明する。

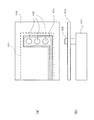

図11は、通電検出部7をいわゆるサーチコイルで実装する場合の構成例を示しており、図11(a)はサーチコイルを備えた回路基板の平面図、図11(b)はその回路基板及び装着した主回路MOSFETモジュールパッケージの側面図を示している。この図11において、主回路MOSFETモジュールパッケージ101は、その内部で主回路に接続するパッケージ端子102(図示する例では3本)が回路基板103を直交して貫通するよう固定され、主電流は回路基板103を貫通して図示しない配線へ流れるよう構成されている。そしてそのパッケージ端子102に対し、その主電流の通電方向(つまり円柱形状にあるパッケージ端子102の軸方向)を軸とした軸周りに包囲する配置で回路基板103の表面に配線されたパターン配線104がサーチコイルとして機能する。なお、このサーチコイルのパターン配線104は、図示するように主回路MOSFETモジュールパッケージ101と逆側の回路基板103の表面に配線する以外にも、主回路MOSFETモジュールパッケージ101と同じ側の回路基板103の表面に配線してもよい(図示省略)。このように通電検出部7をサーチコイルで実装することで、主回路MOSFETモジュールパッケージ101の内部配線レイアウトによらず安定した主電流の増減変化状態の検出機能を安価に実装できる。

図12は、通電検出部7をトランスで実装する場合の構成例を示しており、図12(a)はトランスを備えた回路基板の平面図(図12(b)中の矢視XIIa−XIIaの断面図)、図12(b)はその回路基板の側断面図(図12(a)中の矢視XIIb−XIIbの断面図)を示している。この図12において、回路基板103には主電流が通電する主回路パターン配線105が配線されており、その通電方向を軸とした軸周りに包囲する配置で環状の磁性体コア106が回路基板103を貫通するよう設けられている。そして、その磁性体コア106の通磁方向(つまり環状にある磁性体コア106の周方向)を軸とした軸周りに包囲する配置で回路基板103の表面に検出用パターン配線107が配線されている。これら主回路パターン配線105と、磁性体コア106と、検出用パターン配線107の組合せがトランスとして機能する。なお、検出用パターン配線107は、図示するように主回路パターン配線105と同じ側の回路基板103の表面に配線する以外にも、主回路パターン配線105と逆側の回路基板103の表面に配線してもよい(図示省略)。このように通電検出部7をトランスで実装することでも、主回路MOSFETモジュールパッケージ101の内部配線レイアウトによらず安定した主電流の増減変化状態の検出機能を安価に実装できる。

上記実施形態の駆動回路1の適用例としては、例えば直流電力を所定周波数の交流電力にPWM電力変換し、これを駆動電力としてモータ(回転型、直動型)に給電するモータ制御装置などがある。以下、このモータ制御装置の構成例について説明する。

2 駆動電圧切替部

3 低速制御部

4 増速制御部

5 増速切替部

6 タイミング調整部

7 通電検出部

8 通電切替部

21 プッシュプル回路(駆動電圧切替部)

31 ゲート抵抗(低速制御部、制御抵抗)

41 ターンON増速制御用MOSFET(増速制御部、半導体スイッチング素子)

42 ターンOFF増速制御用MOSFET(増速制御部、半導体スイッチング素子)

61 ターンONタイミング調整回路(タイミング調整部)

62 ターンOFFタイミング調整回路(タイミング調整部)

81 通電切替回路(通電切替部)

100 主回路MOSFET(半導体素子)

103 回路基板

104 パターン配線

105 主回路パターン配線

106 磁性体コア

107 検出用パターン配線

224 制御回路(制御部)

Gm 主回路MOSFETのゲート端子(制御端子)

Dm 主回路MOSFETのドレイン端子(主端子)

Sm 主回路MOSFETのソース端子(主端子)

Claims (12)

- 主電流を通電する一対の主端子と前記主電流の流通状態を制御する制御電圧を付加する制御端子とを備える半導体素子に対し、入力される制御信号の変化に対応して前記制御電圧の経時的増減変化を制御する半導体素子の駆動回路であって、

前記制御信号の変化に応じて出力する駆動電圧を切り替える駆動電圧切替部と、

前記制御電圧を低速で増減変化させる低速制御部と、

前記低速制御部による前記制御電圧の変化速度を増速させる増速制御部と、

前記増速制御部による増速制御の有無と増速変化の大きさを切り替える増速切替部と、

を有することを特徴とする半導体素子の駆動回路。 - 前記増速切替部は、

前記駆動電圧切替部による前記駆動電圧の切り替え後から所定時間経過した切替タイミングで前記増速制御部による増速制御の有無を切り替えるタイミング調整部を有していることを特徴とする請求項1記載の半導体素子の駆動回路。 - 前記切替タイミングは、

前記半導体素子における前記一対の主端子の間の主端子間電圧の増減変化期間中に設定されることを特徴とする請求項2記載の半導体素子の駆動回路。 - 前記増速切替部は、

前記半導体素子をターンONする場合には、前記切替タイミングで前記増速制御部の増速制御を有りから無しに切り替えることを特徴とする請求項3記載の半導体素子の駆動回路。 - 前記増速切替部は、

前記半導体素子をターンOFFする場合には、前記切替タイミングで前記増速制御部の増速制御を無しから有りに切り替えることを特徴とする請求項3記載の半導体素子の駆動回路。 - 前記増速切替部は、

前記主電流の増減変化状態を検出する通電検出部と、

前記通電検出部が増減変化状態を検出した際に前記増速制御部による増速制御の増速変化を大きくさせるよう切り替える通電切替部と、

を有することを特徴とする請求項1乃至5のいずれか1項に記載の半導体素子の駆動回路。 - 前記通電検出部は、

前記主端子に対してその通電方向を軸とした軸周りに包囲する配置の回路基板上のパターン配線であることを特徴とする請求項6記載の半導体素子の駆動回路。 - 前記通電検出部は、

回路基板上の前記主電流のパターン配線に対してその通電方向を軸とした軸周りに包囲する配置の磁性体コアと、

前記磁性体コアに対してその通磁方向を軸とした軸周りに包囲する回路基板上のパターン配線とを有していることを特徴とする請求項6記載の半導体素子の駆動回路。 - 前記低速制御部は、

前記増速制御部による増速制御時よりも増速変化が小さくなるよう前記制御端子の電流を制限する制御抵抗であることを特徴とする請求項1乃至8のいずれか1項に記載の半導体素子の駆動回路。 - 前記増速制御部は、

前記制御端子へ追加する電流の付加と非付加の切り替えとその電流量を制御する半導体スイッチング素子であることを特徴とする請求項1乃至9のいずれか1項に記載の半導体素子の駆動回路。 - 直流電力を交流に電力変換してモータに給電するモータ制御装置であって、

請求項1乃至10のいずれか1項に記載の半導体素子の駆動回路と、

前記主電流の流通状態の制御により前記電力変換を行う前記半導体素子と、

前記制御信号を出力する制御部と、

を有することを特徴とするモータ制御装置。 - 主電流を通電する一対の主端子と前記主電流の流通状態を制御する制御電圧を付加する制御端子とを備える半導体素子に対し、入力される制御信号の変化に対応して前記制御電圧の経時的増減変化を制御する半導体素子の駆動方法であって、

前記制御信号の変化に応じて出力する駆動電圧を切り替えることと、

前記制御電圧を低速で増減変化させることと、

前記制御電圧の変化速度を増速させることと、

増速制御の有無と増速変化の大きさを切り替えることと、

を実行することを特徴とする半導体素子の駆動方法。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2018/003608 WO2019150555A1 (ja) | 2018-02-02 | 2018-02-02 | 半導体素子の駆動回路、半導体素子の駆動方法、およびモータ制御装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2019150555A1 JPWO2019150555A1 (ja) | 2020-12-03 |

| JP6889872B2 true JP6889872B2 (ja) | 2021-06-18 |

Family

ID=67479727

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019568522A Active JP6889872B2 (ja) | 2018-02-02 | 2018-02-02 | 半導体素子の駆動回路、半導体素子の駆動方法、およびモータ制御装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US11342832B2 (ja) |

| EP (1) | EP3748826A4 (ja) |

| JP (1) | JP6889872B2 (ja) |

| CN (1) | CN111615783B (ja) |

| WO (1) | WO2019150555A1 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN114865891A (zh) * | 2022-05-31 | 2022-08-05 | 广东美的白色家电技术创新中心有限公司 | 一种驱动电路及驱动电路控制方法、装置及存储介质 |

| US12191825B2 (en) * | 2022-06-09 | 2025-01-07 | Diodes Incorporated | Dynamic control of output driver in a switching amplifier |

| US20250105760A1 (en) * | 2023-09-21 | 2025-03-27 | Allegro Microsystems, Llc | Active dc bus discharge |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4766477B2 (ja) * | 2004-04-06 | 2011-09-07 | 三菱電機株式会社 | 電流検出装置およびそれを備えた電力変換装置 |

| JP4713347B2 (ja) | 2006-01-13 | 2011-06-29 | 株式会社日立製作所 | 半導体素子の駆動回路 |

| JP4816139B2 (ja) * | 2006-02-27 | 2011-11-16 | 株式会社日立製作所 | パワー半導体スイッチング素子の駆動回路 |

| JP5881477B2 (ja) * | 2012-03-06 | 2016-03-09 | 三菱電機株式会社 | スイッチング素子駆動回路 |

| JP6362996B2 (ja) * | 2014-10-24 | 2018-07-25 | 株式会社日立製作所 | 半導体駆動装置ならびにそれを用いた電力変換装置 |

| JP6375945B2 (ja) * | 2014-12-26 | 2018-08-22 | 日産自動車株式会社 | スイッチング装置 |

| JP6451429B2 (ja) * | 2015-03-16 | 2019-01-16 | 株式会社デンソー | スイッチング素子の駆動装置 |

| JP6836342B2 (ja) * | 2016-06-22 | 2021-02-24 | ルネサスエレクトロニクス株式会社 | 駆動装置および電力供給システム |

-

2018

- 2018-02-02 JP JP2019568522A patent/JP6889872B2/ja active Active

- 2018-02-02 WO PCT/JP2018/003608 patent/WO2019150555A1/ja not_active Ceased

- 2018-02-02 EP EP18903189.1A patent/EP3748826A4/en active Pending

- 2018-02-02 CN CN201880086589.8A patent/CN111615783B/zh active Active

-

2020

- 2020-07-23 US US16/936,816 patent/US11342832B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN111615783B (zh) | 2023-10-10 |

| EP3748826A1 (en) | 2020-12-09 |

| US20200350813A1 (en) | 2020-11-05 |

| US11342832B2 (en) | 2022-05-24 |

| CN111615783A (zh) | 2020-09-01 |

| EP3748826A4 (en) | 2021-09-08 |

| JPWO2019150555A1 (ja) | 2020-12-03 |

| WO2019150555A1 (ja) | 2019-08-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5267616B2 (ja) | 駆動制御装置 | |

| CN105103427B (zh) | 绝缘栅型半导体装置 | |

| JP6610679B2 (ja) | 電力変換装置 | |

| CN101147313A (zh) | 功率转换装置 | |

| CN110401335B (zh) | 驱动电路、功率模块以及电力变换系统 | |

| JP6582764B2 (ja) | 半導体素子の駆動装置 | |

| JP7051008B2 (ja) | 並列駆動装置及び電力変換装置 | |

| JP2018011467A (ja) | 半導体スイッチング素子のゲート駆動回路 | |

| JP6889872B2 (ja) | 半導体素子の駆動回路、半導体素子の駆動方法、およびモータ制御装置 | |

| KR100936427B1 (ko) | 전력 변환 장치 | |

| JP2008067593A (ja) | 絶縁ゲート型半導体スイッチ素子のゲート駆動回路 | |

| WO2015111154A1 (ja) | スイッチング回路、インバータ回路、及びモータ制御装置 | |

| JP7552550B2 (ja) | スイッチの過電流検出装置 | |

| US11050358B2 (en) | Power module with built-in drive circuit | |

| JP6705234B2 (ja) | インバータ装置の制御方法 | |

| JP2001025259A (ja) | Pwmインバーター装置 | |

| JP2008043003A (ja) | 電圧駆動型半導体素子のゲート駆動装置 | |

| WO2020044945A1 (ja) | スイッチの駆動回路 | |

| JP6717426B2 (ja) | 電力変換装置 | |

| KR20180106622A (ko) | 액티브 클램프 제어장치 | |

| CN113439384A (zh) | 电源装置、马达驱动装置、鼓风机、压缩机以及空调机 | |

| JP7063082B2 (ja) | スイッチング素子制御回路 | |

| JP2024118512A (ja) | 電力変換装置 | |

| JP2024118518A (ja) | 電力変換装置 | |

| JP2025047625A (ja) | 半導体駆動装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200618 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210423 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210506 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6889872 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |