JP6794635B2 - 駆動回路、駆動回路の制御方法および液体吐出装置 - Google Patents

駆動回路、駆動回路の制御方法および液体吐出装置 Download PDFInfo

- Publication number

- JP6794635B2 JP6794635B2 JP2016034988A JP2016034988A JP6794635B2 JP 6794635 B2 JP6794635 B2 JP 6794635B2 JP 2016034988 A JP2016034988 A JP 2016034988A JP 2016034988 A JP2016034988 A JP 2016034988A JP 6794635 B2 JP6794635 B2 JP 6794635B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- signal

- period

- drive circuit

- side transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000007788 liquid Substances 0.000 title claims description 19

- 238000000034 method Methods 0.000 title claims description 13

- 230000003321 amplification Effects 0.000 claims description 17

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 17

- 230000008859 change Effects 0.000 claims description 16

- 238000006073 displacement reaction Methods 0.000 claims description 2

- 238000010586 diagram Methods 0.000 description 39

- 239000003990 capacitor Substances 0.000 description 34

- 239000000976 ink Substances 0.000 description 34

- 239000000758 substrate Substances 0.000 description 21

- 238000006243 chemical reaction Methods 0.000 description 10

- 101150056836 Sctr gene Proteins 0.000 description 8

- 230000007423 decrease Effects 0.000 description 7

- 238000004458 analytical method Methods 0.000 description 6

- 230000007246 mechanism Effects 0.000 description 5

- 230000032258 transport Effects 0.000 description 5

- 230000002159 abnormal effect Effects 0.000 description 4

- 238000004891 communication Methods 0.000 description 4

- 230000005669 field effect Effects 0.000 description 4

- 230000010355 oscillation Effects 0.000 description 4

- 230000007723 transport mechanism Effects 0.000 description 4

- 230000003071 parasitic effect Effects 0.000 description 3

- 230000000903 blocking effect Effects 0.000 description 2

- 238000010304 firing Methods 0.000 description 2

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 230000001788 irregular Effects 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 239000013642 negative control Substances 0.000 description 2

- 239000013641 positive control Substances 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 241000379208 Latris Species 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 239000013013 elastic material Substances 0.000 description 1

- 239000004744 fabric Substances 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 230000013011 mating Effects 0.000 description 1

- 238000003801 milling Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 230000001568 sexual effect Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 230000002123 temporal effect Effects 0.000 description 1

- 238000011144 upstream manufacturing Methods 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/01—Details

- H03K3/012—Modifications of generator to improve response time or to decrease power consumption

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/04541—Specific driving circuit

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/04581—Control methods or devices therefor, e.g. driver circuits, control circuits controlling heads based on piezoelectric elements

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/04593—Dot-size modulation by changing the size of the drop

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/005—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by bringing liquid or particles selectively into contact with a printing material

- B41J2/01—Ink jet

- B41J2/015—Ink jet characterised by the jet generation process

- B41J2/04—Ink jet characterised by the jet generation process generating single droplets or particles on demand

- B41J2/045—Ink jet characterised by the jet generation process generating single droplets or particles on demand by pressure, e.g. electromechanical transducers

- B41J2/04501—Control methods or devices therefor, e.g. driver circuits, control circuits

- B41J2/04596—Non-ejecting pulses

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N30/00—Piezoelectric or electrostrictive devices

- H10N30/80—Constructional details

- H10N30/802—Circuitry or processes for operating piezoelectric or electrostrictive devices not otherwise provided for, e.g. drive circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K4/00—Generating pulses having essentially a finite slope or stepped portions

- H03K4/94—Generating pulses having essentially a finite slope or stepped portions having trapezoidal shape

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N30/00—Piezoelectric or electrostrictive devices

- H10N30/20—Piezoelectric or electrostrictive devices with electrical input and mechanical output, e.g. functioning as actuators or vibrators

- H10N30/204—Piezoelectric or electrostrictive devices with electrical input and mechanical output, e.g. functioning as actuators or vibrators using bending displacement, e.g. unimorph, bimorph or multimorph cantilever or membrane benders

- H10N30/2047—Membrane type

Landscapes

- Particle Formation And Scattering Control In Inkjet Printers (AREA)

- Amplifiers (AREA)

Description

そこで、本発明のいくつかの態様の目的の一つは、消費電力を改善した駆動回路、駆動回路の制御方法および液体吐出装置を提供することにある。

上記一態様に係る駆動回路によれば、D級増幅方式と比較して、ローパスフィルターが不要であるので、当該ローパスフィルターにおいて消費される電力を無視することができ、その分、低消費電力化が図られる。また、D級増幅方式のように、スイッチング動作だけであると、駆動信号の波形精度が低下しやすいが、上記一態様によれば、第2期間でのリニア動作によって波形精度の向上が図られる。

また、上記一態様に係る駆動回路において、前記駆動信号は、傾きに連続性を有する波形であり、前記第1期間は、前記駆動信号の電圧変化が相対的に大きい期間であり、前記第2期間は、前記駆動信号の電圧変化が相対的に小さき期間である構成としても良い。この構成によれば、傾きに連続性を有する波形については、例えば正弦波の極小・極大値付近のように、電圧変化が相対的に小さい期間では、リニア動作により精度良く再現することができる。

また、上記一態様に係る駆動回路において、前記第2期間のうち、前記駆動信号が所定の閾値以上の電圧の場合では、前記ハイサイドトランジスターがリニア動作し、前記ローサイドトランジスターがオフし、前記駆動信号が前記閾値よりも低い電圧の場合では、前記ローサイドトランジスターがリニア動作し、前記ハイサイドトランジスターがオフする構成としても良い。

この構成において、前記閾値は、前記駆動信号の電圧の最高値よりも低く、前記駆動信号の電圧の最低値よりも高くしても良い。

また、ここでいう液体吐出装置とは、液体を吐出するものであれば良く、これには後述する印刷装置のほかに、立体造形装置(いわゆる3Dプリンター)、捺染装置なども含まれる。

この図に示される印刷装置(その1)は、液体の一例であるインクを吐出することによって、紙などの媒体Pにインクドット群を形成し、これにより、画像(文字、図形等を含む)を印刷する液体吐出装置の一種である。

なお、印刷装置については、便宜的に符号を1で統一するが、後述するように、いくつかの態様が存在するので、区別するために印刷装置(その1)、印刷装置(その2)というように符号の代わりに括弧書を付与する場合がある。

移動機構6は、キャリッジ20を移動させるキャリッジモーター61と、両端が固定されたキャリッジガイド軸62と、キャリッジガイド軸62とほぼ平行に延在し、キャリッジモーター61により駆動されるタイミングベルト63と、を有している。

キャリッジ20は、キャリッジガイド軸62に往復動自在に支持されるとともに、タイミングベルト63の一部に固定されている。そのため、キャリッジモーター61によりタイミングベルト63を正逆走行させると、キャリッジ20がキャリッジガイド軸62に案内されて往復動する。

なお、キャリッジ20には、フレキシブルフラットケーブル190を介してメイン基板(この図では省略)から駆動信号を含む各種の制御信号等が供給される構成となっている。

なお、本実施形態において主走査は、キャリッジ20を移動させることで実行されるが、媒体Pを移動させることで実行しても良く、キャリッジ20と媒体Pとの双方を移動させても良い。要は、媒体Pとキャリッジ20(印刷ヘッド22)とが相対的に移動する構成であれば良い。

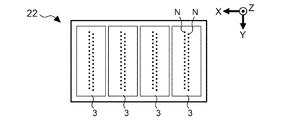

この図に示されるように、1個のヘッドユニット3では、複数のノズルNが2列で配列する。ここで、説明の便宜上、この2列をそれぞれノズル列Na、Nbとする。

このようにノズルNを、ノズル列Na、Nbの2列で、Y方向にピッチP1の半分だけシフトして配置させることにより、Y方向の解像度を、1列の場合と比較して実質的に倍に高めることができる。

なお、1個のヘッドユニット3におけるノズルNの個数を便宜的にm(mは2以上の整数)とする。

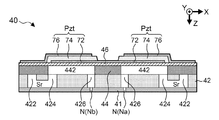

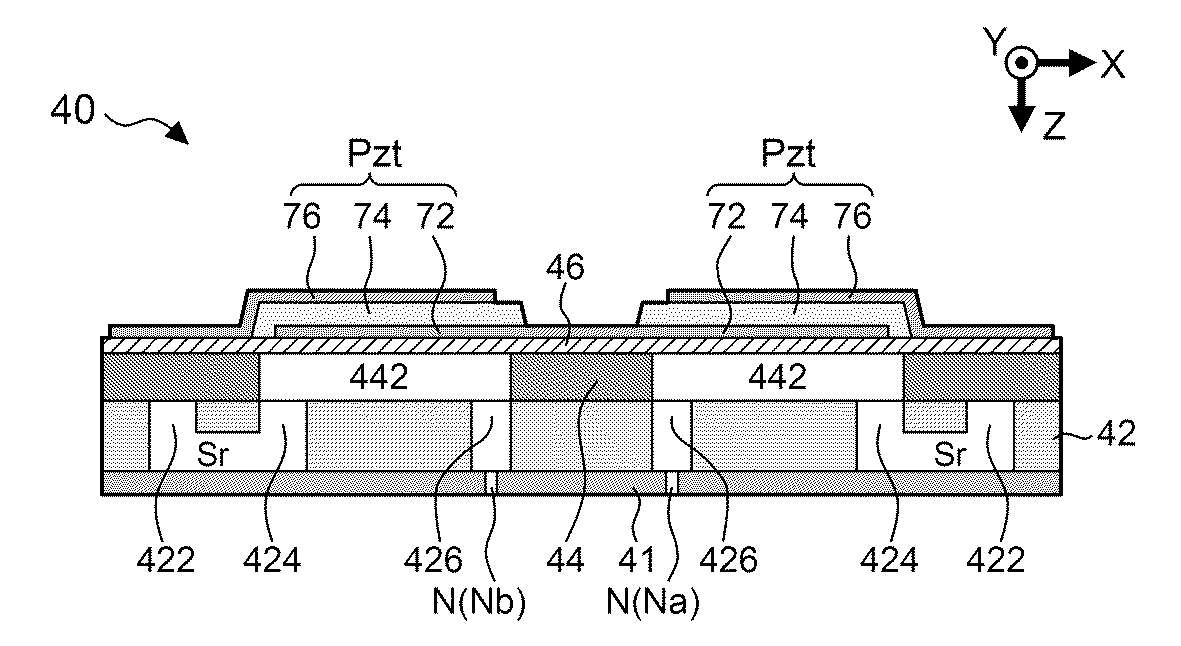

図3に示されるように、アクチュエーター基板40は、流路基板42のうち、Z方向の負側の面上に圧力室基板44と振動板46とが設けられる一方、Z方向の正側の面上にノズル板41が設置された構造体である。

アクチュエーター基板40の各要素は、概略的にはY方向に長尺な略平板状の部材であり、例えば接着剤等により互いに固定される。また、流路基板42および圧力室基板44は、例えばシリコンの単結晶基板で形成される。

振動板46のうち圧力室基板44とは反対側の表面には、ノズルN(キャビティ442)毎に圧電素子Pztが形成される。

また、この例では、圧電体74に対し、共通の駆動電極72を下層とし、個別の駆動電極76を上層としたが、逆に駆動電極72を上層とし、駆動電極76を下層とする構成としても良い。

なお、アクチュエーター基板40については、駆動ICを直接実装した構成でも良い。

このため、圧電素子Pztは、駆動電極72、76に印加された電圧に応じて、上または下方向に変位する。詳細には、駆動電極76を介して印加される駆動信号の電圧Voutが低くなると、圧電素子Pztにおける中央部分が両端部分に対して上方向に撓む一方、当該電圧Voutが高くなると、下方向に撓む構成となっている。

ここで、上方向に撓めば、キャビティ442の内部容積が拡大(圧力が減少)するので、インクが液体貯留室Srから引き込まれる一方、下方向に撓めば、キャビティ442の内部容積が縮小(圧力が増加)するので、縮小の程度によっては、インク滴がノズルNから吐出される。このように、圧電素子Pztに適切な駆動信号が印加されると、当該圧電素子Pztの変位によって、インクがノズルNから吐出される。このため、少なくとも圧電素子Pzt、キャビティ442、ノズルNによってインクを吐出する吐出部が構成されることになる。

この図に示されるように、印刷装置1は、メイン基板100にヘッドユニット3が接続された構成となっている。ヘッドユニット3は、アクチュエーター基板40と、駆動IC50とに大別される。

メイン基板100は、駆動IC50に、制御信号Ctrや、駆動信号COM−A、COM−Bを供給し、アクチュエーター基板40に、電圧VBS(オフセット電圧)の保持信号を、配線550を介して供給する。

なお、印刷装置1では、4個のヘッドユニット3が設けられ、メイン基板100が、4個のヘッドユニット3をそれぞれ独立に制御する。4個のヘッドユニット3では、吐出するインクの色以外において異なることがないので、以下においては便宜的に1個のヘッドユニット3について代表して説明することにする。

このうち、制御部110は、CPUや、RAM、ROMなどを有する一種のマイクロコンピューターであり、印刷対象となる画像データがホストコンピューター等から供給されたときに、所定のプログラムを実行して各部を制御するための各種の制御信号等を出力する。

なお、駆動信号COM−A、COM−B(アナログ変換後の信号ain、bin、インピーダンス変換前の信号Ain、Bin)については、それぞれ後述するように台形波形である。

なお、制御部110は、移動機構6および搬送機構8を制御するが、このような構成については既知であるので省略する。

各選択部520は、選択制御部510による指示にしたがって、駆動信号COM−A、COM−Bのいずれかを選択し(または、いずれも選択せずに)、電圧Voutの駆動信号として、対応する圧電素子Pztの一端に印加する。

アクチュエーター基板40には、上述したようにノズルN毎に圧電素子Pztが1個ずつ設けられる。圧電素子Pztの各々における他端は共通接続されて、当該他端には配線550を介してオフセット電圧生成回路130による電圧VBSが印加される。

そこで先に、駆動信号COM−A、COM−Bについて説明し、この後、駆動信号COM−A、COM−Bを選択するための選択制御部510および選択部520の詳細な構成について説明する。

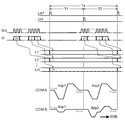

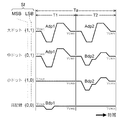

図に示されるように、駆動信号COM−Aは、印刷周期Taのうち、制御信号LATが出力されて(立ち上がって)から制御信号CHが出力されるまでの期間T1に配置された台形波形Adp1と、印刷周期Taのうち、制御信号CHが出力されてから次の制御信号LATが出力されるまでの期間T2に配置された台形波形Adp2とを繰り返す波形となっている。

本例では、駆動信号COM−A(信号Ain)の電圧の最高値をmaxとし、最低値をminとしたときに、便宜的にmax>Vth>Vcen>minとして説明する。なお、max>Vcen>Vth>minとしても良い。

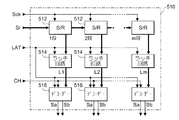

この図に示されるように、選択制御部510には、クロック信号Sck、印刷データSI、制御信号LAT、CHが供給される。選択制御部510では、シフトレジスタ(S/R)512とラッチ回路514とデコーダー516との組が、圧電素子Pzt(ノズルN)のそれぞれに対応して設けられている。

印刷データSIは、クロック信号Sckに同期してノズルN(圧電素子Pzt)毎に、媒体Pの搬送に合わせて供給される。当該印刷データSIを、ノズルNに対応して2ビット分、一旦保持するための構成がシフトレジスタ512である。

詳細には、m個の圧電素子Pzt(ノズル)の各々に対応した計m段のシフトレジスタ512が縦続接続されるとともに、図において左端に位置する1段のシフトレジスタ512に供給された印刷データSIが、クロック信号Sckにしたがって順次後段(下流側)に転送される構成となっている。

なお、図では、シフトレジスタ512を区別するために、印刷データSIが供給される上流側から順番に1段、2段、…、m段と表記している。

デコーダー516は、ラッチ回路514によってラッチされた2ビットの印刷データSIをデコードして、制御信号LATと制御信号CHとで規定される期間T1、T2ごとに、選択信号Sa、Sbを出力して、選択部520での選択を規定する。

この図において、ラッチされた2ビットの印刷データSIについては(MSB、LSB)と表記している。デコーダー516は、例えばラッチされた印刷データSIが(0、1)であれば、選択信号Sa、Sbの論理レベルを、期間T1ではそれぞれH、Lレベルで、期間T2ではそれぞれL、Hレベルで、出力するということを意味している。

なお、選択信号Sa、Sbの論理レベルについては、クロック信号Sck、印刷データSI、制御信号LAT、CHの論理レベルよりも、レベルシフター(図示省略)によって、高振幅論理にレベルシフトされる。

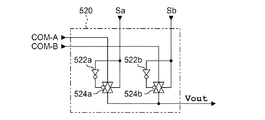

この図に示されるように、選択部520は、インバーター(NOT回路)522a、522bと、トランスファーゲート524a、524bとを有する。

デコーダー516からの選択信号Saは、トランスファーゲート524aにおいて丸印が付されていない正制御端に供給される一方で、インバーター522aによって論理反転されて、トランスファーゲート524aにおいて丸印が付された負制御端に供給される。同様に、選択信号Sbは、トランスファーゲート524bの正制御端に供給される一方で、インバーター522bによって論理反転されて、トランスファーゲート524bの負制御端に供給される。

トランスファーゲート524aの入力端には、駆動信号COM−Aが供給され、トランスファーゲート524bの入力端には、駆動信号COM−Bが供給される。トランスファーゲート524a、524bの出力端同士は、共通接続されるとともに、対応する圧電素子Pztの一端に接続される。

トランスファーゲート524aは、選択信号SaがHレベルであれば、入力端および出力端の間を導通(オン)させ、選択信号SaがLレベルであれば、入力端と出力端との間を非導通(オフ)させる。トランスファーゲート524bについても同様に選択信号Sbに応じて、入力端および出力端の間をオンオフさせる。

ここで、制御信号LATが立ち上がると、ラッチ回路514のそれぞれは、シフトレジスタ512に保持された印刷データSIを一斉にラッチする。図5において、L1、L2、…、Lm内の数字は、1段、2段、…、m段のシフトレジスタ512に対応するラッチ回路514によってラッチされた印刷データSIを示している。

すなわち、第1に、デコーダー516は、当該印刷データSIが(1、1)であって、大ドットのサイズを規定する場合、選択信号Sa、Sbを、期間T1においてH、Lレベルとし、期間T2においてもH、Lレベルとする。第2に、デコーダー516は、当該印刷データSIが(0、1)であって、中ドットのサイズを規定する場合、選択信号Sa、Sbを、期間T1においてH、Lレベルとし、期間T2においてL、Hレベルとする。第3に、デコーダー516は、当該印刷データSIが(1、0)であって、小ドットのサイズを規定する場合、選択信号Sa、Sbを、期間T1においてL、Lレベルとし、期間T2においてL、Hレベルとする。第4に、デコーダー516は、当該印刷データSIが(0、0)であって、非記録を規定する場合、選択信号Sa、Sbを、期間T1においてL、Hレベルとし、期間T2においてL、Lレベルとする。

印刷データSIが(1、1)であるとき、選択信号Sa、Sbは、期間T1においてH、Lレベルとなるので、トランスファーゲート524aがオンし、トランスファーゲート524bがオフする。このため、期間T1において駆動信号COM−Aの台形波形Adp1が選択される。選択信号Sa、Sbは期間T2においてもH、Lレベルとなるので、選択部520は、駆動信号COM−Aの台形波形Adp2を選択する。

このように期間T1において台形波形Adp1が選択され、期間T2において台形波形Adp2が選択されて、駆動信号として圧電素子Pztの一端に供給されると、当該圧電素子Pztに対応したノズルNから、中程度の量のインクが2回にわけて吐出される。このため、媒体Pにはそれぞれのインクが着弾し合体して、結果的に、印刷データSIで規定される通りの大ドットが形成されることになる。

したがって、ノズルから、中程度および小程度の量のインクが2回にわけて吐出される。このため、媒体Pには、それぞれのインクが着弾して合体して、結果的に、印刷データSIで規定された通りの中ドットが形成されることになる。

次に、選択信号Sa、Sbは期間T2においてL、Hレベルとなるので、駆動信号COM−Bの台形波形Bdp2が選択される。このため、ノズルNから、期間T2においてのみ小程度の量のインクが吐出されるので、媒体Pには、印刷データSIで規定された通りの小ドットが形成されることになる。

このため、期間T1においてノズルN付近のインクが微振動するのみであり、インクは吐出されないので、結果的に、ドットが形成されない、すなわち、印刷データSIで規定された通りの非記録になる。

なお、図5に示した駆動信号COM−A、COM−Bはあくまでも一例である。実際には、媒体Pの性質や搬送速度などに応じて、予め用意された様々な波形の組み合わせが用いられる。

また、ここでは、圧電素子Pztが、電圧の低下に伴って上方向に撓む例で説明したが、駆動電極72、76に印加する電圧を逆転させると、圧電素子Pztは、電圧の低下に伴って下向に撓むことになる。このため、圧電素子Pztが、電圧の低下に伴って下方向に撓む構成では、図に例示した駆動信号COM−A、COM−Bが、電圧Vcenを基準に反転した波形となる。

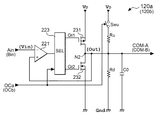

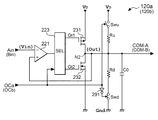

なお、駆動回路の符号については、駆動信号COM−Aを出力する側を120aで、駆動信号COM−Bを出力する側を120bで、それぞれ統一するが、後述するように、いくつかの態様が存在するので、印刷装置と同様に、区別するために、駆動回路(その1)、駆動回路(その2)というように符号の代わりに括弧書を付与する場合がある。

なお、差動増幅器221の出力信号は、後述するスイッチング動作のための信号として用いられる場合もあれば、リニア動作のための信号として用いられる場合もある。スイッチング動作のための信号として用いられる場合、Hレベルは電圧VDであり、Lレベルは電圧ゼロのグランドGndである。

また、差動増幅器221による出力信号は、結局のところ、後述するようにトランジスター231、232のスイッチング動作およびリニア動作を制御するので、トランジスターの制御信号と言うことができる。また、後述するように、駆動信号を降圧して帰還する一方、元駆動信号を電圧増幅して駆動信号として出力する場合もあるので、駆動信号に基づく信号が差動増幅器221に帰還される、と言っても良い。

換言すれば、セレクター223は、信号OCaがLレベルであれば、トランジスター231を選択して、差動増幅器221の出力信号である差信号を当該トランジスター231のゲート端子に供給し、信号OCaがHレベルであれば、トランジスター232を選択して、上記差信号を当該トランジスター232のゲート端子に供給する一方、選択しなかったトランジスターのゲート端子には、後述するように当該トランジスターをオフにさせる信号を供給する構成となっている。

トランジスター231、232のドレイン端子同士は、互いに接続されて、駆動回路120aの出力端であるノードN2となっている。すなわち、ノードN2から駆動信号COM−Aが出力される構成となっている。

なお、駆動回路120aの出力であるノードN2の電圧をOutと表記し、入力である信号Ainの電圧をVinと表記する。

この図において、信号Ainは、駆動信号COM−Aのインピーダンス変換前の信号であるので、当該駆動信号COM−Aとほぼ同波形である。また、上述したように、駆動信号COM−Aは、印刷周期Taにおいて2つの同じ台形波形Adp1、Adp2が繰り返された波形であるので、信号Ainも同様な繰り返し波形である。

図11における電圧波形のそれぞれについて、説明の便宜上、電圧を示す縦スケールは必ずしも揃っていない。

期間P1では、信号Gt1がHレベルであるので、Pチャネル型のトランジスター231はオフする。

一方、当該期間P1では、まず信号Ainの電圧VinがノードN2の電圧Outよりも先んじて低下する。逆にいえば、電圧Outは、電圧Vin以上となる。このため、信号Gt2として選択される差動増幅器221の出力信号の電圧は、両者の差電圧に応じて高くなり、ほぼHレベルに振れる。信号Gt2がHレベルになると、トランジスター232がオンするので、電圧Outが低下する。なお、電圧Outは、コンデンサーC0や容量性を有する圧電素子Pztなどにより、実際には、一気にグランドGndに低下することはなく、緩慢に低下する。

電圧Outが電圧Vinよりも低くなると、信号Gt2がLレベルになり、トランジスター232がオフするが、電圧Vinが低下しているので、再び電圧Outが電圧Vin以上となる。このため、信号Gt2がHレベルとなって、トランジスター232が再びオンすることになる。

期間P1では、信号Gt2がH、Lレベルで交互に切り替えられ、これにより、トランジスター232は、オンオフを繰り返す動作、すなわちスイッチング動作をすることになる。このスイッチング動作により、電圧Outを電圧Vinの低下に追従させる制御が実行されることになる。

前の期間P1では、電圧Outが電圧Vinに追従するように制御されるが、その制御内容は、上述したようにトランジスター232のスイッチング動作である。このため、期間P2の開始直後、すなわち電圧Vinが最低値minで一定に転じた直後では、電圧Outが、電圧Vinに一致していない場合がある。

したがって、期間P2において、電圧Outは、当該電圧Outを低下させる方向と上昇させる方向とが均衡する地点、すなわち、電圧Vin(最低値min)に一致する地点で一定になる。このとき、トランジスター232は線形(リニア)動作となり、信号Gt2は、トランジスター232におけるソース・ドレイン間の抵抗、および、抵抗素子Ru、Rdで定まる電圧Outが電圧Vinとなるような電圧で一定となる。

なお、図11では、期間P1から期間P2にかけての信号Gt2の電圧変化については簡略化して、直ちに一定となった状態を示している。

期間P3では、信号Gt2がLレベルであるので、Nチャネル型のトランジスター232はオフする。

一方、当該期間P3では、まず電圧Vinが電圧Outよりも先んじて上昇する。逆にいえば、電圧Outは、電圧Vinよりも低くなる。このため、信号Gt1として選択される差動増幅器221の出力信号の電圧は、両者の差電圧に応じて低くなり、ほぼLレベルに振れる。信号Gt1がLレベルになると、トランジスター231がオンするので、電圧Outが上昇する。なお、電圧Outは、コンデンサーC0や容量性を有する圧電素子Pztなどにより、実際には、一気に電圧VDに上昇することはなく、緩慢に上昇する。

電圧Outが電圧Vin以上になると、信号Gt2がHレベルになり、トランジスター231がオフする。トランジスター231がオフすると、電圧Outの上昇は停止するが、電圧Vinが上昇しているので、再び電圧Outが電圧Vinよりも低くなる。このため、信号Gt1がLレベルとなって、トランジスター231が再びオンすることになる。

期間P3では、信号Gt1がH、Lレベルで交互に切り替えられ、これにより、トランジスター231は、スイッチング動作をすることになる。このスイッチング動作により、電圧Outを電圧Vinの上昇に追従させる制御が実行されることになる。

前の期間P3では、電圧Outが電圧Vinに追従するように制御されるが、その制御内容は、上述したようにトランジスター231によるスイッチング動作であるので、期間P4において電圧Vinが最高値maxで一定に転じた直後では、電圧Outが、信号Ainの電圧Vinに一致していない場合がある。

したがって、期間P4において、電圧Outは、当該電圧Outを低下させる方向と上昇させる方向とが均衡する地点、すなわち、電圧Vin(最高値max)に一致する地点で一定になる。このとき、トランジスター232はリニア動作となり、信号Gt2は、トランジスター232におけるソース・ドレイン間の抵抗、および、抵抗素子Ru、Rdで定まる電圧Outが電圧Vin(最高値max)となるような電圧で一定となる。

なお、図11では、期間P3から期間P4にかけての信号Gt2の電圧変化については簡略化して、直ちに一定となった状態を示している。

期間P5では、電圧Outを信号Ainの電圧Vinに追従させる制御が実行されるが、期間P6において電圧Vinが電圧Vcenで一定に転じた直後では、電圧Outが、信号Ainの電圧Vinに一致していない場合があるが、期間P2に転じた直後と同様に、電圧Outは、電圧Vin(Vcen)に一致する地点で一定になる。このとき、トランジスター232はリニア動作となり、信号Gt2は、トランジスター232におけるソース・ドレイン間の抵抗、および、抵抗素子Ru、Rdで定まる電圧Outが電圧Vin(Vcen)となるような電圧で一定となる。

なお、図11では、期間P5から期間P6にかけての信号Gt2の電圧変化については簡略化して、直ちにバランスした状態を示している。

すなわち、電圧Vinが低下する期間P1、P5ではトランジスター232のスイッチング動作により、電圧Vinが閾値Vthよりも低い値で一定となる期間P2、P6では、トランジスター232のリニア動作により、電圧Vinが上昇する期間P3ではトランジスター231のスイッチング動作により、電圧Vinが閾値Vth以上の値で一定となる期間P4では、トランジスター231のリニア動作により、それぞれ電圧Outを電圧Vinに追従させる制御が実行される。

また、駆動回路(その1)において、電圧Voutが閾値Vth以上の電圧で一定となる期間P4では、トランジスター231がリニア動作し、電圧Voutが閾値Vthよりも低い電圧で一定となる期間P2、P6では、トランジスター232がリニア動作すると説明したが、同様な理由により、スイッチング動作する場合もあり得る。

このため、スイッチSwu、Swdが互いに排他的にオンオフするので、電源の高位側電圧VDからグランドGndに向かって、抵抗素子Ru、Rdを介して貫通電流が流れない。このため、駆動回路(その3)は、駆動回路(その2)と比較して、さらに低消費電力化を図ることができる。

プルアップが特に必要となる場合とは、信号Ain(駆動信号COM−A)が閾値Vthよりも低い電圧で一定となる期間P2、P6、すなわちトランジスター232をリニア動作させる場合である。この場合、高位側のトランジスター231がオフであるので、低位側のトランジスター232によってノードN2の電圧Outを信号Ainに追従させるためには、ノードN2を高位側にプルアップする必要がある。

一方、プルダウンが特に必要となる場合とは、信号Ain(駆動信号COM−A)が閾値Vth以上の電圧で一定となる期間P4、すなわちトランジスター231をリニア動作させる場合である。この場合、ローサイドのトランジスター232がオフであるので、ハイサイドのトランジスター231によってノードN2の電圧Outを電圧Ainに追従させるために、ノードN2を低位側にプルダウンする必要がある。

例えば、データdA(dB)についての、時間的に隣り合う離散値(データ)同士を比較し、当該離散値同士が同じであれば、電圧一定区間であるし、当該一定区間における離散値を判別することで、一定区間の電圧が閾値Vth以上であるか否かを判別することができる。また、当該離散値同士のうち、時間的に後の離散値が前の離散値よりも電圧変換したときに高くなっていれば、電圧上昇区間であるし、時間的に後の離散値が前の離散値よりも電圧変換したときに低くなっていれば、電圧低下区間である。

データdA(dB)ではなく、アナログ変換後の信号を同様に解析しても良い。

そこで次に、この点を改善した別構成に係る駆動回路(その4)について説明する。

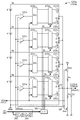

この図に示されるように、駆動回路120aは、4つの基準電源Eと、差動増幅器221およびセレクター223に加えて、ゲートセレクター270a、270b、270c、270dと、セレクター280と、4つのトランジスター対と、抵抗素子R1、R2と、スイッチSwuと、コンデンサーC0とを含む。

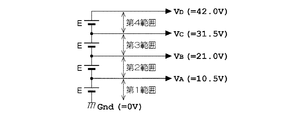

この図に示されるように、電圧Eを例えば10.5Vとしたとき、電圧VA、VB、VC、VDの各々は、それぞれ10.5V、21.0V、31.5V、42.0Vである。本実施形態では、電圧VA、VB、VC、VDで次のような電圧範囲が規定される。すなわち、電圧ゼロのグランドGnd以上電圧VA未満の範囲が第1範囲として規定され、電圧VA以上電圧VB未満の範囲が第2範囲として規定され、電圧VB以上電圧VC未満の範囲が第3範囲として規定され、電圧VC以上電圧VD未満の範囲が第4範囲として規定される。

なお、駆動回路(その4)における差動増幅器221は、駆動回路(その1)とは異なり、電源の高位側を電圧VAとしている。このため、差動増幅器221の出力電圧は、グランドGndから電圧VAまでの範囲となる。

詳細には、セレクター280は、データdA(dB)で規定される電圧Vinが0V以上1.05V未満であると判別した場合、すなわち、電圧Vinを10倍で増幅したときの電圧が上記第1範囲に含まれる場合、選択信号SaのみをHレベルとし、他の選択信号Sb、Sc、SdをLレベルとする。また、セレクター280は、データdA(dB)で規定される電圧Vinが1.05V以上2.10V未満であると判別した場合、すなわち、電圧Vinを10倍で増幅したときの電圧が上記第2範囲に含まれる場合、選択信号SbのみをHレベルとし、他の選択信号Sa、Sc、SdをLレベルとする。同様に、セレクター280は、データdA(dB)で規定される電圧Vinが2.10V以上3.15V未満であると判別した場合、すなわち、電圧Vinを10倍で増幅したときの電圧が上記第3範囲に含まれる場合、選択信号ScのみをHレベルとし、他の選択信号Sa、Sb、SdをLレベルとし、当該電圧Vinが3.15V以上4.20V未満であると判別した場合、すなわち、電圧Vinを10倍で増幅したときの電圧が上記第4範囲に含まれる場合、選択信号SdのみをHレベルとし、他の選択信号Sa、Sb、ScをLレベルとする。

この例において、4つのトランジスター対は、トランジスター231a、232aのペア、トランジスター231b、232bのペア、トランジスター231c、232cのペア、および、トランジスター231d、232dのペアによって構成される。

各トランジスター対のうち、ハイサイドのトランジスター231a、231b、231c、231dは、例えばPチャネル型の電界効果トランジスターであり、ローサイドのトランジスター232a、232b、232c、232dは、例えばNチャネル型の電界効果トランジスターである。

同様に、トランジスター231b(231c、231d)については、ソース端子に電圧VB(VC、VD)が印加され、ドレイン端子がノードN2に接続される。トランジスター232b(232c、232d)については、ソース端子に電圧VA(VB、VC)が印加され、ドレイン端子がノードN2に共通に接続される。

この構成では、トランジスター231a、232aの電源電圧、トランジスター231b、232bの電源電圧、トランジスター231c、232cの電源電圧、および、トランジスター231d、232dの電源電圧は、それぞれ10.5Vとなる。

なお、ゲートセレクター270aに限っていえば、信号Gt1、Gt2の最低電圧から最高電圧までの範囲は第1範囲に一致しているので、イネーブルされたときに、信号Gt1、Gt2をそのままトランジスター231a、232aのゲート端子に供給する。

ゲートセレクター270dについても同様に、イネーブルされたときに、信号Gt1の最低電圧から最高電圧までの範囲を、電圧VCから電圧VDまでの第4範囲にレベルシフトして、トランジスター231dのゲート端子に供給し、信号Gt2の最低電圧から最高電圧までの範囲を、上記第4範囲にレベルシフトして、トランジスター232dのゲート端子に供給する。すなわち、ゲートセレクター270dに限っていえば、イネーブルされたときに、信号Gt1、Gt2に31.5Vを上乗せして、トランジスター231d、232dのゲート端子に供給する。

ここでいうH、Lレベルは、ゲートセレクター270a、270b、270c、270dのそれぞれにおける電源電圧の高位側電圧、低位側電圧である。例えば、ゲートセレクター270bは、電圧VBと電圧VAとを電源電圧とするので、高位側の電圧VBがHレベルであり、低位側の電圧VAがLレベルである。

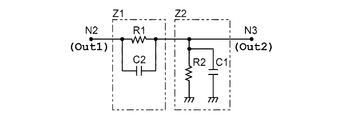

ノードN3は、抵抗素子R2を介してグランドGndに接地される。このため、ノードN3の電圧Out2は、電圧Outの電圧を、抵抗素子R1、R2の抵抗値で規定される比、すなわち、R2/(R1+R2)で分圧した電圧となる。本実施形態において、降圧比は、1/10に設定される。換言すれば、電圧Out2は、電圧Outの1/10という関係にある。

なお、ノードN2の電圧Outは電圧VDよりも高くならないので、逆流を考慮する必要がない。このため、トランジスター231dに対してダイオードd1は設けられていない。同様にノードN2の電圧Outは電圧ゼロのグランドGndよりも低くならないので、トランジスター232aに対してダイオードd2は設けられていない。

このため、電圧VA、VB、VC、VDで規定される第1範囲から第4範囲までを、信号ainの電圧範囲に換算する場合、電圧VA/10、VB/10、VC/10、VD/10で規定される。詳細には、信号ainについては、0V以上電圧VA/10(=1.05V)未満の範囲が第1範囲に相当し、電圧VA/10以上電圧VB/10(=2.10V)未満の範囲が第2範囲に相当し、電圧VB/10以上電圧VC/10(=3.15V)未満の範囲が第3範囲に相当し、電圧VC/10以上電圧VD/10(=4.20V)未満の範囲が第4範囲に相当する。

電圧Vinがタイミングt2からタイミングt3までの期間にわたって第1範囲となったとき、セレクター280は、選択信号SaのみをHレベルとし、この結果、ゲートセレクター270aのみがイネーブルされるので、トランジスター231a、232aが電源電圧として電圧VA、グランドGndを用いて駆動信号COM−Aを出力することになる。

ここでは、電圧Vinが第3範囲から第2範囲へと移行する場合を例にとって説明したが、他の場合でも同様であり、例えば第2範囲から第1範囲への移行であれば、ゲートセレクター270bがディセーブルになり、ゲートセレクター270aがイネーブルされるので、トランジスター231a、232aによって、引き続き電圧Out2が電圧Vinに追従するように制御される。

このため、DAC113aは、デジタルのデータdAをアナログで小振幅の信号ainに変換し、電圧増幅器295aは、当該信号ainの電圧を例えば10倍に増幅して、大振幅の信号Ainとして出力する。

駆動回路(その6)では、ノードN2の電圧Outを降圧して帰還する必要がないので、図14Aで示される駆動回路(その4)の抵抗素子R1、R2が廃止されている。ただし、ノードN2をプルダウンするために、抵抗素子RdがスイッチSwとともに設けられている。

また、駆動回路(その6)によれば、スイッチSwu、Swdが互いに排他的にオンオフするので、電源の高位側電圧VDおよびグランドGndの間において抵抗素子R1、R2を介して貫通電流が流れない。このため、さらなる低消費電力化を図ることができる。

このため、トランジスター対を元駆動信号に基づく信号に応じて選択する、といった場合の当該信号には、データdA(dB)の場合もあるし、当該データdA(dB)をアナログ変換した信号ain(bin)の場合もあるし、データdA(dB)と信号ain(bin)とを重み付けした信号の場合もある。

なお、4つのトランジスター対については、元駆動信号に基づく信号に応じてセレクター280によって選択されるとともに、選択されたトランジスター対から駆動信号COM−Aが出力される一方、非選択としたトランジスター対がゲートセレクターによってオフにさせられるので、セレクター280およびゲートセレクター270a、270b、270c、270dをトランジスター対切替部として概念することができる。

また、駆動回路(その4、その5、その6)において、電圧VA、VB、VC、VDについて、電圧Eを出力する基準電源の4段直列接続(図15参照)によって出力する構成としたので、各電圧セットにおける高位側電圧と低位側電圧との差を電圧E(=10.5V)で揃えたが、不揃いとした構成でも良い。

電圧範囲については、第1範囲から第4範囲までのうち、隣り合う範囲については一部重複させても良い。

なお、セレクター280がアナログ変換後の信号ain(bin)で判別しても良い点や、トランジスター対のセット数が「2」以上であれば良い点等については、後述する駆動回路(その10、その11、その12)でも同様に適用可能である。

このうち、DAC293aは、デジタルのデータdAをアナログで小振幅の信号ainに変換し、電圧増幅器295aは、当該信号ainの電圧を例えば10倍に増幅して大振幅の信号Ainとして出力する。

詳細には、電圧切替器300は、電圧選択器350と、スイッチS−AH、S−ALの組と、スイッチS−BH、S−BLの組と、スイッチS−CH、S−CLの組と、スイッチS−DH、S−DLの組と、を含み、電圧選択器350がデータdAに応じて選択信号Sel-A、Sel-B、Sel-C、Sel-Dを次のように出力する。

すなわち、トランジスター対の電源電圧が相違するだけであり、ノードN2の電圧Outを、トランジスター231、232が、電源電圧の範囲にある電圧Vinに追従するように制御する点については共通である。ここで、電圧Vinが、現状の電圧VH以上高くなる場合、電圧VH、VLとして1段高いセットに切り替えられる一方、電圧VLより低くなる場合、電圧VH、VLとして1段低いセットに切り替えられる。このため、駆動回路(その7)によれば、信号Ainの電圧Vinが、グランドGndから電圧VDまでの範囲にわたる場合、電圧切替器300によって、当該電圧Vinに応じた電圧VH、VLのセットを切り替えられながら、単位回路200によって、ノードN2の電圧Outが電圧Vinに追従するように制御されることになる。

これに対して、駆動回路(その7)によれば、データdA(電圧Vin)に応じて電圧セットが切り替えられて、単位回路200の電源電圧として給電される。このため、本実施形態では、0〜40V程度の電圧Outを出力するのにもかかわらず、単位回路200における電源電圧は、10.5Vに抑えられるので、高コスト化や、回路規模の肥大化を防ぐことができる。

なお、電圧選択器350のおける推定は、例えば次のようなものである。

すなわち、電圧選択器350は、選択制御部510(図6参照)におけるシフトレジスタ512およびラッチ回路514と同様な回路によって、制御部110からの制御信号Ctrに含まれる印刷データSIをラッチするとともに、当該ラッチした印刷データSIを解析し、印刷周期Taの期間T1、T2のそれぞれにおいて駆動信号COM−Aが一端に印加される圧電素子Pztの個数を求めることによって容量性負荷の大きさを推定する。

また、ここでいう遅延量とは、選択信号の論理レベルを切り替えるタイミングでの遅れ時間をいう。

すなわち、駆動回路120a(120b)における容量性の負荷は、印刷データSIで規定される印刷内容によって大きく変動する。

このため、圧電素子Pztの容量や、インダクタンス成分、抵抗成分などで形成される積分回路によって、最終的に圧電素子Pztの一端に印加される駆動信号COM−A(COM−B)の波形が鈍る。この波形の鈍りの程度は、選択される圧電素子Pztの個数が多くなるにつれて、すなわち容量性負荷が大きくなるにつれて、酷くなり(大きくなり)、信号Ain(Bin)に対して、圧電素子Pztの一端に印加される駆動信号COM−A(COM−B)が遅延することになる。

このため、駆動信号COM−A(COM−B)の遅延を想定していない構成では、当該駆動信号COM−A(COM−B)の目標電圧と電圧切替器300で選択される電圧セットとが不整合となり、波形を歪ませる可能性が高くなる。

そこで、この点を改善した駆動回路(その9)について説明する。なお、この駆動回路(その9)が適用される印刷装置は、図21で示した印刷装置(その4)であり、印刷データSIを含む制御信号Ctrが駆動回路120a、120bに供給される構成となっている。

スイッチSwcは、コンデンサーC0の他端とグランドGndとの間に介挿されて、解析部260から出力される信号SctrがHレベルであればオンし、当該信号SctrがLレベルであればオフする。なお、スイッチSwcは、ノードN2とコンデンサーC0の一端との間に介挿されても良い。

ここで、信号SctrがHレベルであれば、スイッチSwcがオンするので、コンデンサーC0の他端がグランドGndに電気的に接続(有効化)されて、圧電素子Pztと並列化される。一方、信号SctrがLレベルであれば、スイッチSwcがオフするので、コンデンサーC0の他端がグランドGndから切り離されて、当該コンデンサーC0が無効化される。

例えば駆動信号COM−Aを出力する駆動回路120aでみると、印刷周期Taの期間T1において駆動信号COM−Aが一端に印加される圧電素子Pztの個数が0からm/2(mの半分)までの範囲である場合、圧電素子Pztの容量は0Cから5Cまでの範囲で変動する。この場合、解析部260は信号SctrlをHレベルとするので、スイッチSwcがオンして、容量5CのコンデンサーC0が圧電素子Pztに対して並列接続となる。このため、ノードN2からみた容量性負荷の総和は、5Cから10Cまでの範囲となる。

なお、ここでは駆動回路120aについてみたが、駆動回路120bについて同様であり、駆動信号COM−Bが印加される圧電素子Pztの個数が変動しても、ノードN2からみた容量性負荷の変動を抑えることができる。

なお、図24の例では、コンデンサーC0を1個としたが、2個以上としても良い。具体的には、複数個のコンデンサーのそれぞれを、スイッチを介して圧電素子Pztに対して並列接続する一方で、駆動信号が一端に印加される圧電素子Pztの個数が多くなるにつれて、オフするスイッチSwの個数を段階的に増加させる構成とすれば良い。

この微積回路における特性の具体例について説明する。

なお、図27において縦軸は、位相(度)であり、周波数が10MHz付近をピークにして位相が相対的に進んでいることを示している。したがって、微積回路では、トランジスター対がスイッチングする周波数帯にわたって位相が進むので、帰還経路における位相遅れが補償される。

図25における微積回路を、入力側を左側に、出力側を右側にそれぞれ書き改めると、図28に示される通りとなり、抵抗素子R1とコンデンサーC2との並列接続と、抵抗素子R2とコンデンサーC1との並列接続とで表現することができる。

また、ノードN2には、異常発振防止用のコンデンサーC0が接続されるが、このコンデンサーC0は、ノードN2からみたときに負荷になるので、無駄に電力が消費される原因の1つとなる。コンデンサーC0の容量を小さくすれば、無駄な消費電力を抑えることができるが、コンデンサーC1、C2が存在しない構成では、異常発振の可能性が高くなる。これに対して、本実施形態によれば、コンデンサーC1、C2を含む微積回路によって、異常発振を抑えた上でコンデンサーC0の容量を小さくすることができるので、低消費電力化を図ることが可能になる。

ただし、信号OCaの本来の役目は、セレクター223における選択の指示であって、スイッチSwu、Swdにおけるオンオフの制御ではない。また、スイッチSwu、Swdや、NOT回路291などで遅延が発生すると、貫通電流が一時的に流れる可能性もある。

そこで次に、この点を改善した駆動回路(その12)について説明する。

信号Pubは、駆動信号COM−B(信号bin)が閾値Vthよりも低い電圧で一定となる期間でHレベルとなり、それ以外の期間でLレベルとなる。また、信号Pdbは、駆動信号COM−Bが閾値Vth以上高い電圧で一定となる期間でHレベルとなり、それ以外の期間でLレベルとなる。

一方、期間P4は、トランジスター231がリニア動作となる場合である。この場合、トランジスター232がオフになっているので、トランジスター231によってノードN2の電圧Outを電圧ainに追従させるためには、ノードN2を抵抗素子Rdによってプルダウンする必要がある。ただし、それ以外の期間P1〜P3、P5では、ノードN2をプルダウンする必要は特にない。

したがって、駆動回路(その12)によれば、抵抗素子Ruによるプルアップ、および、抵抗素子Rdによるプルダウンを、それぞれ必要な期間だけ機能させている構成ということができる。

図32は、駆動回路(その12)にDAC293を設けた駆動回路(その13)を示す図である。駆動回路(その10、その11)にDAC293を設けた例についての図示は省略する。

Claims (9)

- 容量性負荷を駆動する駆動信号の電圧と前記駆動信号の元となる元駆動信号の電圧とに基づいた差電圧を増幅して出力する差動増幅器と、

ハイサイドトランジスターおよびローサイドトランジスターを含み、前記駆動信号を出力端から出力する増幅部と、

を備え、

前記駆動信号は、

単位時間当たりで第1電圧以上で電圧が変化する第1期間と、

前記単位時間当たりで第1電圧よりも低く電圧が変化する、または、変化しない第2期間と、

を含み、

前記第1期間では、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方がスイッチング動作する期間を含み、

前記第2期間では、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方がリニア動作する期間を含む、

ことを特徴とする駆動回路。 - 前記駆動信号は、台形波形であり、

前記第1期間は、前記駆動信号の電圧が変化する期間であり、

前記第2期間は、前記駆動信号の電圧が一定である期間である

ことを特徴とする請求項1に記載の駆動回路。 - 前記駆動信号は、傾きに連続性を有する波形であり、

前記第1期間は、前記駆動信号の電圧変化が相対的に大きい期間であり、

前記第2期間は、前記駆動信号の電圧変化が相対的に小さい期間である、

ことを特徴とする請求項1に記載の駆動回路。 - 前記第1期間のうち、

前記駆動信号の電圧が上昇する場合では、前記ハイサイドトランジスターがスイッチング動作し、前記ローサイドトランジスターがオフし、

前記駆動信号の電圧が低下する場合では、前記ローサイドトランジスターがスイッチング動作し、前記ハイサイドトランジスターがオフする、

ことを特徴とする請求項1乃至3のいずれかに記載の駆動回路。 - 前記第2期間のうち、

前記駆動信号が所定の閾値以上の電圧の場合では、前記ハイサイドトランジスターがリニア動作し、前記ローサイドトランジスターがオフし、

前記駆動信号が前記閾値よりも低い電圧の場合では、前記ローサイドトランジスターがリニア動作し、前記ハイサイドトランジスターがオフする、

ことを特徴とする請求項1乃至4のいずれかに記載の駆動回路。 - 前記閾値は、

前記駆動信号の電圧の最高値よりも低く、

前記駆動信号の電圧の最低値よりも高い、

ことを特徴とする請求項5に記載の駆動回路。 - 前記ハイサイドトランジスターまたは前記ローサイドトランジスターのいずれかを選択し、当該選択したトランジスターのゲート端子に前記差電圧を印加し、非選択としたトランジスターのゲート端子に当該非選択としたトランジスターをオフにさせる信号を供給するセレクターをさらに備える

ことを特徴とする請求項1乃至6のいずれかに記載の駆動回路。 - 容量性負荷を駆動する駆動信号の電圧と前記駆動信号の元となる元駆動信号の電圧とに基づいた差電圧を増幅して出力する差動増幅器と、

ハイサイドトランジスターおよびローサイドトランジスターを含み、前記駆動信号を出力端から出力する増幅部と、

を備え、容量性負荷を駆動する駆動回路の制御方法であって、

前記駆動信号は、

単位時間当たりで第1電圧以上で電圧が変化する第1期間と、

前記単位時間当たりで第1電圧よりも低く電圧が変化する、または、変化しない第2期間と、

を含み、

前記差動増幅器は、

前記第1期間の少なくとも一部期間において、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方をスイッチング動作させ、

前記第2期間間の少なくとも一部期間において、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方をリニア動作させる、

ことを特徴とする駆動回路の制御方法。 - 駆動信号の印加により変位する圧電素子を含み、当該圧電素子の変位により液体を吐出する吐出部と、

前記駆動信号の電圧と前記駆動信号の元となる元駆動信号の電圧とに基づいた差電圧を増幅して出力する差動増幅器と、

ハイサイドトランジスターおよびローサイドトランジスターを含み、前記駆動信号を出力端から出力する増幅部と、

を備え、

前記駆動信号は、

単位時間当たりで第1電圧以上で電圧が変化する第1期間と、

前記単位時間当たりで第1電圧よりも低く電圧が変化する、または、変化しない第2期間と、

を含み、

前記第1期間では、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方がスイッチング動作する期間を含み、

前記第2期間では、前記ハイサイドトランジスターと前記ローサイドトランジスターとの一方がリニア動作する期間を含む、

ことを特徴とする液体吐出装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016034988A JP6794635B2 (ja) | 2016-02-26 | 2016-02-26 | 駆動回路、駆動回路の制御方法および液体吐出装置 |

| US15/412,477 US10044343B2 (en) | 2016-02-26 | 2017-01-23 | Drive circuit, and control method of drive circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016034988A JP6794635B2 (ja) | 2016-02-26 | 2016-02-26 | 駆動回路、駆動回路の制御方法および液体吐出装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2017149065A JP2017149065A (ja) | 2017-08-31 |

| JP6794635B2 true JP6794635B2 (ja) | 2020-12-02 |

Family

ID=59679008

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016034988A Active JP6794635B2 (ja) | 2016-02-26 | 2016-02-26 | 駆動回路、駆動回路の制御方法および液体吐出装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US10044343B2 (ja) |

| JP (1) | JP6794635B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6766372B2 (ja) * | 2016-02-26 | 2020-10-14 | セイコーエプソン株式会社 | 駆動回路および液体吐出装置 |

| JP6922263B2 (ja) * | 2017-03-06 | 2021-08-18 | セイコーエプソン株式会社 | 液体吐出装置および容量性負荷の駆動回路 |

| US10630290B2 (en) * | 2017-09-27 | 2020-04-21 | Apple Inc. | Low leakage power switch |

| US10523194B2 (en) * | 2017-09-27 | 2019-12-31 | Apple Inc. | Low leakage power switch |

| CN109445336B (zh) * | 2018-10-30 | 2022-05-17 | 温州市麦特力克电器有限公司 | 开关控制电路及开关控制系统 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5105070B2 (ja) | 2008-02-14 | 2012-12-19 | セイコーエプソン株式会社 | 容量性負荷の駆動回路及び液体吐出装置 |

| JP2010114711A (ja) | 2008-11-07 | 2010-05-20 | Seiko Epson Corp | 電力増幅装置 |

| JP6287341B2 (ja) * | 2014-03-03 | 2018-03-07 | セイコーエプソン株式会社 | 液体吐出装置および液体吐出装置の制御方法 |

-

2016

- 2016-02-26 JP JP2016034988A patent/JP6794635B2/ja active Active

-

2017

- 2017-01-23 US US15/412,477 patent/US10044343B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2017149065A (ja) | 2017-08-31 |

| US20170250679A1 (en) | 2017-08-31 |

| US10044343B2 (en) | 2018-08-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6759643B2 (ja) | 液体吐出装置、駆動回路および集積回路 | |

| JP6794635B2 (ja) | 駆動回路、駆動回路の制御方法および液体吐出装置 | |

| JP6716953B2 (ja) | 液体吐出装置および駆動回路 | |

| US9862184B2 (en) | Liquid ejecting apparatus, drive circuit, and head unit | |

| JP6759644B2 (ja) | 液体吐出装置および駆動回路 | |

| JP6753075B2 (ja) | 駆動回路および液体吐出装置 | |

| JP6668858B2 (ja) | 液体吐出装置、駆動回路および集積回路 | |

| JP2018103419A (ja) | 液体吐出装置および駆動回路 | |

| JP6794634B2 (ja) | 駆動回路および液体吐出装置 | |

| JP6922263B2 (ja) | 液体吐出装置および容量性負荷の駆動回路 | |

| JP6753246B2 (ja) | 液体吐出装置および駆動回路 | |

| JP6836120B2 (ja) | 液体吐出装置および駆動回路 | |

| JP6728761B2 (ja) | 液体吐出装置、駆動回路およびヘッドユニット | |

| JP6766372B2 (ja) | 駆動回路および液体吐出装置 | |

| JP6747216B2 (ja) | 液体吐出装置、駆動回路および駆動方法 | |

| JP2016175336A (ja) | 液体吐出装置、駆動回路およびヘッドユニット | |

| JP2017149075A (ja) | 液体吐出装置、駆動回路およびヘッドユニット | |

| JP2017149069A (ja) | 液体吐出装置、駆動回路およびヘッドユニット | |

| JP2018051809A (ja) | 液体吐出装置、駆動回路および駆動方法 | |

| JP6699414B2 (ja) | 液体吐出装置、駆動回路および集積回路 | |

| JP2017149066A (ja) | 液体吐出装置、駆動回路およびヘッドユニット | |

| JP2017149074A (ja) | 液体吐出装置、駆動回路およびヘッドユニット | |

| JP2017149063A (ja) | 液体吐出装置、駆動回路およびヘッドユニット | |

| JP2017149068A (ja) | 液体吐出装置、駆動回路およびヘッドユニット | |

| JP2017149067A (ja) | 液体吐出装置、駆動回路およびヘッドユニット |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190110 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20191023 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20191119 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200116 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200512 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200525 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20201013 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20201026 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6794635 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |