JP6340193B2 - 液晶表示装置 - Google Patents

液晶表示装置 Download PDFInfo

- Publication number

- JP6340193B2 JP6340193B2 JP2013254206A JP2013254206A JP6340193B2 JP 6340193 B2 JP6340193 B2 JP 6340193B2 JP 2013254206 A JP2013254206 A JP 2013254206A JP 2013254206 A JP2013254206 A JP 2013254206A JP 6340193 B2 JP6340193 B2 JP 6340193B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel

- display area

- electrode

- liquid crystal

- counter substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 68

- 239000000758 substrate Substances 0.000 claims description 122

- 230000002093 peripheral effect Effects 0.000 claims description 72

- 239000011159 matrix material Substances 0.000 claims description 37

- 239000010408 film Substances 0.000 description 101

- 239000010410 layer Substances 0.000 description 32

- 238000002161 passivation Methods 0.000 description 26

- 239000012535 impurity Substances 0.000 description 25

- 150000002500 ions Chemical class 0.000 description 24

- 239000011229 interlayer Substances 0.000 description 16

- 230000005684 electric field Effects 0.000 description 15

- 238000005229 chemical vapour deposition Methods 0.000 description 10

- 239000003566 sealing material Substances 0.000 description 10

- 238000000034 method Methods 0.000 description 6

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 6

- 239000004065 semiconductor Substances 0.000 description 6

- 230000008859 change Effects 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 238000002834 transmittance Methods 0.000 description 4

- 229910000789 Aluminium-silicon alloy Inorganic materials 0.000 description 3

- MUBZPKHOEPUJKR-UHFFFAOYSA-N Oxalic acid Chemical compound OC(=O)C(O)=O MUBZPKHOEPUJKR-UHFFFAOYSA-N 0.000 description 3

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- 229920002120 photoresistant polymer Polymers 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 239000004925 Acrylic resin Substances 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 2

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 210000002858 crystal cell Anatomy 0.000 description 1

- 230000000593 degrading effect Effects 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 238000010304 firing Methods 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 238000005040 ion trap Methods 0.000 description 1

- 238000005224 laser annealing Methods 0.000 description 1

- 235000006408 oxalic acid Nutrition 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Landscapes

- Liquid Crystal (AREA)

Description

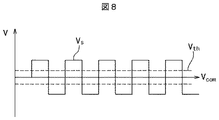

Vdummy=Vactive・・・・・(1)

とすることによってコーナーにおける表示むらを防止することが出来る。

本実施例の駆動方法は、次のような構成となっている。

(1)VactiveがVcom≦Vactive<Vthを満たす場合、

Vdummy=Vactive・・・・・(2)

とする。

(2)VactiveがVth≦Vactiveを満たす場合、

Vdummy=Vth・・・・・(3)

とする。なお、Vdummyとは表示領域最外周の画素に隣接するダミー画素に印加される電圧をいう。

Claims (7)

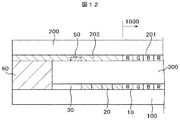

- コモン電極の上に絶縁膜を挟んでスリットを有する画素電極が形成され、TFTを有する画素がマトリクス状に形成された表示領域を有し、表示領域の外側にダミー画素が形成されたTFT基板と、

カラーフィルタが形成された表示領域と表示領域周辺をブラックマトリクスによって覆った対向基板を有し、TFT基板と対向基板との間に液晶層が挟持された液晶表示装置であって、

前記表示領域の最外周の画素に印加される信号電圧と同じ電圧を、前記最外周の画素に隣接する前記ダミー画素に印加し、

前記TFT基板において、前記ダミー画素の外側に第1周辺電極が配置され、前記第1周辺電極には、コモン電圧が印加されることを特徴とする液晶表示装置。 - コモン電極の上に絶縁膜を挟んでスリットを有する画素電極が形成され、TFTを有する画素がマトリクス状に形成された表示領域を有し、表示領域の外側にダミー画素が形成されたTFT基板と、

カラーフィルタが形成された表示領域と表示領域周辺をブラックマトリクスによって覆った対向基板を有し、TFT基板と対向基板との間に液晶層が挟持された液晶表示装置であって、

前記液晶層におけるスレッショルド電圧をVthとし、前記表示領域の最外の画素の電圧をVactiveとし、前記最外の画素に隣接するダミー画素に印加する電圧をVdummyとした場合、

VactiveがVcom≦Vactive<Vthを満たす場合、

Vdummy=Vactiveとし、

VactiveがVth≦Vactiveを満たす場合、

Vdummy=Vthとすることを特徴とする液晶表示装置。 - コモン電極の上に絶縁膜を挟んでスリットを有する画素電極が形成され、TFTを有する画素がマトリクス状に形成された表示領域を有し、表示領域の外側にダミー画素が形成されたTFT基板と、

カラーフィルタが形成された表示領域と表示領域周辺をブラックマトリクスによって覆った対向基板を有し、TFT基板と対向基板との間に液晶層が挟持された液晶表示装置であって、

前記表示領域の表示画面の平均輝度に相当する信号電圧を前記表示領域最外の画素に隣接するダミー画素に印加し、

前記TFT基板において、前記ダミー画素の外側に第1周辺電極が配置され、前記第1周辺電極には、コモン電圧が印加されることを特徴とする液晶表示装置。 - 前記TFT基板において、前記ダミー画素の外側に第1周辺電極が配置され、前記第1周辺電極には、コモン電圧が印加されることを特徴とする請求項2に記載の液晶表示装置。

- 前記対向基板において、前記表示領域の外側に第2周辺電極が配置され、前記第2周辺電極にはコモン電圧が印加されることを特徴とする請求項1、3、または4のいずれか1項に記載の液晶表示装置。

- 前記対向基板において、前記表示領域の外側に第2周辺電極が配置され、前記第2周辺電極にはコモン電圧が印加されることを特徴とする請求項1乃至3のいずれか1項に記載の液晶表示装置。

- 前記対向基板はタッチパネル用電極を含むことを特徴とする請求項1乃至6のいずれか1項に記載の液晶表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013254206A JP6340193B2 (ja) | 2013-12-09 | 2013-12-09 | 液晶表示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013254206A JP6340193B2 (ja) | 2013-12-09 | 2013-12-09 | 液晶表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015114375A JP2015114375A (ja) | 2015-06-22 |

| JP2015114375A5 JP2015114375A5 (ja) | 2017-01-26 |

| JP6340193B2 true JP6340193B2 (ja) | 2018-06-06 |

Family

ID=53528249

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013254206A Active JP6340193B2 (ja) | 2013-12-09 | 2013-12-09 | 液晶表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6340193B2 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7322941B2 (ja) * | 2017-08-31 | 2023-08-08 | 株式会社Jvcケンウッド | 反射型液晶表示装置 |

| JP7218086B2 (ja) * | 2017-08-31 | 2023-02-06 | 株式会社Jvcケンウッド | 反射型液晶表示装置 |

| JP6827650B2 (ja) | 2017-10-11 | 2021-02-10 | 株式会社Jvcケンウッド | 位相変調装置 |

| JP6904889B2 (ja) | 2017-11-16 | 2021-07-21 | パナソニック液晶ディスプレイ株式会社 | 液晶表示パネル |

| JP6998740B2 (ja) | 2017-11-16 | 2022-01-18 | パナソニック液晶ディスプレイ株式会社 | 液晶表示パネル |

| JP6909713B2 (ja) | 2017-11-16 | 2021-07-28 | パナソニック液晶ディスプレイ株式会社 | 液晶表示パネル |

| JP6901382B2 (ja) | 2017-11-29 | 2021-07-14 | パナソニック液晶ディスプレイ株式会社 | 液晶表示パネル |

| JP7354064B2 (ja) | 2020-07-14 | 2023-10-02 | パナソニック インテレクチュアル プロパティ コーポレーション オブ アメリカ | 液晶表示パネル及び液晶モジュール |

| JP2022166948A (ja) | 2021-04-22 | 2022-11-04 | セイコーエプソン株式会社 | 電気光学装置および電子機器 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005003802A (ja) * | 2003-06-10 | 2005-01-06 | Toshiba Matsushita Display Technology Co Ltd | 液晶表示装置 |

| TWI329774B (en) * | 2007-04-13 | 2010-09-01 | Au Optronics Corp | Liquid crystal display panel |

| JP5575412B2 (ja) * | 2009-03-09 | 2014-08-20 | 株式会社ジャパンディスプレイ | 液晶装置及び電子機器 |

| JP2011059374A (ja) * | 2009-09-10 | 2011-03-24 | Seiko Epson Corp | 電気光学装置、その製造方法、および電子機器 |

-

2013

- 2013-12-09 JP JP2013254206A patent/JP6340193B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015114375A (ja) | 2015-06-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6340193B2 (ja) | 液晶表示装置 | |

| JP5335628B2 (ja) | 液晶表示装置 | |

| JP5372900B2 (ja) | 液晶表示装置 | |

| JP6639866B2 (ja) | 液晶表示装置 | |

| JP5394655B2 (ja) | 液晶表示装置 | |

| TWI515483B (zh) | 液晶顯示裝置及其製造方法 | |

| JP5192941B2 (ja) | 液晶表示装置 | |

| TW201621431A (zh) | 顯示面板 | |

| JP2017103408A (ja) | 表示装置 | |

| EP2821845B1 (en) | Liquid crystal display device | |

| US20170351129A1 (en) | Liquid crystal display device | |

| US9703152B2 (en) | Liquid crystal display device | |

| JP2016015404A (ja) | 液晶表示装置 | |

| JP5687778B2 (ja) | 液晶表示装置 | |

| JP5939755B2 (ja) | 液晶表示装置 | |

| JP2014106322A (ja) | 液晶表示装置 | |

| JP2017097190A (ja) | 液晶表示装置 | |

| JP6918090B2 (ja) | 液晶表示装置 | |

| JP5456919B2 (ja) | 液晶表示装置 | |

| JP2018146923A (ja) | 液晶表示装置 | |

| JP5714676B2 (ja) | 液晶表示装置およびその製造方法 | |

| JP5714679B2 (ja) | 液晶表示装置 | |

| JP5814617B2 (ja) | 液晶表示装置 | |

| JP2015138867A (ja) | 薄膜トランジスタ搭載基板の製造方法 | |

| JP2011164199A (ja) | 液晶表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161207 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20161207 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170926 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171003 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171127 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180417 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180514 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6340193 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |