JP6323813B2 - 撮像装置 - Google Patents

撮像装置 Download PDFInfo

- Publication number

- JP6323813B2 JP6323813B2 JP2015207303A JP2015207303A JP6323813B2 JP 6323813 B2 JP6323813 B2 JP 6323813B2 JP 2015207303 A JP2015207303 A JP 2015207303A JP 2015207303 A JP2015207303 A JP 2015207303A JP 6323813 B2 JP6323813 B2 JP 6323813B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- voltage

- circuit

- signal

- reset

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000003384 imaging method Methods 0.000 title claims description 104

- 230000003321 amplification Effects 0.000 claims description 178

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 178

- 238000006243 chemical reaction Methods 0.000 claims description 38

- 239000003990 capacitor Substances 0.000 claims description 31

- 238000001514 detection method Methods 0.000 claims description 17

- 230000001629 suppression Effects 0.000 description 47

- 238000010586 diagram Methods 0.000 description 29

- 101100168116 Magnaporthe oryzae (strain 70-15 / ATCC MYA-4617 / FGSC 8958) CON7 gene Proteins 0.000 description 24

- 238000012986 modification Methods 0.000 description 20

- 230000004048 modification Effects 0.000 description 20

- 230000000875 corresponding effect Effects 0.000 description 19

- 238000012545 processing Methods 0.000 description 19

- 230000008859 change Effects 0.000 description 17

- 101100168115 Neurospora crassa (strain ATCC 24698 / 74-OR23-1A / CBS 708.71 / DSM 1257 / FGSC 987) con-6 gene Proteins 0.000 description 16

- 101100168117 Neurospora crassa (strain ATCC 24698 / 74-OR23-1A / CBS 708.71 / DSM 1257 / FGSC 987) con-8 gene Proteins 0.000 description 14

- 238000000034 method Methods 0.000 description 14

- 230000000694 effects Effects 0.000 description 12

- 230000002093 peripheral effect Effects 0.000 description 12

- 238000013461 design Methods 0.000 description 7

- 230000003287 optical effect Effects 0.000 description 7

- 230000008901 benefit Effects 0.000 description 5

- 230000001276 controlling effect Effects 0.000 description 5

- 230000007423 decrease Effects 0.000 description 5

- 239000002184 metal Substances 0.000 description 5

- 239000004065 semiconductor Substances 0.000 description 5

- 238000003860 storage Methods 0.000 description 5

- 230000003071 parasitic effect Effects 0.000 description 4

- 238000012546 transfer Methods 0.000 description 4

- 230000002238 attenuated effect Effects 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 238000009825 accumulation Methods 0.000 description 2

- 230000002596 correlated effect Effects 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 238000005070 sampling Methods 0.000 description 2

- 230000035945 sensitivity Effects 0.000 description 2

- 239000000758 substrate Substances 0.000 description 2

- 102000003712 Complement factor B Human genes 0.000 description 1

- 108090000056 Complement factor B Proteins 0.000 description 1

- 206010047571 Visual impairment Diseases 0.000 description 1

- 230000002730 additional effect Effects 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000011514 reflex Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 230000002123 temporal effect Effects 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/60—Noise processing, e.g. detecting, correcting, reducing or removing noise

- H04N25/65—Noise processing, e.g. detecting, correcting, reducing or removing noise applied to reset noise, e.g. KTC noise related to CMOS structures by techniques other than CDS

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Solid State Image Pick-Up Elements (AREA)

Description

入射光を光電変換する光電変換部と、光電変換部の信号を検出する信号検出回路と、を含む単位画素セルを備え、信号検出回路は、光電変換部の信号を増幅する第1のトランジスタと、第1のトランジスタの出力を選択的に外部に出力する第2のトランジスタと、光電変換部の信号を第1のトランジスタを介さずに負帰還するフィードバック回路と、を有する、撮像装置。

第1のトランジスタは、フィードバック回路の帰還経路の外に配置されている、項目1に記載の撮像装置。

入射光を光電変換する光電変換部と、光電変換部の信号を検出する信号検出回路と、を含む単位画素セルを備え、信号検出回路は、光電変換部の信号を増幅する第1のトランジスタと、第1のトランジスタの出力を選択的に外部に出力する第2のトランジスタと、光電変換部の信号を第1のトランジスタを介して負帰還するフィードバック回路と、を有する、撮像装置。

第1のトランジスタは、フィードバック回路の帰還経路に配置されている、項目3に記載の撮像装置。

第1のトランジスタの出力側に定電流源が接続されている、項目3または4に記載の撮像装置。

光電変換部の信号を初期化するリセットトランジスタをさらに備える、項目1から5のいずれかに記載の撮像装置。

信号検出回路は、フィードバック回路が有効である第1の期間と、フィードバック回路が無効である第2の期間との間で増幅率を切り替える、項目1から5のいずれかに記載の撮像装置。

リセットトランジスタは、フィードバック回路のループの一部を形成する、項目6に記載の撮像装置。

リセットトランジスタは、負帰還トランジスタである、項目8に記載の撮像装置。

光電変換部と基準電圧との間に、互いに直列に接続された第1および第2の容量素子をさらに備える、項目1から9のいずれかに記載の撮像装置。

フィードバック回路は、第1の容量素子を介して形成される、項目10に記載の撮像装置。

第2の容量素子の容量は、第1の容量素子の容量よりも大きい、項目10に記載の撮像装置。

リセットトランジスタの一端は、フィードバック回路のループの一部を形成せずに光電変換部に接続されている、項目6に記載の撮像装置。

リセットトランジスタの他の一端は、第1のトランジスタの出力に接続されている、項目6に記載の撮像装置。

フィードバック回路の帯域を制御する帯域制御トランジスタをさらに備え、

帯域制御トランジスタは、フィードバック回路のループの一部を形成し、

リセットトランジスタの他の一端は、帯域制御トランジスタ接続されている、項目6に記載の撮像装置。

第2のトランジスタに接続された信号読み出しラインをさらに備え、

第2のトランジスタは、

第1のトランジスタの出力と、信号読み出しラインと、を電気的に切断する第1の期間と、

第1のトランジスタの出力と、信号読み出しラインと、を電気的に接続する第2の期間と、

を有する、項目1から5のいずれかに記載の撮像装置。

フィードバック回路の帯域を制御する帯域制御トランジスタをさらに備え、

帯域制御トランジスタは、任意の第1の帯域から、任意の第2の帯域まで、連続的に変化するように制御されることを特徴とする、項目1から5のいずれかに記載の撮像装置。

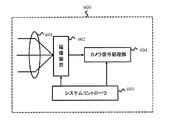

項目1から17のいずれかに記載の撮像装置と、

撮像装置に被写体像を結像する光学系と、

撮像装置からの出力信号を処理する信号処理部と、

を備える、カメラシステム。

図3から図8を参照して、本実施形態に係る撮像装置100の、構造、機能および駆動方法を説明する。本実施形態に係る撮像装置100は、3つのトランジスタを含む読み出し回路50Aを備えている。

まず、図3を参照しながら、撮像装置100の構造を説明する。

次に、図7を参照しながら、読み出し回路50Aの動作フローを説明する。

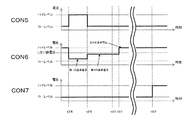

時刻t1において、選択制御信号線CON7の電圧はローレベルである。従って、第1の選択トランジスタ500はオフ状態であり、第1の増幅トランジスタ200と信号読み出しライン7とは電気的に分離されている。また、時刻t1において、帯域制御信号線CON1の電圧をハイレベルにして、第1の帯域制御トランジスタ300をオン状態にする。また、時刻t1においては、切替回路20の第1のスイッチ素子11はオン状態となっており、第1の増幅トランジスタ200のソースおよびドレインの他方には電圧Va1(例えばGND)が印加されている。これにより、FDの電圧は、リセット電圧VRSTと等しくなる。

次に、時刻t2から時刻t4の期間では、帯域制御信号線CON1の電圧を、ハイレベルとローレベルとの間、例えば中間の電圧に設定する。その場合、第1の帯域制御トランジスタ300の動作帯域は、第1の帯域よりも狭い第2の帯域となる。第2の帯域は、ゲート電圧が中間の電圧であるときの、第1の帯域制御トランジスタ300の動作帯域を意味する。

時刻t5において、選択制御信号線CON7の電圧をハイレベルにして第1の選択トランジスタ500をオンにする。また、第1の増幅トランジスタ200のソースおよびドレインの他方の電圧がVa2(例えばVDD)になるように、切替回路20を制御する。すなわち、第2のスイッチ素子12がオンになり、第1の増幅トランジスタ200のソースおよびドレインの他方には、電圧Va2が印加される。この状態においては、第1の増幅トランジスタ200と定電流源6とがソースフォロア回路を形成する。そして、信号読み出しライン7は、FDに蓄積された信号電荷に応じた電圧となる。そのとき、ソースフロア回路の増幅率は1倍程度である。

図9から図17を参照して、本実施形態に係る撮像装置100の構造、機能および駆動方法を説明する。本実施形態による撮像装置100は、4つのトランジスタを含む読み出し回路50Bを備えている点で、第1の実施形態と異なる。

本実施形態による撮像装置100は、第1の実施形態と同様に、2次元に配列された複数の単位画素セル110Bと、周辺回路とを備えている。単位画素セル110Bは、各種の制御線を介して周辺回路に接続されている。

時刻t11において、選択制御線CON7の電圧はローレベルである。従って、第1の選択トランジスタ500はオフ状態であり、第1の増幅トランジスタ200と信号読み出しライン7とは電気的に分離されている。また、時刻t11において、帯域制御信号線CON3の電圧をハイレベルにして第2の帯域制御トランジスタ301をオン状態にする。また、時刻t11において、切替回路20の第1のスイッチ素子11はオン状態となっており、第1の増幅トランジスタ200のソースおよびドレインの他方には電圧Va1(例えばGND)が印加されている。さらに、時刻t11において、リセット制御信号線CON2の電圧をハイレベルにし、リセットトランジスタ400をオンにすることにより、FDはリセットされ、FDの電圧は、基準電圧VR2となる。

時刻t13から時刻t15の期間に、帯域制御信号線CON3の電圧をハイレベルとローレベルとの間、例えば中間の電圧に設定する。その場合、第2の帯域制御トランジスタ301の動作帯域は第1の帯域よりも狭い第2の帯域となる。

時刻t16において選択制御信号線CON7の電圧をハイレベルにして、第1の選択トランジスタ500をオンにし、第1の増幅トランジスタ200のソースおよびドレインの他方の電圧がVa2(例えばVDD)になるように切替回路20を制御する。この状態においては、第1の増幅トランジスタ200と定電流源6とがソースフォロア回路を形成する。信号読み出しライン7は、FDに蓄積された信号電荷に応じた電圧となる。そのとき、ソースフロア回路の増幅率は1倍程度である。

図18から図22Bを参照して、本実施形態による撮像装置100の構造、機能および駆動方法を説明する。本実施形態による撮像装置100は、読み出し回路50Cの出力選択部5Cが、選択トランジスタとしてPMOSトランジスタを含み、切替回路40に接続されている点で、第2の実施形態による撮像装置100とは異なる。以下、第2の実施形態とは異なる点を中心に説明する。

時刻t21において、選択制御線CON8の電圧をローレベルおよびハイレベルの間、例えば中間の電圧にする。また、信号読み出しライン7に電圧源VB2を接続するように、切替回路40を制御する。また、帯域制御信号線CON3の電圧をハイレベルにして、第2の帯域制御トランジスタ301をオンにする。また、時刻t21において、第1の増幅トランジスタ200のソースおよびドレインの他方は、第1の電圧源VA1に接続されている。第1の電圧源VA1の電圧Va1は、例えばGNDである。さらに、時刻t21において、リセット制御信号線CON2の電圧をハイレベルにし、リセットトランジスタ400をオンにすることにより、FDをリセットする。その結果、FDの電圧は、基準電圧VR2となる。

時刻t23から時刻t25の期間に、帯域制御信号線CON3の電圧を、ハイレベルとローレベルとの間、例えば中間の電圧に設定する。その場合、第2の帯域制御トランジスタ301の動作帯域は、第1の帯域よりも狭い第2の帯域となる。

時刻t26において、選択制御信号線CON8の電圧をローレベルにして、第3の選択トランジスタ502をオンにし、第1の増幅トランジスタ200のソースおよびドレインの他方の電圧がVa2(例えばVDD)になるように切替回路20を制御する。また、信号読み出しライン7に定電流源6が接続されるように切替回路40を制御する。この状態においては、第1の増幅トランジスタ200と定電流源6とがソースフォロア回路を形成する。信号読み出しライン7は、FDに蓄積された信号電荷に応じた電圧となる。そのとき、ソースフロア回路の増幅率は1倍程度である。

図23から図27を参照して、本実施形態による撮像装置100の構造、機能および駆動方法を説明する。本実施形態による撮像装置100は、以下の点で、第1から第3の実施形態による撮像装置100とは異なる。第1に、読み出し回路50D内の増幅器2Aが、増幅機能および帯域制御機能を有する。第2に、増幅器2Aは、自身の出力を入力に戻すことにより、自ら帯域制御を行いながら、自らの増幅機能(増幅率:−A)で負帰還をかけ、リセットノイズを1/(1+A)1/2に抑制する。

時刻t28において、第7の制御信号線CON7の電圧はローレベルであり、第2の選択トランジスタ501はオフしている。すなわち、信号読み出しライン7と第4の増幅トランジスタ203とは電気的に切り離されている。この状態で、FDが所望のリセット電圧VRST近傍の電圧になるように、第4の制御信号線CON4の電圧を第1の基準電圧に設定する。このとき、第2の増幅トランジスタ201の帯域は、広帯域である第3の帯域に設定される。これにより、FD、第2の増幅トランジスタ201のゲート、および第2の増幅トランジスタ201のソースおよびドレインの一方は、高速に所望の電圧に設定される。第3の帯域は、第1の基準電圧に対応した帯域を意味する。

時刻t29からt31において、第7の制御信号線CON7はローレベルのままであり、第2の選択トランジスタ501はオフ状態である。すなわち、信号読み出しライン7と、第4の増幅トランジスタ203とは、電気的に切り離された状態のままである。この状態で、第4の制御信号線CON4の電圧を、第2の基準電圧に設定する。これにより、第2の増幅トランジスタ201はオンからオフに徐々に変更される。そのとき、第2の増幅トランジスタ201において、kTCノイズが発生する。このkTCノイズは、第2の増幅トランジスタ201のソースおよびドレインの一方が接続されたFDに寄生する容量Cfdに依存している。そこで、第2の増幅トランジスタ201による帰還ループを用いて、このノイズを抑制する。

FDのノイズが十分抑制され、電圧が安定した状態で、所望の期間において、FDに電荷を蓄積する。その後、時刻t32において、第2の選択トランジスタ501をオンし、第4の増幅トランジスタ203を信号読み出しライン7と電気的に接続する。これにより、第4の増幅トランジスタ203と定電流源6とはソースフォロア回路を形成する。FDに蓄積された信号電荷は、ソースフォロア回路で増幅され、信号読み出しライン7を介して、周辺回路(CDS回路、A/D回路等)に出力される。

図28から図34を参照して、本実施形態による撮像装置100の構造、機能および駆動方法を説明する。本実施形態による撮像装置100は、第4の実施形態による読み出し回路50Dにスイッチ部4Bを付加した点で、第4の実施形態による撮像装置100とは異なる。以下、第4の実施形態とは異なる点を中心に説明する。

時刻t28において、第5の制御信号線CON5の電圧をハイレベルにして、スイッチトランジスタ401をオンにする。このとき、第4の基準電圧VR4とFDとが接続される。また、時刻t28において、第7の制御信号線CON7の電圧はローレベルであり、選択トランジスタ501はオフ状態である。すなわち、信号読み出しライン7から、第4の増幅トランジスタ203は電気的に切り離されている。この状態で、FDが所望のリセット電圧VRST(=VR4)近傍の電圧になるように、第6の制御信号CON6を第1の基準電圧に設定する。このとき、第3の増幅トランジスタ202の帯域を、広帯域である第3の帯域に設定することにより、FD、第3の増幅トランジスタ202のゲートと、3の増幅トランジスタ202のソースおよびドレインの他方は、高速に所望の電圧に設定される。

スイッチトランジスタ401がオフされ、第4の基準電圧VR4とFDとが切断された状態で、ノイズ抑制動作と、信号レベルまたはリセットレベルの読み出し動作とが実施される。

FDのノイズが十分抑制され、電圧が安定した状態で、所望の期間において、FDに信号電荷を蓄積させる。その後、時刻t32において、第2の選択トランジスタ501をオンし、第4の増幅トランジスタ203を信号読み出しライン7と電気的に接続する。これにより、第4の増幅トランジスタ203と定電流源6とは、ソースフォロア回路を形成する。FDに蓄積された信号電荷は、ソースフォロア回路で増幅され、信号読み出しライン7を介して、周辺回路(CDS回路、A/D回路等)に出力される。

図35を参照して、本実施形態によるカメラシステム600を説明する。

1A 有機光電膜

1B フォトダイオー

2、2A、2B 増幅器

3、3’ 帯域制御部

3A、3B 帯域制御回路

4A リセット回路

4B スイッチ部

5、5B、5C 出力選択部

6、8、144 定電流源

7 信号読み出しライン

9 第1の容量素子

10 第2の容量素子

11 第1のスイッチ素子

12 第2のスイッチ素子

13 第3のスイッチ素子

14 第4のスイッチ素子

20、40 切替回路

30、30’ フィードバック回路

50A、50B、50B’、50C、50C’、50D、50E 読み出

し回路

100 撮像装置

110A、110B、110C、110D、110E 単位画素セル

120 電源配線

130 蓄積制御線

141 垂直走査回路

142 カラム信号処理回路

143 水平信号読み出し回路

170 垂直信号線

180 水平信号共通線

200 第1の増幅トランジスタ

201 第2の増幅トランジスタ

202 第3の増幅トランジスタ

203 第4の増幅トランジスタ

300 第1の帯域制御トランジスタ

301 第2の帯域制御トランジスタ

400 リセットトランジスタ

401 スイッチトランジスタ

500 第1の選択トランジスタ

501 第2の選択トランジスタ

502 第3の選択トランジスタ

503 第4の選択トランジスタ

600 カメラシステム

601 レンズ光学系

602 固体撮像装置

603 システムコントローラ

604 信号処理部

CON1、CON3 帯域制御信号線

CON2 リセット制御信号線

CON4 第4の制御信号線

CON5 第5の制御信号線

CON6 第6の制御信号線

CON7 第7の制御信号線

CON8、CON9 選択制御信号線 FD 電荷蓄積部

RD 画素内ノード

Vp 基準電圧/制御電圧

VR1、VR2、VR3、VR4 基準電圧/制御電圧源

VA1、VA2、VB1、VB2 基準電圧/制御電圧源

V1、V2、V3、V4 制御信号

Claims (10)

- 入射光を光電変換し電気信号を生成する光電変換部と、

前記電気信号を検出する信号検出回路と、

を含む単位画素セルを備え、

前記信号検出回路は、

前記電気信号を増幅する第1のトランジスタと、

前記第1のトランジスタの出力を、前記単位画素セルの外部に選択的に出力する第2のトランジスタと、

前記電気信号を、前記第1のトランジスタを介して負帰還させる帰還経路を形成するフィードバック回路と、

を有し、

前記フィードバック回路は、前記帰還経路上に第3のトランジスタと、第1の容量素子と、第2の容量素子とを含み、

前記第3のトランジスタのゲートには、互いに異なる少なくとも3種類の電圧を出力する電圧制御回路が接続され、

前記第1の容量素子は、前記第3のトランジスタのソースおよびドレインの一方に電気的に接続され、

前記第2の容量素子は、前記光電変換部と、前記第3のトランジスタのソースおよびドレインの前記一方と、に電気的に接続されている、撮像装置。 - 前記第2のトランジスタは、垂直信号線を介して前記第1のトランジスタの出力を前記単位画素セルの外部に選択的に出力し、

前記垂直信号線は、前記第2のトランジスタのソースおよびドレインの一方に電気的に接続され、

前記フィードバック回路は、前記第2のトランジスタを介さずに、前記電気信号を負帰還させる、請求項1に記載の撮像装置。 - 前記第1のトランジスタは、前記帰還経路上に配置されている、請求項1または2に記載の撮像装置。

- 前記第1のトランジスタの出力側に定電流源が接続されている、請求項1から3のいずれか1項に記載の撮像装置。

- 前記信号検出回路は、前記電気信号を初期化するリセットトランジスタをさらに備える、請求項1から4のいずれか1項に記載の撮像装置。

- 前記フィードバック回路が前記帰還経路を形成する第1の期間と、前記フィードバック回路が前記帰還経路を形成しない第2の期間との間で、前記信号検出回路が前記電気信号を増幅する増幅率が異なる、請求項1から4のいずれか1項に記載の撮像装置。

- 前記リセットトランジスタは、前記帰還経路上に配置される、請求項5に記載の撮像装置。

- 前記リセットトランジスタは、負帰還トランジスタである、請求項7に記載の撮像装置。

- 前記第1の容量素子と前記第2の容量素子とは、前記光電変換部と基準電圧との間に配置されている、請求項1から8のいずれか1項に記載の撮像装置。

- 前記第1の容量素子の容量は、前記第2の容量素子の容量よりも大きい、請求項1から9のいずれか1項に記載の撮像装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN201510828816.8A CN105744183B (zh) | 2014-12-26 | 2015-11-25 | 摄像装置 |

| CN202010765317.XA CN111901540B (zh) | 2014-12-26 | 2015-11-25 | 摄像装置 |

| US14/965,687 US10141364B2 (en) | 2014-12-26 | 2015-12-10 | Imaging device including unit pixel cell |

| US16/161,903 US10672827B2 (en) | 2014-12-26 | 2018-10-16 | Imaging device including unit pixel cell |

| US16/859,623 US11482558B2 (en) | 2014-12-26 | 2020-04-27 | Imaging device including unit pixel cell |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014264696 | 2014-12-26 | ||

| JP2014264696 | 2014-12-26 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017219972A Division JP6754975B2 (ja) | 2014-12-26 | 2017-11-15 | 撮像装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016127593A JP2016127593A (ja) | 2016-07-11 |

| JP6323813B2 true JP6323813B2 (ja) | 2018-05-16 |

Family

ID=56359882

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015207303A Active JP6323813B2 (ja) | 2014-12-26 | 2015-10-21 | 撮像装置 |

| JP2017219972A Active JP6754975B2 (ja) | 2014-12-26 | 2017-11-15 | 撮像装置 |

| JP2020133236A Active JP7029683B2 (ja) | 2014-12-26 | 2020-08-05 | 撮像装置 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017219972A Active JP6754975B2 (ja) | 2014-12-26 | 2017-11-15 | 撮像装置 |

| JP2020133236A Active JP7029683B2 (ja) | 2014-12-26 | 2020-08-05 | 撮像装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (3) | JP6323813B2 (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108337409B (zh) * | 2017-01-19 | 2021-06-22 | 松下知识产权经营株式会社 | 摄像装置及照相机系统 |

| CN108878462B (zh) | 2017-05-12 | 2023-08-15 | 松下知识产权经营株式会社 | 摄像装置及照相机系统 |

| WO2019087472A1 (ja) * | 2017-10-30 | 2019-05-09 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像素子 |

| WO2019167551A1 (ja) | 2018-02-28 | 2019-09-06 | パナソニックIpマネジメント株式会社 | 撮像装置 |

| CN110556390B (zh) | 2018-05-31 | 2024-09-27 | 松下知识产权经营株式会社 | 摄像装置 |

| JP2019212900A (ja) | 2018-05-31 | 2019-12-12 | パナソニックIpマネジメント株式会社 | 撮像装置 |

| CN110650300B (zh) | 2018-06-26 | 2024-08-13 | 松下知识产权经营株式会社 | 摄像装置 |

| JP7316673B2 (ja) | 2018-10-19 | 2023-07-28 | パナソニックIpマネジメント株式会社 | 撮像装置 |

| JP7478968B2 (ja) * | 2019-03-20 | 2024-05-08 | パナソニックIpマネジメント株式会社 | 撮像装置 |

| WO2021059882A1 (ja) * | 2019-09-26 | 2021-04-01 | パナソニックIpマネジメント株式会社 | 撮像装置 |

| CN114788263A (zh) | 2019-12-23 | 2022-07-22 | 松下知识产权经营株式会社 | 摄像装置 |

| WO2022196155A1 (ja) * | 2021-03-16 | 2022-09-22 | パナソニックIpマネジメント株式会社 | 撮像装置及びその駆動方法 |

| DE112022004941T5 (de) * | 2021-10-15 | 2024-08-14 | Sony Semiconductor Solutions Corporation | Festkörperbildsensor, bildgebungsvorrichtung und verfahren zum steuern eines festkörperbildsensors |

| WO2023166832A1 (ja) * | 2022-03-03 | 2023-09-07 | パナソニックIpマネジメント株式会社 | 撮像装置 |

| WO2024070115A1 (ja) * | 2022-09-30 | 2024-04-04 | パナソニックIpマネジメント株式会社 | 撮像装置 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH10170658A (ja) * | 1996-12-06 | 1998-06-26 | Toshiba Corp | X線撮像装置 |

| US6424375B1 (en) * | 1999-09-21 | 2002-07-23 | Pixel Devices, International | Low noise active reset readout for image sensors |

| JP4132850B2 (ja) * | 2002-02-06 | 2008-08-13 | 富士通株式会社 | Cmosイメージセンサおよびその制御方法 |

| US7215369B2 (en) * | 2003-04-02 | 2007-05-08 | Micron Technology, Inc. | Compact pixel reset circuits using reversed current readout |

| EP1508920A1 (en) * | 2003-08-21 | 2005-02-23 | STMicroelectronics S.A. | CMOS light sensing cell |

| JP2012151369A (ja) * | 2011-01-20 | 2012-08-09 | Panasonic Corp | 固体撮像装置 |

| JP6132213B2 (ja) * | 2012-08-09 | 2017-05-24 | パナソニックIpマネジメント株式会社 | 固体撮像装置 |

| JP6134979B2 (ja) * | 2013-06-04 | 2017-05-31 | 富士フイルム株式会社 | 固体撮像素子および撮像装置 |

-

2015

- 2015-10-21 JP JP2015207303A patent/JP6323813B2/ja active Active

-

2017

- 2017-11-15 JP JP2017219972A patent/JP6754975B2/ja active Active

-

2020

- 2020-08-05 JP JP2020133236A patent/JP7029683B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2018061271A (ja) | 2018-04-12 |

| JP7029683B2 (ja) | 2022-03-04 |

| JP2020188511A (ja) | 2020-11-19 |

| JP2016127593A (ja) | 2016-07-11 |

| JP6754975B2 (ja) | 2020-09-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7029683B2 (ja) | 撮像装置 | |

| CN105744183B (zh) | 摄像装置 | |

| KR200492043Y1 (ko) | 향상된 셔터 효율을 가지는 글로벌 셔터 이미지 센서 픽셀들 | |

| US11381769B2 (en) | Imaging device | |

| JP3734717B2 (ja) | イメージセンサ | |

| JP5959829B2 (ja) | 固体撮像装置 | |

| US9185273B2 (en) | Imaging pixels with improved dynamic range | |

| US9502457B2 (en) | Global shutter image sensor pixels having centralized charge storage regions | |

| US9906746B2 (en) | Solid-state image pickup device and image pickup apparatus | |

| US9456159B1 (en) | Pixels with an active reset circuit in CMOS image sensors | |

| JP2017005435A (ja) | 撮像装置および信号処理回路 | |

| US9794497B2 (en) | Solid-state imaging device controlling read-out of signals from pixels in first and second areas | |

| US10116854B2 (en) | Photoelectric conversion apparatus, switching an electric path between a conductive state and a non-conductive state | |

| JP2017092554A (ja) | 固体撮像装置及び撮像システム | |

| CN111726547B (zh) | 摄像装置 | |

| JP2009225301A (ja) | 光電変換装置の駆動方法 | |

| US11653117B2 (en) | Imaging device | |

| US20220256106A1 (en) | Imaging device and control method | |

| JP2017011514A (ja) | 固体撮像装置及びその駆動方法 | |

| JP2011044921A (ja) | 固体撮像素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160714 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170417 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170509 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170705 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170919 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180313 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180402 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6323813 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |