JP6151568B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6151568B2 JP6151568B2 JP2013112441A JP2013112441A JP6151568B2 JP 6151568 B2 JP6151568 B2 JP 6151568B2 JP 2013112441 A JP2013112441 A JP 2013112441A JP 2013112441 A JP2013112441 A JP 2013112441A JP 6151568 B2 JP6151568 B2 JP 6151568B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- storage unit

- circuit

- correction code

- error correction

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C14/00—Digital stores characterised by arrangements of cells having volatile and non-volatile storage properties for back-up when the power is down

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/28—Supervision thereof, e.g. detecting power-supply failure by out of limits supervision

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/30—Means for acting in the event of power-supply failure or interruption, e.g. power-supply fluctuations

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3206—Monitoring of events, devices or parameters that trigger a change in power modality

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3206—Monitoring of events, devices or parameters that trigger a change in power modality

- G06F1/3215—Monitoring of peripheral devices

- G06F1/3225—Monitoring of peripheral devices of memory devices

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/325—Power saving in peripheral device

- G06F1/3275—Power saving in memory, e.g. RAM, cache

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1048—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices using arrangements adapted for a specific error detection or correction feature

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/14—Error detection or correction of the data by redundancy in operation

- G06F11/1402—Saving, restoring, recovering or retrying

- G06F11/1415—Saving, restoring, recovering or retrying at system level

- G06F11/1441—Resetting or repowering

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/023—Free address space management

- G06F12/0238—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory

- G06F12/0246—Memory management in non-volatile memory, e.g. resistive RAM or ferroelectric memory in block erasable memory, e.g. flash memory

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/005—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor comprising combined but independently operative RAM-ROM, RAM-PROM, RAM-EPROM cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1697—Power supply circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/143—Detection of memory cassette insertion or removal; Continuity checks of supply or ground lines; Detection of supply variations, interruptions or levels ; Switching between alternative supplies

- G11C5/144—Detection of predetermined disconnection or reduction of power supply, e.g. power down or power standby

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C2029/0411—Online error correction

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Quality & Reliability (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- Power Sources (AREA)

Description

図1に示す図は、電源供給を停止してもデータの保持が可能な半導体装置のブロック図である。図1に示す半導体装置100は、データ処理回路101、データ退避時間制御回路102、パワーゲーティング制御回路103を有する。

本実施の形態では、実施の形態1で説明した半導体装置において、より具体的な構成を示し、その動作について詳述する。なお実施の形態1で示す構成と同じ構成については同じ符号を付し、重複する説明を省略し、上記実施の形態1での説明を援用するものとする。

本実施の形態では、上記実施の形態1及び実施の形態2で説明した揮発性記憶部及び不揮発性記憶部の構成について説明する。図5には、揮発性記憶部及び不揮発性記憶部のブロック図の一例を示す。

本実施の形態では、上記実施の形態3で説明したOSトランジスタ611と、nチャネル型トランジスタ613及びpチャネル型トランジスタ612と、を積層して設けた半導体装置の断面図の構成について図9に示し、説明する。

D_1 データ

Q_n 出力端子

Q_1 出力端子

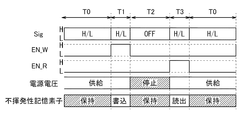

T0 期間

T1 期間

T2 期間

T3 期間

100 半導体装置

101 データ処理回路

102 データ退避時間制御回路

103 パワーゲーティング制御回路

105 汎用レジスタ

106 誤り訂正符号用レジスタ

107 誤り訂正符号回路

108 揮発性記憶部

109 不揮発性記憶部

110 揮発性記憶部

111 不揮発性記憶部

112 スイッチ

201 誤り訂正符号計算回路

202 誤り訂正符号比較回路

203 訂正回路

211 エラー信号記憶回路

212 データ退避時間決定フラグ記憶回路

221 データ退避時間カウンター

321 下部素子層

322 配線層

323 上部素子層

333 基板

334 BOX層

335 SOI層

336 n型不純物領域

337 ゲート絶縁層

338 ゲート電極

339 p型不純物領域

340 絶縁層

341 配線

342 素子分離絶縁層

344 絶縁層

345 絶縁層

351 配線

352 配線

353 配線

361 ゲート絶縁層

362 酸化物半導体膜

363A ソース電極

363B ドレイン電極

364 絶縁層

365 バックゲート電極

501 単位記憶部

502 揮発性記憶部

503 不揮発性記憶部

511 制御回路

512 不揮発性記憶素子

513 制御回路

601 制御回路

602 可変抵抗記憶素子

603 制御回路

611 OSトランジスタ

612 pチャネル型トランジスタ

613 nチャネル型トランジスタ

614 nチャネル型トランジスタ

615 インバータ

621 制御回路

622 不揮発性記憶素子

623 制御回路

Claims (3)

- データ退避時間制御回路と、

パワーゲーティング制御回路と、

汎用レジスタ、誤り訂正符号用レジスタ、及び誤り訂正符号回路を有するデータ処理回路と、を有し、

前記汎用レジスタ及び前記誤り訂正符号用レジスタは、それぞれ揮発性記憶部及び不揮発性記憶部を有し、

前記データ退避時間制御回路は、前記誤り訂正符号用レジスタの不揮発性記憶部に記憶された誤り訂正符号を前記誤り訂正符号回路で検出して得られるエラーの有無に従って、前記パワーゲーティング制御回路より出力され、前記汎用レジスタの揮発性記憶部から不揮発性記憶部に記憶するデータを記憶するためのデータ退避時間を変更する回路である半導体装置。 - 請求項1において、

前記パワーゲーティング制御回路は、前記データ退避時間制御回路によって制御されるデータ退避時間カウンターを有し、

前記データ退避時間カウンターは、前記データ退避時間カウンターのカウント値に従って、前記データ処理回路への電源供給を制御する半導体装置。 - 請求項1または請求項2において、

前記不揮発性記憶部は、不揮発性記憶素子を有し、

前記不揮発性記憶素子は、酸化物半導体層を有するトランジスタを用いた電荷の保持により前記データまたは前記誤り訂正符号の保持を行う半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013112441A JP6151568B2 (ja) | 2012-06-01 | 2013-05-29 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012125651 | 2012-06-01 | ||

| JP2012125651 | 2012-06-01 | ||

| JP2013112441A JP6151568B2 (ja) | 2012-06-01 | 2013-05-29 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014006889A JP2014006889A (ja) | 2014-01-16 |

| JP2014006889A5 JP2014006889A5 (ja) | 2016-06-23 |

| JP6151568B2 true JP6151568B2 (ja) | 2017-06-21 |

Family

ID=49671834

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013112441A Expired - Fee Related JP6151568B2 (ja) | 2012-06-01 | 2013-05-29 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9058867B2 (ja) |

| JP (1) | JP6151568B2 (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6185311B2 (ja) * | 2012-07-20 | 2017-08-23 | 株式会社半導体エネルギー研究所 | 電源制御回路、及び信号処理回路 |

| TWI618058B (zh) | 2013-05-16 | 2018-03-11 | 半導體能源研究所股份有限公司 | 半導體裝置 |

| US9905700B2 (en) | 2015-03-13 | 2018-02-27 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device or memory device and driving method thereof |

| US9887010B2 (en) | 2016-01-21 | 2018-02-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, memory device, and driving method thereof |

| US10223198B2 (en) * | 2016-02-18 | 2019-03-05 | Micron Technology, Inc. | Error rate reduction |

| US10120470B2 (en) | 2016-07-22 | 2018-11-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device and electronic device |

| US10489253B2 (en) * | 2017-05-16 | 2019-11-26 | International Business Machines Corporation | On-demand GPR ECC error detection and scrubbing for a multi-slice microprocessor |

| KR102558422B1 (ko) * | 2018-11-07 | 2023-07-24 | 에스케이하이닉스 주식회사 | 파워 게이팅 시스템 |

| JP2022080162A (ja) * | 2020-11-17 | 2022-05-27 | ソニーセミコンダクタソリューションズ株式会社 | 半導体回路 |

| WO2025163443A1 (ja) * | 2024-01-31 | 2025-08-07 | 株式会社半導体エネルギー研究所 | 記憶装置 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61193591A (ja) * | 1985-02-22 | 1986-08-28 | Nec Corp | 主記憶装置の障害処理方式 |

| US5414861A (en) * | 1991-09-11 | 1995-05-09 | Fujitsu Limited | Data protection system using different levels of reserve power to maintain data in volatile memories for any period of time |

| US5535399A (en) * | 1993-09-30 | 1996-07-09 | Quantum Corporation | Solid state disk drive unit having on-board backup non-volatile memory |

| JPH08272701A (ja) * | 1995-03-30 | 1996-10-18 | Mitsubishi Electric Corp | メモリ装置 |

| JPH09288619A (ja) * | 1996-04-22 | 1997-11-04 | Mitsubishi Electric Corp | 主記憶装置 |

| JPH10260912A (ja) * | 1997-03-17 | 1998-09-29 | Mitsubishi Electric Corp | メモリカード |

| US6810347B2 (en) * | 2003-01-09 | 2004-10-26 | Micrel, Inc. | Robust power-on meter and method |

| US6785191B2 (en) * | 2003-01-09 | 2004-08-31 | Micrel, Inc. | Robust power-on meter and method using a limited-write memory |

| US7370260B2 (en) * | 2003-12-16 | 2008-05-06 | Freescale Semiconductor, Inc. | MRAM having error correction code circuitry and method therefor |

| JP4235919B2 (ja) * | 2006-10-06 | 2009-03-11 | コニカミノルタビジネステクノロジーズ株式会社 | 情報処理装置及びプログラム |

| US8301833B1 (en) * | 2007-06-01 | 2012-10-30 | Netlist, Inc. | Non-volatile memory module |

| US8325554B2 (en) * | 2008-07-10 | 2012-12-04 | Sanmina-Sci Corporation | Battery-less cache memory module with integrated backup |

| US8671258B2 (en) * | 2009-03-27 | 2014-03-11 | Lsi Corporation | Storage system logical block address de-allocation management |

| JP4956640B2 (ja) * | 2009-09-28 | 2012-06-20 | 株式会社東芝 | 磁気メモリ |

| US20120054524A1 (en) * | 2010-08-31 | 2012-03-01 | Infinidat Ltd. | Method and system for reducing power consumption of peripherals in an emergency shut-down |

| TWI525614B (zh) | 2011-01-05 | 2016-03-11 | 半導體能源研究所股份有限公司 | 儲存元件、儲存裝置、及信號處理電路 |

| US8902653B2 (en) * | 2011-08-12 | 2014-12-02 | Micron Technology, Inc. | Memory devices and configuration methods for a memory device |

-

2013

- 2013-05-23 US US13/900,578 patent/US9058867B2/en active Active

- 2013-05-29 JP JP2013112441A patent/JP6151568B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US9058867B2 (en) | 2015-06-16 |

| US20130326309A1 (en) | 2013-12-05 |

| JP2014006889A (ja) | 2014-01-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6151568B2 (ja) | 半導体装置 | |

| JP5839477B2 (ja) | 記憶回路 | |

| JP6143388B2 (ja) | 半導体装置 | |

| JP6068994B2 (ja) | 半導体装置 | |

| US9183894B2 (en) | Semiconductor device | |

| JP6381716B2 (ja) | 半導体装置 | |

| US8675382B2 (en) | Programmable LSI | |

| US8705292B2 (en) | Nonvolatile memory circuit with an oxide semiconductor transistor for reducing power consumption and electronic device | |

| JP5985339B2 (ja) | 半導体装置 | |

| JP6188857B2 (ja) | 半導体装置 | |

| US8681533B2 (en) | Memory circuit, signal processing circuit, and electronic device | |

| JP5952077B2 (ja) | 記憶素子 | |

| US9058892B2 (en) | Semiconductor device and shift register | |

| JP6122709B2 (ja) | 信号処理回路 | |

| JP6391728B2 (ja) | 半導体装置 | |

| JP2013182998A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160504 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160504 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170214 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170215 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170413 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170516 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170525 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6151568 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |