JP6127816B2 - 半導体集積回路装置、電子機器、及び、メモリー制御方法 - Google Patents

半導体集積回路装置、電子機器、及び、メモリー制御方法 Download PDFInfo

- Publication number

- JP6127816B2 JP6127816B2 JP2013160206A JP2013160206A JP6127816B2 JP 6127816 B2 JP6127816 B2 JP 6127816B2 JP 2013160206 A JP2013160206 A JP 2013160206A JP 2013160206 A JP2013160206 A JP 2013160206A JP 6127816 B2 JP6127816 B2 JP 6127816B2

- Authority

- JP

- Japan

- Prior art keywords

- clock signal

- signal

- circuit

- write address

- read address

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

図1は、本発明の第1の実施形態に係る半導体集積回路装置の構成例を示すブロック図である。この半導体集積回路装置は、クロック信号のスペクトラムを拡散することによって電磁放射ノイズを低減するSSCG方式を採用しており、例えば、携帯電話や液晶テレビ等の電子機器に搭載されて、液晶表示パネルを駆動するために用いられる。

図2は、図1に示す変調回路の構成例を示すブロック図である。図2に示すように、変調回路20は、遅延回路21と、選択回路22とを含んでいる。遅延回路21は、基準クロック信号CK1に基づいて、複数の異なる位相を有する多相クロック信号を出力する。選択回路22は、選択信号に従って、遅延回路21から出力される多相クロック信号の内の1つを選択することにより、変調された周波数を有する変調クロック信号CK2を生成する。

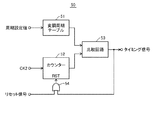

図9は、本発明の第2の実施形態に係る半導体集積回路装置の構成例を示すブロック図である。第2の実施形態においては、ライトアドレスカウンター71が、タイミング信号生成回路50によって生成されるタイミング信号によって、ライトアドレスWAD[3:0]とリードアドレスRAD[3:0]との間隔が初期状態となるように同期化される。これにより、リードアドレスRAD[3:0]を基準としてライトアドレスWAD[3:0]が定期的に再設定されるので、外部からのノイズ等による誤動作からデュアルポートRAM73を正常動作に復帰させることができる。また、タイミング信号がアクティブとなる際には、基準クロック信号CK1及び変調クロック信号CK2の位相が揃っているので、デュアルポートRAM73が誤動作していない場合には、デュアルポートRAM73から読み出される画像データの連続性を維持することができる。

図10は、本発明の一実施形態に係るメモリー制御方法を示すフローチャートである。このメモリー制御方法は、図1又は図9に示す半導体集積回路装置において実施することができる。

Claims (8)

- 一定の周波数を有する第1のクロック信号に基づいて、変調された周波数を有する第2のクロック信号を生成する変調回路と、

所定の周期毎に前記第1のクロック信号と前記第2のクロック信号との位相差を所定の範囲内にすると共に、前記所定の周期において前記第2のクロック信号の周波数を変化させるように、前記変調回路を制御する制御回路と、

初期状態において設定された第1の初期値に基づいて前記第1のクロック信号に同期するライトアドレスを生成するライトアドレスカウンターと、

初期状態において設定された第2の初期値に基づいて前記第2のクロック信号に同期するリードアドレスを生成するリードアドレスカウンターと、

前記第1のクロック信号に同期して、前記ライトアドレスによって指定されたセルにデータが書き込まれると共に、前記第2のクロック信号に同期して、前記リードアドレスによって指定されたセルからデータが読み出されるメモリーと、

を具備し、前記ライトアドレスカウンターと前記リードアドレスカウンターとの内の一方が、前記所定の周期毎に、前記ライトアドレスと前記リードアドレスとの間隔が初期状態となるように同期化される、半導体集積回路装置。 - 前記第1又は第2のクロック信号のパルスをカウントすることにより、前記所定の周期毎にアクティブとなるタイミング信号を生成するタイミング信号生成回路を具備し、

前記制御回路は、前記タイミング信号がアクティブとなる際に前記第1のクロック信号と前記第2のクロック信号との位相差を所定の範囲内にすると共に、前記所定の周期において前記第2のクロック信号の周波数を変化させ、

前記ライトアドレスカウンターは、前記第1の初期値を前記第1のクロック信号に同期してインクリメントすることにより得られる第1のカウント値に基づいて、ライトアドレスを生成し、

前記リードアドレスカウンターは、前記第2の初期値を前記第2のクロック信号に同期してインクリメントすることにより得られる第2のカウント値に基づいて、リードアドレスを生成し、

前記ライトアドレスカウンターと前記リードアドレスカウンターとの内の一方は、前記タイミング信号によって同期化される、請求項1記載の半導体集積回路装置。 - 前記ライトアドレスカウンターが、前記所定の周期毎に同期化されたときに、前記リードアドレスの値に基づいて第1のカウント値を設定し、その後、前記第1のカウント値を前記第1のクロック信号に同期してインクリメントすることにより、ライトアドレスを生成する、請求項1または2記載の半導体集積回路装置。

- 前記リードアドレスカウンターが、前記所定の周期毎に同期化されたときに、前記ライトアドレスの値に基づいて第2のカウント値を設定し、その後、前記第2のカウント値を前記第2のクロック信号に同期してインクリメントすることにより、リードアドレスを生成する、請求項1または2記載の半導体集積回路装置。

- 前記変調回路が、

前記第1のクロック信号に基づいて、複数の異なる位相を有する多相クロック信号を出力する遅延回路と、

選択信号に従って前記多相クロック信号の内の1つを選択することにより、前記第2のクロック信号を生成する選択回路と、

を含み、前記制御回路が、前記所定の周期毎に前記第1のクロック信号と前記第2のクロック信号との位相差を所定の範囲内にすると共に、前記所定の周期において前記第2のクロック信号の周波数を変化させるように、前記選択信号を生成する、請求項1〜4のいずれか1項記載の半導体集積回路装置。 - 前記第2のクロック信号の生成が停止したときに内部リセット信号をアクティブにするクロック停止検出回路をさらに具備し、

前記タイミング信号生成回路が、前記内部リセット信号によってリセットされる、

請求項1〜5のいずれか1項記載の半導体集積回路装置。 - 請求項1〜6のいずれか1項記載の半導体集積回路装置を具備する電子機器。

- 一定の周波数を有する第1のクロック信号に基づいて、変調された周波数を有する第2のクロック信号を生成するステップと、

所定の周期毎に前記第1のクロック信号と前記第2のクロック信号との位相差を所定の範囲内にすると共に、前記所定の周期において前記第2のクロック信号の周波数を変化させるステップと、

初期状態において設定された第1の初期値に基づいて前記第1のクロック信号に同期するライトアドレスを生成するステップと、

初期状態において設定された第2の初期値に基づいて前記第2のクロック信号に同期するリードアドレスを生成するステップと、

前記所定の周期毎に、前記ライトアドレスと前記リードアドレスとの間隔が初期状態となるように同期化するステップと、

メモリーにおいて、前記第1のクロック信号に同期して、前記ライトアドレスによって指定されたセルにデータを書き込むと共に、前記第2のクロック信号に同期して、前記リードアドレスによって指定されたセルからデータを読み出すステップと、

を具備するメモリー制御方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013160206A JP6127816B2 (ja) | 2013-08-01 | 2013-08-01 | 半導体集積回路装置、電子機器、及び、メモリー制御方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013160206A JP6127816B2 (ja) | 2013-08-01 | 2013-08-01 | 半導体集積回路装置、電子機器、及び、メモリー制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015032938A JP2015032938A (ja) | 2015-02-16 |

| JP2015032938A5 JP2015032938A5 (ja) | 2016-05-12 |

| JP6127816B2 true JP6127816B2 (ja) | 2017-05-17 |

Family

ID=52517936

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013160206A Active JP6127816B2 (ja) | 2013-08-01 | 2013-08-01 | 半導体集積回路装置、電子機器、及び、メモリー制御方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6127816B2 (ja) |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0750856B2 (ja) * | 1985-12-05 | 1995-05-31 | 日本電気株式会社 | 遅延回路 |

| JP3364943B2 (ja) * | 1992-02-25 | 2003-01-08 | 株式会社日立製作所 | クロックスキュー補正回路 |

| JP2001148690A (ja) * | 1999-11-19 | 2001-05-29 | Sony Corp | クロック発生装置 |

| JP5177856B2 (ja) * | 2008-03-11 | 2013-04-10 | Necエンジニアリング株式会社 | クロック乗せ換え回路 |

| JP5987292B2 (ja) * | 2011-10-31 | 2016-09-07 | セイコーエプソン株式会社 | 半導体集積回路装置及びそれを用いた電子機器 |

-

2013

- 2013-08-01 JP JP2013160206A patent/JP6127816B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015032938A (ja) | 2015-02-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4504581B2 (ja) | リング遅延とカウンタを利用したレジスタ制御遅延固定ループ | |

| US7777543B2 (en) | Duty cycle correction circuit apparatus | |

| US7889581B2 (en) | Digital DLL circuit | |

| JP4751178B2 (ja) | 同期型半導体装置 | |

| US9824731B2 (en) | Data reading circuit | |

| US11251706B2 (en) | Multiphase switched mode power supply clocking circuits and related methods | |

| US20150015310A1 (en) | Clock delay detecting circuit and semiconductor apparatus using the same | |

| JP5987292B2 (ja) | 半導体集積回路装置及びそれを用いた電子機器 | |

| US7843743B2 (en) | Data output circuit for semiconductor memory apparatus | |

| CN111161766B (zh) | Ddr sdram物理层接口电路与ddr sdram控制装置 | |

| JP6313085B2 (ja) | 半導体装置 | |

| CN110442320B (zh) | 运用于双倍数据率存储器系统的先进先出电路 | |

| JP6127816B2 (ja) | 半導体集積回路装置、電子機器、及び、メモリー制御方法 | |

| US7392406B2 (en) | Circuit and method for generating clock signals for clocking digital signal processor and memory | |

| US7427886B2 (en) | Clock generating method and circuit thereof | |

| JP2006302056A (ja) | クロック制御回路 | |

| US7696801B2 (en) | Reset method for clock triggering digital circuit and related signal generating apparatus utilizing the reset method | |

| JP2007243601A (ja) | 半導体集積回路 | |

| WO2007125519A2 (en) | Latency optimized resynchronization solution for ddr/ddr2 sdram read path | |

| JP5560778B2 (ja) | クロック乗せ換え回路、及びクロック乗せ換え方法 | |

| EP2391007A2 (en) | Division circuit, division device, and electronic apparatus | |

| US11134189B2 (en) | Image device and operating method thereof | |

| KR100853465B1 (ko) | 내부리드신호 생성회로와 이를 포함하는 반도체 메모리장치 | |

| US11644861B2 (en) | Information processing apparatus including function blocks and generation units | |

| US8514005B2 (en) | Circuit and method for generating multiphase clock signals and corresponding indication signals |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20150113 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160317 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160317 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20160616 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20160624 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161130 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161213 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170120 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170314 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170327 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6127816 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |