JP6110693B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP6110693B2 JP6110693B2 JP2013044631A JP2013044631A JP6110693B2 JP 6110693 B2 JP6110693 B2 JP 6110693B2 JP 2013044631 A JP2013044631 A JP 2013044631A JP 2013044631 A JP2013044631 A JP 2013044631A JP 6110693 B2 JP6110693 B2 JP 6110693B2

- Authority

- JP

- Japan

- Prior art keywords

- oxide semiconductor

- semiconductor film

- film

- oxide

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 268

- 239000010408 film Substances 0.000 description 327

- 238000000034 method Methods 0.000 description 82

- 239000000758 substrate Substances 0.000 description 61

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 60

- 229910052760 oxygen Inorganic materials 0.000 description 60

- 239000001301 oxygen Substances 0.000 description 60

- 239000001257 hydrogen Substances 0.000 description 41

- 229910052739 hydrogen Inorganic materials 0.000 description 41

- 239000011701 zinc Substances 0.000 description 39

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 30

- 238000010438 heat treatment Methods 0.000 description 30

- 239000013078 crystal Substances 0.000 description 25

- 239000004973 liquid crystal related substance Substances 0.000 description 22

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 21

- 239000010410 layer Substances 0.000 description 17

- 229910052751 metal Inorganic materials 0.000 description 16

- 238000004544 sputter deposition Methods 0.000 description 16

- 239000012071 phase Substances 0.000 description 15

- 238000005401 electroluminescence Methods 0.000 description 14

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 13

- 125000004429 atom Chemical group 0.000 description 12

- 230000015572 biosynthetic process Effects 0.000 description 12

- 239000007789 gas Substances 0.000 description 12

- 239000000463 material Substances 0.000 description 12

- 239000002184 metal Substances 0.000 description 12

- 229910052782 aluminium Inorganic materials 0.000 description 11

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 11

- 230000005684 electric field Effects 0.000 description 11

- 150000002431 hydrogen Chemical class 0.000 description 11

- 238000004519 manufacturing process Methods 0.000 description 11

- 239000012298 atmosphere Substances 0.000 description 10

- 230000008569 process Effects 0.000 description 10

- 239000012535 impurity Substances 0.000 description 9

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 8

- 230000007547 defect Effects 0.000 description 8

- 229910052733 gallium Inorganic materials 0.000 description 8

- 239000000203 mixture Substances 0.000 description 8

- 238000011282 treatment Methods 0.000 description 8

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 229910052738 indium Inorganic materials 0.000 description 7

- 229910052757 nitrogen Inorganic materials 0.000 description 7

- 239000010936 titanium Substances 0.000 description 7

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 7

- 229910052721 tungsten Inorganic materials 0.000 description 7

- 239000010937 tungsten Substances 0.000 description 7

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 6

- 229910003437 indium oxide Inorganic materials 0.000 description 6

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 6

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 6

- 239000013081 microcrystal Substances 0.000 description 6

- 230000003071 parasitic effect Effects 0.000 description 6

- 239000000565 sealant Substances 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- 239000010409 thin film Substances 0.000 description 6

- 229910052719 titanium Inorganic materials 0.000 description 6

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 5

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- 239000002156 adsorbate Substances 0.000 description 5

- 239000004020 conductor Substances 0.000 description 5

- 229910044991 metal oxide Inorganic materials 0.000 description 5

- 150000004706 metal oxides Chemical class 0.000 description 5

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 5

- 238000000206 photolithography Methods 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- 239000002356 single layer Substances 0.000 description 5

- 229910052725 zinc Inorganic materials 0.000 description 5

- 229910020994 Sn-Zn Inorganic materials 0.000 description 4

- 229910009069 Sn—Zn Inorganic materials 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 4

- 229910045601 alloy Inorganic materials 0.000 description 4

- 239000000956 alloy Substances 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- 238000011109 contamination Methods 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 4

- 238000003795 desorption Methods 0.000 description 4

- 239000011261 inert gas Substances 0.000 description 4

- MWUXSHHQAYIFBG-UHFFFAOYSA-N nitrogen oxide Inorganic materials O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 4

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 description 4

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 4

- 229910001930 tungsten oxide Inorganic materials 0.000 description 4

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 4

- 239000011787 zinc oxide Substances 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 3

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 3

- MUBZPKHOEPUJKR-UHFFFAOYSA-N Oxalic acid Chemical compound OC(=O)C(O)=O MUBZPKHOEPUJKR-UHFFFAOYSA-N 0.000 description 3

- 229910052786 argon Inorganic materials 0.000 description 3

- 239000000969 carrier Substances 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 229910052804 chromium Inorganic materials 0.000 description 3

- 238000004140 cleaning Methods 0.000 description 3

- 229920001940 conductive polymer Polymers 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 230000018044 dehydration Effects 0.000 description 3

- 238000006297 dehydration reaction Methods 0.000 description 3

- 238000006356 dehydrogenation reaction Methods 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 230000005611 electricity Effects 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 239000000945 filler Substances 0.000 description 3

- 229910052735 hafnium Inorganic materials 0.000 description 3

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000011733 molybdenum Substances 0.000 description 3

- 150000002894 organic compounds Chemical class 0.000 description 3

- 238000009832 plasma treatment Methods 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 125000006850 spacer group Chemical group 0.000 description 3

- 239000003381 stabilizer Substances 0.000 description 3

- 230000003068 static effect Effects 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- UWCWUCKPEYNDNV-LBPRGKRZSA-N 2,6-dimethyl-n-[[(2s)-pyrrolidin-2-yl]methyl]aniline Chemical compound CC1=CC=CC(C)=C1NC[C@H]1NCCC1 UWCWUCKPEYNDNV-LBPRGKRZSA-N 0.000 description 2

- 229910018120 Al-Ga-Zn Inorganic materials 0.000 description 2

- 229910018137 Al-Zn Inorganic materials 0.000 description 2

- 229910018573 Al—Zn Inorganic materials 0.000 description 2

- PAYRUJLWNCNPSJ-UHFFFAOYSA-N Aniline Chemical compound NC1=CC=CC=C1 PAYRUJLWNCNPSJ-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- 108010083687 Ion Pumps Proteins 0.000 description 2

- KAESVJOAVNADME-UHFFFAOYSA-N Pyrrole Chemical compound C=1C=CNC=1 KAESVJOAVNADME-UHFFFAOYSA-N 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- 229910020833 Sn-Al-Zn Inorganic materials 0.000 description 2

- 229910020868 Sn-Ga-Zn Inorganic materials 0.000 description 2

- YTPLMLYBLZKORZ-UHFFFAOYSA-N Thiophene Chemical compound C=1C=CSC=1 YTPLMLYBLZKORZ-UHFFFAOYSA-N 0.000 description 2

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 2

- 150000001342 alkaline earth metals Chemical class 0.000 description 2

- 239000002585 base Substances 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 230000003098 cholesteric effect Effects 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 238000001704 evaporation Methods 0.000 description 2

- 230000005281 excited state Effects 0.000 description 2

- 230000001747 exhibiting effect Effects 0.000 description 2

- 239000000284 extract Substances 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- -1 lanthanum (La) Chemical class 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 238000005192 partition Methods 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 229910052727 yttrium Inorganic materials 0.000 description 2

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 2

- 229910052726 zirconium Inorganic materials 0.000 description 2

- MGWGWNFMUOTEHG-UHFFFAOYSA-N 4-(3,5-dimethylphenyl)-1,3-thiazol-2-amine Chemical compound CC1=CC(C)=CC(C=2N=C(N)SC=2)=C1 MGWGWNFMUOTEHG-UHFFFAOYSA-N 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910052684 Cerium Inorganic materials 0.000 description 1

- 239000004986 Cholesteric liquid crystals (ChLC) Substances 0.000 description 1

- 229910052692 Dysprosium Inorganic materials 0.000 description 1

- 229910052691 Erbium Inorganic materials 0.000 description 1

- 229910052693 Europium Inorganic materials 0.000 description 1

- 229910052688 Gadolinium Inorganic materials 0.000 description 1

- 206010052128 Glare Diseases 0.000 description 1

- 239000005264 High molar mass liquid crystal Substances 0.000 description 1

- 229910052689 Holmium Inorganic materials 0.000 description 1

- 102000006391 Ion Pumps Human genes 0.000 description 1

- 229910052765 Lutetium Inorganic materials 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 239000004983 Polymer Dispersed Liquid Crystal Substances 0.000 description 1

- 229910052777 Praseodymium Inorganic materials 0.000 description 1

- 229910052772 Samarium Inorganic materials 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 239000004990 Smectic liquid crystal Substances 0.000 description 1

- 229910020944 Sn-Mg Inorganic materials 0.000 description 1

- 229910052771 Terbium Inorganic materials 0.000 description 1

- 239000004974 Thermotropic liquid crystal Substances 0.000 description 1

- 229910052775 Thulium Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 229910052769 Ytterbium Inorganic materials 0.000 description 1

- 229910009369 Zn Mg Inorganic materials 0.000 description 1

- 229910007573 Zn-Mg Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 239000003929 acidic solution Substances 0.000 description 1

- 239000012670 alkaline solution Substances 0.000 description 1

- 239000011230 binding agent Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- GWXLDORMOJMVQZ-UHFFFAOYSA-N cerium Chemical compound [Ce] GWXLDORMOJMVQZ-UHFFFAOYSA-N 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000006258 conductive agent Substances 0.000 description 1

- 229920001577 copolymer Polymers 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- KBQHZAAAGSGFKK-UHFFFAOYSA-N dysprosium atom Chemical compound [Dy] KBQHZAAAGSGFKK-UHFFFAOYSA-N 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- UYAHIZSMUZPPFV-UHFFFAOYSA-N erbium Chemical compound [Er] UYAHIZSMUZPPFV-UHFFFAOYSA-N 0.000 description 1

- OGPBJKLSAFTDLK-UHFFFAOYSA-N europium atom Chemical compound [Eu] OGPBJKLSAFTDLK-UHFFFAOYSA-N 0.000 description 1

- 239000005262 ferroelectric liquid crystals (FLCs) Substances 0.000 description 1

- UIWYJDYFSGRHKR-UHFFFAOYSA-N gadolinium atom Chemical compound [Gd] UIWYJDYFSGRHKR-UHFFFAOYSA-N 0.000 description 1

- 229910001195 gallium oxide Inorganic materials 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 229910000449 hafnium oxide Inorganic materials 0.000 description 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- KJZYNXUDTRRSPN-UHFFFAOYSA-N holmium atom Chemical compound [Ho] KJZYNXUDTRRSPN-UHFFFAOYSA-N 0.000 description 1

- 150000002484 inorganic compounds Chemical class 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 229910052747 lanthanoid Inorganic materials 0.000 description 1

- 150000002602 lanthanoids Chemical class 0.000 description 1

- 229910052746 lanthanum Inorganic materials 0.000 description 1

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 1

- 238000000608 laser ablation Methods 0.000 description 1

- OHSVLFRHMCKCQY-UHFFFAOYSA-N lutetium atom Chemical compound [Lu] OHSVLFRHMCKCQY-UHFFFAOYSA-N 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 239000011572 manganese Substances 0.000 description 1

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 239000002159 nanocrystal Substances 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 238000005121 nitriding Methods 0.000 description 1

- JCXJVPUVTGWSNB-UHFFFAOYSA-N nitrogen dioxide Inorganic materials O=[N]=O JCXJVPUVTGWSNB-UHFFFAOYSA-N 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 239000001272 nitrous oxide Substances 0.000 description 1

- 239000012788 optical film Substances 0.000 description 1

- 235000006408 oxalic acid Nutrition 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 1

- 125000004430 oxygen atom Chemical group O* 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000128 polypyrrole Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- PUDIUYLPXJFUGB-UHFFFAOYSA-N praseodymium atom Chemical compound [Pr] PUDIUYLPXJFUGB-UHFFFAOYSA-N 0.000 description 1

- 230000000750 progressive effect Effects 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- KZUNJOHGWZRPMI-UHFFFAOYSA-N samarium atom Chemical compound [Sm] KZUNJOHGWZRPMI-UHFFFAOYSA-N 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 239000007790 solid phase Substances 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- GZCRRIHWUXGPOV-UHFFFAOYSA-N terbium atom Chemical compound [Tb] GZCRRIHWUXGPOV-UHFFFAOYSA-N 0.000 description 1

- 229920001187 thermosetting polymer Polymers 0.000 description 1

- 229930192474 thiophene Natural products 0.000 description 1

- FRNOGLGSGLTDKL-UHFFFAOYSA-N thulium atom Chemical compound [Tm] FRNOGLGSGLTDKL-UHFFFAOYSA-N 0.000 description 1

- LEONUFNNVUYDNQ-UHFFFAOYSA-N vanadium atom Chemical compound [V] LEONUFNNVUYDNQ-UHFFFAOYSA-N 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- NAWDYIZEMPQZHO-UHFFFAOYSA-N ytterbium Chemical compound [Yb] NAWDYIZEMPQZHO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41733—Source or drain electrodes for field effect devices for thin film transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

Description

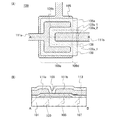

本実施の形態では、電気特性の優れたトランジスタの構造、及びそれを生産性高く作製する方法について、図1及び図2を用いて説明する。

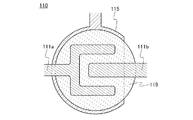

本実施の形態では、実施の形態1に示すトランジスタと上面形状が異なるトランジスタについて、図5を用いて説明する。

本実施の形態では、実施の形態1及び実施の形態2に示すトランジスタにおいて、酸化物半導体膜中に含まれる水素濃度、及び酸素欠損を低減したトランジスタの作製方法について、図2を用いて説明する。なお、本実施の形態に示す工程の一以上と、実施の形態1に示すトランジスタの作製工程とが組み合わさればよく、全て組み合わせる必要はない。

本実施の形態では、実施の形態1乃至実施の形態3に示すトランジスタにおいて、酸化物半導体膜中に含まれる酸素欠損を低減したトランジスタの作製方法について、図2を用いて説明する。なお、本実施の形態に示す工程の一以上と、実施の形態1及び実施の形態3に示すトランジスタの作製工程とが組み合わさればよく、全て組み合わせる必要はない。

上記実施の形態で一例を示したトランジスタを用いて表示機能を有する半導体装置(表示装置ともいう。)を作製することができる。また、トランジスタを含む駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。本実施の形態では、上記実施の形態で一例を示したトランジスタを用いた表示装置の例について、図6及び図7を用いて説明する。なお、図7(A)及び図7(B)は、図6(B)中でM−Nの一点鎖線で示した部位の断面構成を示す断面図である。

Claims (5)

- 第1の端部と、前記第1の端部とは反対側にある第2の端部と、を有するゲート電極と、

前記ゲート電極に接する領域を有するゲート絶縁膜と、

前記ゲート絶縁膜を介して前記ゲート電極の上方に設けられ、第3の端部と、前記第3の端部とは反対側にある第4の端部と、を有する酸化物半導体膜と、

前記酸化物半導体膜と電気的に接続され、第1の部分と、第2の部分と、第3の部分と、第4の部分と、を有する第1の電極と、

前記酸化物半導体膜と電気的に接続された第2の電極と、

を有し、

前記第1の部分は、前記第3の部分を介して前記第2の部分と電気的に接続され、

前記第3の部分は、前記第4の部分と電気的に接続され、

前記第1の部分と、前記第2の部分と、前記第3の部分とは、前記酸化物半導体膜と重なる領域を有し、

前記第4の部分は、前記第3の端部と重なる領域を越えて延びて設けられた領域を有し、

前記第4の部分は、前記第1の端部と重なる領域を越えて延びて設けられた領域を有し、

前記第1の端部は、前記第3の端部よりも外側にあり、

前記第2の電極は、前記第1の部分と前記第2の部分との間に配置された領域を有し、

前記第2の電極は、前記第2の端部と重なる領域を越えて延びて設けられた領域を有し、

前記第2の電極は、前記第4の端部と重なる領域を越えて延びて設けられた領域を有し、

前記第2の端部は、前記第4の端部よりも内側にあることを特徴とする半導体装置。 - 請求項1において、

前記第1の部分と、前記第2の部分とは、前記第4の端部と重ならないことを特徴とする半導体装置。 - 請求項1において、

前記第1の部分は、前記第4の端部と重なる領域を越えて延びて設けられた領域を有し、

前記第2の部分は、前記第4の端部と重なる領域を越えて延びて設けられた領域を有することを特徴とする半導体装置。 - 請求項1乃至3のいずれか一項において、

前記酸化物半導体膜は、上面が円形の形状を有することを特徴とする半導体装置。 - 請求項1乃至4のいずれか一項において、

前記ゲート電極は、上面が円形の一部の形状を有することを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013044631A JP6110693B2 (ja) | 2012-03-14 | 2013-03-06 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012057738 | 2012-03-14 | ||

| JP2012057738 | 2012-03-14 | ||

| JP2013044631A JP6110693B2 (ja) | 2012-03-14 | 2013-03-06 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013219335A JP2013219335A (ja) | 2013-10-24 |

| JP2013219335A5 JP2013219335A5 (ja) | 2016-04-14 |

| JP6110693B2 true JP6110693B2 (ja) | 2017-04-05 |

Family

ID=49156825

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013044631A Expired - Fee Related JP6110693B2 (ja) | 2012-03-14 | 2013-03-06 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20130240872A1 (ja) |

| JP (1) | JP6110693B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9112037B2 (en) | 2012-02-09 | 2015-08-18 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP6001308B2 (ja) | 2012-04-17 | 2016-10-05 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US10529740B2 (en) * | 2013-07-25 | 2020-01-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including semiconductor layer and conductive layer |

| JP6541398B2 (ja) | 2014-04-11 | 2019-07-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9722090B2 (en) * | 2014-06-23 | 2017-08-01 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including first gate oxide semiconductor film, and second gate |

| EP2960943B1 (en) * | 2014-06-27 | 2019-08-07 | LG Display Co., Ltd. | Thin film transistor of display apparatus |

| JP6827328B2 (ja) | 2016-01-15 | 2021-02-10 | 株式会社半導体エネルギー研究所 | 半導体装置及び電子機器 |

| CN114792701A (zh) * | 2021-01-24 | 2022-07-26 | 张葳葳 | 一种主动驱动无机发光二极管显示和照明器件及其制作方法 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5229644A (en) * | 1987-09-09 | 1993-07-20 | Casio Computer Co., Ltd. | Thin film transistor having a transparent electrode and substrate |

| JP3276930B2 (ja) * | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| JP3415602B2 (ja) * | 2000-06-26 | 2003-06-09 | 鹿児島日本電気株式会社 | パターン形成方法 |

| JP4211250B2 (ja) * | 2000-10-12 | 2009-01-21 | セイコーエプソン株式会社 | トランジスタ及びそれを備える表示装置 |

| JP4604440B2 (ja) * | 2002-02-22 | 2011-01-05 | 日本電気株式会社 | チャネルエッチ型薄膜トランジスタ |

| JP2005084416A (ja) * | 2003-09-09 | 2005-03-31 | Sharp Corp | アクティブマトリクス基板およびそれを用いた表示装置 |

| TWI279916B (en) * | 2005-01-31 | 2007-04-21 | Au Optronics Corp | TFT array substrate of a LCD, LCD panel and method of fabricating the same |

| KR101085451B1 (ko) * | 2005-02-11 | 2011-11-21 | 삼성전자주식회사 | 표시장치용 박막트랜지스터 기판과 그 제조방법 |

| KR101410926B1 (ko) * | 2007-02-16 | 2014-06-24 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조방법 |

| EP2073255B1 (en) * | 2007-12-21 | 2016-08-10 | Semiconductor Energy Laboratory Co., Ltd. | Diode and display device comprising the diode |

| JP5409024B2 (ja) * | 2008-02-15 | 2014-02-05 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP5587591B2 (ja) * | 2008-11-07 | 2014-09-10 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP5504008B2 (ja) * | 2009-03-06 | 2014-05-28 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| CN102884634B (zh) * | 2010-05-10 | 2015-09-16 | 夏普株式会社 | 半导体装置、有源矩阵基板以及显示装置 |

| JP5610855B2 (ja) * | 2010-06-04 | 2014-10-22 | 京セラディスプレイ株式会社 | 液晶表示装置および液晶表示装置の製造方法 |

-

2013

- 2013-03-06 JP JP2013044631A patent/JP6110693B2/ja not_active Expired - Fee Related

- 2013-03-08 US US13/790,248 patent/US20130240872A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013219335A (ja) | 2013-10-24 |

| US20130240872A1 (en) | 2013-09-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102355315B1 (ko) | 반도체 장치 및 그 제작 방법 | |

| JP6110693B2 (ja) | 半導体装置 | |

| US11411121B2 (en) | Semiconductor device | |

| JP6871328B2 (ja) | 半導体装置 | |

| JP6460610B2 (ja) | 半導体装置 | |

| TWI639235B (zh) | 半導體裝置 | |

| JP6208485B2 (ja) | 半導体装置、液晶表示装置 | |

| TWI750464B (zh) | 半導體裝置及其製造方法 | |

| JP5947629B2 (ja) | 半導体装置 | |

| KR102163686B1 (ko) | 반도체 장치 | |

| JP6343122B2 (ja) | 半導体装置の作製方法 | |

| JP6144882B2 (ja) | 半導体装置 | |

| JP6585780B2 (ja) | 発光表示装置 | |

| JP2014238577A (ja) | 表示装置、及び該表示装置を用いた電子機器 | |

| TW202013840A (zh) | 顯示裝置 | |

| JP2019176182A (ja) | 半導体装置 | |

| JP5873324B2 (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160223 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160223 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161209 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170214 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170310 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6110693 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |